# Advance Information

# Low-Voltage CMOS 16-Bit Latching Transceiver With 5V-Tolerant Inputs and Outputs (3-State, Non-Inverting)

The MC74LCX16543 is a high performance, non–inverting 16–bit latching transceiver operating from a 2.7 to 3.6V supply. The device is byte controlled. Each byte has separate control inputs which can be tied together for full 16–bit operation. High impedance TTL compatible inputs significantly reduce current loading to input drivers while TTL compatible outputs offer improved switching noise performance. A V<sub>I</sub> specification of 5.5V allows MC74LCX16543 inputs to be safely driven from 5V devices. The MC74LCX16543 is suitable for memory address driving and all TTL level bus oriented transceiver applications.

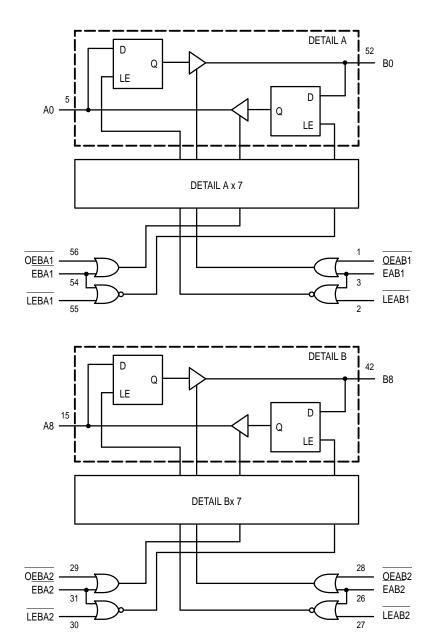

For data flow from A to B with the EAB LOW, the A-to-B Output Enable (OEAB) must be LOW in order to enable data to the B bus, as indicated in the Function Table. With EAB LOW, a LOW signal on the A-to-B Latch Enable (LEAB) input makes the A-to-B latches transparent; a subsequent LOW-to-HIGH transition of the LEAB signal will latch the A latches. and the outputs no longer change with the A inputs. With EAB and OEAB both LOW, the 3-State B output buffers are active and reflect the data present at the output of the A latches. Control of data flow from B to A is symetric to that above, but uses the EBA, LEBA, and OEBA inputs.

- Designed for 2.7 to 3.6V VCC Operation

- 5.2ns Maximum tpd

- 5V Tolerant Interface Capability With 5V TTL Logic

- · Supports Live Insertion and Withdrawal

- IOFF Specification Guarantees High Impedance When VCC = 0V

- LVTTL Compatible

- LVCMOS Compatible

- 24mA Balanced Output Sink and Source Capability

- Near Zero Static Supply Current in All Three Logic States (20μA) Substantially Reduces System Power Requirements

- Latchup Performance Exceeds 500mA

- ESD Performance: Human Body Model >2000V; Machine Model >200V

## MC74LCX16543

LOW-VOLTAGE CMOS 16-BIT LATCHING TRANSCEIVER

**DT SUFFIX**PLASTIC TSSOP PACKAGE

CASE 1202–01

### **PIN NAMES**

| 1 III IIAIILO                              |                                                                                                      |

|--------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pins                                       | Function                                                                                             |

| OExxn<br>Exxn<br>LExxn<br>A0-A15<br>B0-B15 | Output Enable Inputs Enable Inputs Latch Enable Inputs 3-State Inputs/Outputs 3-State Inputs/Outputs |

|                                            |                                                                                                      |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

### **LOGIC DIAGRAM**

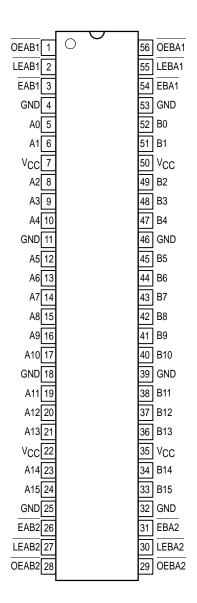

Pinout: 56-Lead TSSOP (Top View)

#### **FUNCTION TABLE**

|       |       | Inpu | uts  |       |       | Data Ports |        | On continue Mode                   |

|-------|-------|------|------|-------|-------|------------|--------|------------------------------------|

| OEABn | OEBAn | EABn | EBAn | LEABn | LEBAn | An         | Bn     | - Operating Mode                   |

| Н     | Н     |      |      |       |       | Input      | Input  |                                    |

|       |       | Х    | Х    | Х     | Х     | Х          | Х      | Disable Outputs                    |

|       |       | L    | L    | L     | L     | X          | Х      | Transparent Data; Outputs Disabled |

|       |       |      |      | Н     | Н     | l<br>h     | l<br>h | Latch and Outputs Disabled         |

| L     | Н     |      |      |       |       | Input      | Output |                                    |

|       |       | Н    | X*   | L     | Х     | l<br>h     | Z<br>Z | Load and B Outputs Disabled        |

|       |       |      |      | Н     | Х     | Х          | Z      | Hold; B Outputs Disabled           |

|       |       | L    | X*   | L     | Х     | L<br>H     | L<br>H | Transparent A to B                 |

|       |       |      |      | Н     | Х     | l<br>h     | L<br>H | Latch and Display B Outputs        |

| Н     | L     |      |      |       |       | Output     | Input  |                                    |

|       |       | X*   | Н    | Х     | L     | Z<br>Z     | l<br>h | Load and A Outputs Disabled        |

|       |       |      |      | Х     | Н     | Z          | Х      | Hold; A Outputs DIsabled           |

|       |       | X*   | L    | Х     | L     | L<br>H     | L<br>H | Transparent B to A                 |

|       |       |      |      | Х     | Н     | L<br>H     | l<br>h | Latch and Display A Outputs        |

H = High Voltage Level; h = High Voltage Level One Setup Time Prior to the Latch Enable or Enable Low—to—High Transition; L = Low Voltage Level; l = Low Voltage Level One Setup Time Prior to the Latch Enable or Enable Low—to—High Transition; X = Don't Care; \* = The latches are not internally gated with the Output Enables. Therefore, data at the A or B ports may enter the latches at any time, provided that the LExx and Exx pins are set accordingly. For I<sub>CC</sub> reasons, Do Not Float Inputs.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Symbol           | Parameter                        | Value                             | Condition            | Unit |

|------------------|----------------------------------|-----------------------------------|----------------------|------|

| Vcc              | DC Supply Voltage                | -0.5 to +7.0                      |                      | V    |

| VI               | DC Input Voltage                 | $-0.5 \le V_1 \le +7.0$           |                      | V    |

| VO               | DC Output Voltage                | $-0.5 \le V_{O} \le +7.0$         | Output in 3–State    | V    |

|                  |                                  | $-0.5 \le V_{O} \le V_{CC} + 0.5$ | Note 1.              | V    |

| Ιικ              | DC Input Diode Current           | <b>–</b> 50                       | V <sub>I</sub> < GND | mA   |

| loк              | DC Output Diode Current          | -50                               | V <sub>O</sub> < GND | mA   |

|                  |                                  | +50                               | AO > ACC             | mA   |

| lo               | DC Output Source/Sink Current    | ±50                               |                      | mA   |

| Icc              | DC Supply Current Per Supply Pin | ±100                              |                      | mA   |

| <sup>I</sup> GND | DC Ground Current Per Ground Pin | ±100                              |                      | mA   |

| TSTG             | Storage Temperature Range        | -65 to +150                       |                      | °C   |

<sup>\*</sup> Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute—maximum—rated conditions is not implied.

3

<sup>1.</sup> Output in HIGH or LOW State. IO absolute maximum rating must be observed.

### RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter                                                                       | Min        | Тур        | Max                    | Unit |

|--------|---------------------------------------------------------------------------------|------------|------------|------------------------|------|

| Vcc    | Supply Voltage Operating Data Retention Only                                    | 2.0<br>1.5 | 3.3<br>3.3 | 3.6<br>3.6             | V    |

| VI     | Input Voltage                                                                   | 0          |            | 5.5                    | V    |

| VO     | Output Voltage (HIGH or LOW State) (3–State)                                    | 0<br>0     |            | V <sub>CC</sub><br>5.5 | V    |

| IOH    | HIGH Level Output Current, V <sub>CC</sub> = 3.0V – 3.6V                        |            |            | -24                    | mA   |

| loL    | LOW Level Output Current, V <sub>CC</sub> = 3.0V – 3.6V                         |            |            | 24                     | mA   |

| loн    | HIGH Level Output Current, V <sub>CC</sub> = 2.7V - 3.0V                        |            |            | -12                    | mA   |

| lOL    | LOW Level Output Current, V <sub>CC</sub> = 2.7V – 3.0V                         |            |            | 12                     | mA   |

| TA     | Operating Free-Air Temperature                                                  | -40        |            | +85                    | °C   |

| Δt/ΔV  | Input Transition Rise or Fall Rate, $V_{IN}$ from 0.8V to 2.0V, $V_{CC}$ = 3.0V | 0          |            | 10                     | ns/V |

### DC ELECTRICAL CHARACTERISTICS

|                 |                                       |                                                                                    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |      |

|-----------------|---------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------|------|------|

| Symbol          | Characteristic                        | Condition                                                                          | Min                                           | Max  | Unit |

| V <sub>IH</sub> | HIGH Level Input Voltage (Note 2.)    | 2.7V ≤ V <sub>CC</sub> ≤ 3.6V                                                      | 2.0                                           |      | V    |

| V <sub>IL</sub> | LOW Level Input Voltage (Note 2.)     | 2.7V ≤ V <sub>CC</sub> ≤ 3.6V                                                      |                                               | 0.8  | V    |

| Vон             | HIGH Level Output Voltage             | $2.7V \le V_{CC} \le 3.6V; I_{OH} = -100\mu A$                                     | V <sub>CC</sub> - 0.2                         |      | V    |

|                 |                                       | V <sub>CC</sub> = 2.7V; I <sub>OH</sub> = -12mA                                    | 2.2                                           |      | 1    |

|                 |                                       | V <sub>CC</sub> = 3.0V; I <sub>OH</sub> = -18mA                                    | 2.4                                           |      | 1    |

|                 |                                       | V <sub>CC</sub> = 3.0V; I <sub>OH</sub> = -24mA                                    | 2.2                                           |      | 1    |

| VOL             | LOW Level Output Voltage              | $2.7V \le V_{CC} \le 3.6V$ ; $I_{OL} = 100\mu A$                                   |                                               | 0.2  | V    |

|                 |                                       | V <sub>CC</sub> = 2.7V; I <sub>OL</sub> = 12mA                                     |                                               | 0.4  | 1    |

|                 |                                       | V <sub>CC</sub> = 3.0V; I <sub>OL</sub> = 16mA                                     |                                               | 0.4  | 1    |

|                 |                                       | V <sub>CC</sub> = 3.0V; I <sub>OL</sub> = 24mA                                     |                                               | 0.55 | 1    |

| lį              | Input Leakage Current                 | 2.7V ≤ V <sub>CC</sub> ≤ 3.6V; 0V ≤ V <sub>I</sub> ≤ 5.5V                          |                                               | ±5.0 | μΑ   |

| loz             | 3–State Output Current                | $2.7 \le V_{CC} \le 3.6V$ ; $0V \le V_{O} \le 5.5V$ ; $V_{I} = V_{IH}$ or $V_{IL}$ |                                               | ±5.0 | μΑ   |

| loff            | Power-Off Leakage Current             | $V_{CC} = 0V$ ; $V_I$ or $V_O = 5.5V$                                              |                                               | 10   | μΑ   |

| ICC             | Quiescent Supply Current              | $2.7 \le V_{CC} \le 3.6V$ ; $V_I = GND \text{ or } V_{CC}$                         |                                               | 20   | μΑ   |

|                 |                                       | $2.7 \le V_{CC} \le 3.6V$ ; $3.6 \le V_I$ or $V_O \le 5.5V$                        |                                               | ±20  | μΑ   |

| ΔlCC            | Increase in I <sub>CC</sub> per Input | 2.7 ≤ V <sub>CC</sub> ≤ 3.6V; V <sub>IH</sub> = V <sub>CC</sub> − 0.6V             |                                               | 500  | μΑ   |

<sup>2.</sup> These values of V<sub>I</sub> are used to test DC electrical characteristics only.

### **AC CHARACTERISTICS** (Note 3.; $t_R = t_F = 2.5 \text{ns}$ ; $C_L = 50 \text{pF}$ ; $R_L = 500 \Omega$ )

|                                        |                                                                 |          |                                               | Lin        | nits              |            |      |

|----------------------------------------|-----------------------------------------------------------------|----------|-----------------------------------------------|------------|-------------------|------------|------|

|                                        |                                                                 |          | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |            |                   |            | 1    |

|                                        |                                                                 |          | V <sub>CC</sub> = 3.                          | 0V to 3.6V | V <sub>CC</sub> = | = 2.7V     | 1    |

| Symbol                                 | Parameter                                                       | Waveform | Min                                           | Max        | Min               | Max        | Unit |

| <sup>t</sup> PLH<br><sup>t</sup> PHL   | Propagation Delay<br>An to Bn or Bn to An                       | 1        | 1.5<br>1.5                                    | 5.2<br>5.2 | 1.5<br>1.5        | 6.0<br>6.0 | ns   |

| <sup>t</sup> PLH<br><sup>t</sup> PHL   | <u>Propag</u> ation Del <u>ay</u><br>LEBAn to An or LEABn to Bn | 4        | 1.5<br>1.5                                    | 6.5<br>6.5 | 1.5<br>1.5        | 7.5<br>7.5 | ns   |

| <sup>t</sup> PZH<br><sup>t</sup> PZL   | Output Enable Time OEBAn to An or OEABn to Bn                   | 2        | 1.5<br>1.5                                    | 6.5<br>6.5 | 1.5<br>1.5        | 7.0<br>7.0 | ns   |

| <sup>t</sup> PHZ<br><sup>t</sup> PLZ   | Output Disable Time OEBAn to An or OEABn to Bn                  | 2        | 1.5<br>1.5                                    | 6.5<br>6.5 | 1.5<br>1.5        | 7.0<br>7.0 | ns   |

| <sup>t</sup> PZH<br><sup>t</sup> PZL   | Output Enable <u>Time</u><br>EBAn to An or EABn to Bn           | 2        | 1.5<br>1.5                                    | 6.5<br>6.5 | 1.5<br>1.5        | 7.0<br>7.0 | ns   |

| <sup>t</sup> PHZ<br><sup>t</sup> PLZ   | Output Disable <u>Time</u><br>EBAn to An or EABn to Bn          | 2        | 1.5<br>1.5                                    | 6.5<br>6.5 | 1.5<br>1.5        | 7.0<br>7.0 | ns   |

| t <sub>S</sub>                         | Setup Time, HIGH to LOW Data to LExxn                           | 4        | 2.5                                           |            | 2.5               |            | ns   |

| th                                     | Hold Time, HIGH to LOW Data to LExxn                            | 4        | 1.5                                           |            | 1.5               |            | ns   |

| t <sub>S</sub>                         | Setup Time, HIGH to LOW Data to Exxn                            | 4        | 2.5                                           |            | 2.5               |            | ns   |

| t <sub>h</sub>                         | Hold Time, HIGH to LOW Data to Exxn                             | 4        | 1.5                                           |            | 1.5               |            | ns   |

| t <sub>W</sub>                         | Latch Enable or Enable Pulse Width, LOW                         | 4        | 3.0                                           |            | 3.0               |            | ns   |

| <sup>t</sup> OSHL<br><sup>t</sup> OSLH | Output–to–Output Skew (Note 4.)                                 |          |                                               | 1.0<br>1.0 |                   |            | ns   |

<sup>3.</sup> These AC parameters are preliminary and may be modified prior to release. The maximum AC limits are design targets. Actual performance will be specified upon completion of characterization.

### **DYNAMIC SWITCHING CHARACTERISTICS**

|                  |                                      |                                                                  | T <sub>A</sub> = +25°C |     |     |      |

|------------------|--------------------------------------|------------------------------------------------------------------|------------------------|-----|-----|------|

| Symbol           | Characteristic                       | Condition                                                        | Min                    | Тур | Max | Unit |

| V <sub>OLP</sub> | Dynamic LOW Peak Voltage (Note 5.)   | $V_{CC} = 3.3V$ , $C_L = 50pF$ , $V_{IH} = 3.3V$ , $V_{IL} = 0V$ |                        | 0.8 |     | V    |

| V <sub>OLV</sub> | Dynamic LOW Valley Voltage (Note 5.) | $V_{CC} = 3.3V$ , $C_L = 50pF$ , $V_{IH} = 3.3V$ , $V_{IL} = 0V$ |                        | 0.8 |     | V    |

<sup>5.</sup> Number of outputs defined as "n". Measured with "n-1" outputs switching from HIGH-to-LOW or LOW-to-HIGH. The remaining output is measured in the LOW state.

#### **CAPACITIVE CHARACTERISTICS**

| Symbol           | Parameter                     | Parameter Condition                             |    | Unit |

|------------------|-------------------------------|-------------------------------------------------|----|------|

| C <sub>IN</sub>  | Input Capacitance             | $V_{CC} = 3.3V$ , $V_I = 0V$ or $V_{CC}$        | 7  | pF   |

| C <sub>I/O</sub> | Input/Output Capacitance      | $V_{CC} = 3.3V$ , $V_I = 0V$ or $V_{CC}$        | 8  | pF   |

| C <sub>PD</sub>  | Power Dissipation Capacitance | 10MHz, $V_{CC} = 3.3V$ , $V_I = 0V$ or $V_{CC}$ | 20 | pF   |

5

<sup>4.</sup> Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (toshL) or LOW-to-HIGH (toslH); parameter guaranteed by design.

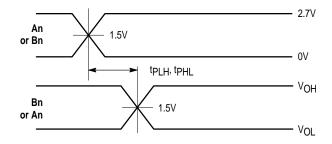

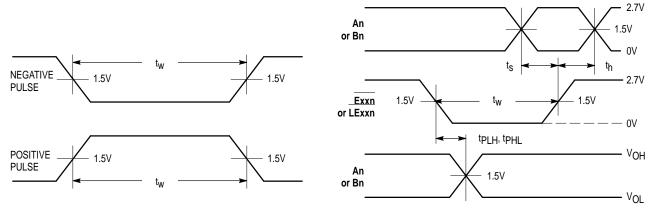

### WAVEFORM 1 - A/B to B/A PROPAGATION DELAYS

$t_R = t_F = 2.5$ ns, 10% to 90%; f = 1MHz;  $t_W = 500$ ns

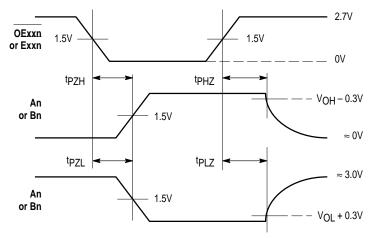

WAVEFORM 2 – OExx/Exx to A or B OUTPUT ENABLE AND DISABLE TIMES  $t_R = t_F = 2.5 ns, \, 10\% \text{ to } 90\%; \, f = 1 MHz; \, t_W = 500 ns$

Figure 1. AC Waveforms

**WAVEFORM 3 – INPUT PULSE DEFINITION**  $t_R = t_F = 2.5$ ns, 10% to 90% of 0V to 2.7V

WAVEFORM 4 - Enable to A or B PROPAGATION DELAYS, Enable MINIMUM PULSE WIDTH, A or B to Enable SETUP AND HOLD TIMES  $t_R = t_F = 2.5 ns$ , 10% to 90%; f = 1MHz;  $t_W = 500 ns$  except when noted

Figure 2. AC Waveforms (continued)

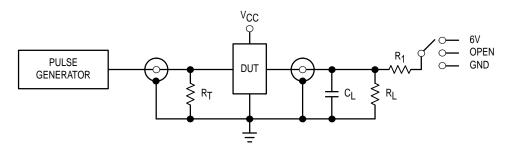

| TEST                                | SWITCH |

|-------------------------------------|--------|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Open   |

| tPZL, tPLZ                          | 6V     |

| Open Collector/Drain tpLH and tpHL  | 6V     |

| <sup>t</sup> PZH <sup>, t</sup> PHZ | GND    |

$C_L$  = 50pF or equivalent (Includes jig and probe capacitance)  $R_L$  =  $R_1$  = 500 $\Omega$  or equivalent  $R_T$  =  $Z_{OUT}$  of pulse generator (typically 50 $\Omega$ )

Figure 3. Test Circuit

7

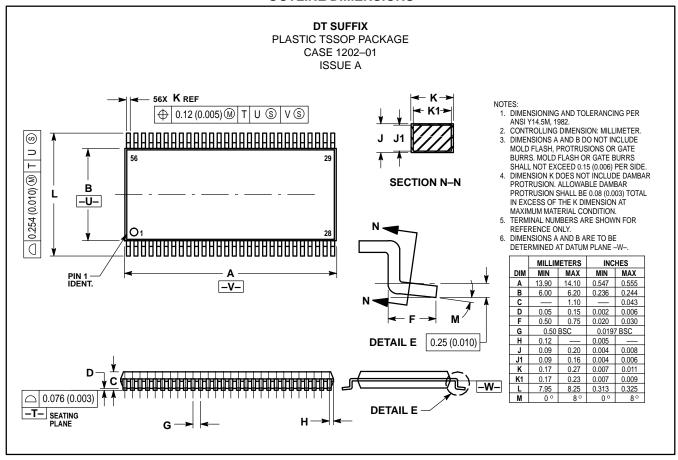

#### **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the design or manufacture of the part. Motorola and opportunity/Affirmative Action Employer.

#### How to reach us:

**USA/EUROPE/Locations Not Listed**: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–800–441–2447

Mfax™: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design=NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

MC74LCX16543/D