# Clock Driver Quad D-Type Flip-Flop With Matched Propagation Delays

The MC74F803 is a high-speed, low-power, quad D-type flip-flop featuring separate D-type inputs, and inverting outputs with closely matched propagation delays. With a buffered clock (CP) input that is common to all flip-flops, the F803 is useful in high-frequency systems as a clock driver, providing multiple outputs that are synchronous. Because of the matched propagation delays, the duty cycles of the output waveforms in a clock driver application are symmetrical within 1.0 to 1.5 nanoseconds.

- Edge-Triggered D-Type Inputs

- Buffered Positive Edge-Triggered Clock

- Matched Outputs for Synchronous Clock Driver Applications

- Outputs Guaranteed for Simultaneous Switching

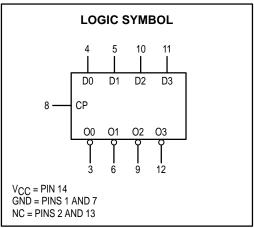

#### Pinout: 14-Lead Plastic (Top View) О3 D2 02 СР D3 10 9 8 2 **GND** NC 00 D0 D1 01 **GND**

#### **GUARANTEED OPERATION RANGES**

| Symbol         | Parameter                              | Min | Тур | Max | Unit |

|----------------|----------------------------------------|-----|-----|-----|------|

| VCC            | Supply Voltage                         | 4.5 | 5.0 | 5.5 | V    |

| T <sub>A</sub> | Operating Ambient<br>Temperature Range | 0   | 25  | 70  | °C   |

| loн            | Output Current — High                  | _   | -   | -20 | mA   |

| loL            | Output Current — Low                   | _   | 1   | 24  | mA   |

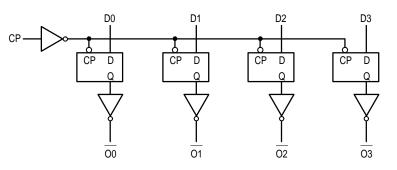

#### **LOGIC DIAGRAM**

# MC74F803

CLOCK DRIVER QUAD D-TYPE FLIP-FLOP WITH MATCHED PROPAGATION DELAYS

11/93

#### **FUNCTIONAL DESCRIPTION**

The F803 consists of four positive edge-triggered flip-flops with individual D-type inputs and inverting outputs. The buffered clock is common to all flip-flops and the following specifications allow for outputs switching simultaneously. The four flip-flops store the state of their individual D inputs that meet the setup and hold time requirements on the LOW-to-HIGH Clock (CP) transition. The maximum frequency of the clock input is 70 megahertz, and the LOW-to-HIGH and HIGH-to-LOW propagation delays of the O<sub>1</sub> output vary by, at most, 1 nanosecond. Therefore, the device is ideal for use as

a divide-by-two driver for high-frequency clock signals that require symmetrical duty cycles. The difference between the LOW-to-HIGH\_and HIGH-to-LOW propagation delays for the O<sub>0</sub>, O<sub>2</sub>, and O<sub>3</sub> outputs vary by at most 1.5 nanoseconds. These outputs are very useful as clock drivers for circuits with less stringent requirements. In addition, the output-to-output skew is a maximum of 1.5 nanoseconds. Finally, the I<sub>OH</sub> specification at 2.5 volts is guaranteed to be at least – 20 milliamps. If their inputs are identical, multiple outputs can be tied together and the I<sub>OH</sub> is commensurately increased.

# DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

|                 |                                          | Limits |      |       |      |                               |                         |

|-----------------|------------------------------------------|--------|------|-------|------|-------------------------------|-------------------------|

| Symbol          | Parameter                                | Min    | Тур  | Max   | Unit | Test (                        | Conditions*             |

| VIH             | Input HIGH Voltage                       | 2.0    | _    | _     | V    | Guaranteed Input HIGH Voltage |                         |

| V <sub>IL</sub> | Input LOW Voltage                        | _      | _    | 0.8   | V    | Guaranteed Input L            | OW Voltage              |

| VIK             | Input Clamp Diode Voltage                | _      | _    | - 1.2 | V    | $I_{IN} = -18 \text{ mA}$     | V <sub>CC</sub> = MIN   |

| Vон             | Output HIGH Voltage                      | 2.5    | _    | _     | V    | I <sub>OH</sub> = -20 mA      | V <sub>CC</sub> = 4.5 V |

| VOL             | Output LOW Voltage                       | _      | 0.35 | 0.5   | V    | I <sub>OL</sub> = 24 mA       | V <sub>CC</sub> = MIN   |

|                 |                                          | _      | _    | 20    | μΑ   | V <sub>IN</sub> = 2.7 V       | V <sub>CC</sub> = MAX   |

| lн              | Input HIGH Current                       | _      | _    | 100   |      | V <sub>IN</sub> = 7.0 V       | V <sub>CC</sub> = MAX   |

| I <sub>IL</sub> | Input LOW Current                        | _      | _    | -0.6  | mA   | V <sub>IN</sub> = 0.5 V       | V <sub>CC</sub> = MAX   |

| los             | Output Short Circuit Current<br>(Note 2) | -60    | _    | -150  | mA   | VOUT = 0 V                    | V <sub>CC</sub> = MAX   |

| Icc             | Power Supply Current                     | _      | _    | 70    | mA   | V <sub>CC</sub> = MAX         |                         |

<sup>\*</sup> Normal test conditions for this device are all four outputs switching simultaneously. Two outputs of the 74F803 can be tied together and the IOH doubles.

## AC CHARACTERISTICS ( $T_A = 0$ to $70^{\circ}$ C, $V_{CC} = 5.0 \text{ V} \pm 10\%$ , see Note 1)

|                                                                     |                                                                                                         | C <sub>L</sub> = 50 pF |     | C <sub>L</sub> = 100 pF |     |      |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------|-----|-------------------------|-----|------|

| Symbol                                                              | Parameter                                                                                               | Min                    | Max | Min                     | Max | Unit |

| f <sub>max</sub>                                                    | Maximum Clock Frequency                                                                                 | 70                     | _   | 50                      | _   | MHz  |

| tPLH<br>tPHL                                                        | Propagation Delay CP to On                                                                              |                        | 7.5 | 3.0                     | 10  | ns   |

| tp <sub>V</sub>                                                     | Propagation Delay CP to On Variation (see Note 3)                                                       |                        | 3.0 | _                       | 4.0 | ns   |

| t <sub>ps</sub> O <sub>1</sub>                                      | Propagation Delay Skew  tpLH Actual - tpHL Actual  for O1 Only                                          |                        | 1.0 | _                       | 2.0 | ns   |

| t <sub>ps</sub> O <sub>0</sub> ,<br>O <sub>2</sub> , O <sub>3</sub> | Propagation Delay Skew  tpLH Actual - tpHL Actual  for O <sub>0</sub> , O <sub>2</sub> , O <sub>3</sub> |                        | 1.5 | _                       | 2.0 | ns   |

| t <sub>os</sub>                                                     | Output to Output Skew (see Note 2)  tp On - tp Om                                                       | _                      | 1.5 | _                       | 2.5 | ns   |

| t <sub>rise</sub> , t <sub>fall</sub><br>O <sub>1</sub>             | Rise/Fall Time for O <sub>1</sub> (0.8 to 2.0 V)                                                        |                        | 3.0 | _                       | 4.0 | ns   |

| trise, tfall<br>O <sub>0</sub> , O <sub>2</sub> , O <sub>3</sub>    | Rise/Fall Time for $O_0$ , $O_2$ , $O_3$ (0.8 to 2.0 V)                                                 |                        | 3.5 | _                       | 4.5 | ns   |

<sup>1.</sup> The test conditions used are all four outputs switching simultaneously. The AC characteristics described above (except for O<sub>1</sub>) are also guarantee<u>d</u> when two outputs are tied together.

<sup>1.</sup> For conditions such as MIN or MAX, use the appropriate value specified under guaranteed operating ranges.

<sup>2.</sup> Not more than one output should be shorted at a time, nor for more than 1 second.

<sup>2.</sup> Where t<sub>p</sub> On and t<sub>p</sub> Om are the actual propagation delays (any combination of high or low) for two separate outputs from a given high transition of CP.

<sup>3.</sup> For a given set of conditions (i.e., capacitive load, temperature, V<sub>CC</sub>, and number of outputs switching simultaneously) the variation from device to device is guaranteed to be less than or equal to the maximum.

# AC OPERATING REQUIREMENTS (T<sub>A</sub> = 0 to 70°C, $V_{CC}$ = 5.0 V $\pm$ 10%)

|                |                                                 | C <sub>L</sub> = 50 pF |     | C <sub>L</sub> = 100 pF |     |      |

|----------------|-------------------------------------------------|------------------------|-----|-------------------------|-----|------|

| Symbol         | Parameter                                       | Min                    | Max | Min                     | Max | Unit |

| ts(H)<br>ts(L) | Setup Time, HIGH or LOW<br>D <sub>n</sub> to CP | 3.0<br>3.0             |     | 4.0<br>4.0              |     | ns   |

| tf             | t <sub>p</sub> + t <sub>S</sub> (see Note)      | _                      | 9.0 | _                       | 12  | ns   |

| th(H)<br>th(L) | Hold Time, HIGH or LOW D <sub>n</sub> to CP     | 2.0<br>2.0             |     | 2.0<br>2.0              | 1 1 | ns   |

| tw(H)<br>tw(L) | CP Pulse Width<br>HIGH or LOW                   | 7.0<br>6.0             |     | 8.0<br>8.0              |     | ns   |

The combination of the setup time (t<sub>S</sub>) requirement and maximum propagation delay (t<sub>p</sub>) are guaranteed to be within this limit for all conditions.

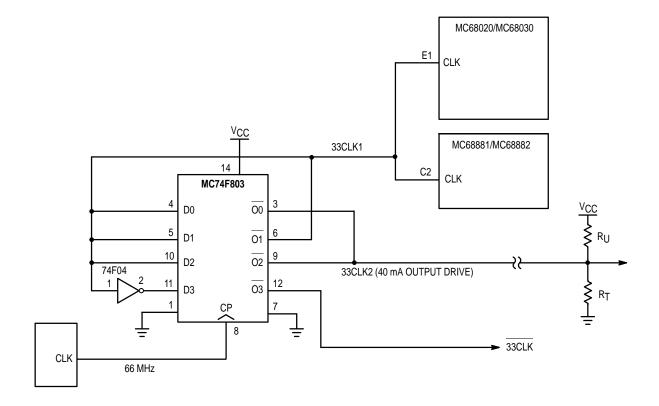

# **APPLICATION NOTE**

The closely matched outputs of the MC74F803 provide an ideal interface for the clock input of Motorola's high-frequency microprocessors.

## 74F803 INTERFACE AS CLOCK TO MC68020 SYSTEM

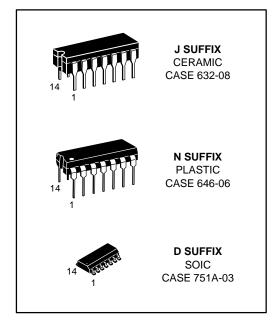

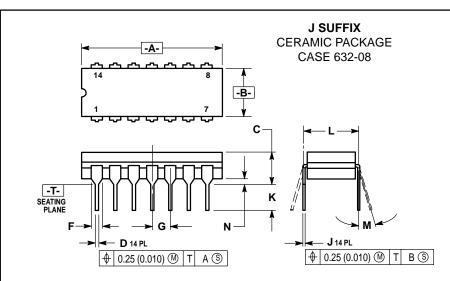

### **OUTLINE DIMENSIONS**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEAD WHEN

TO SENTER OF LEAD WHEN FORMED PARALLEL.

4. DIM F MAY NARROW TO 0.76 (0.030) WHERE

- THE LEAD ENTERS THE CERAMIC BODY.

5. 632-01 THRU -07 OBSOLETE, NEW STANDARD

|     | MILLIMETERS |       | INC       | HES   |  |

|-----|-------------|-------|-----------|-------|--|

| DIM | MIN         | MAX   | MIN       | MAX   |  |

| Α   | 19.05       | 19.94 | 0.750     | 0.785 |  |

| В   | 6.23        | 7.11  | 0.245     | 0.280 |  |

| С   | 3.94        | 5.08  | 0.155     | 0.200 |  |

| D   | 0.39        | 0.50  | 0.015     | 0.020 |  |

| F   | 1.40        | 1.65  | 0.055     | 0.065 |  |

| G   | 2.54        | BSC   | 0.100 BSC |       |  |

| J   | 0.21        | 0.38  | 0.008     | 0.015 |  |

| K   | 3.18        | 4.31  | 0.125     | 0.170 |  |

| L   | 7,62 BSC 。  |       | 0.300     | BSC 。 |  |

| M   | 0           | 15    | 0         | 15    |  |

| N   | 0.51        | 1.01  | 0.020     | 0.040 |  |

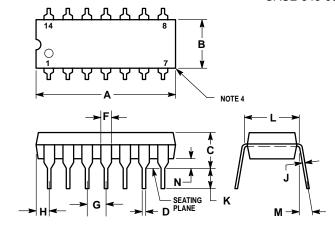

# **N SUFFIX** PLASTIC PACKAGE CASE 646-06

#### NOTES:

- 1. LEADS WITHIN 0.13 mm (0.005) RADIUS OF TRUE POSITION AT SEATING PLANE AT MAXIMUM MATERIAL CONDITION.

DIMENSION "L" TO CENTER OF LEADS WHEN FORMED PARALLEL.

- DIMENSION "B" DOES NOT INCLUDE MOLD FLASH.

- ROUNDED CORNERS OPTIONAL. 646-05 OBSOLETE, NEW STANDARD 646-06.

|     | MILLIM                              | IETERS    | INC          | HES   |  |

|-----|-------------------------------------|-----------|--------------|-------|--|

| DIM | MIN MAX                             |           | MIN          | MAX   |  |

| Α   | 18.16                               | 19.56     | 0.715        | 0.770 |  |

| В   | 6.10                                | 6.60      | 0.240        | 0.260 |  |

| С   | 3.69                                | 4.69      | 0.145        | 0.185 |  |

| D   | 0.38                                | 0.38 0.53 |              | 0.021 |  |

| F   | 1.02                                | 1.78      | 0.040        | 0.070 |  |

| G   | 2.54                                | BSC       | 0.100 BSC    |       |  |

| Н   | 1.32                                | 2.41      | 0.052        | 0.095 |  |

| J   | 0.20                                | 0.38      | 0.008        | 0.015 |  |

| K   | 2.92                                | 3.43      | 0.115        | 0.135 |  |

| L   | <sub>0</sub> 7.62 BSC <sub>0°</sub> |           | <b>₽</b> 300 | BSG.  |  |

| M   | 0.39                                | 1.01      | 0.015        | 0.039 |  |

| N   | 0.55                                | 1.01      | 0.013        | 0.000 |  |

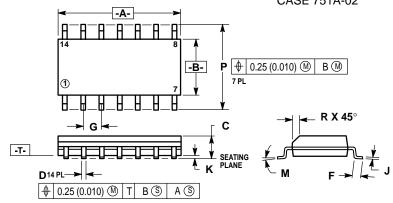

# **D SUFFIX** SOIC PACKAGE CASE 751A-02

#### NOTES:

- DIMENSIONS "A" AND "B" ARE DATUMS AND "T" IS A DATUM SURFACE.

DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- 5. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- 751A-01 IS OBSOLETE, NEW STANDARD 751A-02.

|     | MILLIMETERS |          | INC       | HES   |

|-----|-------------|----------|-----------|-------|

| DIM | MIN MAX     |          | MIN       | MAX   |

| Α   | 8.55        | 8.75     | 0.337     | 0.344 |

| В   | 3.80        | 4.00     | 0.150     | 0.157 |

| С   | 1.35        | 1.75     | 0.054     | 0.068 |

| D   | 0.35        | 0.49 0.0 |           | 0.019 |

| F   | 0.40        | 1.25     | 0.016     | 0.049 |

| G   | 1.27 BSC    |          | 0.050 BSC |       |

| J   | 0.19        | 0.25     | 0.008     | 0.009 |

| K   | 0.10        | 0.25     | 0.004     | 0.009 |

| M   | 0           | 7        | 0         | 7     |

| P   | 5.80        | 6.20     | 0.229     | 0.244 |

| R   | 0.25        | 0.50     | 0.010     | 0.019 |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### **Literature Distribution Centers:**

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan.

ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

CODELINE TO BE PLACED HERE