# Multi-Character LED Display/Lamp Driver CMOS

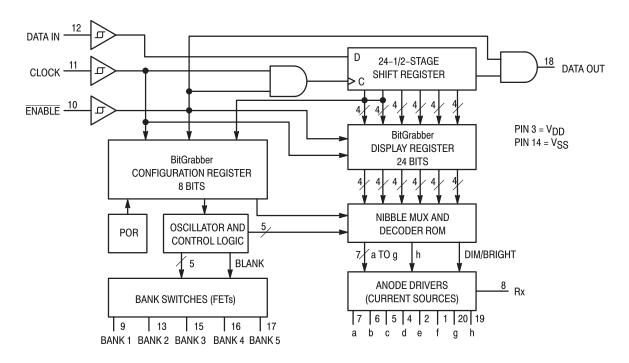

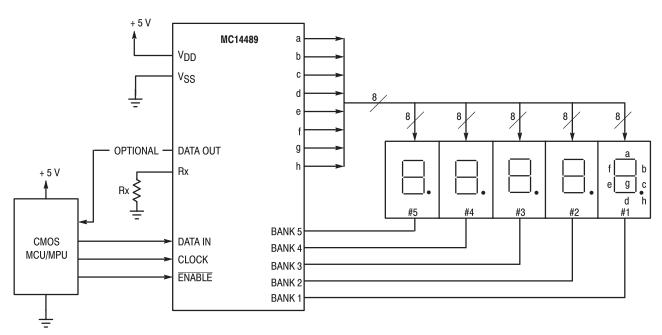

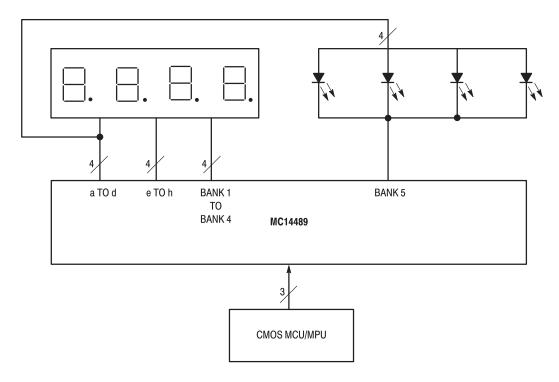

The MC14489 is a flexible light—emitting—diode driver which directly interfaces to individual lamps, 7—segment displays, or various combinations of both. LEDs wired with common cathodes are driven in a multiplexed—by—5 fashion. Communication with an MCU/MPU is established through a synchronous serial port. The MC14489 features data retention plus decode and scan circuitry, thus relieving processor overhead. A single, current—setting resistor is the only ancillary component required.

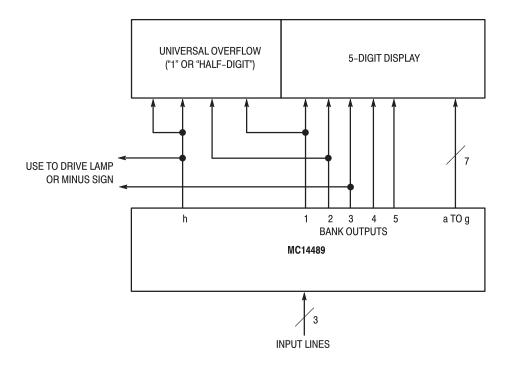

A single device can drive any one of the following: a 5–digit display plus decimals, a 4–1/2–digit display plus decimals and sign, or 25 lamps. A special technique allows driving 5 1/2 digits; see Figure 16. A configuration register allows the drive capability to be partitioned off to suit many additional applications. The on–chip decoder outputs 7–segment–format numerals 0 to 9, hexadecimal characters A to F, plus 15 letters and symbols.

The MC14489 is compatible with the Motorola SPI and National MICRO-WIRE™ serial data ports. The chip's patented BitGrabber™ registers augment the serial interface by allowing random access without steering or address bits. A 24-bit transfer updates the display register. Changing the configuration register requires an 8-bit transfer.

- Operating Voltage Range of Drive Circuitry: 4.5 to 6 V

- Operating Junction Temperature Range: 40° to 130°C

- · Current Sources Controlled by Single Resistor Provide Anode Drive

- Low-Resistance FET Switches Provide Direct Common Cathode Interface

- Low-Power Mode (Extinguishes the LEDs) and Brightness Controlled via Serial Port

- Special Circuitry Minimizes EMI when Display is Driven and Eliminates EMI in Low–Power Mode

- Power–On Reset (POR) Blanks the Display on Power–Up, Independent of Supply Ramp Up Time

- May Be Used with Double-Heterojunction LEDs for Optimum Efficiency

- Chip Complexity: 4300 Elements (FETs, Resistors, Capacitors, etc.)

- See Application Note AN431, Temperature Measurement and Display Using the MC68HC05B4 and the MC14489 and Engineering Bulletin EB153, Driving a Seven–Segment Display with the Neuron<sup>®</sup> Chip

# MC14489

See web site motorola.com/pll for PLL control software. Look under Overview/Support Products/ PLL Demonstration Software. Choose PLLGEN.EXE. Although the MC14489 is not a PLL, the software available at the above location may be used with this part.

BitGrabber is a trademark of Motorola Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

REV 4 8/98 TN98081000

#### **BLOCK DIAGRAM**

#### MAXIMUM RATINGS\* (Voltages Referenced to VSS)

| Symbol                            | Parameter                                                                                                   | Value                          | Unit |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------|------|

| V <sub>DD</sub>                   | DC Supply Voltage                                                                                           | - 0.5 to + 6.0                 | V    |

| V <sub>in</sub>                   | DC Input Voltage                                                                                            | - 0.5 to V <sub>DD</sub> + 0.5 | V    |

| V <sub>out</sub>                  | DC Output Voltage                                                                                           | - 0.5 to V <sub>DD</sub> + 0.5 | V    |

| l <sub>in</sub>                   | DC Input Current — per Pin<br>(Includes Pin 8)                                                              | ± 15                           | mA   |

| l <sub>out</sub>                  | DC Output Current — Pins 1, 2, 4 – 7, 19, 20 Sourcing Sinking                                               | - 40<br>10                     | mA   |

|                                   | Pins 9, 13, 15, 16, 17 Sinking                                                                              | 320                            |      |

|                                   | Pin 18                                                                                                      | ± 15                           |      |

| I <sub>DD</sub> , I <sub>SS</sub> | DC Supply Current, V <sub>DD</sub> and V <sub>SS</sub> Pins                                                 | ± 350                          | mA   |

| TJ                                | Chip Junction Temperature                                                                                   | - 40 to + 130                  | °C   |

| R <sub>θJA</sub>                  | Device Thermal Resistance, Junction-to-Ambient (see Thermal Considerations section) Plastic DIP SOG Package | 90<br>100                      | °C/W |

| T <sub>stg</sub>                  | Storage Temperature                                                                                         | - 65 to + 150                  | °C   |

| TL                                | Lead Temperature, 1 mm from Case for 10 Seconds                                                             | 260                            | °C   |

<sup>\*</sup> Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics tables or Pin Descriptions section.

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}.$

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>). Unused outputs must be left open.

# $\textbf{ELECTRICAL CHARACTERISTICS} \text{ (Voltages Referenced to V}_{SS}, \text{ T}_{J} = -40^{\circ} \text{ to } 130^{\circ}\text{C}^{\star} \text{ unless otherwise indicated)}$

| Parameter                                                                                                                       | Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>DD</sub>                                   | Guaranteed<br>Limit            | Unit                                              |  |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------|---------------------------------------------------|--|

| Power Supply Voltage Range of LED Drive Circuitry                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   | 4.5 to 6.0                     | V                                                 |  |

| Minimum Standby Voltage                                                                                                         | Bits Retained in Display and<br>Configuration Registers, Data<br>Port Fully Functional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                 | 3.0                            | V                                                 |  |

| Maximum Low–Level Input Voltage (Data In, Clock, Enable)                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.0<br>6.0                                        | 0.9<br>1.8                     | V                                                 |  |

| Minimum High-Level Input Voltage<br>(Data In, Clock, Enable)                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.0<br>6.0                                        | 2.1<br>4.2                     | V                                                 |  |

| Minimum Hysteresis Voltage<br>(Data In, Clock, Enable)                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.0<br>6.0                                        | 0.2<br>0.4                     | V                                                 |  |

| Maximum Low–Level Output Voltage<br>(Data Out)                                                                                  | I <sub>out</sub> = 20 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.0<br>6.0                                        | 0.1<br>0.1                     | V                                                 |  |

|                                                                                                                                 | I <sub>out</sub> = 1.3 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.5                                               | 0.4                            |                                                   |  |

| Minimum High-Level Output Voltage<br>(Data Out)                                                                                 | I <sub>out</sub> = - 20 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.0<br>6.0                                        | 2.9<br>5.9                     | V                                                 |  |

|                                                                                                                                 | I <sub>out</sub> = - 800 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.5                                               | 4.1                            |                                                   |  |

| Maximum Input Leakage Current                                                                                                   | V <sub>in</sub> = V <sub>DD</sub> or V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6.0                                               | ± 2.0                          | μΑ                                                |  |

| (Data In, Clock, Enable)                                                                                                        | $V_{in} = V_{DD} \text{ or } V_{SS},$<br>$T_J = 25^{\circ}\text{C only}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6.0                                               | ± 0.1                          |                                                   |  |

| Minimum Sinking Current (a, b, c, d, e, f, g, h)                                                                                | V <sub>out</sub> = 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.5                                               | 0.2                            | mA                                                |  |

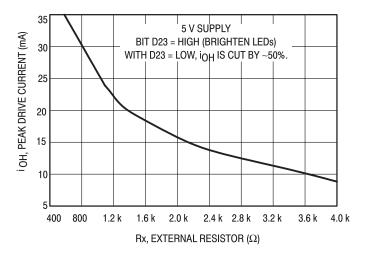

| Peak Sourcing Current — See Figure 7 for currents up to 35 mA (a, b, c, d, e, f, g, h)                                          | $Rx = 2.0 \text{ k}\Omega$ , $V_{Out} = 3.0 \text{ V}$ , Dimmer Bit = High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.0                                               | 13 to 17.5                     | mA                                                |  |

|                                                                                                                                 | $Rx = 2.0 \text{ k}\Omega$ , $V_{out} = 3.0 \text{ V}$ , Dimmer Bit = Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.0                                               | 6 to 9                         |                                                   |  |

| Maximum Output Leakage Current                                                                                                  | V <sub>out</sub> = V <sub>DD</sub> (FET Leakage)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6.0                                               | 50                             | μΑ                                                |  |

| (Bank 1, Bank 2, Bank 3, Bank 4, Bank 5)                                                                                        | $V_{out} = V_{DD}$ (FET Leakage),<br>T <sub>J</sub> = 25°C only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.0                                               | 1                              |                                                   |  |

|                                                                                                                                 | V <sub>out</sub> = V <sub>SS</sub> (Protection Diode<br>Leakage)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6.0                                               | 1                              |                                                   |  |

| Maximum ON Resistance<br>(Bank 1, Bank 2, Bank 3, Bank 4, Bank 5)                                                               | I <sub>out</sub> = 0 to 200 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.0                                               | 10                             | Ω                                                 |  |

| Maximum Quiescent Supply Current                                                                                                | Device in Low–Power Mode,<br>V <sub>in</sub> = V <sub>SS</sub> or V <sub>DD</sub> , Rx in<br>Place, Outputs Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6.0                                               | 100                            | μА                                                |  |

|                                                                                                                                 | Same as Above, T <sub>J</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6.0                                               | 20                             |                                                   |  |

| Maximum RMS Operating Supply Current (The V <sub>SS</sub> leg does not contain the Rx current component. See Pin Descriptions.) | Device NOT in Low–Power<br>Mode, V <sub>in</sub> = V <sub>SS</sub> or V <sub>DD</sub> ,<br>Outputs Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.0                                               | 1.5                            | mA                                                |  |

|                                                                                                                                 | Power Supply Voltage Range of LED Drive Circuitry  Minimum Standby Voltage  Maximum Low-Level Input Voltage (Data In, Clock, Enable)  Minimum High-Level Input Voltage (Data In, Clock, Enable)  Minimum Hysteresis Voltage (Data In, Clock, Enable)  Maximum Low-Level Output Voltage (Data Out)  Minimum High-Level Output Voltage (Data Out)  Minimum Sinking Current (Data In, Clock, Enable)  Minimum Sinking Current (a, b, c, d, e, f, g, h)  Peak Sourcing Current — See Figure 7 for currents up to 35 mA (a, b, c, d, e, f, g, h)  Maximum Output Leakage Current (Bank 1, Bank 2, Bank 3, Bank 4, Bank 5)  Maximum ON Resistance (Bank 1, Bank 2, Bank 3, Bank 4, Bank 5)  Maximum Quiescent Supply Current (The VSS leg does not contain the Rx current component. | Power Supply Voltage Range of LED Drive Circuitry | Parameter   Test Condition   V | Power Supply Voltage Range of LED Drive Circuitry |  |

<sup>\*</sup> See Thermal Considerations section.

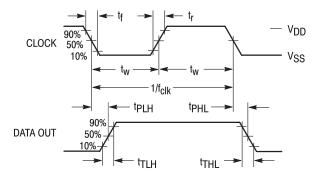

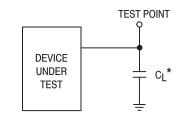

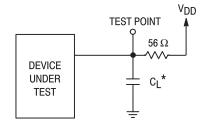

# AC ELECTRICAL CHARACTERISTICS ( $T_J = -40^{\circ}$ to $130^{\circ}C^*$ , $C_L = 50$ pF, Input $t_f = t_f = 10$ ns)

| Symbol                                 | Parameter                                                                                                           | V <sub>DD</sub>   | Guaranteed<br>Limit                 | Unit |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------|------|

| f <sub>Clk</sub>                       | Serial Data Clock Frequency, Single Device or Cascaded Devices NOTE: Refer to Clock t <sub>W</sub> below (Figure 1) | 3.0<br>4.5<br>6.0 | dc to 3.0<br>dc to 4.0<br>dc to 4.0 | MHz  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Maximum Propagation Delay, Clock to Data Out<br>(Figures 1 and 5)                                                   | 3.0<br>4.5<br>6.0 | 140<br>80<br>80                     | ns   |

| t <sub>TLH</sub> ,<br>tTHL             | Maximum Output Transistion Time, Data Out<br>(Figures 1 and 5)                                                      | 3.0<br>4.5<br>6.0 | 70<br>50<br>50                      | ns   |

| fR                                     | Refresh Rate — Bank 1 through Bank 5 (Figures 2 and 6)                                                              | 3.0<br>4.5<br>6.0 | NA<br>700 to 1900<br>700 to 1900    | Hz   |

| C <sub>in</sub>                        | Maximum Input Capacitance — Data In, Clock, Enable                                                                  | _                 | 10                                  | pF   |

<sup>\*</sup> See Thermal Considerations section.

# **TIMING REQUIREMENTS** (T<sub>J</sub> = $-40^{\circ}$ to $130^{\circ}$ C\*, Input t<sub>f</sub> = t<sub>f</sub> = 10 ns unless otherwise indicated)

| Symbol                                                 | Parameter                                                                  | V <sub>DD</sub><br>V | Guaranteed<br>Limit | Unit |

|--------------------------------------------------------|----------------------------------------------------------------------------|----------------------|---------------------|------|

| t <sub>su</sub> , t <sub>h</sub>                       | Minimum Setup and Hold Times, Data In versus Clock (Figure 3)              | 3.0<br>4.5<br>6.0    | 50<br>40<br>40      | ns   |

| t <sub>su</sub> , t <sub>h</sub> ,<br>t <sub>rec</sub> | Minimum Setup, Hold, ** and Recovery Times, Enable versus Clock (Figure 4) | 3.0<br>4.5<br>6.0    | 150<br>100<br>100   | ns   |

| t <sub>W</sub> (L)                                     | Minimum Active–Low Pulse Width, Enable (Figure 4)                          | 3.0<br>4.5<br>6.0    | 4.5<br>3.4<br>3.4   | μs   |

| <sup>t</sup> w(H)                                      | Minimum Inactive–High Pulse Width, Enable (Figure 4)                       | 3.0<br>4.5<br>6.0    | 300<br>150<br>150   | ns   |

| t <sub>W</sub>                                         | Minimum Pulse Width, Clock (Figure 1)                                      | 3.0<br>4.5<br>6.0    | 167<br>125<br>125   | ns   |

| t <sub>r</sub> , t <sub>f</sub>                        | Maximum Input Rise and Fall Times — Data In, Clock, Enable (Figure 1)      | 3.0<br>4.5<br>6.0    | 1<br>1<br>1         | ms   |

<sup>\*</sup> See Thermal Considerations section.

#### NOTES:

- 1. This restriction does NOT apply for  $f_{Clk}$  rates less than those listed above. For "slow"  $f_{Clk}$  rates, use the  $t_h$  limits in the above table.

- 2. This restriction does NOT apply for an access involving more than 8 Clocks. For > 8 Clocks, use the th limits in the above table.

<sup>\*\*</sup> For a high-speed 8-Clock access, th for Enable is determined as follows:

$<sup>\</sup>begin{array}{l} \text{V}_{DD} = 3 \text{ to } 4.5 \text{ V, } f_{Clk} > 1.78 \text{ MHz: } t_h = 4350 - (7500/f_{Clk}) \\ \text{V}_{DD} = 4.5 \text{ to } 6 \text{ V, } f_{Clk} > 2.34 \text{ MHz: } t_h = 3300 - (7500/f_{Clk}) \\ \text{where } t_h \text{ is in ns and } f_{Clk} \text{ is in MHz.} \end{array}$

Figure 1.

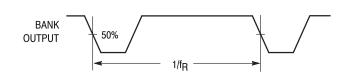

Figure 2.

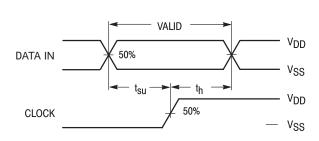

Figure 3.

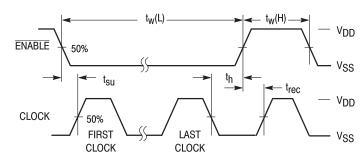

Figure 4.

\*Includes all probe and fixture capacitance.

Figure 5.

<sup>\*</sup>Includes all probe and fixture capacitance.

Figure 6.

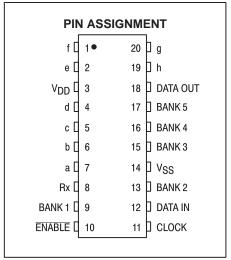

#### PIN DESCRIPTIONS

#### **DIGITAL INTERFACE**

#### Data In (Pin 12)

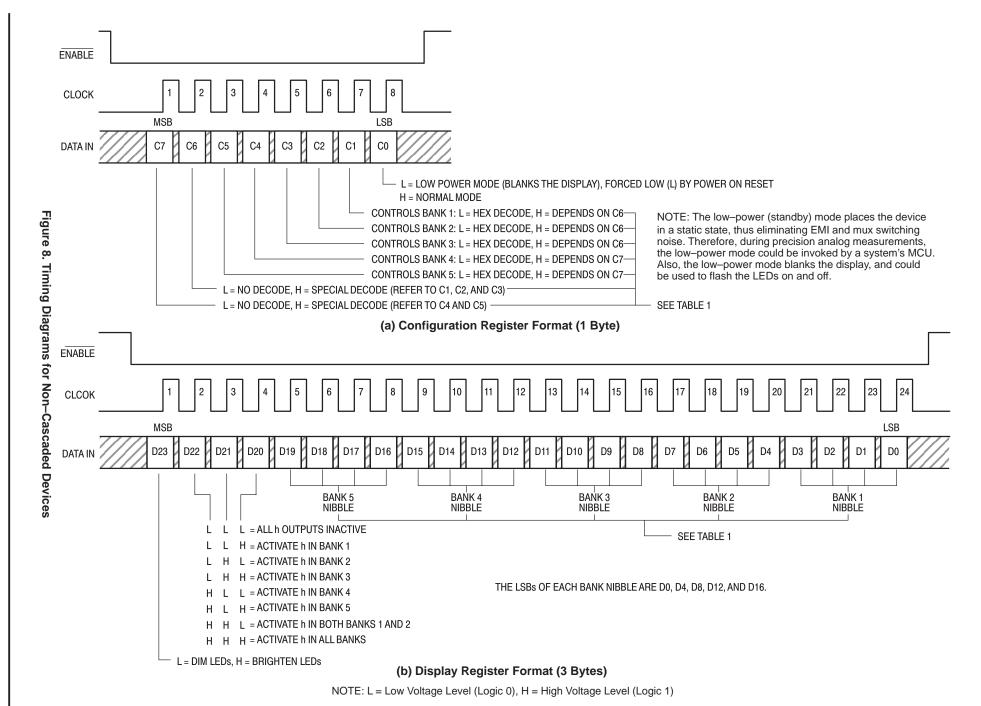

Serial Data Input. The bit stream begins with the MSB and is shifted in on the low–to–high transition of Clock. When the device is not cascaded, the bit pattern is either 1 byte (8 bits) long to change the configuration register or 3 bytes (24 bits) long to update the display register. For two chips cascaded, the pattern is either 4 or 6 bytes, respectively. The display does not change during shifting (until Enable makes a low–to–high transition) which allows slow serial data rates, if desired

The bit stream needs neither address nor steering bits due to the innovative BitGrabber registers. Therefore, all bits in the stream are available to be data for the two registers. Random access of either register is provided. That is, the registers may be accessed in any sequence. Data is retained in the registers over a supply range of 3 to 6 V. Formats are shown in Figures 8 through 14 and summarized in Table 2. Information on the segment decoder is given in Table 1.

Data In typically switches near 50% of V<sub>DD</sub> and has a Schmitt–triggered input buffer. These features combine to maximize noise immunity for use in harsh environments and bus applications. This input can be directly interfaced to CMOS devices with outputs guaranteed to switch near rail–to–rail. When interfacing to NMOS or TTL devices, either a level shifter (MC14504B, MC74HCT04A) or pullup resistor of 1 k $\Omega$  to 10 k $\Omega$  must be used. Parameters to be considered when sizing the resistor are the worst–case  $I_{OL}$  of the driving device, maximum tolerable power consumption, and maximum data rate.

# Clock (Pin 11)

Serial Data Clock Input. Low-to-high transitions on Clock shift bits available at Data In, while high-to-low transitions shift bits from Data Out. The chip's 24–1/2–stage shift register is static, allowing clock rates down to dc in a continuous or intermittent mode. The Clock input does not need to be synchronous with the on-chip clock oscillator which drives the multiplexing circuit.

Eight clock cycles are required to access the configuration register, while 24 are needed for the display register when the MC14489 is not cascaded. See Figures 8 and 9.

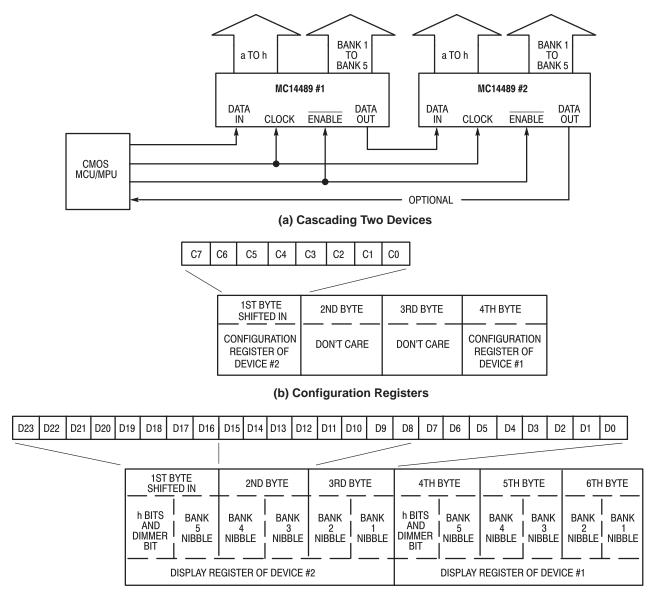

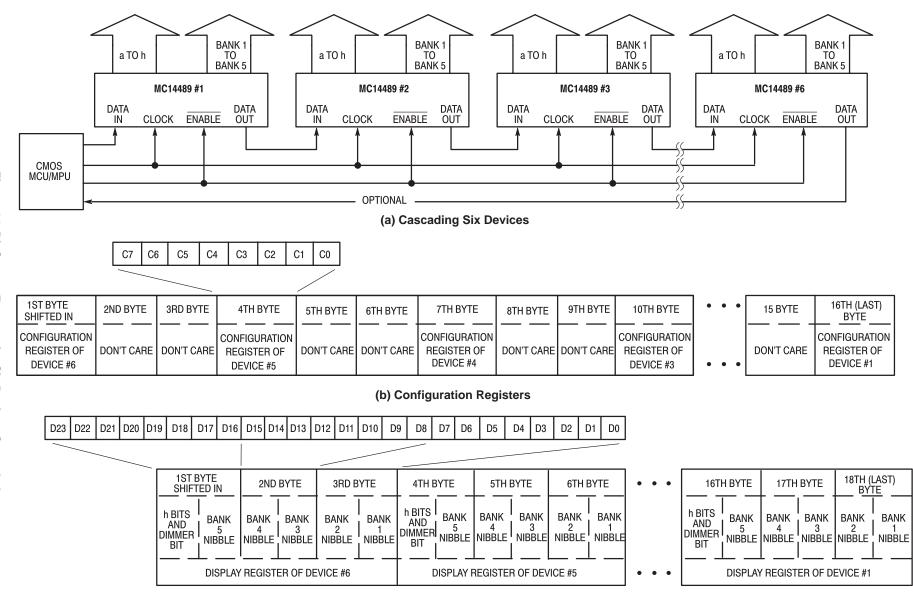

As shown in Figure 10, two devices may be cascaded. In this case, 32 clock cycles access the configuration register and 48 access the display register, as depicted in Figure 10.

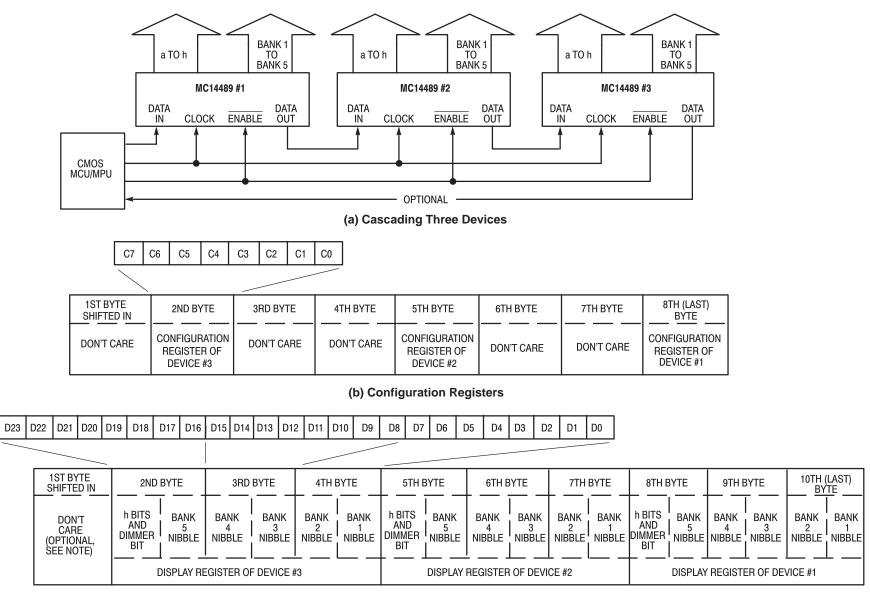

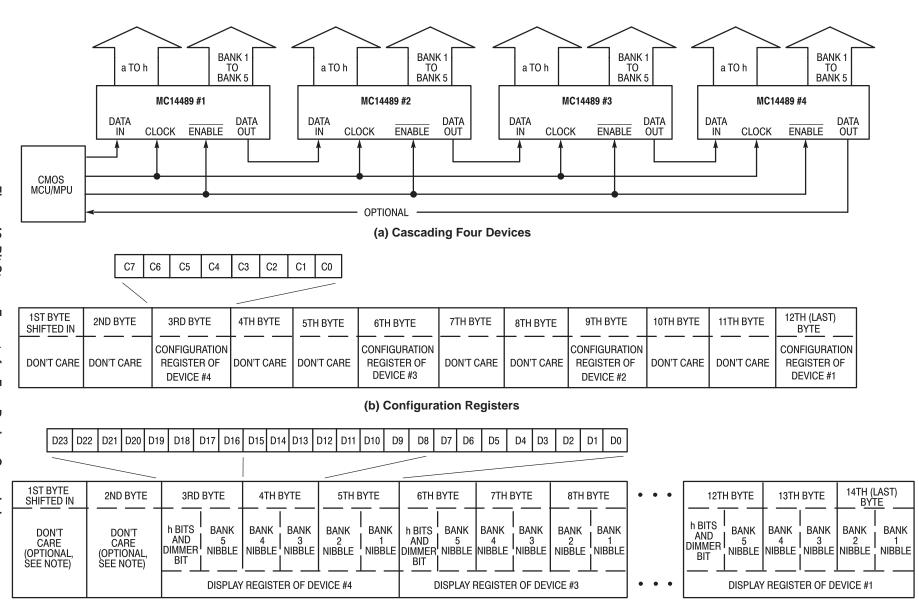

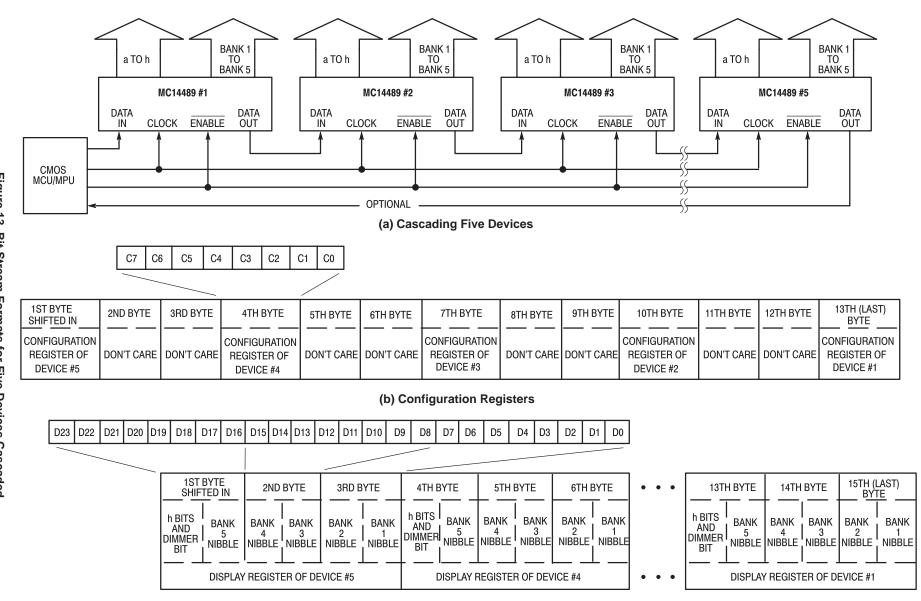

Cascading of 3, 4, 5, and 6 devices is shown in Figures 11, 12, 13, and 14, respectively. Also, reference Table 2.

Clock typically switches near 50% of  $V_{DD}$  and has a Schmitt-triggered input buffer. Slow Clock rise and fall times are tolerated. See the last paragraph of **Data In** for more information.

#### NOTE

To guarantee proper operation of the power–on reset (POR) circuit, the Clock pin must NOT be floated or toggled during power–up. That is, the Clock pin must be stable until the  $V_{DD}$  pin reaches at least 3 V.

If control of the Clock pin during power—up is not practical, then the MC14489 must be reset via bit C0 in the C register. To accomplish this, C0 is reset low, then set high.

#### Enable (Pin 10)

Active—Low Enable Input. This pin allows the MC14489 to be used on a serial bus, sharing Data In and Clock with other peripherals. When Enable is in an inactive high state, Data Out is forced to a known (low) state, shifting is inhibited, and the port is held in the initialized state. To transfer data to the device, Enable (which initially must be inactive high) is taken low, a serial transfer is made via Data In and Clock, and Enable is taken high. The low—to—high transition on Enable transfers data to either the configuration or display register, depending on the data stream length.

Every rising edge on Enable initiates a blanking interval while data is loaded. Thus, continually loading the device with the same data may cause the LEDs on some banks to appear dimmer than others.

#### **NOTE**

Transitions on Enable must not be attempted while Clock is high. This puts the device out of synchronization with the microcontroller. Resynchronization occurs when Enable is high and Clock is low.

This input is also Schmitt–triggered and switches near 50% of  $V_{DD}$ , thereby minimizing the chance of loading erroneous data in the registers. See the last paragraph of **Data In** for more information.

## Data Out (Pin 18)

Serial Data Output. Data is transferred out of the shift register through Data Out on the high–to–low transition of Clock. This output is a no connect, unless used in one of the manners discussed below.

When cascading MC14489's, Data Out feeds Data In of the next device per Figures 10, 11, 12, 13, and 14.

Data Out could be fed back to an MCU/MPU to perform a wrap—around test of serial data. This could be part of a system check conducted at power—up to test the integrity of the system's processor, pc board traces, solder joints, etc.

The pin could be monitored at an in-line Q.A. test during board manufacturing.

Finally, Data Out facilitates troubleshooting a system.

## **DISPLAY INTERFACE**

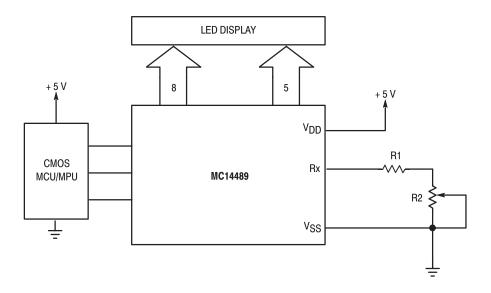

# Rx (Pin 8)

External Current–Setting Resistor. A resistor tied between this pin and ground (VSS) determines the peak segment drive current delivered at pins a through h. Pin 8's resistor ties into a current mirror with an approximate current gain of 10 when bit D23 = high (brighten). With D23 = low, the peak current is reduced about 50%. Values for Rx range from 700  $\Omega$  to infinity. When Rx =  $\infty$  (open circuit), the display is extinguished. For proper current control, resistors having  $\pm$  1% tolerance should be used. See Figure 7.

#### **CAUTION**

Small Rx values may cause the chip to overheat if precautions are not observed. See **Thermal Considerations.**

#### a through h (Pins 1, 2, 4 - 7, 19, 20)

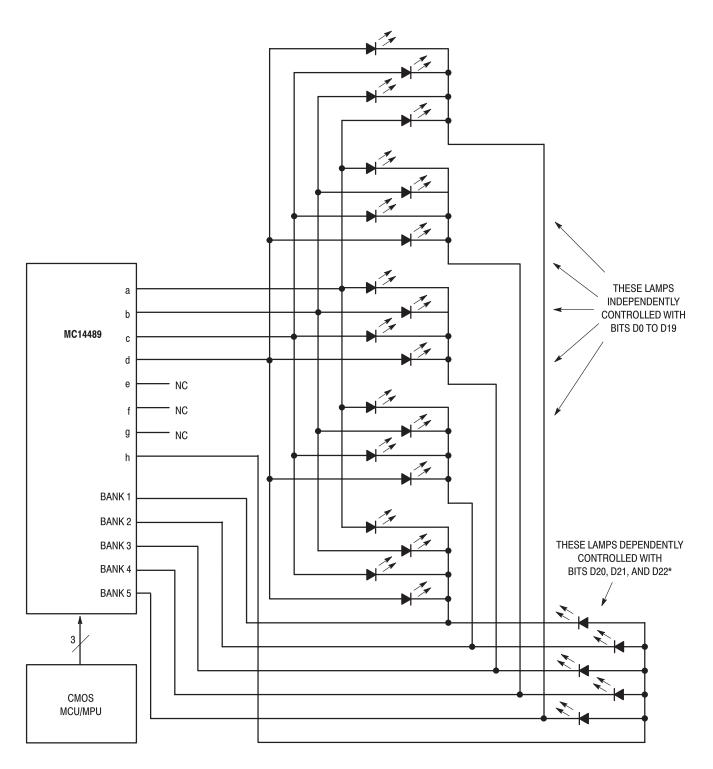

Anode—Driver Current Sources. These outputs are closely-matched current sources which directly tie to the anodes of external discrete LEDs (lamps) or display segment LEDs. Each output is capable of sourcing up to 35 mA.

When used with lamps, outputs a, b, c, and d are used to independently control up to 20 lamps. Output h is used to control up to 5 lamps dependently. (See Figure 17.) For lamps, the *No Decode* mode is selected via the configuration register, forcing e, f, and g inactive (low).

When used with segmented displays, outputs a through g drive segments a through g, respectively. Output h is used to drive the decimals. Refer to Figure 9. If unused, h must be left open.

#### Bank 1 through Bank 5 (Pins 9, 13, 15, 16, 17)

Diode—Bank FET Switches. These outputs are low—resistance switches to ground (VSS) capable of handling currents of up to 320 mA each. These pins directly tie to the common cathodes of segmented displays or the cathodes of lamps (wired with cathodes common).

The display is refreshed at a nominal 1 kHz rate to achieve optimum brightness from the LEDs. A 20% duty cycle is utilized.

Special design techniques are used on—chip to accommodate the high currents with low EMI (electromagnetic interference) and minimal spiking on the power lines.

#### **POWER SUPPLY**

# VSS (Pin 14)

Most–negative supply potential. This pin is usually ground. Resistor Rx is externally tied to ground (VSS). Therefore, the chip's VSS pin does not contain the Rx current component.

#### **VDD (Pin 13)**

Most-positive supply potential.

To guarantee data integrity in the registers and to ensure the serial interface is functional, this voltage may range from 3 to 6 volts with respect to VSS. For example, within this voltage range, the chip could be placed in and out of the low-power mode.

To adequately drive the LEDs, this voltage must be 4.5 to 6 volts with respect to VSS.

The V<sub>DD</sub> pin contains the Rx current component plus the chip's current drain. In the low–power mode, the current mirror and clock oscillator are turned off, thus significantly reducing the V<sub>DD</sub> current, I<sub>DD</sub>.

NOTE: Drive current tolerance is approximately  $\pm$  15%.

Figure 7. a through h Nominal Current per Output versus Rx

**Table 1. Triple-Mode Segment Decoder Function Table**

|                   |                   |                                              |                                                     | Lamp Conditions                               |    |    | s  |

|-------------------|-------------------|----------------------------------------------|-----------------------------------------------------|-----------------------------------------------|----|----|----|

| Bank Nibble Value |                   | 7–Segment Display<br>Characters              |                                                     | No Decode 1<br>(Invoked via<br>Bits C1 to C7) |    |    | D  |

| Hexadecimal       | Binary<br>MSB LSB | Hex Decode<br>(Invoked via<br>Bits C1 to C5) | Special<br>Decode<br>(Invoked via<br>Bits C1 to C7) | d                                             | С  | b  | а  |

| \$0               | LLLL              | 0                                            |                                                     |                                               |    |    |    |

| \$1               | LLLH              | /                                            | C                                                   |                                               |    |    | on |

| \$2               | LLHL              | 2<br>3                                       | H                                                   |                                               |    | on |    |

| \$3               | LLHH              | 3                                            | h                                                   |                                               |    | on | on |

| \$4               | LHLL              | 4                                            | J                                                   |                                               | on |    |    |

| \$5               | LHLH              | 5 ②                                          | L                                                   |                                               | on |    | on |

| \$6               | LHHL              | 8                                            | n                                                   |                                               | on | on |    |

| \$7               | L Н Н Н           | 7                                            | o <sub>.</sub>                                      |                                               | on | on | on |

| \$8               | HLLL              | 83                                           | Р                                                   | on                                            |    |    |    |

| \$9               | HLLH              | 3 4                                          | r                                                   | on                                            |    |    | on |

| \$A               | HLHL              | 8                                            | U                                                   | on                                            |    | on |    |

| \$B               | ньнн              | Ь                                            | u                                                   | on                                            |    | on | on |

| \$C               | HHLL              | Ε                                            | У                                                   | on                                            | on |    |    |

| \$D               | нньн              | ರ                                            | -                                                   | on                                            | on |    | on |

| \$E               | нннь              | E<br>F                                       | =                                                   | on                                            | on | on |    |

| \$F               | нннн              | F                                            | 0                                                   | on                                            | on | on | on |

# NOTES:

- 1. In the *No Decode* mode, outputs e, f, and g are unused and are all forced inactive (low). Output h decoding is unaffected, i.e., unchanged from the other modes. The *No Decode* mode is used for three purposes:

- a. Individually controlling lamps.

- b. Controlling a half digit with sign.

- c. Controlling annunciators examples: AM, PM, UHF, kV, mm Hg.

- 2. Can be used as capital S.

- 3. Can be used as capital B.

- 4. Can be used as small g.

MC14489 MOTOROLA

# **APPLICATIONS INFORMATION**

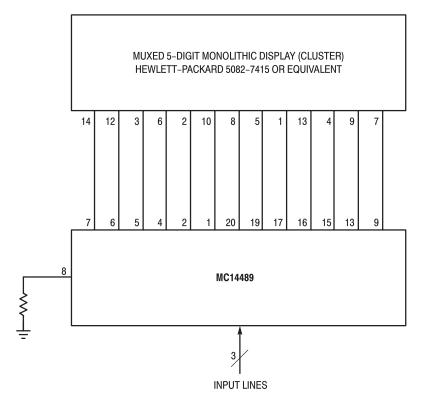

Figure 9. Non-Cascaded Application Example: 5 Character Common Cathode LED Display with Two Intensities as Controlled via Serial Port

MC14489 10

(c) Display Registers

NOTE: ENABLE (which initially must be inactive high) is kept active—low during the entire 4—byte configuration transfer or 6—byte display transfer.

When ENABLE is brought back high, either a 4— or 6—byte transfer occurs in the cascaded devices, depending on the number of bytes in the transfer.

#### (c) Display Registers

NOTE: When the leading "don't care" bytes are included, ENABLE (which initially must be inactive high) is kept active—low during the entire 8—byte configuration transfer or 10—byte display transfer. When ENABLE is brought back high, either an 8— or 10—byte transfer occurs in the cascaded devices. Alternatively, when updating the display registers, the one "don't care" byte can be eliminated as follows: (1) take ENABLE active low, (2) transfer 6 bytes, (3) pulse ENABLE inactive high, see t (4) transfer last 3 bytes, and (5) take ENABLE inactive high.

#### (c) Display Registers

NOTE: When the leading "don't care" bytes are included, ENABLE (which initially must be inactive high) is kept active—low during the entire 12—byte configuration transfer or 14—byte display transfer.

When ENABLE is brought back high, either a 12— or 14—byte transfer occurs in the cascaded devices. Alternatively, when updating the display registers, the two "don't care" bytes can be eliminated as follows: (1) take ENABLE active low, (2) transfer 6 bytes, (3) pulse ENABLE inactive high, see tw(H) spec, (4) transfer last 6 bytes, and (5) take ENABLE inactive high.

#### (c) Display Registers

NOTE: ENABLE (which initially must be inactive high) is kept active—low during the entire 13—byte configuration transfer or 15—byte display transfer. When ENABLE is brought back high, either a 13— or 15—byte transfer occurs in the cascaded devices, depending on the number of bytes in the transfer.

(c) Display Registers

NOTE: ENABLE (which initially must be inactive high) is kept active—low during the entire 16—byte configuration transfer or 18—byte display transfer. When ENABLE is brought back high, either a 16— or 18—byte transfer occurs in the cascaded devices, depending on the number of bytes in the transfer.

Table 2. Register Access for Two or More Cascaded Devices

|                              | Configuration F       | Register Access                         | Display Register Access |                                         |  |

|------------------------------|-----------------------|-----------------------------------------|-------------------------|-----------------------------------------|--|

| Criteria*                    | Total Number of Bytes | Number of Leading<br>"Don't Care" Bytes | Total Number of Bytes   | Number of Leading<br>"Don't Care" Bytes |  |

| If 3N is a Multiple of 4     | 3N                    | 2                                       | 3N + 2                  | 2                                       |  |

| If 3N – 1 is a Multiple of 4 | 3N – 1                | 1                                       | 3N + 1                  | 1                                       |  |

| If 3N – 2 is a Multiple of 4 | 3N – 2                | 0                                       | 3N                      | 0                                       |  |

| If 3N – 3 is a Multiple of 4 | 3N – 2                | 0                                       | 3N                      | 0                                       |  |

<sup>\*</sup> N = number of devices that are cascaded. For example, to drive 10 digits, 2 devices are cascaded; therefore, N = 2. To drive 35 digits, seven devices are cascaded; therefore N = 7.

NOTE: R1 limits the maximum current to avoid damaging the display and/or the MC14489 due to overheating. See the Thermal Considerations section. An 1/8 watt resistor may be used for R1. R2 is a 1 k $\Omega$  or 5 k $\Omega$  potentiometer ( $\geq$  1/8 watt). R2 may be a light–sensitive resistor.

Figure 15. Common-Cathode LED Display with Dial-Adjusted Brightness

NOTE: A Universal Overflow pins out all anodes and cathodes.

Figure 16. Driving 5 1/2 Digits

<sup>\*</sup> If required, this group of lamps can be independently controlled. To accomplish independent control, only connect lamps to BANK 1 and BANK 2 for output h (two lamps). Then, use bits D20, D21, and D22 for control of these two lamps.

Figure 17. 25-Lamp Application

Figure 18. 4-Digit Display Plus Decimals with Four Annunciators or 4-1/2-Digit Display Plus Sign

Figure 19. Compact Display System with Three Components

# THERMAL CONSIDERATIONS

The MC14489 is designed to operate with a *chip–junction* temperature (T<sub>J</sub>) ranging from – 40 to 130°C, as indicated in the electrical characteristics tables. The *ambient* operating temperature range (T<sub>A</sub>) is dependent on R<sub>θ</sub>J<sub>A</sub>, the internal chip current, how many anode drivers are used, the number of bank drivers used, the drive current, and how the package is cooled. The maximum ratings table gives the thermal resistance, junction–to–ambient, of the MC14489 mounted on a pc board using natural convection to be 90°C per watt for the plastic DIP. The SOG thermal resistance is 100°C per watt.

The following general equation (1) is used to determine the power dissipated by the MC14489.

$$PT = PD + PI \tag{1}$$

where

PT = Total power dissipation of the MC14489

P<sub>D</sub> = Power dissipated in the driver circuitry (mW)

$P_I = Power dissipated by the internal chip$

circuitry (mW)

The equations for the two terms of the general equation are:

$$P_D = (i_{OH}) (N)(V_{DD} - V_{LED})(B/5)$$

(2)

$$P_{I} = (1.5 \text{ mA})(V_{DD}) + I_{Rx}(V_{DD} - I_{Rx}Rx)$$

(3)

where

iOH = Peak anode driver current (mA)

$I_{RX} = i_{OH}/10$ , with  $i_{OH} =$  the peak anode driver current (mA) when the dimmer bit is high

N = Number of anode drivers used

B = Number of bank drivers used

$Rx = External resistor value (k\Omega)$

V<sub>DD</sub> = Maximum supply voltage, referenced to V<sub>SS</sub>

V<sub>LED</sub> = Minimum anticipated voltage drop across the

LED

1.5 mA = Operating supply current of the MC14489

The following two examples show how to calculate the maximum allowable ambient temperature.

#### Worst-Case Analysis Example 1:

5–digit display with decimals (5 banks and 8 anode drivers) DIP without heat sink on PC board

iOH = 20 mA max

$V_{LED} = 1.8 V min$

$V_{DD} = 5.25 \, \text{max}$

$$P_D = (20)(8)(5.25 - 1.8)(5/5) = 552 \text{ mW}$$

Ref. (2)

$$P_1 = (1.5)(5.25) + 2[5.25 - 2(2)] = 10 \text{ mW}$$

Ref. (3)

Therefore,

$$P_T = 552 + 10 = 562 \text{ mW}$$

Ref. (1)

and  $\Delta T_{chip} = R_{\theta JA}P_{T} = (90^{\circ}C/W)(0.562) = 51^{\circ}C$

Finally, the maximum allowable

$$T_A = T_J max - \Delta T_{chip} = 130 - 51 = 79^{\circ}C$$

That is, if  $T_A = 79^{\circ}C$ , the maximum junction temperature is 130°C. The chip's average temperature for this example is lower than 130°C because all segments are usually not illuminated simultaneously for an indefinite period.

#### Worst-Case Analysis Example 2:

16 lamps (4 banks and 4 anode drivers) SOG without heat sink on PC board

iOH = 30 mA max

$V_{LED} = 1.8 V min$

$V_{DD} = 5.5 \text{ max}$

$$P_D = (30)(4)(5.5 - 1.8)(4/5) = 355 \text{ mW}$$

Ref. (2)

$$P_I = (1.5)(5.5) + 3[5.5 - 3(1.0)] = 16 \text{ mW}$$

Ref. (3)

Therefore,

$$P_T = 355 + 16 = 371 \text{ mW}$$

Ref. (1)

and

$$\Delta T_{chip} = R_{\theta}JAPT = (100^{\circ}C/W)(0.371) = 37^{\circ}C$$

Finally, the maximum allowable

$$T_A = T_J max - \Delta T_{chip} = 130 - 37 = 93^{\circ}C$$

To extend the allowable ambient temperature range or to reduce TJ, which extends chip life, a heat sink such as shown in Figure 20 can be used in high–current applications. Alternatively, heat–spreader techniques can be used on the PC board, such as running a wide trace under the MC14489 and using thermal paste. Wide, radial traces from the MC14489 leads also act as heat spreaders.

AAVID #5804 or equivalent

(Tel. 603/524-4443, FAX 603/528-1478)

Motorola cannot recommend one supplier over another and in no way suggests that this is the only heat sink supplier.

Figure 20. Heat Sink

Table 3. LED Lamp and Common–Cathode Display

Manufacturers

| marraraotaro.                                                  |  |  |  |  |

|----------------------------------------------------------------|--|--|--|--|

| Supplier                                                       |  |  |  |  |

| QT Optoelectronics                                             |  |  |  |  |

| Hewlett-Packard (HP), Components Group                         |  |  |  |  |

| Industrial Electronic Engineers (IEE), Component Products Div. |  |  |  |  |

| Purdy Electronics Corp., AND Product Line                      |  |  |  |  |

NOTE: Motorola cannot recommend one supplier over another and in no way suggests that this is a complete listing of LED suppliers.

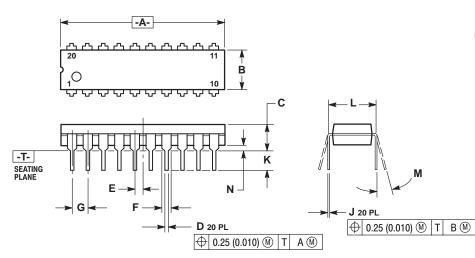

# **PACKAGE DIMENSIONS**

#### **P SUFFIX PLASTIC DIP** CASE 738-03

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH.

- DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.

DIMENSION B DOES NOT INCLUDE MOLD

- FLASH.

|     | INC            | HES   | MILLIN   | IETERS |

|-----|----------------|-------|----------|--------|

| DIM | MIN            | MAX   | MIN      | MAX    |

| Α   | 1.010          | 1.070 | 25.66    | 27.17  |

| В   | 0.240          | 0.260 | 6.10     | 6.60   |

| С   | 0.150          | 0.180 | 3.81     | 4.57   |

| D   | 0.015          | 0.022 | 0.39     | 0.55   |

| E   | 0.050 BSC      |       | 1.27 BSC |        |

| F   | 0.050          | 0.070 | 1.27     | 1.77   |

| G   | 0.100 BSC      |       | 2.54     | BSC    |

| J   | 0.008          | 0.015 | 0.21     | 0.38   |

| K   | 0.110          | 0.140 | 2.80     | 3.55   |

| L   | 0.300 BSC 7.62 |       | 7.62     | BSC    |

| M   | 0°             | 15°   | 0°       | 15°    |

| N   | 0.020          | 0.040 | 0.51     | 1.01   |

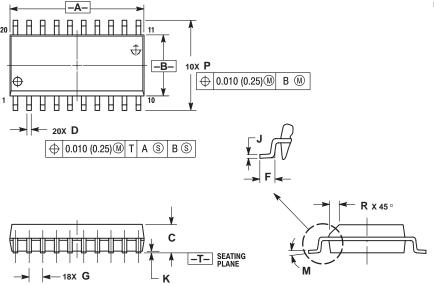

## **DW SUFFIX SOG PACKAGE** CASE 751D-04

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.150 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN   | METERS | INCHES    |       |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 12.65    | 12.95  | 0.499     | 0.510 |

| В   | 7.40     | 7.60   | 0.292     | 0.299 |

| С   | 2.35     | 2.65   | 0.093     | 0.104 |

| D   | 0.35     | 0.49   | 0.014     | 0.019 |

| F   | 0.50     | 0.90   | 0.020     | 0.035 |

| G   | 1.27 BSC |        | 0.050 BSC |       |

| J   | 0.25     | 0.32   | 0.010     | 0.012 |

| K   | 0.10     | 0.25   | 0.004     | 0.009 |

| M   | 0 °      | 7 °    | 0 °       | 7 °   |

| P   | 10.05    | 10.55  | 0.395     | 0.415 |

| R   | 0.25     | 0.75   | 0.010     | 0.029 |

This page intentionally left blank.

MC14489 MOTOROLA

This page intentionally left blank.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Mfax is a trademark of Motorola, Inc.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; JAPAN: Nippon Motorola Ltd.; SPD, Strategic Planning Office, 141, P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan. 81–3–5487–8488

Customer Focus Center: 1-800-521-6274

Mfax™: RMFAX0@email.sps.mot.com - TOUCHTONE 1-602-244-6609

Motorola Fax Back System - US & Canada ONLY 1-800-774-1848 - http://sps.motorola.com/mfax/

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298 - http://sps.motorola.com/mfax/

HOME PAGE: http://motorola.com/sps/

MC14489/D