# MC141622EVK

# **ACF-II Evaluation Board Operating Manual**

#### 1. SUMMARY

The MC141622EVK is a development board for evaluation of the MC141622. In addition to the MC141622, the MC141622EVK contains all the analog circuit that is necessary for buffering both the input and output video signal and generation of the 4xfsc clock. By connecting an external signal source, monitor, and power supply, it is possible to evaluate all the operating modes on the MC141622.

#### 2. SPECIFICATION

Board Dimensions 100 mm (Length) x 150 mm (Width)

Y/C Separation LSI MC141622FU Mount

Video Input Amplifier MC14577 2SC2002 Use

Video Output Amplifier MC14576 Use

Clamp Circuit 2SC2002 2SA953 Use

Clock Generator MC1378P Use Clock Buffer Amplifier MC14576 Use

Analog Input/Output Interface BNC Connector x3, S Terminal Output Mount

Digital Input/Output Interface 16 Pin Header Mount

Action Mode MC141622 Supports All Operating Modes

Regulator MC7805CT Use

Recommended Supply Voltage + 10 V

Operating Temperature 0 to 50°C

Supply Current 350 mA

#### 3. BOARD OPERATION

## 3.1 ACF-II Operating Mode

AFC-II has four operating modes. Any one of these modes can be selected using the digital code input to MODE 0 and MODE 1 using ROTARY SW. The function of each mode is as follows.

## (1) Normal fsc Mode

This is the mode for usual Y/C separation. It separates Y/C from the video signal that is input to the A/D converter.

The coring parameter of the vertical enhancer can be set up by the digital code that is input to C0 - C3 (block level parameter), C4 - C7 (white level parameter), and D4 - D7 (noise slice level parameter).

The clock is a 3.579545 MHz subcarrier input to the CLK connector; the built–in 4x PLL generates 4xfsc clock.

## (2) Normal 4xfsc Mode

This mode is used for Y/C separation. It separates Y/C from the video signal that is input to the A/D converter.

The coring parameter of the vertical enhancer can be set up by the digital code that is input to C0 - C3 (block level parameter), C4 - C7 (white level parameter), and D4 - D7 (noise slice level parameter).

The clock is 14.31818 MHz which is a 4x subcarrier input to the CLK connector.

## (3) Digital Input Comb Filter Mode

This mode uses the A/D converter, filter, and D/A converter as two independent blocks. The digital data converted by the A/D converter is output on CO - C7. Data input on DO - D7 is processed by the ACF–II. Filtering is performed by the algorithm of ACF–II and the Y/C video is output as analog signals from  $Y_{Out}$  and  $Y_{Out}$ . These two blocks can operate with input clock signals that have different frequencies or phases and can be operated independently by using the CLK(AD) for the A/D converter, and the CLK input for the D/A converter.

The clock is 14.31818 MHz which is a 4x subcarrier input to the CLK connector and the CLK(AD) connector.

## (4) Digital Output Comb Filter Mode

In addition to the normal Y/C analog outputs, the MC141622EVK can provide the Y/C signals as digital luminance and chrominance signals. The digital luminance data is output on C0 - C7 and the digital chrominance data is output on D0 - D7. This digital data can be modified by other digital processing.

MC141622EVK MOTOROLA

The following table is the assignment for the operating mode.

**MODE Switching Function**

| Mode                               | MODE1 | MODE0 | Rotary SW |

|------------------------------------|-------|-------|-----------|

| Normal fsc Mode                    | L     | L     | 0         |

| Normal 4xfsc Mode                  | L     | Н     | 1         |

| Digital Input Comb Filtering Mode  | Н     | L     | 2         |

| Digital Output Comb Filtering Mode | Н     | Н     | 3         |

#### 4. BK FUNCTION

By setting the BK pin (toggle SW1) to the H level, composite video is output on the Yout pin and the chrominance signal on the Cout pin.

The following table is the function of the BK pin.

**BK Function**

| BK Pin | Y <sub>out</sub> Pin | C <sub>out</sub> Pin |  |

|--------|----------------------|----------------------|--|

| L      | Luminance            | Chrominance          |  |

| Н      | Composite            | Chrominance          |  |

#### 4.1 Vertical Enhancer Function

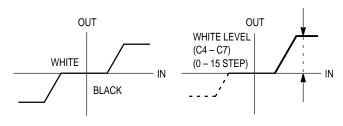

By setting the VH pin (toggle SW2) to the L level, the vertical enhancer feature is enabled. The coring parameter of the vertical enhancer can be set up every 1 LSB by the digital code that are input to C0 - C3 (black level parameter), C4 - C7 (white level parameter), and D4 - D7 (noise slice level parameter.

The set up level of the coring parameter and characteristics are as follows.

**Coring Characteristics**

#### **Vertical Enhancer Function**

| VH Pin | Vertical Enhancer |  |

|--------|-------------------|--|

| L      | On                |  |

| Н      | Off               |  |

## **Coring Parameter Set Up**

| C7         C6         C5         C4           C3         C2         C1         C0           D7         D6         D5         D4           L         L         L         L           L         L         L         0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7         D6         D5         D4           L         L         L         L         0                                                                                                                             |

| L L L L O                                                                                                                                                                                                           |

|                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                     |

| L L L H 1<br>L L H L 2                                                                                                                                                                                              |

| L L H H 3                                                                                                                                                                                                           |

| L H L L 4                                                                                                                                                                                                           |

| L   H   L   H   5                                                                                                                                                                                                   |

| L                                                                                                                                                                                                                   |

| L H H H H 7                                                                                                                                                                                                         |

| H L L L 8                                                                                                                                                                                                           |

| H   L   L   H   9                                                                                                                                                                                                   |

| H                                                                                                                                                                                                                   |

| H                                                                                                                                                                                                                   |

| H H L L C                                                                                                                                                                                                           |

| H                                                                                                                                                                                                                   |

| H                                                                                                                                                                                                                   |

| H H H H F                                                                                                                                                                                                           |

MOTOROLA MC141622EVK

## 4.2 Clock Generator Compounding

The clock generator (MC1378P) provides the necessary reference oscillator and phase locks the clock to the color subcarrier by inputting the composite video signal.

VC1 adjusts the horizontal VCO to synchronize the output of the burst gate (pin 5 on the MC1378P) with the input video signal. VC2 adjusts the chroma VCO for maximum amplitude output from the clock buffer (pin 1 on the MC14576).

VR3 adjusts pull—in of the chroma PLL filter. This is usually fixed to the center position. VR4 selects the dc bias for the clock buffer output and is usually 2.25 V.

## 4.3 Video Amplifier Adjustment

On the video amplifier (MC14577), the gain is adjusted by VR1. This sets the input range (3.0 Vp-p) of the A/D converter in MC141622FU.

VR2 is the clamp level adjustment. This adjusts the sync tip clamping of the input video signal to the video amplifier.

#### 4.4 Outside Interface

The outside interface should provide a composite video input signal to BNC1. The MC141622EVK provides Y/C separation and outputs the luminance from BNC2 and the color signal from BNC3. There is an S output connector on this board for easy connection to instruments having an S input connector.

BNC4 and BNC5 are for the external input of each CLK and CLK(AD). However, when using these, it is necessary to modify the board pattern; i.e., cut (J5, J6).

There is no filter for bandwidth limitations on this board beyond that imposed by the bandwidth limitations of the MC14577 buffer amplifier. To minimize noise resulting from excessive bandwidth, the bandwidth of input video signal should be limited to no more than one half of the clock frequency.

MC141622EVK MOTOROLA

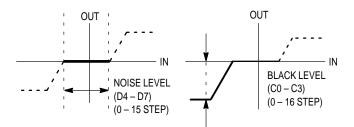

#### 5. MC141622EVK CIRCUIT

**MOTOROLA** MC141622EVK

## 6. MC141622EVK PARTS LIST

| Reference        |                                                          | Reference       |                 |

|------------------|----------------------------------------------------------|-----------------|-----------------|

| Designation      | Description                                              | Designation     | Description     |

| IC1              | MC141622FU                                               | C1              | 0.1 μF          |

| IC2              | MC14576CP                                                | C2, C3          | 47 μF           |

| IC3              | MC14577CP                                                | C4, C5, C6      | 0.1 μF          |

| IC4              | MC7805CT                                                 | C7              | 47 μF           |

| IC5              | MC14576CP                                                | C8              | 47 μι<br>0.1 μF |

| IC6              | MC1378P                                                  | C9              | 0.1 μF          |

| TR1              | 2SC2002                                                  | C10             | 0.1 μF          |

| TR2              | 2SC2002                                                  | C10             | 0.1 μF          |

| TR3              | 2SA953                                                   | C12             | 0.33 μF         |

| R1               | 9.1 kΩ                                                   | C12             | ·               |

| R2               | 62 kΩ                                                    | C13<br>C14, C15 | 1.0 μF          |

| R3, R4           | 75 Ω                                                     |                 | 0.1 μF          |

| R5               | $3.6~\mathrm{k}\Omega$                                   | C16             | 47 μF           |

| R6               | 750 kΩ                                                   | C17             | 0.1 μF          |

| R7, R8           | 2.0 kΩ                                                   | C18             | 1.0 μF          |

| R9               | 510 Ω                                                    | C19             | 47 μF           |

| R10              | 150 Ω                                                    | C20, C21        | 0.1 μF          |

| R11              | 510 kΩ                                                   | C22             | 47 μF           |

| R12, R13         | 2.2 kΩ                                                   | C23             | 0.1 μF          |

| R14              | 47 kΩ x 4                                                | C24             | 47 μF           |

| R15              | 47 kΩ x 8                                                | C25             | 0.1 μF          |

| R16              | 10 kΩ x 8                                                | C26             | 47 μF           |

| R17              | 47 kΩ x 8                                                | C27             | 10 μF           |

| R18              | 10 kΩ x 8                                                | C28             | 0.1 μF          |

| R19, R20         | 10 kΩ x 4                                                | C29, C30        | 47 μF           |

| R21              | 200 Ω                                                    | C31             | 0.1 μF          |

| R22              | 1.8 kΩ                                                   | C32             | 0.022 μF        |

| R23              | 680 Ω                                                    | C33, C34        | 1.0 μF          |

| R24<br>R25       | 750 kΩ                                                   | C35             | 0.1 μF          |

| R26              | $2.2 \text{ k}\Omega$ $7.5 \text{ m}\Omega$              | C36             | 0.001 μF        |

| R27              | 1.0 mΩ                                                   | C37             | 47 μF           |

| R28              | 150 Ω                                                    | C38 - C45       | 0.1 μF          |

| R29              | 470 kΩ                                                   | C46             | 1.0 μF          |

|                  |                                                          | C47, C48        | 0.1 μF          |

| L1 – L9          | 33 μH                                                    | C49 - C51       | 1.0 μF          |

| L10              | 4.7 μH                                                   | C52             | 0.1 μF          |

| L11              | 33 μΗ                                                    | C53             | 47 μF           |

| VR1              | 1 kΩ                                                     | C54             | 0.047 μF        |

| VR2              | 2.2 kΩ                                                   | C55 - C57       | 0.1 μF          |

| VR3              | 1 kΩ                                                     |                 |                 |

| VR4              | 1 m $\Omega$                                             |                 |                 |

| VC1, VC2         | 30 pF                                                    |                 |                 |

| SW1, SW2         | Toggle Switch                                            |                 |                 |

| DIP SW1, DIP SW2 | 8 Channel Dip Switch                                     |                 |                 |

| ROTARY SW        | 16 Channel Switch<br>4 MHz Cer. Res<br>14.32 MHz Crystal |                 |                 |

|                  | -                                                        |                 |                 |

MC141622EVK MOTOROLA

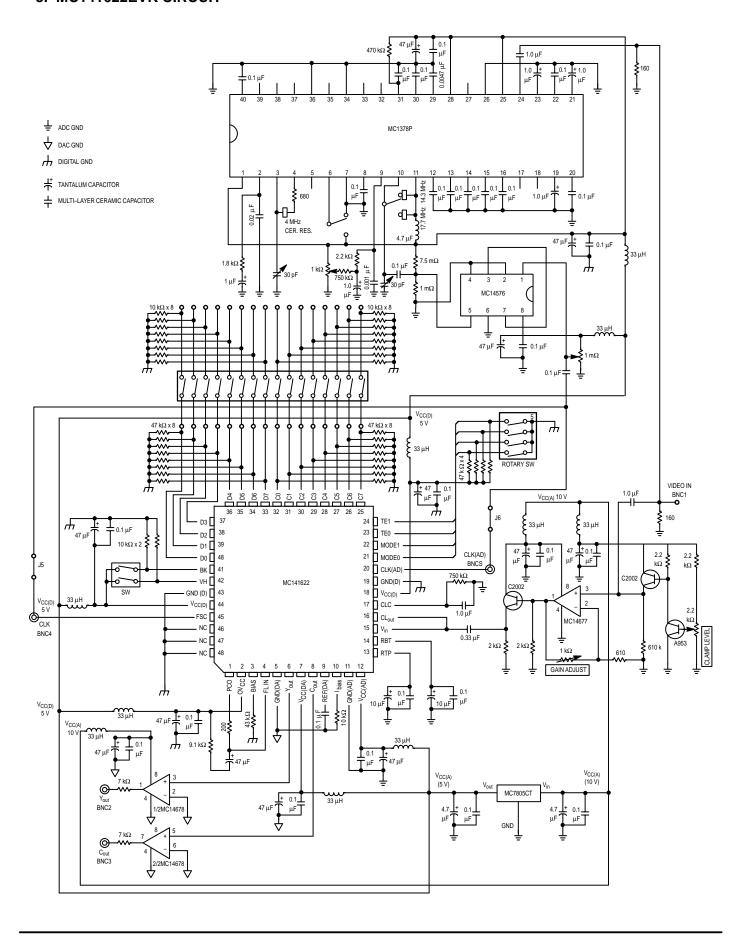

#### 7. MC141622EVK LAYOUT

**MOTOROLA** MC141622EVK

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the de

How to reach us:

**USA/EUROPE/Locations Not Listed**: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 303–675–2140 or 1–800–441–2447

$\label{eq:max} \textbf{Mfax}^{\text{TM}}: RMFAX0@email.sps.mot.com - TOUCHTONE~602-244-6609~INTERNET:~http://www.mot.com/SPS/$

Mfax is a trademark of Motorola, Inc.

**JAPAN**: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 81–3–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

MC141622EVK/D