## Advance Information

## Multimode Color Monitor Horizontal, Vertical, and Video Combination Processor

The MC13081X includes all the signal processing functions for a scan frequency agile and multiple sync system analog RGB monitor and includes the following functions:

- Automatic Horizontal Frequency Tracking of All Commonly Used Personal Computers, Continuously Adaptable from 30 kHz to 64 kHz

- Sync-on-Green Detection

- Vertical Timebase Operates from 45 to 100 Hz

- Vertical and Horizontal Sync Polarity Detection with Outputs for Mode Switching

- Video Pre–Amplifiers Typical Rise/Fall Time of 5.0 ns at 3.0 Vpp Output Voltage Swing

- Overall Contrast Control and Independent RGB Gain Controls

# MULTIMODE COLOR MONITOR PROCESSOR

SEMICONDUCTOR TECHNICAL DATA

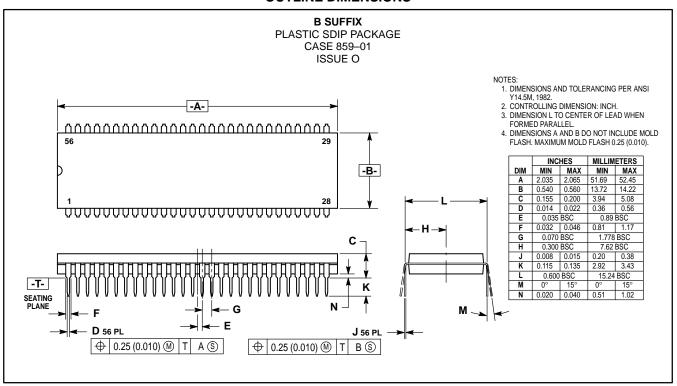

B SUFFIX

PLASTIC SDIP PACKAGE

CASE 859

#### ORDERING INFORMATION

| Device    | Operating<br>Temperature Range                 | Package      |

|-----------|------------------------------------------------|--------------|

| MC13081XB | $T_A = 0^\circ \text{ to } +70^\circ \text{C}$ | Plastic SDIP |

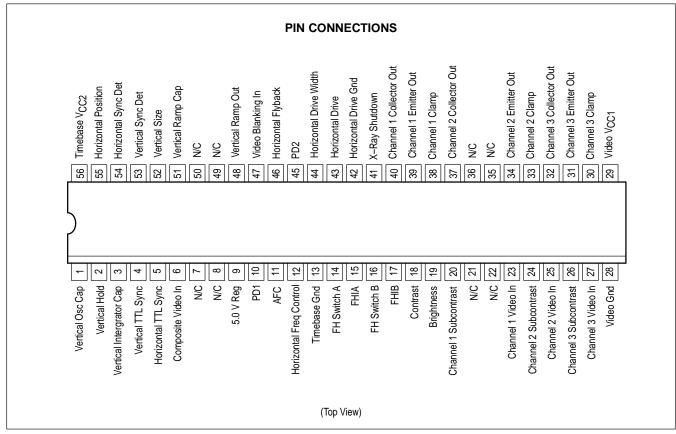

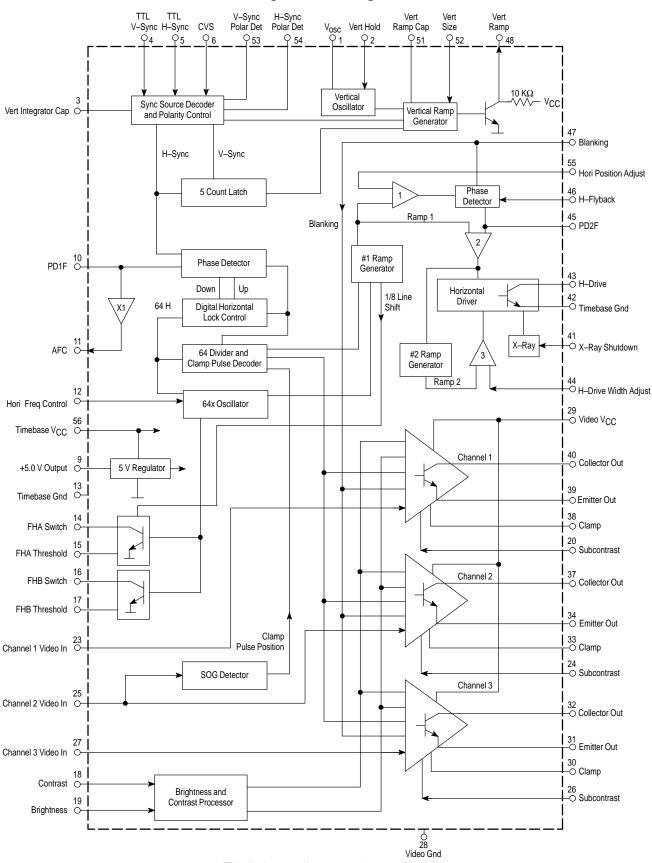

Figure 1. Block Diagram

This device contains 1074 active transistors.

**MAXIMUM RATINGS** ( $T_A = 25^{\circ}C$ , unless otherwise noted.)

| Rating                                                                                                                                                  | Pin                        | Value                            | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------|------|

| Power Supply Voltage Video Section V <sub>CC1</sub> Timebase Section V <sub>CC2</sub>                                                                   | 29<br>56                   | -0.5, +10<br>-0.5, +10           | Vdc  |

| Brightness, Contrast, Horizontal Flyback<br>Input, Frequency Switch when Off                                                                            | 19, 18, 46,<br>14, 16      | 0 to V <sub>CC</sub>             | Vdc  |

| X–Ray Shutdown                                                                                                                                          | 41                         | -0.5, +0.9                       | Vdc  |

| Subcontrast RGB Controls                                                                                                                                | 20, 24, 26                 | 0 to +2.0                        | Vdc  |

| Horizontal Drive Width, Horizontal Position                                                                                                             | 44, 55                     | 0 to +5.0                        | Vdc  |

| Voltage on Horizontal Drive when Off, Vertical TTL Sync Input, Horizontal TTL Sync Input, Composite Video Sync Input, Video Amplifier Output Collectors | 43, 4, 5, 6,<br>32, 37, 40 | -0.5 to<br>V <sub>CC</sub> + 0.5 | Vdc  |

| Current into Horizontal Drive when On                                                                                                                   | 43                         | 100                              | mA   |

| Current into Frequency Switch when On                                                                                                                   | 14, 16                     | 30                               | mA   |

| Video Amplifier Inputs                                                                                                                                  | 23, 25, 27                 | -0.5, + 5.0                      | Vdc  |

| Video Amplifier Output Current (Total for the Three Channels)                                                                                           | 40, 39, 37,<br>34, 32, 31  | 120                              | mA   |

| Storage Temperature                                                                                                                                     | _                          | -65 to +150                      | °C   |

| Junction Temperature                                                                                                                                    | -                          | +150                             | °C   |

NOTE: ESD data available upon request.

#### RECOMMENDED OPERATING CONDITIONS

| Characteristic                                                       | Pin        | Min  | Тур | Max | Unit |

|----------------------------------------------------------------------|------------|------|-----|-----|------|

| Power Supply Voltage                                                 |            |      |     |     | Vdc  |

| Video Section V <sub>CC1</sub>                                       | 29         | 7.6  | 8.0 | 8.4 |      |

| Timebase Section V <sub>CC2</sub>                                    | 56         | 7.6  | 8.0 | 8.4 |      |

| Power Supply Voltage Difference, V <sub>CC2</sub> – V <sub>CC1</sub> | _          | -0.3 | 0   | 0.8 | Vdc  |

| Internal 5.0 V Regulator Output Current                              | 9          | -20  | _   | 0   | mA   |

| Contrast Control                                                     | 18         | 0    | _   | 5.0 | Vdc  |

| Brightness Control                                                   | 19         | 0    | -   | 5.0 | Vdc  |

| Subcontrast Control                                                  | 20, 24, 26 | 0    | -   | 2.0 | Vdc  |

| Horizontal Drive Width Adjust                                        | 44         | 0    | -   | 5.0 | Vdc  |

| Horizontal Position Adjust                                           | 55         | 1.0  | -   | 4.0 | Vdc  |

| Horizontal Flyback Signal Amplitude                                  | 46         | 0.7  | 5.0 | 8.0 | V    |

| Horizontal Flyback Signal DC Input Voltage Level                     | 46         | -0.2 | 0   | -   | Vdc  |

| Voltage on Horizontal Drive Collector when "Off"                     | 43         | 0    | -   | Vcc | V    |

| Current into Horizontal Drive Collector when "On"                    | 43         | 0    | -   | 40  | mA   |

| Voltage on Horizontal Drive Emitter W.R.T. Circuit Ground            | 42         | -0.3 | 0   | 2.0 | Vdc  |

| Blanking Input Signal Amplitude                                      | 47         | 1.5  | -   | 4.0 | V    |

| Voltage on FH Switches when "Off"                                    | 14, 16     | 0    | -   | 8.0 | Vdc  |

| Current into each FH Switch when "On"                                | 14, 16     | 0    | -   | 20  | mA   |

| X–Ray Shutdown                                                       | 41         | 0    | -   | 0.7 | Vdc  |

| Composite Video Sync Input                                           | 6          | 1.0  | -   | 2.0 | Vpp  |

| Vertical Sync Frequency                                              | -          | 45   | -   | 100 | Hz   |

| Horizontal Sync Frequency                                            | -          | 30   | -   | 64  | kHz  |

| Vertical Sync Pulse Width                                            | _          | -    | 70  | _   | μs   |

| Horizontal Sync Pulse Width                                          | _          | -    | 1.0 | _   | μs   |

## RECOMMENDED OPERATING CONDITIONS (continued)

| Characteristic                                          | Pin                      | Min   | Тур           | Max     | Unit |

|---------------------------------------------------------|--------------------------|-------|---------------|---------|------|

| Video Signal Amplitude (with 75 Ω Termination)          | 23, 25, 27               | 0.5   | 0.7           | 1.2     | Vpp  |

| Voltage on Video Amplifier Collector                    | 32, 37, 40               | 4.5   | _             | VCC     | Vdc  |

| Current Through Video Collector–Emitter                 | 40, 39, 37<br>34, 32, 31 | 0     | _             | 40      | mA   |

| Vertical Hold Set Resistance, R9 + VR2 (Figure 2)       | 2                        | -     | 10            | -       | kΩ   |

| Vertical Size Set Resistance, R10 + VR3 (Figure 2)      | 52                       | -     | 220           | -       | kΩ   |

| Vertical Linearity Set Resistance, R12 + VR4 (Figure 2) | 51                       | -     | 1000          | -       | kΩ   |

| Operating Ambient Temperature                           | -                        | 0     | 25            | 70      | °C   |

| FH Switches Set Resistance                              | 15, 17                   | See A | pplication Se | ction 5 | -    |

| Vertical TTL Sync Input                                 | 4                        | TT    | L Voltage Le  | vel     | Vdc  |

| Horizontal TTL Sync Input                               | 5                        | TT    | L Voltage Le  | vel     | Vdc  |

## **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = $25^{\circ}$ C, V<sub>CC</sub> = 8.0 Vdc)

| Characteristic                                                                                     | Condition                                                                                                                         | Pin    | Min                 | Тур                      | Max                      | Unit                     |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|--------------------------|--------------------------|--------------------------|

| POWER SUPPLIES                                                                                     |                                                                                                                                   |        | •                   | •                        |                          | •                        |

| Supply Current<br>Total Consumption                                                                | -                                                                                                                                 | 29, 56 | 70                  | 85                       | 110                      | mA                       |

| 5.0 V Regulator Output Voltage Line Regulation Load Regulation Temperature Coefficient             | Load Current (I <sub>B</sub> ) = 0 mA<br>7.6 V < V <sub>CC</sub> < 8.4 V, I <sub>B</sub> = 0 mA<br>-10 mA < I <sub>B</sub> < 0 mA | 9      | 4.75<br>-<br>-<br>- | 5.0<br>25<br>100<br>-0.3 | 5.25<br>-<br>-<br>-<br>- | Vdc<br>mV<br>mV<br>mV/°C |

| Thermal Resistance, Junction–to–Ambient                                                            | -                                                                                                                                 | _      | _                   | 59                       | _                        | °C/W                     |

| HORIZONTAL PROCESSING                                                                              |                                                                                                                                   | 40     | 20                  | <u> </u>                 |                          | T 1.11=                  |

| Horizontal Oscillator Frequency Range  Horizontal Oscillator Free Running Frequency @ 112 = 240 μA | -<br>Sink 240 μA from Pin 12 with<br>Resistor R5 Opened                                                                           | 43     | 29                  | 31                       | 33                       | kHz<br>kHz               |

| Horizontal Sync Detector Output/+VE Sync                                                           | -                                                                                                                                 | 54     | _                   | 0                        | -                        | Vdc                      |

| Horizontal Sync Detector Output/–VE Sync                                                           | -                                                                                                                                 | 54     | _                   | 3.6                      | -                        | Vdc                      |

| Horizontal Sync Input<br>Input Impedance<br>Input Level – Low<br>Input Level – High                | -                                                                                                                                 | 5      | -<br>0<br>2.4       | 22<br>-<br>-             | 0<br>0.8<br>5.0          | kΩ<br>Vdc<br>Vdc         |

| Composite Video Sync Input<br>Input Impedance<br>Internal Bias Level<br>Minimum Input Amplitude    | _                                                                                                                                 | 6      | -<br>-<br>0.1       | 1.0<br>1.55<br>–         | -<br>-<br>-              | kΩ<br>Vdc<br>Vpp         |

| Short Term Horizontal Pull-In Range                                                                | Time < 5.0 ms                                                                                                                     | -      | _                   | ±5.0                     | -                        | %FH                      |

| Long Term Horizontal Pull-In Range                                                                 | Time > 500 ms                                                                                                                     | -      | 30                  | -                        | 64                       | kHz                      |

| Horizontal Frequency Control (Current Transfer Constant)                                           | Current Flowing Out of Pin 12                                                                                                     | 12     | 115                 | 122                      | 129                      | Hz/μA                    |

| Horizontal Free Running Frequency<br>Change versus Temperature                                     | Pin 11 is Opened                                                                                                                  | -      | -                   | 300                      | -                        | ppm/°C                   |

| FH Switch Threshold Pins<br>Output Current<br>Threshold<br>Hysteresis                              | -                                                                                                                                 | 15, 17 | -<br>-<br>0         | 112/2<br>5.0<br>–        | -<br>-<br>200            | μA<br>V<br>mV            |

| FH Switch Voltage when "On"                                                                        | I = 10 mA                                                                                                                         | 14, 16 | _                   | -                        | 200                      | mVdc                     |

**ELECTRICAL CHARACTERISTICS (continued)** ( $T_A = 25^{\circ}C$ ,  $V_{CC} = 8.0 \text{ Vdc}$ )

| Characteristic                                        | Condition                                                       | Pin        | Min      | Тур        | Max    | Unit       |

|-------------------------------------------------------|-----------------------------------------------------------------|------------|----------|------------|--------|------------|

| HORIZONTAL DRIVE                                      |                                                                 |            |          |            |        |            |

| Horizontal Position Adjust                            | 0 < V55 < 5.0 V,                                                | 55         |          |            |        |            |

| Range                                                 | FH = 30 k – 56 kHz                                              |            | -        | 10         | _      | %          |

| Input Impedance                                       | See Application Section 7                                       |            | _        | 31         | -      | kΩ         |

| Horizontal Drive Width Adjust                         | FH = 35 kHz, 0 < V44 < 5.0 V                                    | 44         | 0.4      |            | 4.0    | 0/         |

| Range<br>Input Impedance                              |                                                                 |            | 2:1      | 30         | 1:2    | %<br>kΩ    |

| Horizontal Flyback                                    | San Application Section 4                                       | 46         |          | 30         |        | 1/22       |

| Threshold                                             | See Application Section 4 Input Signal Should Not Fall          | 40         | _        | 0.7        | _      | v          |

| Input Amplitude                                       | Below –0.2 V                                                    |            | 0        | -          | 8.0    | V          |

| Input Impedance                                       |                                                                 |            | -        | 10         | -      | kΩ         |

| Horizontal Drive                                      |                                                                 | 43         |          |            |        |            |

| Output Low                                            | I <sub>sink</sub> = 40 mA                                       |            | 0        | -          | 0.3    | Vdc        |

| Output High                                           | V43 = V <sub>CC</sub>                                           |            | -        | -          | 100    | μΑ         |

| Time Delay from Flyback to Video Output Blanking      | See Application Section 7                                       | -          | _        | 250        | _      | ns         |

| Time Delay from Blanking to Video Output<br>Blanking  | See Application Section 7                                       | -          | -        | 400        | -      | ns         |

| X–Ray Shutdown<br>Activate Voltage                    | See Application Section 11                                      | 41         | 0.4      | 0.58       | 0.7    | Vdc        |

| Temperature Coefficient of X–Ray<br>Threshold Voltage | _                                                               | 41         | -        | -2.3       | -      | mV/°C      |

| Horizontal Jitter                                     | 30 kHz < FH < 56 kHz                                            | 43         | _        | 3.0        | _      | ns         |

| VERTICAL PROCESSING                                   |                                                                 |            |          |            |        |            |

| Vertical Ramp Frequency                               | _                                                               | 48         | 45       | T _        | 100    | Hz         |

| · · · · · ·                                           | EV 5011-                                                        | 48         |          |            |        | +          |

| Vertical Ramp<br>Amplitude                            | FV = 50  Hz,<br>R12 + VR4 = 820 kΩ                              | 40         | _        | 3.0        | _      | Vpp        |

| Minimum Peak                                          | R10 + VR3 = 120 k $\Omega$ ,                                    |            | _        | 1.9        | _      | V          |

| Maximum Peak                                          | C6 = C7 = 1.0 μF                                                |            | -        | 3.4        | _      | V          |

| Output Current                                        |                                                                 |            | -        | 2.0        | _      | mA         |

| Non-Linearity                                         |                                                                 |            | _        | 0.45       | 1.0    | %          |

| Vertical Ramp Free Running Temperature<br>Drift       | FV = 50 Hz                                                      | 48         | _        | 0.01       | _      | Hz/°C      |

| Vertical Ramp Free Running Drift with $V_{\hbox{CC}}$ | FV = 50 Hz                                                      | 48         | -        | 0.5        | -      | Hz/V       |

| Vertical Ramp Discharge Rate (Retrace)                | FV = 50 Hz                                                      | 48         | -        | 9.5        | -      | V/ms       |

| Vertical Sync Detector Output/+V <sub>E</sub> Sync    |                                                                 | 53         | _        | 0          | -      | Vdc        |

| Vertical Sync Detector Output/–VE Sync                |                                                                 | 53         |          | 3.6        | _      | Vdc        |

| Vertical Sync Input                                   | _                                                               | 4          |          |            |        |            |

| Input Impedance                                       |                                                                 |            | _        | 22         | _      | kΩ         |

| Input Level – Low                                     |                                                                 |            | 0        | _          | 0.8    | Vdc        |

| Input Level – High                                    |                                                                 |            | 2.4      | _          | 5.0    | Vdc        |

| VIDEO AMPLIFIERS                                      |                                                                 |            |          |            |        |            |

| Input Impedance<br>Internal DC Bias Voltage           | -                                                               | 23, 25,27  | 100<br>- | -<br>2.4   | -<br>- | kΩ<br>Vdc  |

| Output Signal Amplitude<br>Voltage Gain               | V <sub>in</sub> = 0.7 Vpp, V18 = 5.0 V<br>V20 = V24 = V26 = 0 V | 39, 34, 31 | 1 1      | 3.6<br>5.1 | -<br>- | Vpp<br>V/V |

| Contrast Control                                      | V18 = 0 to 5.0 V;<br>V20, 24, 26 = 0 V                          | 18         | -        | 20         | -      | dB         |

| Subcontrast Control                                   | V20, 24, 26 = 2.0 to 0 V;<br>V18 = 5.0 V                        | 20, 24, 26 | 1:2.5    | -          | _      | -          |

| Brightness Control                                    | V19 = 0 to 5.0 V, Measure<br>Pin 39, 34, 31 DC Level            | 19         | _        | ±0.5       | -      | Vdc        |

## **ELECTRICAL CHARACTERISTICS (continued)** ( $T_A = 25$ °C, $V_{CC} = 8.0 \text{ Vdc}$ )

| Characteristic                                                                     | Condition                                              | Pin        | Min            | Тур               | Max            | Unit |

|------------------------------------------------------------------------------------|--------------------------------------------------------|------------|----------------|-------------------|----------------|------|

| VIDEO AMPLIFIERS                                                                   |                                                        |            |                |                   |                |      |

| Emitter DC Level<br>Minimum Brightness<br>Nominal Brightness<br>Maximum Brightness | V19 = 0 V<br>V19 = 2.5 V<br>V19 = 5.0 V                | 39, 34, 31 | -<br>1.25<br>- | 1.0<br>1.5<br>2.0 | -<br>1.75<br>- | Vdc  |

| Crosstalk, Amplifier to Amplifier                                                  | Frequency = 10 MHz                                     | 39, 34, 31 | -              | 34                | -              | dB   |

| Output Rise Time<br>Output Fall Time                                               | $V_{in} = 0.7 \text{ Vpp; } V_{out} = 3.0 \text{ Vpp}$ | 39, 34, 31 | 1 1            | 5.0<br>5.0        | -<br>-         | ns   |

#### PIN FUNCTION DESCRIPTION

| Pin  | Name                                | Equivalent Internal Circuit           | Description                                                                                                                                                                                                                                                                                      |

|------|-------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Vertical<br>Oscillator<br>Capacitor | 2.5 k   12   10.7   Vertical Ramp Gen | This capacitor should be 100 nF film type to give good temperature stability.                                                                                                                                                                                                                    |

| 2    | Vertical Hold<br>Control            | R2 C1                                 | The potentiometer at Pin 2 adjusts the free running frequency of the oscillator. It should normally be set for about 55 Hz with no vertical signal input such that it will lock to 60 Hz.                                                                                                        |

| 3    | Vertical<br>Integrator<br>Capacitor | C3   Switching Control                | The capacitor on this pin integrates the sync pulses with a long time constant. C3 is typically 0.01 μF.                                                                                                                                                                                         |

| 4    | Vertical TTL<br>Sync                | Sync 4 22 k To Logic                  | Vertical TTL Sync input. The input threshold voltage at this pin is 2.0 V.                                                                                                                                                                                                                       |

| 5    | Horizontal TTL<br>Sync              | Sync 5 10 k To Logic                  | Composite or Horizontal TTL Sync input. The input threshold voltage at this pin is 2.0 V.                                                                                                                                                                                                        |

| 6    | Composite<br>Video Input            | Comp Input O.1 10 k To Sync Separator | This pin requires a coupling of min 100 nF. The composite sync input should consist of $-V_E$ sync signal only with amplitude > 500 mVpp.  The source impedance of the sync signal should be <1.0 k $\Omega$ .  Sync information at Pin 5 will override this pin, but signals at Pin 4 will not. |

|      |                                     | -                                     | Minimum pulse width is 2.0 μs.                                                                                                                                                                                                                                                                   |

| 7, 8 | N/C                                 |                                       | These two pins are internally connected to each other, and nothing else.                                                                                                                                                                                                                         |

| Pin    | Name                                   | Equivalent Internal Circuit                                   | Description                                                                                                                                                                                                                                                                                                       |

|--------|----------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9      | 5.0 V<br>Regulator<br>Output           | 5.0 V Band Gap Regulator Regulator                            | $5.0~V~(\pm 5\%)$ regulator. Minimum $10~\mu F$ capacitor is required for noise filtering and compensation. Up to $20~mA$ can be supplied to external circuitry. It can source but not sink current. Output impedance is $\approx 10~\Omega$ . This $5.0~V~regulator$ is recommended for use as a reference only. |

| 10     | Phase<br>Detector 1<br>Filter          | Phase Detector #1  Sync Horiz OSC  A00 μA  10 C10A  NR10 C10B | External components at this pin will determine the PLL gain and phase characteristics. The capacitors should be non–polarized.  The voltage at this pin nominally ranges from 1.5 V to 5.0 V with corresponding horizontal frequency from 25 kHz to 68 kHz.                                                       |

| 11     | Automatic<br>Frequency<br>Control      | From Pin 10 VCC R11A R11B                                     | Pin 11 is a buffered equivalent of Pin 10, and ranges from a minimum of 1.5 V at horizontal high frequency to near 5.0 V at low frequency. Pin 11 can sink a maximum of 1.0 mA, but cannot source current.                                                                                                        |

| 12     | Horizontal<br>Frequency<br>Range       | Oscillator 5.0 V 12 R11C                                      | The current out of Pin 12 determines the horizontal frequency by a current transfer constant of ≈ 122 Hz/μA.  Pin 12 is internally maintained at 5.0 V.                                                                                                                                                           |

| 13     | Timebase<br>Ground                     |                                                               | Ground for the timebase section. Connect to a clean, low impedance ground.                                                                                                                                                                                                                                        |

| 14, 16 | FH Switch A, B                         | 0 14 0 16                                                     | Pin 14 (Switch A), and Pin 16 (Switch B) are open collector NPN switches to ground. Each switch is "on" when the horizontal frequency is higher than the set points set by resistors at Pins 15 and 17, respectively.  Maximum voltage is 8.0 V, and maximum sink current is 20 mA.                               |

| 15, 17 | FH Switch A, B<br>Threshold<br>Setting | 15,17  R15                                                    | Pin 15 and Pin 17 are current mirror at 1/2 of Pin 12 current. External resistors at these pins set the horizontal frequency at which Pins 14 and 16 will switch, respectively. The threshold voltage is 5.0 V.                                                                                                   |

| 18     | Contrast<br>Control                    | 5.0 V                                                         | The input control range is from 0 to 5.0 V. An increase of voltage increases contrast.                                                                                                                                                                                                                            |

| 19     | Brightness<br>Control                  | R18 18,19 (R19)                                               | The input control range is from 0 to 5.0 V. An increase of voltage increases brightness.                                                                                                                                                                                                                          |

| Pin                              | Name                                                                                                                               | Equivalent Internal Circuit                                                                         | Description                                                                                                                                                                                                                                                  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20<br>24<br>26                   | Subcontrast<br>Control<br>Channel 1<br>Channel 2<br>Channel 3                                                                      | VCC<br>50 k Gain<br>7.5 k                                                                           | Subcontrast controls the gain of each video channel. 0 V for maximum gain, and 2.0 V for minimum gain.                                                                                                                                                       |

| 21, 22                           | N/C                                                                                                                                |                                                                                                     | These two pins are internally connected to each other, and nothing else.                                                                                                                                                                                     |

| 23<br>25<br>27                   | Video Inputs<br>Channel 1<br>Channel 2<br>Channel 3                                                                                | Video 2.2 μF 23, 25, 27                                                                             | The input coupling capacitor is used for input clamp storage. The maximum source impedance is 100 $\Omega$ . Polarity of the input video signal is positive. Amplitude should be nominally 0.7 Vpp.                                                          |

| 28                               | Video Ground                                                                                                                       |                                                                                                     | Ground for the video section (video amplifiers, contrast and brightness controls, subcontrast, and video reference voltage).  Noise from the timebase section, and other digital                                                                             |

|                                  |                                                                                                                                    |                                                                                                     | circuits, should not be allowed to produce ground bounce at this pin.                                                                                                                                                                                        |

| 29                               | Video V <sub>CC1</sub>                                                                                                             |                                                                                                     | Connected to a 8.0, V $\pm 5\%$ , dc supply. Decoupling is required at this pin.                                                                                                                                                                             |

| 38<br>33<br>30                   | Video Clamp<br>Channel 1<br>Channel 2<br>Channel 3                                                                                 | Clamp Pulse 38, 33, 30 Video Out = 38, 33, 30                                                       | Normally a 100 nF capacitor is connected to each of these pins.                                                                                                                                                                                              |

| 39<br>34<br>31<br>40<br>37<br>32 | Video Emitter<br>Output<br>Channel 1<br>Channel 2<br>Channel 3<br>Video Collector<br>Output<br>Channel 1<br>Channel 2<br>Channel 3 | Blanking  VCC  VCC  VCC  VCC  A0, 37, 32  Rc  Video Amp  Sightness  Contrast  To  Clamp Circuit  Re | Pins 39, 34, and 31 are the emitter outputs of the three video amplifier, and have an internal 33 $\Omega$ resistor. The emitter dc voltage is controlled by the brightness control. The current through each collector and emitter should not exceed 40 mA. |

| 35, 36                           | N/C                                                                                                                                |                                                                                                     | These two pins are internally connected to each other, and nothing else.                                                                                                                                                                                     |

| Pin | Name                                  | Equivalent Internal Circuit                                            | Description                                                                                                                                                                                                  |

|-----|---------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41  | X–Ray<br>Shutdown                     | X-Ray 41 Shutdown                                                      | If the voltage at this pin is > 0.58 V, the horizontal driver device (Pins 42 and 43) will be "on" until power is removed, or the voltage on this pin is taken below 0.4 V.                                  |

| 42  | Horizontal<br>Drive Ground            | V <sub>CC</sub> V <sub>CC</sub> V <sub>CC</sub> 43 R43 V <sub>CC</sub> | This emitter pin must be connected externally to a low impedance ground.  Pin 43 is an open collector pin and normally is pulled up by a resistor to VCC.                                                    |

| 43  | Horizontal<br>Drive                   | 42 To Horizontal Deflection Circuit                                    | Maximum current through Pins 42 and 43 must be less than 40 mA.                                                                                                                                              |

| 44  | Horizontal<br>Drive Width             | 5.0 V<br>R44 22 k<br>13.5 k<br>13.5 k                                  | Varying the voltage at this pin will change the horizontal drive duty cycle. As the voltage of this pin is increased, the "on" time at Pin 43 is decreased. Input impedance is $\approx 30~\text{k}\Omega$ . |

| 45  | Secondary<br>Phase<br>Detector Filter | Phase Detector #2  Sync Horiz OSC  VCC  250 μA  45  C45                | Typically a 10 to 100 nF decoupling capacitor is connected to this pin.                                                                                                                                      |

| 46  | Horizontal<br>Flyback                 | Flyback 46 10 k Signal To Phase Detector #2                            | The flyback signal should be a +V <sub>E</sub> pulse of peak voltage 8.0 V. The internal switching voltage is 0.7 V and it controls the secondary PLL Input impedance is $\approx$ 10 k $\Omega$             |

| 47  | Video Blanking<br>Input               | 2.0 k Blanking                                                         | The video blanking signal should be positive pulse in the range of 1.5 to 4.0 V.                                                                                                                             |

| Pin    | Name                                    | Equivalent Internal Circuit                                                                  | Description                                                                                                                                                                                                                                                   |

|--------|-----------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48     | Vertical Ramp<br>Output                 | 2.0 V, 5.0 V Trip Pts  Vertical Oscillator  Vertical Ramp Generator  Vertical Ramp Generator | This ramp signal drives the external vertical output devices.   Voltage ramps from 2.0 V to less than 5.0 V, depending on frequency and components at Pins 51 and 52.   Loading on this pin must be > 30 k $\Omega$ to avoid distorting or clipping the ramp. |

| 49, 50 | N/C                                     |                                                                                              | These two pins are internally connected to each other, and nothing else.                                                                                                                                                                                      |

| 51     | Vertical Ramp<br>Capacitor              | Switching Control  Vertical                                                                  | The slope of the output ramp is determined by the components at Pins 51 and 52.  The resistor at Pin 52 sets the charging current of the capacitor, and therfore the vertical height of the picture.  The linearity of the ramp can be modified by external   |

| 52     | Vertical Size<br>Control                | Oscillator  52  51  C51                                                                      | feedback.                                                                                                                                                                                                                                                     |

| 53     | Vertical Sync<br>Polarity<br>Detector   | 5.0 V                                                                                        | The output goes low when the vertical sync input polarity is positive. It goes high when the vertical sync input polarity is negative.                                                                                                                        |

| 54     | Horizontal<br>Sync Polarity<br>Detector | 53,54                                                                                        | The output goes low when the horizontal sync input polarity is positive. It goes high when the horizontal sync input polarity is negative.                                                                                                                    |

| 55     | Horizontal<br>Position<br>Control       | 5.0 V<br>R55 S5 25 k<br>25 k<br>R855 R8mp 1                                                  | Varying the voltage at this pin will change the horizontal position of the picture. Input impedance is $\approx$ 31 k $\Omega$ .                                                                                                                              |

| 56     | Timebase<br>V <sub>CC2</sub>            |                                                                                              | Connected to a 8.0 V, $\pm$ 5%, dc supply. Decoupling is required at this pin.                                                                                                                                                                                |

#### APPLICATION INFORMATION

The MC13081X is an integrated multisync color monitor processor. It combines horizontal/vertical deflection processing circuitry and video pre–amplifiers into a single device.

The overall timebase section consists of two parts: horizontal and vertical. The horizontal timebase can be operated from 30 kHz to 64 kHz, and can be driven from TTL separate sync, composite sync, or a composite video signal. There are two PLLs which ensure proper timing throughout the whole system. The first PLL provides line locking of the horizontal sync signal with the built—in oscillator, while the second one maintains fixed timing with the horizontal flyback signal such that a stable display can be achieved.

The vertical timebase section operates from 45 Hz to 100 Hz, and can receive various sync signals as the horizontal one does. This section consists of an oscillator and a ramp generator. Adjustments include linearity, ramp

amplitude, and minimum free running frequency in the absence of sync signal.

The video section has three 70 MHz bandwidth pre–amplifiers. The outputs of these amplifiers are uncommitted collector/emitter facilitating cascode configuration with subsequent stages. Controls include brightness and contrast. In addition, the voltage gain of each amplifier can be adjusted individually which provides flexibility in adjusting color correctness. Blanking and clamping signals are provided to the amplifiers internally from the timebase section. Additionally, a blanking signal can also be supplied externally.

Separate power supply and ground pins are provided to the timebase and video section in order to minimize the cross interference between these two sections.

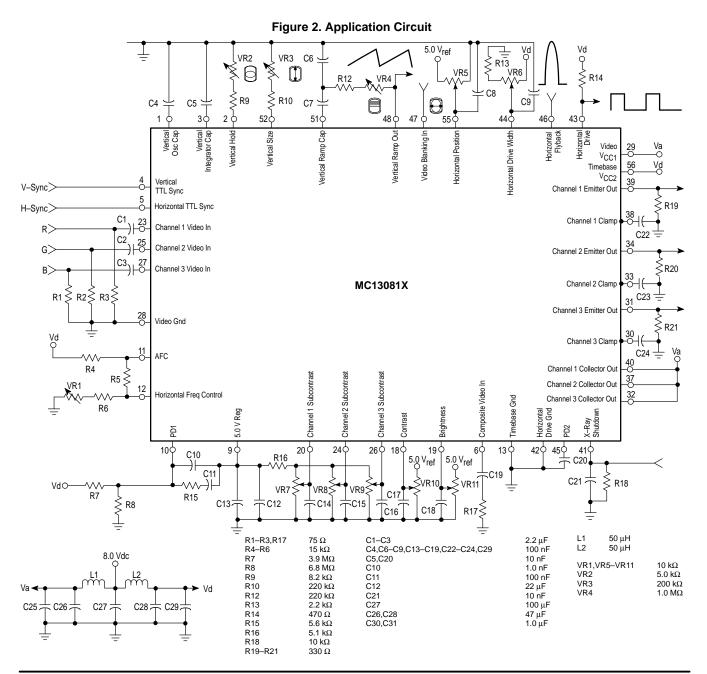

The following describes a step-by-step procedure in using the MC13801 for a typical multisync color monitor chassis; component notations refer to Figure 2.

#### Horizontal Frequency Range Resistor Network (Pins 11, 12)

F<sub>Hm</sub> = Minimum Horizontal Frequency F<sub>Hx</sub> = Maximum Horizontal Frequency Oscillator Transfer Constant = 122 Hz/μA

$$R5 = \frac{6.35 \times 10^8}{F_{Hx} - F_{Hm}}$$

$$R6 = \frac{5}{\frac{F_{Hx}}{122 \times 10^6} - \frac{3.5}{R5}}$$

$$R4 \le \frac{V_{CC} - 6.0}{1.5}$$

x R5 and  $\frac{V_{CC} - 1.5}{R4} < 1.0$  mA

For most applications, R4 = R5 provides the required results.

**NOTE:** In order to compensate device/component tolerance, a potentiometer is recommended in series with R6, as VR1.

#### Horizontal Frequency Range Phase Detector Filter Network (Pin 10)

Typical values are:

C10 = 1.0 nF

C11 = 100 nF

R15 = 5.6 k

$C11 \ge 100 \times C10$

NOTE: C10 and C11 should have less than 1.0  $\mu\text{A}$  leakage.

#### 3. Horizontal Free Running Frequency

The voltage at Pin 10 will be buffered to Pin 11, and hence control the internal oscillator. In the absence of horizontal sync signal, the free running horizontal frequency will vary between preset minimum and maximum horizontal frequency values.

If an undetermined free running frequency value is not desired, a large impedance resistor can be used to pull Pin 10 to V<sub>CC</sub> or Gnd, and the free running frequency will be equal to F<sub>Hm</sub> or F<sub>Hx</sub>, respectively.

The free running frequency can also be set to any value within the horizontal frequency range by using a voltage divider, as R7 and R8 indicate.

$$V11 = V_D \times \frac{R7}{R7 + R8}$$

$$112 = \frac{V11}{R6 + VR1} - \frac{V11 - 5}{5}$$

Free Running Frequency = I12  $\mu$ A x  $\frac{122~Hz}{\mu A}$

The above formula provides the ratio of R7 and R8. The values chosen should be similar to those shown in Figure 2.

#### 4. Horizontal Flyback Input (Pin 46)

The horizontal flyback signal not only provides proper timing reference for the horizontal drive output, but also supplies the necessary blanking for the video outputs.

There are two precautions for the flyback input. First, the signal should have a zero volt reference, and second, the peak value should be as near to VCC as possible.

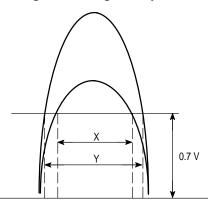

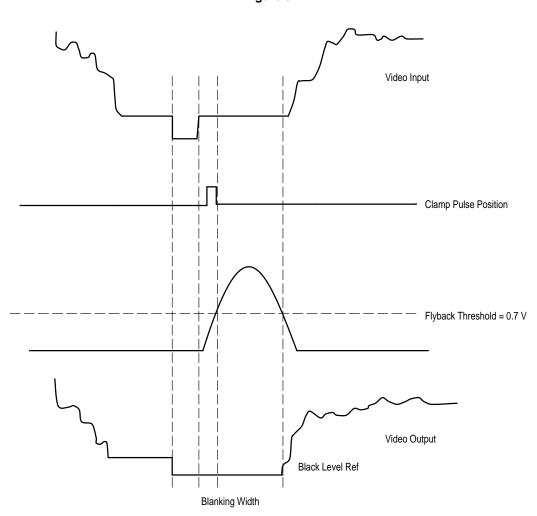

The threshold voltage for Pin 46 is 0.7 V. The blanking period depends on the amplitude, as shown in Figure 3 (X and Y, respectively). A larger amplitude provides better consistency and control of the blanking period.

Figure 3. Voltage for Flyback

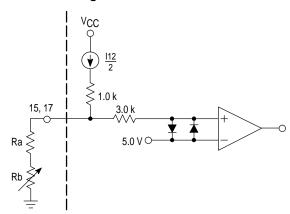

#### 5. Frequency Switch (Pin 14 to 17)

There are two frequency switches available for screen size compensation for different timing standards. Each switch will turn on at the switch frequency set with its external resistor. See Figure 4.

Figure 4. FH Switches

The switch frequency is calculated as follow:

SF = Switch Frequency

$$SF = \frac{5 \times 2 \times 122 \times 10^6}{Ra + Rb}$$

In considering the ratio of Ra to Rb, the following parameters, and their tolerances, need to be clarified:

1. l<sub>OSC</sub> ±10% 2. 5.0 V<sub>ref</sub> ±5% 3. V<sub>hys</sub> ±5% 4. Ra, Rb ±?%

Internally, the lock—in horizontal frequency will build up a current reference, and half of this current reference is used for setting up a voltage and then compared with the internal  $5.0\ V_{ref}$ . Looking at the four parameters above, the first three are IC related, while the last item depends on the external component tolerance.

By adding up the first three items, the value of Ra and Rb should be chosen to compensate for about 20% of system tolerance.

Therefore, if Ra is chosen to be 70% of the calculated value (Ra + Rb), Rb should be 60% of (Ra + Rb). That

means, the overall adjustment is about 70% to 130%, which provides additional ±10% margin.

During normal operation, the frequency switch will switch "off" when the pin voltage falls 60 mV below the 5.0 V reference voltage ( $\approx$  4.94 V), and will switch "on" when the pin voltage rises to 40 mV above the 5.0 V reference ( $\approx$  5.04 V).

An Example: Require Trip Point @ 35 kHz

I12 =

$$\frac{35 \times 10^3}{122}$$

$\mu$ A

Trip Point Reference Current =  $\frac{I12}{2}$

=  $\frac{35 \text{ k}}{122 \times 2}$   $\mu$ A

Ra + Rb =

$$\frac{5.0 \text{ V}}{\frac{35 \text{ k}}{122 \text{ x 2}} \mu A}$$

= 34857  $\Omega$

Hysteresis @ 35 kHz =

$$\frac{5.04 - 4.94 \text{ V}}{34857 \Omega}$$

x  $\frac{122 \text{ Hz}}{\mu \text{A}}$

From above, Ra + Rb =  $34857 \Omega$ Select Ra = 24 k, and Rb = 20 k Trim Pot

The Temperature Coefficient of the potentiometer can also be considered. If the value of the potentiometer and Ra vary by 1% (for example) over temperature, the error would be:

5 x

$$\left\{ \frac{1}{34857 \times 0.99} - \frac{1}{34857 \times 1.01} \right\}$$

x  $\frac{122 \text{ Hz}}{\mu\text{A}}$

$\approx 350 \text{ Hz}$

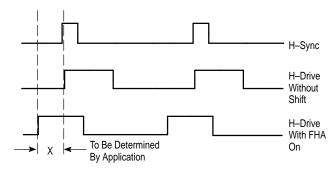

## 6. Horizontal Position Compensation for Selected Scan Frequency in Using FHA Switch

Refering to Figure1 (block diagram), there is an output from the FHA switch to the horizontal drive output. When the FHA switch is switched on, at a specified horizontal frequency, there is a 1/8th horizontal line shift of H–Ramp1. Referring to Figures 5 and 9, a shift of H–Ramp1 will result in a shift of the H–Drive output timing with respect to flyback input.

The exact H–Drive output shift will be determined by the PD2 voltage (Pin 45), which is generated by the flyback input and the internal Comp1 output. That is related to the H–Drive output transistor storage time.

This function is particularly useful for high frequency scan rates. The higher the frequency, the more significant the storage time becomes, compared to the horizontal scan time.

Figure 5.

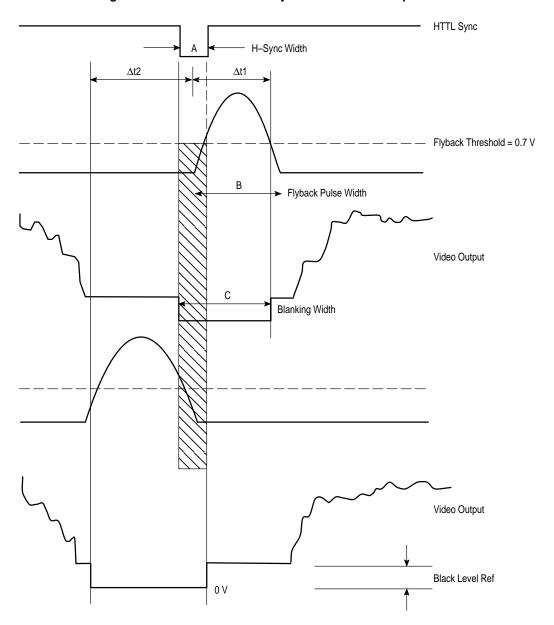

#### 7. Proper Horizontal Phase Control

The horizontal adjustment range depends on the phase angle between the H–Sync signal and the horizontal flyback input. In reality, the actual adjustment range is a combination of horizontal frequency, front porch/back porch timing, flyback pulse width, and horizontal output transistor storage time. The following paragraph conveys the concept for normal operation.

There are two clamping situations for video signals. In case 1, separate VTTL and HTTL sync are provided, the video signal is clamped at sync tip, and the dc voltage built up is used for black level reference. In this instance, the clamp pulse has the same pulse width as H–Sync, and nearly the same position. This clamp pulse is blanked out internally. In order to allow the video output to complete the blanking action during horizontal retrace, the horizontal phase should not be over–adjusted. See Figure 6 for a pictorial perception. Accordingly, the total horizontal position adjustment range is calculated as the sum of  $\Delta t1$  and  $\Delta t2$ .

Should the phase of horizontal flyback/H–Sync move further left or right from the normal adjustment range, the black level reference voltage will be restored, and consequently a slightly brighter than screen dark region will be observed on–screen. See Figure 7 for pictorial explanation.

Horizontal Blanking Time =

$$FP_{time}$$

+ Sync Width +  $BP_{time}$  =  $THB$

Criterion for Normal Operation:

$$|\Delta t1| < \frac{T_{HB}}{2}$$

$|\Delta t2| < \frac{T_{HB}}{2}$

In other words, the left/right 0.7 V threshold flyback reference should be within the H–Sync pulse (shaded area of Figure 6).

Figure 6. Horizontal Position Adjustment at Normal Operation

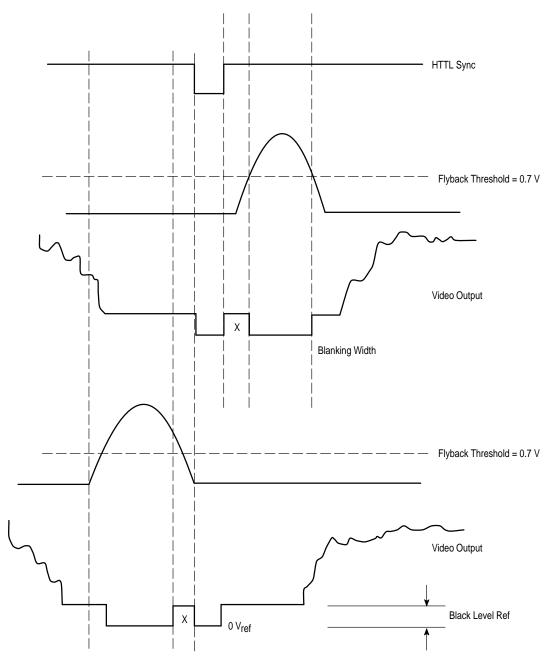

Figure 7. Horizontal Position Adjustment at Overscan Operation

**NOTE:** Region X will appear as bright vertical stripe.

Figure 8.

In case 2, composite sync is used instead of VTTL and HTTL sync, the clamp pulse is located at the backporch of the video signal, and the width of the clamp pulse is calculated as follows:

Clamp Pulse Width =

$$\frac{1}{64 \text{ x Line Frequency}} \times 3$$

Blanking Width = Sync Width + Clamp Pulse Width + Flyback Threshold (0.7 V) (See Figure 8)

From the above diagram, it can be seen that the horizontal position adjustment is basically the same as case 1 except slightly wider with the addition of clamp pulse blanking.

#### 8. Horizontal Timing Relationship for Phase Detector 2

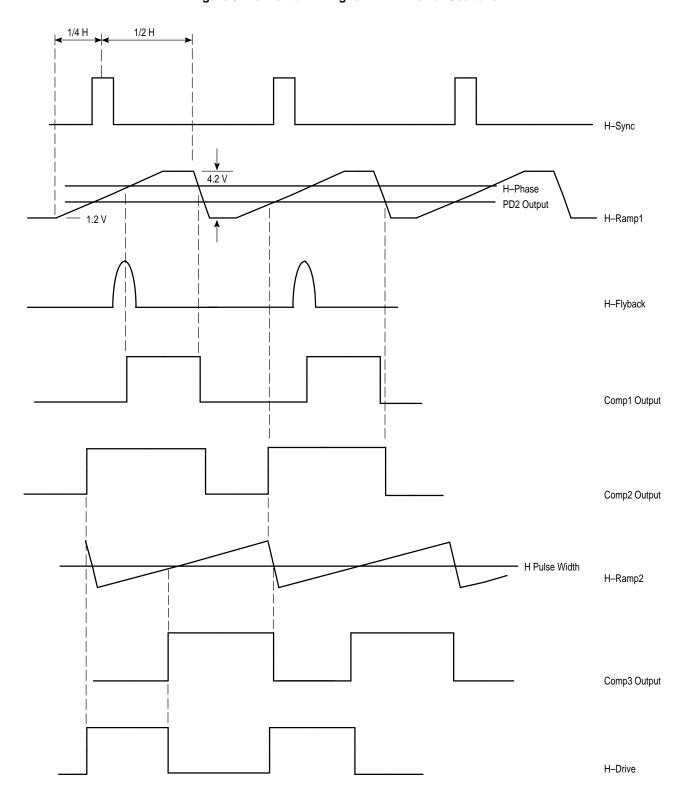

The following paragraphs explain the PLL2 mechanism. Figure 9 portrays the timing signals of various parts of the IC. In using the H–Sync pulse, which is generated from PLL1, a horizontal ramp 1 signal is created. H–Ramp1 starts at

1/4th line before H–Sync and the ramping slope is directly proportional to horizontal frequency. The lower tip of this ramp is at approximately 1.2 V, and the amplitude is about 4.2 V. By adjusting the dc bias to the H–Phase control, a pulse waveform is derived from this H–Ramp1.

A phase detector is used to compare the phase between the pulse generated above, and the incoming flyback pulse. An integrating capacitor is applied to generate a dc voltage. This dc voltage, PD2F output, is used to slice the H–Ramp1 signal in order to generate Comp2 output pulse.

A second ramp signal, H–Ramp2, is triggered from this Comp2 output. By applying a dc voltage (H–Width control) to H–Ramp2, the Comp3 output pulses are generated.

The H–Drive output is formed by the rising edge of Comp2 output and the rising edge of Comp3 output.

It can be seen from Figure 9, if the H–Phase control is over or under driven, it will reach the upper/lower tip of H–Ramp1, and thus PLL2 will be disturbed.

Figure 9. Horizontal Timing for PLL2 Internal Sections

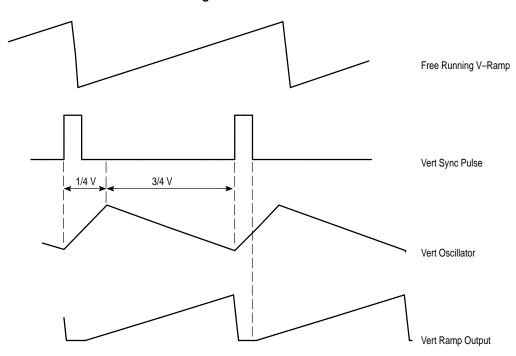

Figure 10. Vertical Section

#### 9. Vertical Frequency Range (Pins 48, 51, 52)

The MC13081X vertical oscillator is an injection–lock type. The device can handle vertical frequency from 45 Hz to 100 Hz.

The internal ramp generator will generate a ramp output in the absence of a V–Sync signal. Upon receiving an external vertical sync pulse, the ramp up portion is forced to retrace, and therefore, the vertical ramp output is synchronized with incoming V–Sync.

The slope of the Vertical Ramp output is directly proportional to the current flowing out of Pin 52. Half of this current is used to charge up the Vertical Ramp Capacitor. As the charging current is increased, so does the ramp slope. External feedback can be provided from Pin 48 to Pins 51 and 52 for linearity adjustment.

#### 10. Vertical Free Running Frequency (Pins 1, 2)

The purpose of the vertical oscillator is to maintain a vertical ramp to the deflection circuitry in the event the vertical sync is not present. Because of the injection—lock type, the free running frequency must be lower than the system's lowest vertical frequency.

While various combinations of C4 and R9 can produce a given frequency, it is recommended C4 be 0.1  $\mu$ F in order to obtain practical values for R9. The free running frequency should be set at about 10% lower than the minimum operating vertical frequency (54 Hz for a 60 Hz system).

R9 is then calculated from:

$$R9 = \frac{V_{CC} - 1.4}{96 \text{ x C4 x FV}} - 2.5 \text{ k}$$

Connecting a potentiometer, (VR2) provides "Vertical Hold" adjustment.

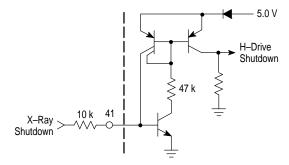

#### 11. X-Ray Shutdown Protection (Pin 41)

The X–Ray input (Pin 41) permits shutting off the horizontal drive, usually by external circuitry which monitors faults within the high voltage supply, such as excess anode current. This input is activated by taking it above  $\approx 0.6~V$  which causes the drive transistor at Pin 43 to be turned on (low) permanently by an internal latch.

An external resistor must be connected to Pin 41 to limit the input current, and to assist with the latching action (see Figure 11). 10 k $\Omega$  is a typical value, but the value can be chosen based on the specifies of the driving circuit. The external resistor reduces the sensitivity of Pin 41 to noise and transients which may otherwise result in false latches.

To resume normal operation (after correction of the fault), lower Pin 41 below 0.4 V. If the external circuit's normal operation does not take it below 0.4 V, but does take it below 0.6 V, then recycle VCC "off"—"on". If the pin is not used, it must be connected to ground.

The minimum holding current to keep the latch on is  $\approx 70~\mu A$ , while the minimum turn—on current is  $\approx 0.4~\mu A$ .

Figure 11. X-Ray Shutdown Circuit

## **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

**USA/EUROPE/Locations Not Listed**: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design-NET.com

**JAPAN**: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298