## Product Preview

# 622Mb/s Fiber Optic Post Amplifier

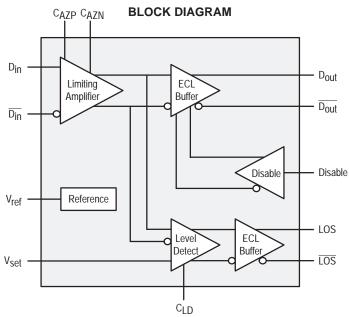

The SX1125A is an integrated limiting amplifier for high frequency fiber optic applications. The device interfaces directly to the trans–impedance amplifier of a typical optical to electrical conversion portion of a fiber optic link. With data rate capabilities in the 622Mb/s range, the high gain limiting amplification of the SX1125A is ideal for high speed fiber optic applications like SONET/SDM, ATM, FDDI, Fibre Channel or Serial Hippi. The device is functionally and pin compatible to the Signetics SA5225 with a significantly higher bandwidth. The CAZP and CAZN inputs to the limiting amplifier provide an auto-zero function to effectively cancel any input offset voltage present in the amplifier.

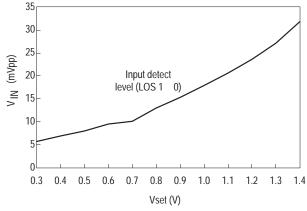

The SX1125A incorporates a programmable level detect function to identify when the input signal has been lost. This information can be fed back to the Disable input of the device to maintain stability under loss of signal conditions. Using the  $V_{\text{Set}}$  pin the sensitivity of the level detect can be adjusted. The  $C_{LD}$  input is used to filter the level detect input so that random noise spikes are filtered out.

The MC10SX1125A is compatible with MECL10H logic levels.

- Wideband Operation: 20kHz to 550MHz

- Programmable Input Signal Level Detection

- Operation with single +5V or standard ECL supply

- Standard 16-lead SOIC Package

- Fully Differential Design to Minimize Noise Affects

- 10KH Compatible

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

#### ON Semiconductor

#### http://onsemi.com

#### MARKING DIAGRAM

SO-16 D SUFFIX CASE 751B

= Assembly Location

WL = Wafer Lot

′ = Year

WW = Work Week

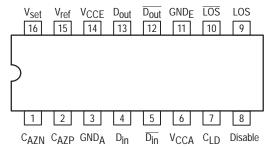

#### **PIN ASSIGNMENT**

Pinout: 16-Lead Plastic Package

(Top View)

#### **ORDERING INFORMATION**

| Device         | Package | Shipping    |  |  |

|----------------|---------|-------------|--|--|

| MC10SX1125AD   | SO-16   | 48 / Rail   |  |  |

| MC10SX1125ADR2 | SO-16   | 2500 / Reel |  |  |

#### **FUNCTION TABLE**

| Pin                                 | Function                                                                                                                                                                                                                                                                                  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>AZN</sub>                    | Auto-zero capacitor pin. A capacitor between this pin and CAZP cancels any offset inherent to the limiting amplifier.                                                                                                                                                                     |

| C <sub>AZP</sub>                    | Auto-zero capacitor pin. A capacitor between this pin and CAZN cancels any offset inherent to the limiting amplifier.                                                                                                                                                                     |

| GND <sub>A</sub>                    | Analog ground pin. Ground for PECL operation or –5.2V for standard ECL operation. GND <sub>A</sub> and GND <sub>E</sub> must be at the same potential.                                                                                                                                    |

| D <sub>in</sub> , D <sub>in</sub>   | Differential data input.                                                                                                                                                                                                                                                                  |

| VCCA                                | Analog power supply pin. +5V for PECL operation or ground for standard ECL operation. V <sub>CCA</sub> and V <sub>CCE</sub> must be at the same potential.                                                                                                                                |

| C <sub>LD</sub>                     | Filter capacitor for the level detect comparator. Capacitor should be connected to VCCA.                                                                                                                                                                                                  |

| Disable                             | When asserted LOW, or left open and pulled LOW via the input pulldown resistor, the output buffer will be enabled and will respond to the input stimulus on the D <sub>in</sub> input. Forcing Disable HIGH will force the D <sub>out</sub> output LOW and its complimentary output HIGH. |

| LOS                                 | Loss of signal. This output will go HIGH when the input signal falls below (V <sub>Set</sub> /100) mV <sub>P-P</sub> .                                                                                                                                                                    |

| GNDE                                | Digital ground pin. Ground for PECL operation or –5.2V for standard ECL operation. GND <sub>A</sub> and GND <sub>E</sub> must be at the same potential.                                                                                                                                   |

| D <sub>out</sub> , D <sub>out</sub> | Differential data outputs.                                                                                                                                                                                                                                                                |

| VCCE                                | Digital power supply pin. +5V for PECL operation or ground for standard ECL operation. V <sub>CCA</sub> and V <sub>CCE</sub> must be at the same potential.                                                                                                                               |

| V <sub>ref</sub>                    | Reference voltage for threshold level set voltage division network (2.64V).                                                                                                                                                                                                               |

| V <sub>set</sub>                    | Input threshold level detect setting input. Input generated from voltage divider between V <sub>ref</sub> and GND <sub>A</sub> .                                                                                                                                                          |

**Figure 1. Typical Operating Circuit**

#### **Coupling Capacitors**

The SX1125A inputs must be AC coupled to allow proper operation of the offset correction function. The coupling capacitors,  $C_{in}$ , must be large enough to pass the lowest input frequency of interest.

$$C_{in} = \frac{1}{2\pi (R_{in}) (f_{low})}$$

where  $R_{in} = input resistance = 5000\Omega$

$f_{low}$  = lowest frequency.

#### **Auto-zero Capacitors**

A feedback amplifier is used to cancel the offset voltage of the forward signal path, so the input to the internal ECL comparator is at its toggle point in the absence of any input signal. The time constant of the cancelling circuitry is set by an external capacitor (CAZ) connected between Pins 1 and 2. The formula for the calculation of the auto–zero capacitor is:

$$C_{AZ} = \frac{150}{2\pi \ (R_{AZ}) \ (f_{IOW})}$$

where  $R_{AZ}$  = internal driving impedance = 290k $\Omega$

$f_{low}$  = lowest frequency.

#### Input Signal Level Detector

The SX1125A allows for user programmable input signal level-detection and can automatically disable the switching of its ECL data output if the input level is below a set threshold. This prevents the outputs from reacting to noise in the absence of a valid input signal, and ensures that data will only be transmitted when the signal-to-noise ratio is sufficient for low bit-error-rate system operation. Complimentary ECL flags (LOS and LOSB) indicate whether the input signal is above or below the desired threshold level. In the level detect system, the input signal is amplified and rectified before being compared to a programmable reference. A filter is included to prevent noise spikes from triggering the level-detector. The filter has a nominal 1 us time constant, and additional filtering can be achieved by using an external capacitor (CLD) from Pin 7 to V<sub>CCA</sub> (the internal driving impedance is nominally 28k). The formula for the calculation of the CLD capacitor

$$C_{LD} = \frac{t}{Rz}$$

where

$R_Z$  = internal driving impedance =  $28k\Omega$ t = LOS filter time constant.

#### DC CHARACTERISTICS (GNDA = GNDE = Ground; VCCA = VCCE = 4.5V to 5.5V)

| Symbol | Characteristic                          | Min   | Тур | Max | Unit              | Condition |

|--------|-----------------------------------------|-------|-----|-----|-------------------|-----------|

| VIN    | Input Signal Voltage (Din) Single-Ended | 0.008 |     | 1.5 | V <sub>P-P</sub>  | Note 1.   |

| Vos    | Input Offset Voltage                    |       |     | 50  | μV                |           |

| ٧N     | Input RMS Noise                         |       |     | 225 | μV                |           |

| VTH    | Input Level Detect Programmability      | 8.0   |     | 20  | mV <sub>P-P</sub> |           |

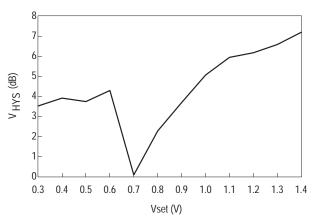

| VHYS   | Level Detect Hysteresis                 | 1.5   | 2.5 | 7.0 | dB                | Note 2.   |

| lн     | Input HIGH Current Disable              |       |     | 150 | μΑ                |           |

| Icc    | Power Supply Current                    |       | 33  | 45  | mA                |           |

- 1. This device functions with  $V_{in}$ min =  $6mV_{P-P}$ , but with increased BER (See BER data).

- 2. This device has an anomoly in VHYS when 0.65 < VSET < 0.75V. Operation in this region is not recommended.

Figure 2. LOS versus Vset  $(T_A = 25^{\circ}C)$

Figure 3. LOS Hysteresis ( $T_A = 25^{\circ}C$ )

#### I/O DC CHARACTERISTICS<sup>1</sup>

|                 |                                                                                               | -40           | )°C           | 0°C           |               | 25°C          |               | 85°C          |               |      |

|-----------------|-----------------------------------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|------|

| Symbol          | Characteristic                                                                                | Min           | Max           | Min           | Max           | Min           | Max           | Min           | Max           | Unit |

| VOH             | Output HIGH Voltage<br>$V_{CC} = -4.5 \text{ to } -5.5 \text{V}$<br>$V_{CC} = 5.0 \text{V}^2$ | 1080<br>3920  | -890<br>4110  | 1020<br>3980  | -840<br>4160  | -980<br>4020  | -810<br>4190  | -910<br>4090  | -720<br>4280  | mV   |

| V <sub>OL</sub> | Output LOW Voltage $V_{CC} = -4.5 \text{ to } -5.5 \text{V}$ $V_{CC} = 5.0 \text{V}^2$        | -1950<br>3050 | -1650<br>3350 | -1950<br>3050 | -1630<br>3370 | -1950<br>3050 | -1630<br>3370 | -1950<br>3050 | -1595<br>3405 | mV   |

| VIH             | Input HIGH Voltage <sup>3</sup> $V_{CC} = -4.5 \text{ to } -5.5V$ $V_{CC} = 5.0V^{2}$         | -1230<br>3770 | -890<br>4110  | -1170<br>3830 | -840<br>4160  | -1130<br>3870 | -810<br>4190  | -1060<br>3940 | -720<br>4280  | mV   |

| V <sub>IL</sub> | Input LOW Voltage <sup>3</sup> $V_{CC} = -4.5 \text{ to } -5.5V$ $V_{CC} = 5.0V^{2}$          | -1950<br>3050 | -1500<br>3500 | -1950<br>3050 | -1480<br>3520 | -1950<br>3050 | -1480<br>3520 | -1950<br>3050 | -1445<br>3555 | mV   |

| I <sub>IL</sub> | Input LOW Current <sup>3</sup>                                                                | 0.5           |               | 0.5           |               | 0.5           |               | 0.3           |               | μΑ   |

<sup>1. 10</sup>SX circuits are designed to meet the DC specifications shown in the table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500lfpm is maintained. Outputs are terminated through a  $50\Omega$  resistor to -2.0 volts except where otherwise specified on the individual data sheets.

#### AC CHARACTERISTICS ( $V_{CCA} = V_{CCE} = 4.5V$ to 5.5V)

| Symbol                          | Characteristic                 | Min | Тур | Max | Unit | Condition |

|---------------------------------|--------------------------------|-----|-----|-----|------|-----------|

| BW <sub>min</sub>               | Lower –3dB Bandwidth           |     |     | 20  | kHz  |           |

| BW <sub>max</sub>               | Upper –3dB Bandwidth           | 550 |     |     | MHz  |           |

| t <sub>PWD</sub>                | Pulse Width Distortion         |     |     | 70  | ps   |           |

| t <sub>r</sub> , t <sub>f</sub> | Rise/Fall Times                | 150 | 250 | 650 | ps   | 20% – 80% |

| R <sub>AZ</sub>                 | Auto-Zero Output Resistance    | 200 | 325 | 450 | kΩ   |           |

| R <sub>F</sub>                  | Level Detect Filter Resistance | 14  | 25  | 41  | kΩ   |           |

| t <sub>LD</sub>                 | Level Detect Time Constant     | 0.5 | ·   | 4.0 | μs   |           |

#### BER (Bit-Error-Rate)

Using a 622Mb/s SONET STS-12 pattern, the SX1125A shows the following typical BERs at  $T_A = 25$ °C:

| Input V <sub>pp</sub> | BER    |  |  |

|-----------------------|--------|--|--|

| 6mV                   | 4E–13  |  |  |

| 7mV                   | <1E–14 |  |  |

| 8mV                   | <5E–15 |  |  |

<sup>2.</sup> Limits hold for  $V_{CC}$  = 5.0V only. Parametric values will vary 1:1 with any variation of  $V_{CC}$ .

3. Parametric values for the Disable input only.

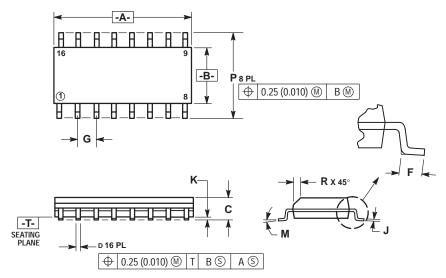

#### **PACKAGE DIMENSIONS**

SO-16 **D SUFFIX** CASE 751B-05 **ISSUE J**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIM   | ETERS | INCHES    |       |  |

|-----|----------|-------|-----------|-------|--|

| DIM | MIN      | MAX   | MIN       | MAX   |  |

| Α   | 9.80     | 10.00 | 0.386     | 0.393 |  |

| В   | 3.80     | 4.00  | 0.150     | 0.157 |  |

| С   | 1.35     | 1.75  | 0.054     | 0.068 |  |

| D   | 0.35     | 0.49  | 0.014     | 0.019 |  |

| F   | 0.40     | 1.25  | 0.016     | 0.049 |  |

| G   | 1.27 BSC |       | 0.050 BSC |       |  |

| J   | 0.19     | 0.25  | 0.008     | 0.009 |  |

| K   | 0.10     | 0.25  | 0.004     | 0.009 |  |

| M   | 0°       | 7°    | 0°        | 7°    |  |

| Р   | 5.80     | 6.20  | 0.229     | 0.244 |  |

| R   | 0.25     | 0.50  | 0.010     | 0.019 |  |

## **Notes**

## **Notes**

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affliliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor - European Support

German Phone: (+1) 303–308–7140 (M–F 1:00pm to 5:00pm Munich Time) Email: ONlit–german@hibbertco.com

ch Phone: (+1) 303–308–7141 (M–F 1:00pm to 5:00pm Toulouse Time)

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303–308–7142 (M-F 12:00pm to 5:00pm UK Time)

Email: ONlit@hibbertco.com

EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781

\*Available from Germany, France, Italy, England, Ireland

#### CENTRAL/SOUTH AMERICA:

Spanish Phone: 303-308-7143 (Mon-Fri 8:00am to 5:00pm MST)

Email: ONlit-spanish@hibbertco.com

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support

Phone: 303-675-2121 (Tue-Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong & Singapore:

001-800-4422-3781 Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–8549

**Phone**: 81–3–5740–2745 **Email**: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.