# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

## MC10318P

#### HIGH SPEED 8-BIT DIGITAL-TO-ANALOG CONVERTER

The MC10318 is a high-speed D/A converter capable of data conversion rates in excess of 25 MHz. The digital inputs are compatible with MECL 10,000 Series Logic. Complementary current outputs provide up to 56 mA full scale capability. The MC10318 is 8-bit accurate, and over temperature to meet the requirements of many applications, including: high-speed instrumentation and test equipment, storage oscilliscopes, display processing, radar systems, and digital video systems (broadcast and receiver applications).

- Fast Settling Time 10 ns (Typ to ±0.19%)

- 8-Bit Accurate (0.19%)

- Inputs MECL 10,000 Compatible

- Complementary Current Outputs

- Output Compliance: −1.3 V to +2.5 V

- Single MECL Supply: −5.2 V

- Standard 16-Pin Dual-In-Line Package

#### HIGH SPEED 8-BIT DIGITAL-TO-ANALOG CONVERTER

SILICON MONOLITHIC INTEGRATED CIRCUIT

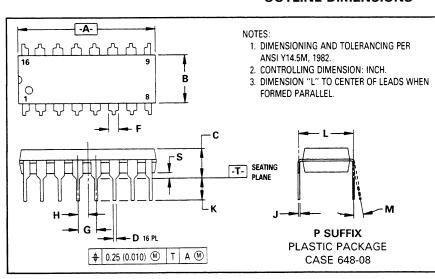

P SUFFIX

PLASTIC PACKAGE

CASE 648

## **MAXIMUM RATINGS** ( $T_A = +25^{\circ}C$ unless otherwise noted.)

| Rating                                                          | Symbol                | Value                    | Unit |

|-----------------------------------------------------------------|-----------------------|--------------------------|------|

| Power Supply Voltage                                            | VEE                   | -6.0 to +0.5             | Vdc  |

| Digital Input Voltage                                           | VI                    | 0 to VEE                 | Vdc  |

| Applied Output Voltage                                          | νo                    | +5.0 to V <sub>EE</sub>  | Vdc  |

| Reference Current                                               | I <sub>ref</sub> (12) | 5.0                      | mA   |

| Output Current                                                  | IFS                   | - 75                     | mA   |

| Reference Amplifier Input Range                                 | V <sub>ref</sub>      | + 0.5 to V <sub>EE</sub> | Vdc  |

| Reference Amplifier Differential Inputs                         | V <sub>ref</sub> (D)  | ± 5.0                    | Vdc  |

| Operating Temperature Range                                     | TA                    | 0 to +70                 | °C   |

| Storage Temperature Range                                       | T <sub>stg</sub>      | -65 to +150              | °C   |

| Junction Temperature                                            | TJ                    | + 130                    | °C   |

| Thermal Resistance, Still Air Junction to Ambient With 500 LFPM | $R\theta$ JA          | 67<br>50                 | °C/W |

## **DC CHARACTERISTICS** ( $V_{EE} = -5.2 \text{ V}, \pm 5\% \text{ T}_{A} = 0^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}$ after thermal equilibrium is reached.)

| Characteristics                                                                                                                                                              | Fig. | Symbol                   | Min         | Тур           | Max    | Unit   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------|-------------|---------------|--------|--------|

| Nonlinearity (Integral) (Pin 14 or 15)<br>( $\alpha$ IFS = 51 mA, 25.5 mA)                                                                                                   |      |                          |             |               | ± 0.19 | %/FS   |

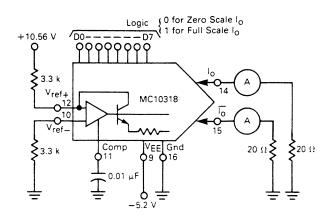

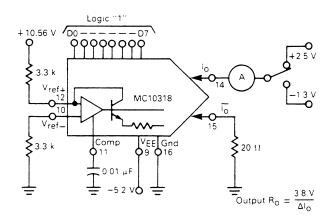

| Zero Scale Output Current (Pin 14 or 15) (T <sub>A</sub> = 25°C)                                                                                                             | 10   | <sup>I</sup> ZS          |             | 5.0           | 50     | μΑ     |

| Zero Scale Output Current Temperature Drift (Pin 14 or 15) $0 < T_{\mbox{$\Delta$}} < 25^{\circ}\mbox{C}$ $25^{\circ}\mbox{C} < T_{\mbox{$\Delta$}} < 70^{\circ}\mbox{C}$    |      | <sup>I</sup> ZS/ΔT       | _           | ± 17<br>± 2.0 |        | nA/°C  |

| Full Scale Output Current (Pin 14 or 15)<br>(I <sub>ref</sub> = 3.2 mA, D0-D7 = 1)                                                                                           | 10   | IFS                      | - 46        | - 51          | - 56   | mA     |

| Full Scale Output Current Temperature Drift (Pin 14 or 15) $0 < T_{\mbox{$\Delta$}} < 25^{\circ}\mbox{C}$ $25^{\circ}\mbox{C} < T_{\mbox{$\Delta$}} < 70^{\circ}\mbox{C}$    |      | ΔI <sub>FS/°</sub> C     | _           | ± 50<br>± 10  | _      | ppm/°C |

| Full Scale Output Sensitivity to Power Supply Variations (Pin 14 or 15) $(-4.94 \text{ V} < \text{V}_{\text{EE}} < -5.46 \text{ V})$                                         |      | IFSPSS                   | <del></del> | ± 0.005       | ± 0.02 | %/%    |

| Full Scale Symmetry (IFS — IFS)                                                                                                                                              | 10   | l <sub>FSS</sub>         |             | ± 21          | ± 100  | μΑ     |

| Output Voltage Compliance (Pin 14 or 15)<br>Full Scale Current Change $\leq$ 1/2 LSB<br>(Specified Nonlinearity) ( $T_A = 25^{\circ}C$ )                                     |      | Voc                      | - 1.3       | _             | + 2.5  | V      |

| Output Resistance (Pin 14 or 15) (T <sub>A</sub> = 25°C)                                                                                                                     | 12   | RO                       |             | 69            | _      | kΩ     |

| Reference Amplifier Offset Voltage (T <sub>A</sub> = 25°C)                                                                                                                   |      | V <sub>IO</sub>          | _           | ± 3.2         | _      | mV     |

| Reference Amplifier Offset Voltage Temperature Drift $0 < T_{\mbox{$\Delta$}} < 25^{\circ}\mbox{C}$ $25^{\circ}\mbox{C} < T_{\mbox{$\Delta$}} < 70^{\circ}\mbox{C}$          |      | $\Delta V_{IO/\Delta T}$ |             | ± 10<br>± 4.0 |        | μV/°C  |

| Reference Amplifier Bias Current (Pin 10)<br>(I <sub>ref</sub> = 3.2 mA)                                                                                                     |      | ΙΒ                       | _           | 4.0           | 15     | μΑ     |

| Reference Amplifier Bias Current Temperature Drift ( $I_{ref}$ = 3.2 mA) 0 < $T_A$ < 25°C 25°C < $T_A$ < 70°C                                                                |      | ΔΙ <sub>ΙΒ/Δ</sub> Τ     | _           | -40<br>-10    | _      | nA/°C  |

| Reference Amplifier Common Mode Range $(V_{EE} = -5.2 \text{ V}) (T_A = 25^{\circ}\text{C})$                                                                                 |      | V <sub>ICR</sub>         |             | ± 1.15        |        | V      |

| Reference Amplifier Common Mode Rejection Ratio $(T_A = 25^{\circ}C) (I_{ref} = 3.2 \text{ mA}, V_{ICR} = 0 \text{ to } -2.0 \text{ V}, \text{Pins } 1-8 = \text{Logic } 1)$ |      | VICMRR                   |             | 58            | _      | dB     |

| Reference Amplifier Input Impedance<br>(Pin 10) (T <sub>A</sub> = 25°C)                                                                                                      |      | R <sub>IN</sub>          | _           | 1.0           |        | MΩ     |

| Power Supply Current (Pins 1 thru 8 Open, $I_{ref} = 3.2 \text{ mA}$ , Includes $I_0 + \overline{I_0}$ )                                                                     |      | lEE                      | _           | 90            | 130    | mA     |

| Characteristics                                                                                          | Fig. | Symbol          | Min | Тур | Max | Unit   |

|----------------------------------------------------------------------------------------------------------|------|-----------------|-----|-----|-----|--------|

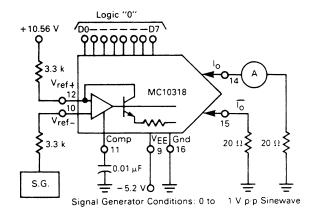

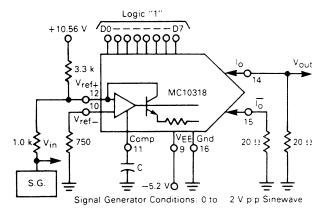

| Feedthrough Current — All Bits Off  f = 10 kHz                                                           | 9    | l <sub>FC</sub> |     | 2.0 |     | μΑ р-р |

| f = 10 kHz                                                                                               |      |                 | _   | 18  | _   |        |

| Distortion — ((a l <sub>0</sub> )                                                                        |      |                 |     |     |     | %      |

| (Sinewave applied to reference amplifier Input, D0-D7 = Logic 1) $C = 0.01 \mu F$ , $f = 20 \text{ kHz}$ |      | THD             |     | 1.0 |     |        |

| $C = 0.01 \mu F$ , $f = 65 \text{ kHz}$                                                                  |      | THD             |     | 5.0 | _   |        |

| $C = 0.001 \mu F$ , $f = 340 \text{ kHz}$                                                                |      | THD             | _   | 1.0 |     |        |

| $C = 0.001 \mu\text{F},  f = 600 \text{kHz}$                                                             |      | THD             |     | 2.0 |     |        |

| C = 240 pF, f = 600 kHz                                                                                  |      | THD             |     | 0.8 |     |        |

| Reference Amplifier Slew Rate (Step change at Pin 10, all bits on)                                       | 13   |                 |     |     |     | mA/μs  |

| $C = 0.01 \mu\text{F}$                                                                                   |      |                 | _   | 0.5 | _   |        |

| $C = 0.001 \mu\text{F}$                                                                                  |      |                 | _   | 5.0 | _   |        |

| C = 240 pF                                                                                               |      |                 |     | 20  |     |        |

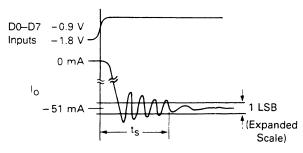

| Settling Time (to $\pm 0.19\%$ of Full Scale)                                                            | 1,22 | t <sub>S</sub>  |     |     |     | ns     |

| 1 LSB Change                                                                                             |      |                 |     | 7.0 | _   |        |

| All Bits Switched                                                                                        |      |                 |     | 10  |     |        |

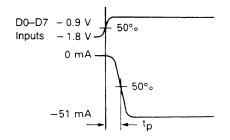

| Propagation Delay                                                                                        | 2    | tp              |     | 5.0 | _   | ns     |

| Output Glitch Energy (with De-Skewing Capacitors)<br>(Input Change: 011111111 ←→ 10000000)               |      |                 |     | 50  | _   | LSB-ns |

| Glitch Duration                                                                                          |      |                 | _   | 5.0 | _   | ns     |

| DIGITAL INPUT VOLTAGE LEVELS |                     |         |                      |         |  |  |  |

|------------------------------|---------------------|---------|----------------------|---------|--|--|--|

|                              | Volts (See Note)    |         |                      |         |  |  |  |

| TA                           | V <sub>IH</sub> max | VIHAmin | V <sub>ILA</sub> max | VĮLmin  |  |  |  |

| 0°C                          | - 0.845             | - 1.151 | - 1.516              | - 1.868 |  |  |  |

| 25°C                         | - 0.810             | - 1.105 | - 1.505              | - 1.850 |  |  |  |

| 70°C                         | - 0.727             | - 1.052 | 1.480                | - 1.830 |  |  |  |

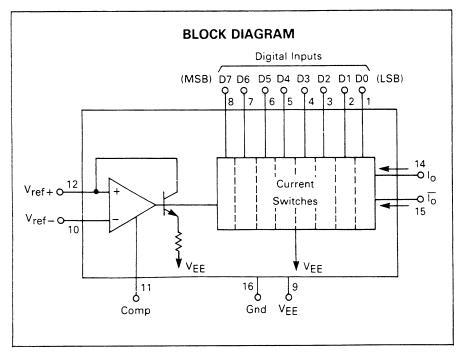

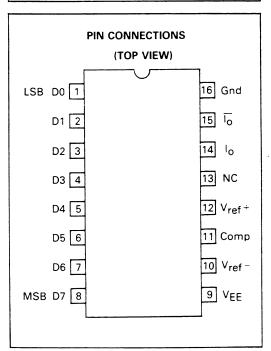

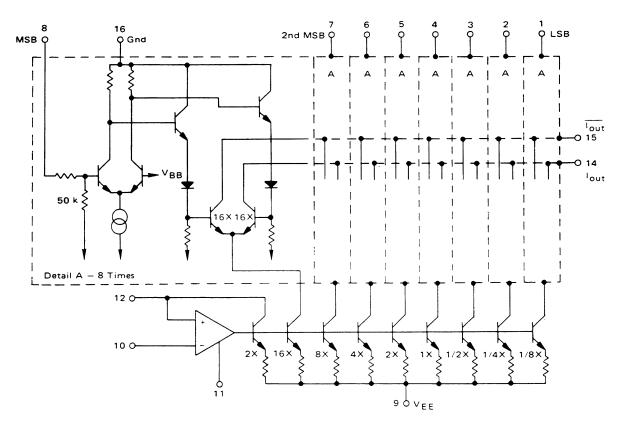

#### **FUNCTIONAL PIN DESCRIPTION**

**D0-D7 (Pins 1-8)** The eight ECL digital inputs compatible with MECL 10,000 series devices. Logic "0" is nominally -1.8 V, and Logic "1" is nominally -0.9 V.

$V_{ref_-}$  (Pin 10) The high impendance input of the reference amplifier. This input is normally grounded, but may be used for ac applications involving modulation, digitally controlled gain, etc. Normal operating range is from ground to  $V_{EE} + 2.9$  V (nominally -2.3 V).

V<sub>ref</sub>\_ (Pin 12) The noninverting input of the reference amplifier. The inverted output of the reference amplifier is internally fed back to this input, thus causing it to track Pin 10. A nominal 3.2 mA is to be supplied to this pin from an external (stable and noise free) voltage source and current setting resistor.

Comp. (Pin 11) A nominal 0.01  $\mu F$  capacitor is connected to this pin and to ground to stabilize the reference amplifier. Lower values of capacitor may be used if a good PC board layout is used, where frequencies higher than 10 kHz are applied to the reference amplifier.

$I_{o}$ ,  $\overline{I_{o}}$  (Pins 14,15) The complementary current outputs. Current flow is into the DAC and varies linearily with  $I_{ref}$  and the digital input code.  $I_{out}$  increases as the digital input increases. Output compliance range is -1.3 V to +2.5 V.

**VEE (Pin 9)** The power supply pin. VEE is nominal -5.2 V,  $\pm 5\%$ .

**Gnd (Pin 16)** The ground pin. This line should be as noise-free as possible in order to obtain a noise-free output.

NOTE:  $V_{EE} = -5.2 \text{ V}$ ,  $\pm 5\%$  Inputs are MECL 10,000 compatible within the temperature and power supply ranges listed. See MECL System Design Handbook for further details. See Fig. 19 in this data sheet.

FIGURE 1 — SETTLING TIME

FIGURE 2 — PROPAGATION DELAY

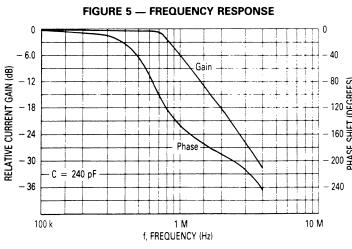

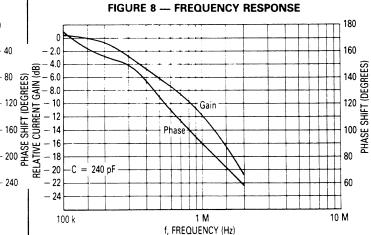

#### REFERENCE AMPLIFIER RESPONSE

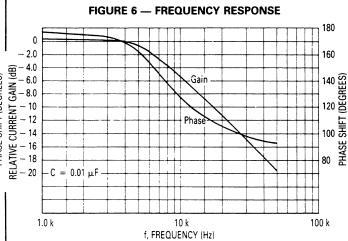

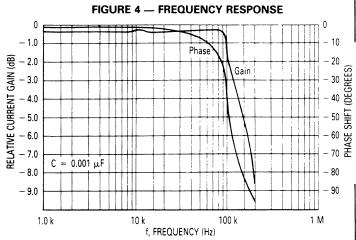

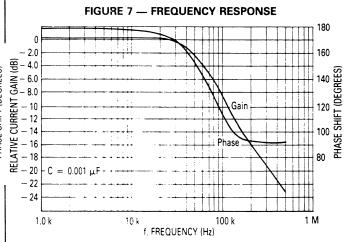

Inverting Input (V<sub>ref</sub>\_) Test Circuit of Fig. 14 Noninverting Input (V<sub>ref+</sub>) Test Circuit of Fig. 11

#### **TEST CIRCUITS**

#### FIGURE 9 — FEEDTHROUGH MEASUREMENT

#### FIGURE 10 — ZERO/FULL SCALE CURRENT

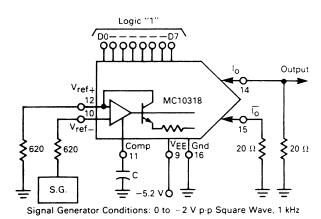

#### FIGURE 11 — GAIN/PHASE MEASUREMENT

Reference dB Level: See Text

See Figures 6-8

#### FIGURE 12 — OUTPUT RESISTANCE

#### FIGURE 13 -- REFERENCE AMPLIFIER SLEW RATE

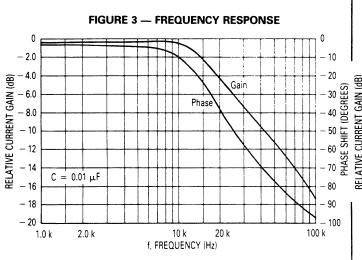

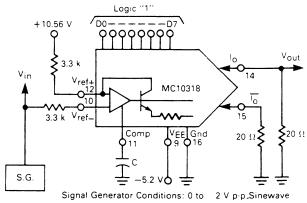

FIGURE 14 - GAIN/PHASE MEASUREMENT

Reference dB Level: See Text

See Figures 3-5

#### **OPERATIONAL INFORMATION**

#### **Typical DAC Operation**

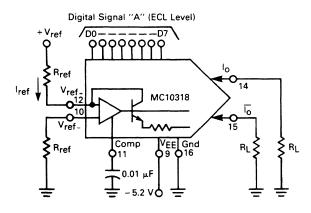

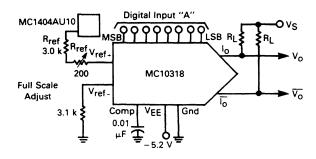

The MC10318 is designed to be operated with an I $_{\rm ref}$  (Pin 12) of 3.2 mA, resulting in a full scale output current (I $_{\rm O}$ ) of 51 mA when D0 through D7 are at a Logical ''1'' ( - 0.9 V). The transfer equation for I $_{\rm O}$  is therefore:

$$I_0 = I_{ref} \times 16 \times \frac{A}{256}$$

("A" is the binary value of the digital input).

Typically  $V_{ref}$  (Pin 10) is connected to Ground, and  $I_{ref}$  is supplied to  $V_{ref}$ . (Pin 12) by means of an external supply  $V_r$  (see Figure 15). A resistor inserted between Pin 10 and Ground will minimize temperature drift, and should have a value equivalent to that connected to Pin 12. Any noise or ripple present on the reference current will be present on the output current, and the stability of the reference directly affects the output current's stability. The ground connection for  $V_{ref}$  should be chosen with care so as not to pick up noise (digital or otherwise).

The complementary outputs  $(I_0 \text{ and } \overline{I_0})$  are high impedance current sources having a compliance range of 3.8 V (-1.3 to +2.5 V). I<sub>O</sub> increases with increasing digital input, while  $\overline{I_0}$  decreases. Their sum is a constant equal to 15.94 x I<sub>ref</sub>. Neither output can be left open an unused output must be connected to ground or a load resistor. Typically both outputs should be loaded similarly for best speed and accuracy performance. A compensation capacitor must be connected between Pin 11 and Ground to stabilize the amplifier. A 0.01 µF ceramic is satisfactory for most applications, and should be located physically close to the device. The ground side of the capacitor should be noise-free. When operated as above, the output(s) will be controlled by the digital inputs, and the MC10318 can be used for various functions such as waveform generation, process control, ADC conversion, and others.

#### FIGURE 15 — TYPICAL OPERATION

#### Common Mode Range — AC Operation

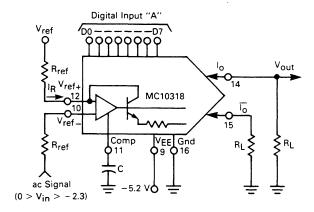

The reference amplifier inputs (Pins 10 and 12) may be used to control the output current in conjunction with the digital inputs for applications such as digitally controlled gain of an ac signal, digitally controlled amplitude modulation, and others. Either the positive or negative input of the reference amplifier may be used, depending on the application. There are, however, differences in the manner in which an ac signal is to be applied.

1) When applying a signal to the  $V_{ref-}$  (Pin 10) input (See Figure 16), the signal must be kept within the range of 0 to -2.3 V. The input has a high impedance (typically 1 Megohm). The  $V_{ref-}$  pin (Pin 12) will track this signal, causing  $I_{ref}$  to vary, in turn causing  $I_0$  and  $\overline{I_0}$  to vary. The ac component of  $I_0$  (and  $\overline{I_0}$ ) will be in phase with the applied signal. The ac gain of the circuit shown is:

$$\frac{\Delta V_{out}}{\Delta V_{in}} = \frac{A \times R_L}{16 \times R_R}$$

Applying the above to the test circuit of Figure 14 yields a gain of 0.0966, which is the 0 dB reference level for the curves of Figures 3–5.

FIGURE 16 — AC OPERATION, NONINVERTING

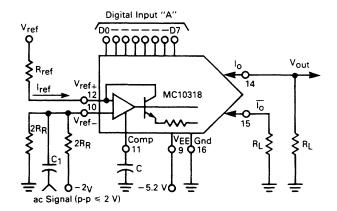

If the peak values of the applied ac signal cannot be kept within the above mentioned voltage range, an alternate circuit is shown in Figure 17.

FIGURE 17 — AC OPERATION, NONINVERTING (ALTERNATE)

The compensation capacitor (Pin 11) of Figures 16 and 17 is to be nominally 0.01  $\mu$ F for best overall stability. If frequencies higher than 10 kHz are to be applied to the reference input, a smaller value capacitor will be necessary as indicated by Figures 3–5. However, greater care will be necessary in the breadboarding and PC layout to prevent instabilities caused by unintended feedback paths.

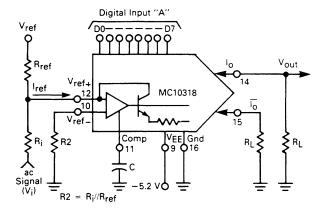

2) When applying a signa! to the  $V_{ref}$ . (Pin 12) input (see Figure 18), the effect is a direct modulation of the reference current supplied by  $V_{ref}$ . Pin 12 is a virtual ground, and therefore the current  $I_{ref}$  is equal to:

$$I_{ref} = \frac{V_{ref}}{R_{ref}} + \frac{V_i}{R_i}$$

$l_{\rm O}$  and  $\overline{l_{\rm O}}$  will vary with the reference current, but the ac component will be  $180^{\rm c}$  out of phase with the applied signal. The ac gain of the circuit shown is:

$$\frac{\Delta V_{\text{out}}}{\Delta V_{i}} = \frac{-A \times R_{L}}{16 \times R_{i}}$$

Applying the above to the test circuit of Figure 11 yields a gain of -0.3188, which is the 0 dB reference level for the curves of Figures 6–8.

The reference current  $I_{ref}$  must always flow **into** Pin 12, requiring that the values of  $V_{ref}$ ,  $R_{ref}$ ,  $R_i$ , and  $V_i$  be chosen so as to guarantee this.

FIGURE 18 - AC OPERATION, INVERTING

The compensation capacitor (Pin 11) of Figure 18 is to be nominally 0.01  $\mu F$  for best overall stability. If frequencies higher than 4 kHz are to be applied, a smaller value capacitor will be necessary as indicated by Figures 6–8. However, greater care will be necessary in the breadboarding and PC layout to prevent instabilities caused by unintended feedback paths.

#### **DIGITAL INTERFACE**

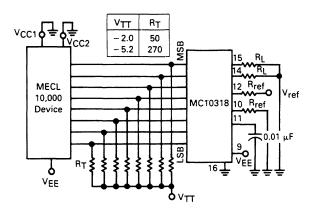

The digital inputs (Pins 1–8) are compatible with MECL 10,000 series devices over the temperature and  $V_{FF}$  range listed on page 3. Standard MECL 10,000 de-

sign guidelines apply, and should be implemented. Maximum speed response requires careful PC board layout and choice of components. See Motorola's MECL System Design Handbook for a complete explanation of specifications and characteristics. Figure 19 shows a typical ECL interconnection with recommended values for optimum speed performance. Other values of  $R_{T}$  and  $V_{TT}$  may be used, but at a slight increase in overall propagation delay. Unused inputs should not be left open, but should be connected to a Logic 0 ( $\sim$  1.8 V), or a Logic 1 ( $\sim$ 0.9 V). Resistors  $R_{T}$  should be connected at the receiving end of the interconnection, i.e. physically located adjacent to the MC10318 inputs, for best speed performance.

FIGURE 19 - STANDARD MECL INTERFACE

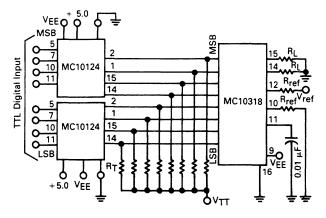

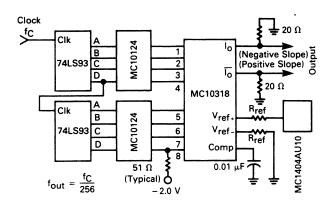

Interfacing a TTL system to the MC10318 is easily accomplished by the use of two MC10124 devices (see Figure 20).

FIGURE 20 - TTL INTERFACE

### **OUTPUT CHARACTERISTICS**

The MC10318 DAC has been designed specifically for high speed operation by incorporating ECL structured inputs, bit switching circuits which are small in size and simple in operation, and high-current complementary outputs (which permits current steering rather than on-off switching). In this manner, very short propagation delays and settling times are possible.

#### **Output Glitch**

All DAC's will produce a glitch at the output when various bits are switched in opposite directions, due to differences in transition times of the switching transistors. During the switching period, typically the output current will momentarily seek a value other than the desired final value, and then return to and settle at the final value. This glitch can be several LSBs in magnitude, but of a very short duration (5–6 ns). In some instances, the output current may overshoot, and then undershoot before reaching the final value, resulting in a "glitch doublet."

The glitch is most apparent when switching the higher order bits, and in the case of the MC10318, the maximum glitch generally occurs when switching bit D5 and the lower 5 bits (typically 85 LSB·ns). Switching bit D6 and the lower 6 bits produces a similar but slightly reduced glitch. Switching bit D7 and the seven lower bits (major carry transition) results in a glitch of typically 50 LSB·ns, with an amplitude of 17 LSBs. Switching of lower order bits while maintaining the higher ones constant produces glitches typically of less than 1 LSB in magnitude, and less than 10 ns in duration, and are generally not considered to be of significance.

Glitches can be removed from the output by filtering, or by using a sample-and-hold circuit on the output, or by using de-skewing capacitors on the higher order bits.

Output glitch is generally specified in terms of glitch energy, which is the area under the curve of the waveform. Most glitches appear as a triangle, and so the area is simply  $\frac{1}{2} \times t \times \Delta l$ , where t is the duration of the glitch, and  $\Delta l$  is the amplitude normalized in terms of LSBs. In the case of a glitch doublet, having both positive and negative amplitude, the areas are summed algebraically. It is possible, therefore to have a glitch with zero energy, although having amplitudes of several LSB's.

In applications where the output glitch is of concern, steps can be taken to minimize its magnitude. The two main factors to consider are: 1) That the 8 bits of data reach the MC10318 simultaneously; and 2) that the PC board layout prevent noise from reaching the MC10318.

It is obvious that if the updated 8 bits are not received by the DAC simultaneously, even an ideal DAC will not produce an ideal waveform. Where simultaneous transmission by the sending device(s) cannot be guaranteed (such as two cascaded counters), latches should be used ahead of the MC10318. The latches should then be clocked after their inputs have settled. Suggested latches are the MC10133/MC10153/MC10168 at the ECL level, and the SN74LS273 at the TTL level.

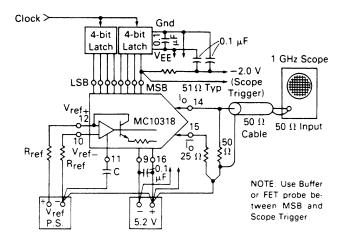

#### FIGURE 21 — PRECISION HIGH-SPEED MEASUREMENTS

#### **Nonlinearity**

Integral nonlinearity has been specified, rather than differential nonlinearity, as this is a better indicator of the maximum error to be expected. Integral nonlinearity is measured by comparing the **actual** output (at each digital value) with the expected ideal value. The expected values lie along a straight line between zero and the full scale output current. The MC10318 will not differ from the **ideal** value by more than the specified nonlinearity.

#### **PC Board Layout**

A proper PC board layout is very important in order to obtain the full benefits of the MC10318's high-speed characteristics. Each of the current paths ( $I_0$ ,  $\overline{I_0}$ ,  $I_{\text{EE}}$ ,  $I_{\text{ref}}$ , etc.) must be carefully considered to avoid interference, and isolation from other circuits on the board (particularly digital) is essential. Bypassing of all supplies is, of course, necessary, and in some cases, bypassing to VEE may be more beneficial than bypassing to Ground. Sockets should be avoided as the extra pin-to-pin capacitance can slow down the ECL edges and/or the output settling time. PC board layout should include the following guidelines:

- A dedicated ground track from the power supply to Pin 16 (Gnd);

- A single dedicated ground track from the power supply to the **two** load resistors associated with I<sub>O</sub> and I

— this results in a constant dc current in this track;

- 3) A separate ground for the circuitry associated with V<sub>ref</sub>, V<sub>ref</sub>, and Comp (Pins 10–12). Any noise on this ground will feed through the reference amplifier and show up on the output;

- 4) The compensation capacitor must be physically adjacent to Pin 11;

- 5) Bypass  $V_{EE}$  (Pin 9) with a 0.1  $\mu$ F to the ground line feeding the load resistors;

- 6) Provide proper terminations at the inputs the suggested values for R<sub>T</sub> and V<sub>TT</sub> will provide best speed response;

- 7) Bypass V<sub>TT</sub> to V<sub>EE</sub> and to Ground with 0.1  $\mu$ F capacitors;

- 8) If the power supplies are not on the same PC board with the MC10318, bypass  $V_{EE}$  and  $V_{TT}$  to Ground with (minimum) 10  $\mu$ F and 0.1  $\mu$ F where the supply voltages enter the PC board;

- 9) Use of a ground plane is mandatory in all high speed applications;

- 10) Keep all TTL circuitry tracks separate from the MC10318 by means of ground tracks and/or ground planes.

Many of the above points have to do with isolating the device from all other circuitry, since most applications involve using the MC10318 (which is 50% analog) in a (noisy) digital circuit. If the output voltage swing is typically 1 volt, then 1 LSB is approximately 4 mV. Since TTL circuitry can easily generate 50 mV noise on the ground line, the need for isolation is apparent.

The above points are not the only ones to be considered by the designer, as each application will have its own individual additional requirements.

#### **Propagation Delay**

The propagation delay is measured from the 50% point of the input transition to the 50% point of the output transition. Since the typical propagation delay is on the order of 5 ns, see Figure 21 and the information in Settling Time if this parameter is to be measured. Switching 1 LSB or all of the bits simultaneously produces no significant difference in propagation delay.

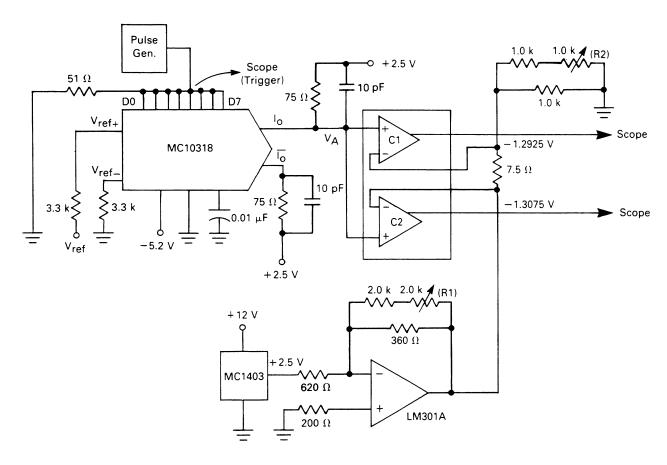

FIGURE 22 — SETTLING TIME MEASUREMENT

#### NOTES:

- 1) Pulse generator outputs -0.9 V to -1.8 V,  $t_r$  and  $t_f \approx 2 \text{ ns}$ .

- 2) Adjust  $V_{ref}$  for full scale output at  $V_A = -1.3000 \ V$ .

- 3) Adjust R1 for -1.3075 V at input of lower comparator.

- 4) Adjust R2 for -1.2925 V at input of upper comparator.

- 5) R1, R2 are 20 turn trimpots.

- 6) Keep all wiring as short, tidy as possible isolate all digital and analog supplies, grounds, signal lines, etc.

- Heavily bypass all supplies at each device, and reference (-) inputs to the comparators.

- 8) Comparators are high-speed devices, such as AM687ADL.

- 9) Account for comparator offset when setting reference values.

#### **Settling Time**

The settling time is defined as the time from the 50% point of the input transition to the point at which the output enters into **and** stays within  $\pm \frac{1}{2}$ LSB (the error band) of the final value. Minimum settling time occurs when the output enters the error band at the maximum slew rate. and then settles out within the band. In actuality, however, the output's slew rate will lessen prior to entering the error band, and then may exit and enter the band once or twice as it settles to its final value. The settling time is determined by the last time the output enters the error band. See Figure 1.

When testing for settling time, the measurement technique used will have an effect on the result. Simply connecting scope probes to an input and output is generally not satisfactory due to the capacitive loading (typically 10–20 pF) of the probes. The rise (fall) time of an ECL input can be significantly increased by such a probe, with the result that the inputs of the MC10318 may be skewed from each other, which, in turn, affects the output. However, probes with low input capacitance, on the order of 2 pF or less (such as FET probes), can be used with very little degradation of the waveforms. The overall propagation delay of the probe (from tip to scope input) must be taken into account, as this can be on the order of 10 ns.

When attempting to view the output on a scope, several factors need to be considered. If the output swing is a full scale transition (e.g., 1.0 V), 1 LSB is 3.9 mV. The scope's amplifier must then be set at a sensitive range (5 mV/cm or 10 mV/cm), with the result that the scope's amplifier will be saturated when the MC10318's output is at the initial value. When the device inputs are switched, the output approaches the final value, but the scope's amplifier will require some time to come out of saturation, and then may overshoot, causing a false indication. In order to overcome this problem, the MC10318 was tested for settling time by connecting the output to a dual high-speed comparator configured as a window detector. The window is 1 LSB wide, centered about the final value. The outputs of the comparators are then monitored on a scope, as they indicate when the MC10318 output is settled within the error band. Propagation delays of the comparators, scope probes, and cable lengths are taken into account. See Figure 22. This method of monitoring the DAC's output, although indirect, does not cause changes to the output waveform because of probe loading, characteristics of the scope, or noise which the probe (and cable) may pick up.

#### **APPLICATIONS**

#### **Voltage Output**

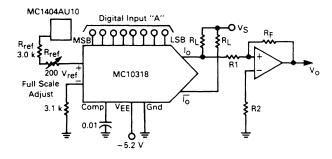

There are two methods of converting the current output of the MC10318 to voltage outputs, depending on the voltage swing desired. For a limited range ( $<3.8\ V\ p-p$ ) the circuit of Figure 23 can be used.

#### FIGURE 23 — VOLTAGE OUTPUT

| ٧s    | RL   | V <sub>o</sub>   | $\overline{v_o}$ |                                                                                      |

|-------|------|------------------|------------------|--------------------------------------------------------------------------------------|

| 0 V   | 25.5 | 0 to - 1.3 V     | - 1.3 V to 0 V   | $V_0 = -\frac{V_{ref} \times A \times R_L}{P_1 \times P_2} + V_S$                    |

| + 2.5 | 49   | + 2.5 to 0 V     | 0 to +2.5 V      | $V_0 = -\frac{\sqrt{\text{ref}} \times 16}{R_{\text{ref}} \times 16} + V_{\text{S}}$ |

| + 2.5 | 74.5 | + 2.5 to - 1.3 V | - 1.3 to + 2.5 V | Tel                                                                                  |

| + 1.0 | 39   | + 1.0 to - 1.0 V | - 1.0 to + 1.0 V |                                                                                      |

Where a larger voltage swing is required, an op amp is required at the output. The choice of op amp will be based on whether accuracy or speed is of primary importance. Where repeatable and stable accuracy is required, the op amp characteristics to consider are openloop gain, offset voltage, bias current, and temperature drift. Where speed is paramount, a wideband amplifier should be used. Slew rate, propagation delay, and settling time of the op amp are the primary factors to evaluate. The PC board should be designed for high frequency operation, possibly using Microstrip or Stripline techniques. See Figure 24 for a suggested circuit.

FIGURE 24 — VOLTAGE OUTPUT

|   | R <sub>ref</sub> | RL | ٧s     | R1    | RF    | Vo           |                                                                                                                  |

|---|------------------|----|--------|-------|-------|--------------|------------------------------------------------------------------------------------------------------------------|

|   | 3125             | 20 | 0      | 1.0 k | 5.0 k | 0 to +5      | V Vref A RL RF VS RF                                                                                             |

| 1 | 3125             | 20 | 0      | 1.0 k | 10 k  | 0 to + 10    | $V_0 = \frac{v_{ref} + v_{ref}}{R_{ref} \cdot 16 \cdot (R1 + R_1)} \cdot \frac{v_{s} \cdot v_{ref}}{(R1 + R_1)}$ |

|   | 3125             | 40 | + 1.02 | 2.0 k | 10 k  | -5 to +5     |                                                                                                                  |

|   | 3125             | 40 | + 1.02 | 2.0 k | 20 k  | - 10 to + 10 |                                                                                                                  |

Connecting  $I_O$  and  $\overline{I_O}$  as shown in the above figures places a constant dc load (51 mA) on the  $V_S$  supply, thus facilitating its design. The Gain Adjust resistor should be a 20 turn trimpot, as this will result in one turn equaling approximately 1 LSB of adjustment (for the recommended values in the figure). All of the resistors should have similar temperature coefficients for best temperature stability.

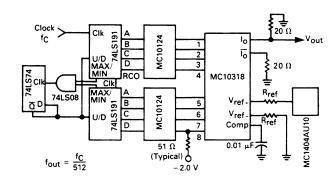

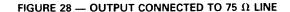

#### **WAVEFORM GENERATION**

#### FIGURE 25 — SAWTOOTH GENERATOR

#### FIGURE 26 — TRIANGLE GENERATOR

#### FIGURE 27 — SINEWAVE GENERATOR

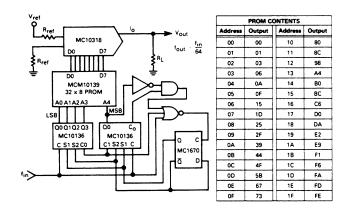

NOTE: Terminating Resistors and  $\rm Z_{O}$  must be matched to within 0.4% to keep initial reflection below 1/2 LSB in magnitude.

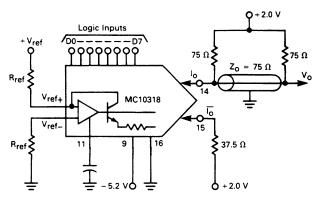

#### FIGURE 29 — OUTPUT CONNECTED TO 50 $\Omega$ LINE

NOTE: Terminating Resistors and Zo must be matched to within 0.4% to keep initial reflection below 1/2 LSB in magnitude.

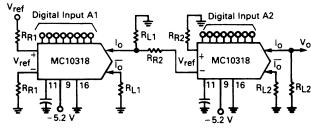

#### FIGURE 30 — DIGITAL MULTIPLICATION

|                  | gested<br>slues |                                                                                                                                   |

|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| V <sub>ref</sub> | + 10 V          | $V_0 = -\frac{A1 \times A2 \times V_{ref} \times R_{L1} \times R_{L2}}{R_{R1} \times R_{R2} \times 256} = -K \times A1 \times A2$ |

| R <sub>R1</sub>  | 3079*           | (With suggested values,                                                                                                           |

| RL1              | 20              | V <sub>O</sub> range is 0 to -1.0 V)                                                                                              |

| R <sub>R2</sub>  | 330             |                                                                                                                                   |

| R <sub>L2</sub>  | 20              | * 3.0 k Resistor + 100 Ω Trimpot                                                                                                  |

#### NOTES:

- 1) When generating waveforms at low frequencies, filtering the output is recommended to smooth out the steps.

- 2) In many applications, bipolar voltage output may be obtained by monitoring the differential voltage at Pins 14 and 15 (with equal load

- 3) When connecting the outputs to transmission lines (See Figures 28 and 29), proper transmission line theory and techniques must be used for optimum performance.

#### **OUTLINE DIMENSIONS**

- 4. DIMENSION "B" DOES NOT INCLUDE MOLD FLASH

- 5. ROUNDED CORNERS OPTIONAL.

|     | MILLIM   | IETERS   | INC   | HES   |

|-----|----------|----------|-------|-------|

| DIM | MIN      | MAX      | MIN   | MAX   |

| Α   | 18.80    | 19.55    | 0.740 | 0.770 |

| В   | 6.35     | 6.85     | 0.250 | 0.270 |

| С   | 3.69     | 4.44     | 0.145 | 0.175 |

| D   | 0.39     | 0.53     | 0.015 | 0.021 |

| F   | 1.02     | 1.77     | 0.040 | 0.070 |

| G   | 2.54 BSC |          | 0.100 | BSC   |

| Н   | 1.27     | 1.27 BSC |       | BSC   |

| J   | 0.21     | 0.38     | 0.008 | 0.015 |

| K   | 2.80     | 3.30     | 0.110 | 0.130 |

| L   | 7.50     | 7.74     | 0.295 | 0.305 |

| M   | 0°       | 10°      | 0°    | 10°   |

| S   | 0.51     | 1.01     | 0.020 | 0.040 |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and the product and trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### **Literature Distribution Centers:**

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

**MOTOROLA**