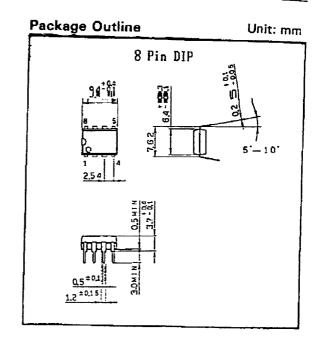

# CXK1012P

# 1024 -bit (128word x 8bit ) Non-volatile метогу

## Description

The CXK1012P is an electrically erasable and programmable E2PROM of 128word× 8 bit structure. It employs non-volatile memory transistors of the MNOS type. For the Input/Output, serial transmission of the data is executed. The built-in charge pump circuit permits all operations with a mere 5V power supply. With the built-in timer external parts are not required anymore, while Brasure and Write are conducted automatically. It is most suitable for the non-volatile channel memory of electronic tuners, for use instead of DIP switching as well as with the setting of various fixed numbers, or for the read only memory system necessary to rewrite immediately on

#### Features

the field.

- · Single 5V power supply

- $\cdot$  128 word imes 8 bit of full decoding structure

- · Serial data transmission

- · Rewritable in 1-word unit and in one chip

- · Memory retention time of more than 10 years with no power supply

- · Number of erasures and writings: more than 10<sup>5</sup> times

- · TTL IC direct drive is possible

- · low power consumption (35 mW Typ.)

To: Juris Sipasa FM: Kestin Weber

Structure

P-channel MNOS IC

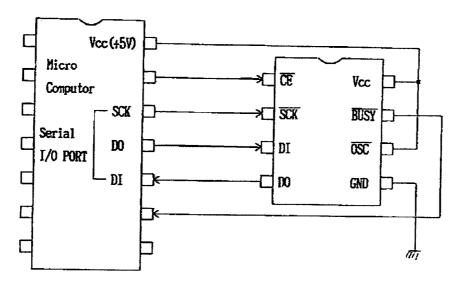

# Application Circuit

1) Using internal timer circuit

(In the example a serial port is used. A general port may also be used. It is also possible to refrain from using BUSY pin.)

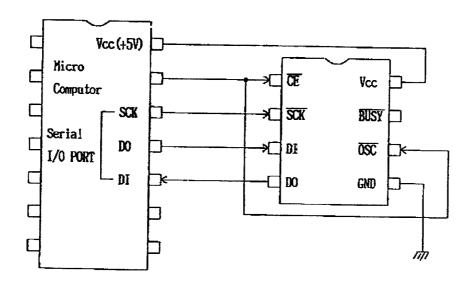

### 2) Using external control

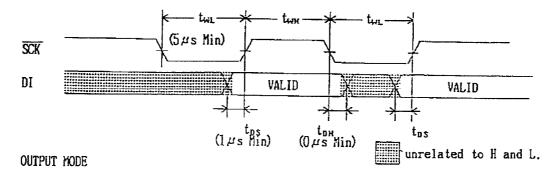

## Input/Output Timing Chart

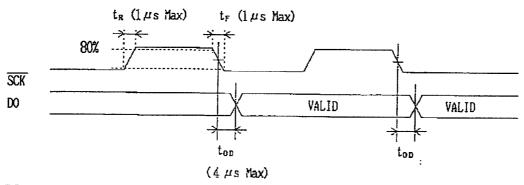

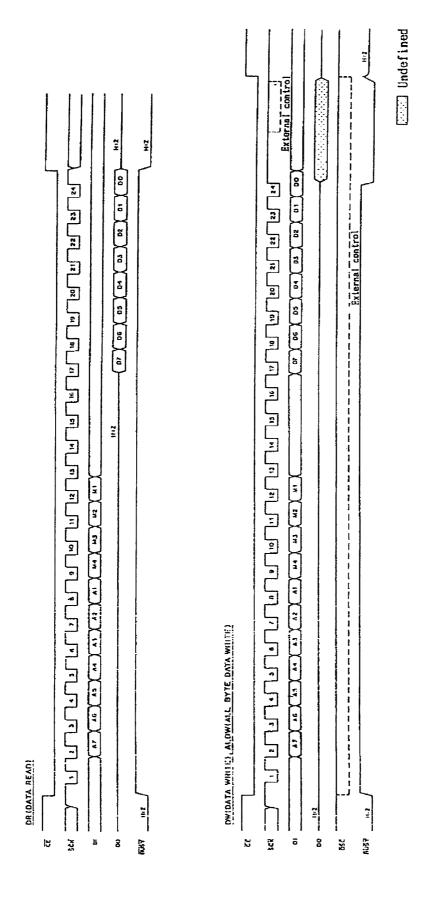

### INPUT MODE

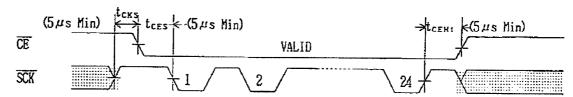

# CE TIMING 1 (DR MODE)

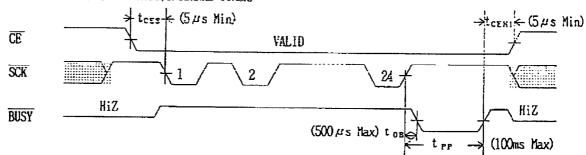

# CE TIMING 2 (DW, ALDW MODE, INTERNAL TIMER)

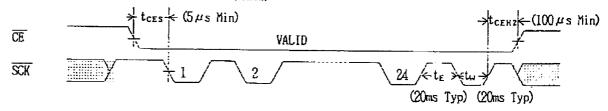

### CE TIMING 3 (DM, ALDW MODE, EXTERNAL CONTROL)

# Pin Description

| No. | Type  | Symbo1 | Description                                                         |  |  |  |  |

|-----|-------|--------|---------------------------------------------------------------------|--|--|--|--|

| 1   | IN    | CE     | Chip enable input pin                                               |  |  |  |  |

| 2   | IN    | SCK    | Sync clock input pin                                                |  |  |  |  |

| 3   | IN    | DI     | Data input pin                                                      |  |  |  |  |

| 4   | OUT   | DO     | Data output pin                                                     |  |  |  |  |

| 5   | Power | GND    | Power supply pin (Normally OV)                                      |  |  |  |  |

| 6   | IN    | OSC    | Oscillation pin (When using internal circuit, Open or fixed to Vcc) |  |  |  |  |

| 7   | OUT   | BUSY   | BUSY signal output pin                                              |  |  |  |  |

| 8   | Power | Vcc    | Power supply pin (Normally +5V)                                     |  |  |  |  |

# Electrical Characteristics 1.

$(Ta=-40 \text{ to } +85^{\circ}C, V_{cc}=5V \pm 10\%, GND=0V)$

| Item                        | (1a=-40 to +00C, Vcc=0V |                  |                            | - IVA; | עווט=עווט |      |      |

|-----------------------------|-------------------------|------------------|----------------------------|--------|-----------|------|------|

|                             | Symbol                  | Name             | Condition                  | Min.   | Typ.      | Max. | Unit |

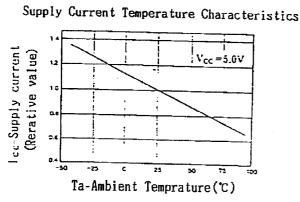

| Power supply current        | Icc                     |                  | *1                         |        | 6.5       | 12   | mΑ   |

| Input pull-up current       | Iıv                     | CE, SCK, DI, OSC | V <sub>1 N</sub> =0V       | -30    | -60       | -180 | μA   |

| Output leakage current      | Iorx                    | DO, BUSY         |                            |        |           | ±10  | μA   |

| Output voltage"High"level 1 | Voki                    | DO DO            | I <sub>OH</sub> = -400 μ A | 2.4    |           |      | V    |

| Output voltage"Low"level 1  | Voli                    | DO               | IoL= 1.6mA                 |        |           | 0.4  | V    |

| Output voltage"High"level 2 | V <sub>OH2</sub>        | BUSY             | I <sub>0H</sub> = -400 μA  | 2,4    |           |      | V    |

| Output voltage"Low"level 2  | V <sub>OL2</sub>        | BUSY             | I <sub>ot</sub> = 400 μ Å  |        |           | 0.4  | V    |

- \*1. Including during Erase and Write.

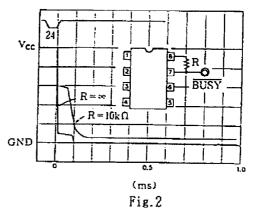

- \*2. See Fig.2.

BUSY Pin Output Delay Characteristics

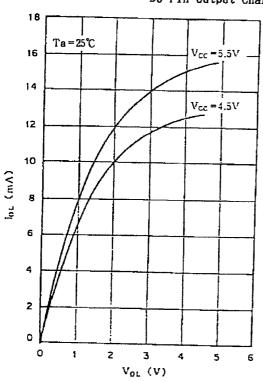

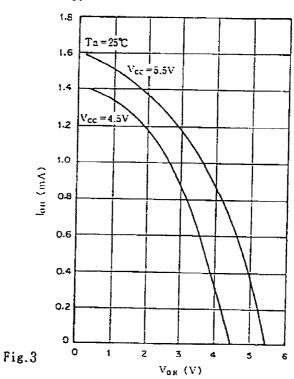

DO Pin Output Characteristics(Typ.)

Fig.4

# Electrical Characteristics 2

| Item                     | symbol            | (Ta=-40 to +8                                           | ic, y | cc=5V    | ±10%,                                            | GND=0 |

|--------------------------|-------------------|---------------------------------------------------------|-------|----------|--------------------------------------------------|-------|

| Clock pulse width        | twi               | Condition                                               | Min.  | Typ.     | Max.                                             | Unit  |

| Colck pulse width        | <del> </del>      |                                                         | 5     |          |                                                  | μs    |

| Data input setup time    | twi               |                                                         | 5     | <u> </u> |                                                  | μs    |

| Data input hold time     | tos               |                                                         | 1     |          |                                                  | μз    |

|                          | ton               |                                                         | 0     |          |                                                  | μs    |

| Rise /Fall time          | tr. tf            |                                                         |       |          | 1                                                | μs    |

| Chip enable setup time   | tces              |                                                         | 5     |          | <del>                                     </del> | μs    |

| Chip enable hold time 1  | t <sub>CEH1</sub> |                                                         | 5     |          |                                                  | μs    |

| Chip enable hold time 2  | tcenz             |                                                         | 100   |          |                                                  | μs    |

| Clock set up time        | tcxs              |                                                         | 5     |          |                                                  | μs    |

| Data delay time          | ton               | DO, C <sub>L</sub> =100pF                               |       |          | 4                                                | ИS    |

| BUSY output delay time*3 | t <sub>BD</sub>   | BUSY, R=10kΩ                                            |       |          | 500                                              | μs    |

| Number of Read           | Nz                | Refresh period                                          | 107   | 10°      |                                                  | time  |

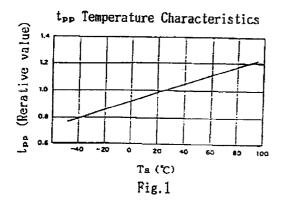

| Program time             | ter               | During internal timer usage *1                          |       | 40       | 100                                              | mS    |

| Erasure time             | t <sub>E</sub>    | During external control *2                              | 16    | 20       | 100                                              | mS    |

| Write time               | tw                | During external control *2                              | 16    | 20       | 100                                              | mS    |

| Memory retention time 1  | thhi              | After rewriting 104 times, store at Ta=85°C             | 10    |          | 1                                                | year  |

| Memory retention time 2  | t <sub>HH2</sub>  | After rewriting 10 <sup>5</sup> times, store at Ta=85°C | 1     |          |                                                  | year  |

- \*1. Including the value when  $Ta=25^{\circ}$  (See fig.1)

- \*2. Usage of ranges  $t_E$  to  $t_W$  (16 to 100ms) presents no problem for Erasure and Write in functions

- \*3. See Fig.2.

### Command Table

| M4 | М3 | M2 | M1 | Operational Command         |

|----|----|----|----|-----------------------------|

| 0  | 0  | 0  | 0  | No operation                |

| 0  | 0  | 1  | 0  | DW: Memory Write            |

| 0  | _1 | 0  | 0  | ALDW:A'l byte write         |

| 0  | 1  | 1  | 0  | Test Mode , Usage forbidden |

| 1  | 0  | 0  | 0  | No operation                |

| 1  | 0  | 1  | 0  | DR: Memory Read             |

| 1  | 1  | 0  | 0  | Test mode, Usage forbidden  |

| 1  | 1  | 1  | 0  | Test mode, Usage forbidden  |

| X  | X  | X  | 1  | Test mode, Usage forbidden  |

### Description of Circuit Operations

#### 1) Timing

At the rise time of Sync clock (SCK), data is taken in from D1 and with the fall time, data is output from D0. Input data should be stabilized, from SCK, rise time and before 1 µs.

### 2) DR:Data Read (Memory Read)

CE is set to L and then the first clock is input after  $5\mu$ s. By entering address data (A7 to A1) and mode data (M4 M3 M2 M1=1010), from the 17th clock and in synchronization with the fall time, D7 D6 through D0 are output in the respective order. When the rise time of the 24th clock has taken place, set  $\overline{CE}$  to H after  $5\mu$ s.

#### 3) DW:Data Write (Memory Write)

CE is set to L and then the first clock is input after  $5\mu$ s. By entering Address data (A7 to A1), mode data (M4 M3 M2 M1=0010) and Data (D7 to D0), from the rise time of the 24th clock, Brasure and Write are performed automatically. As  $\overline{BUSY}$  pin outputs L during Erasure and Write and H at the completion of Write, set  $\overline{CE}$  to H following H output and after  $5\mu$ s.

When BUSY pin is not in use, set CE to H after 100ms (top Max.)

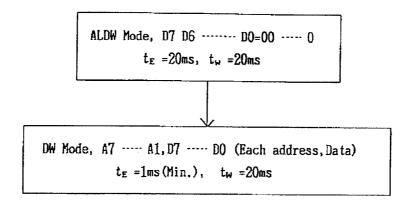

### 4) ALDW: All Byte Data Write

By entering Mode Data (M4 M3 M2 M1=0100), Write operation of the same data (D7 to D0) is carried out simultaneously to all addresses. CE timing and  $\overline{\text{BUSY}}$  output are the same as in above article 3).

### 5) Electrical control of Erasure and Write

Erasure and Write pulses are generated by the built-in C and R. However, external control is also possible. By setting  $\overline{OSC}$  pin to L in DW or ALDW modes, Erasure and Write control are possible through the usage of  $\overline{SCK}$  pin. Erasure is carried out during  $t_E$  (20ms Typ.) and write during  $t_W$  (20ms Typ.).

By setting  $\overline{SCK}$  pin to H after the lapse of  $t_W$ , write complete pulse is generated. However the actual completion takes place about 50  $\mu s$  after the pulse generation,

$(50\mu s\ Typ, 100\mu s\ Max.)$  At that time BUSY pin changes from L to H. Over  $5\mu s$  after it has turned to H, set  $\overline{CE}$  pin to H. When  $\overline{BUSY}$  pin is not in use, after  $\overline{SCK}$  pin has turned from L to H (tw) by over  $100\mu s$ , set  $\overline{CE}$  to H.

Absolute Maximum Ratings (GND = OV)

| · Supply voltage        | Vcc       | -0.3 | to |     | +7.0 | v |

|-------------------------|-----------|------|----|-----|------|---|

| · Input voltage         | VIN       | -0.3 | to | Vcc | +0.3 | V |

| · Operating temperature | $T_{opr}$ | -40  | to |     | +85  | Ċ |

| Storage temperature     | Tstg      | -55  | to |     | +150 | Շ |

Recommended Operating Conditions (Ta=-40 to+85°C, GND=0V)

| · Supply voltage           | Vcc       | 4.5 | to | 5.5                 | v        |

|----------------------------|-----------|-----|----|---------------------|----------|

| · Clock frequency          | $f_{clk}$ | DC  | to | 100                 | v<br>kHz |

| · High level input voltage | VINH O    |     | to | Vcc                 | KDZ<br>V |

| · Low level input voltage  | VIHL      | 0   | to | 0.3 V <sub>cc</sub> | V        |

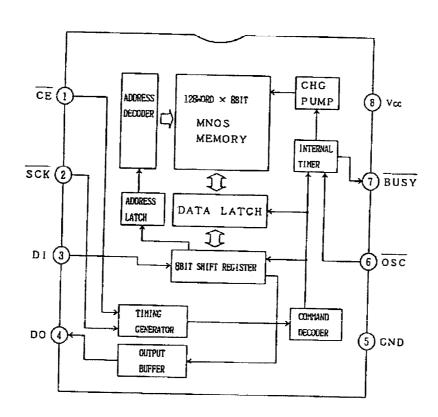

Block Diagram and Pin Configuration

### 6) Usage of ALDW mode H.

Write is carried out to the Memory elements according to the <code>FErase J  $\longrightarrow$  [Write J cycle.During normal write procedures (DW mode), as write is executed for all the 128 address,  $128 \times t_{PP}$  (or  $t_E + t_W$ )=5.12sec (Typ.) amount of time is necessary.</code>

With the CXK1012P, [Brasure state ] and [Data"0" ] are made to correspond.Once "0" has been written into all addresses (Erasure state), by writing data into each address, the program time can be shortened.

In this case, the program time becomes.  $(20\text{ms} + 20\text{ms}) + 128 \times (1\text{ms} + 20\text{ms}) = 2.73\text{sec}$