# **CXD3300R**

# 10-bit 20MSPS Video A/D Converter

Preliminary

## **Description**

The CXD3300R is a 10-bit CMOS A/D converter for video applications. This IC is ideally suited for the A/D conversion of video signals in TVs, VCRs, camcorders, etc.

#### **Features**

- Resolution: 10bits ± 1.0LSB (D.L.E.)

- Maximum sampling frequency: 20MSPS

- Low power consumption: 30mW (at 20MSPS typ.)

- Low input capacitance

- Built-in self-bias circuit

#### Structure

Silicon gate CMOS IC

#### **Absolute Maximum Ratings** (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul>             | AVDD     | AVss - 0.5 to +4.5                   | V  |

|------------------------------------------------|----------|--------------------------------------|----|

|                                                | DVDD     | DVss $-0.5$ to $+4.5$                | V  |

| <ul> <li>Reference voltage</li> </ul>          | VRT, VRB | AVDD + $0.5$ to AVss – $0.5$         | V  |

| <ul><li>Input voltage<br/>(analog)</li></ul>   | VIN      | AVDD + 0.5 to AVss – 0.5             | V  |

| <ul><li>Input voltage<br/>(digital)</li></ul>  | VIH, VIL | AVDD + 0.5 to AVss – 0.5             | V  |

| <ul><li>Output voltage<br/>(digital)</li></ul> | Voн, Vol | DV <sub>DD</sub> + 0.5 to DVss – 0.5 | V  |

| <ul> <li>Storage temperature</li> </ul>        | Tstg     | -55 to +150                          | °C |

#### **Recommended Operating Conditions**

| Supply voltage                              | AVDD, AVSS  | $3.0 \pm 0.3$      | V  |

|---------------------------------------------|-------------|--------------------|----|

|                                             | DVDD, DVss  | $3.0 \pm 0.3$      | V  |

|                                             | DVss – AVss | 0 to 100           | mV |

| <ul> <li>Reference input voltage</li> </ul> | VRB         | 0.3AVDD to 0.5AVDD | V  |

|                                             | VRT         | 0.6AVDD to 0.8AVDD | V  |

| <ul> <li>Analog input</li> </ul>            | Vin         | 0.9Vp-p or more    |    |

| <ul> <li>Clock pulse width</li> </ul>       | tpw1        | 25 (min)           | ns |

|                                             | tpw0        | 25 (min)           | ns |

| Operating ambient temperature               | Topr        | -40 to +85         | °C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

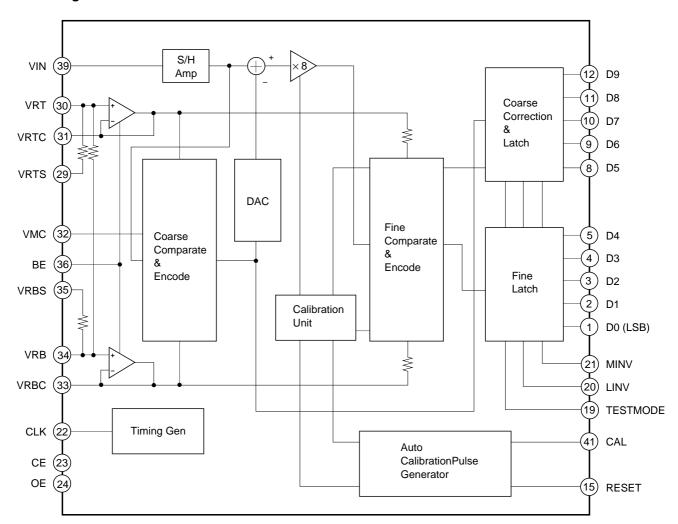

#### **Block Diagram**

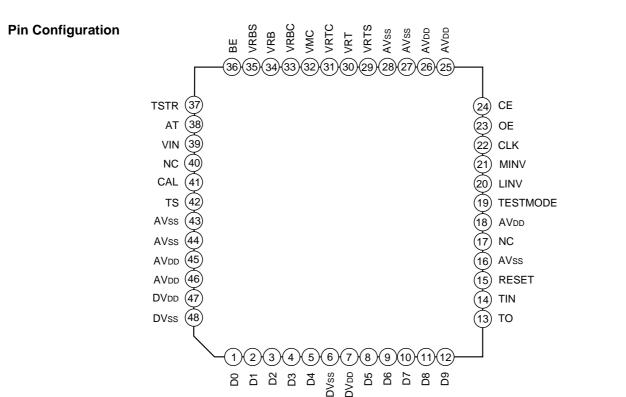

# **Pin Description**

| Pin No.               | Symbol   | Equivalent circuit | Description                                                                                |

|-----------------------|----------|--------------------|--------------------------------------------------------------------------------------------|

| 1 to 5<br>8 to 12     | D0 to D9 | DVss 7//           | D0 (LSB) to D9 (MSB) output.                                                               |

| 6, 48                 | DVss     |                    | Digital Vss.                                                                               |

| 7, 47                 | DVdd     |                    | Digital VDD.                                                                               |

| 13                    | то       |                    | Test signal output. High impedance when TS = High.                                         |

| 14                    | TIN      |                    | Test signal input. Normally fixed to AVDD or AVss.                                         |

| 15                    | RESET    | AVDD W             | Calibration circuit reset and startup calibration restart.                                 |

| 16, 27, 28,<br>43, 44 | AVss     |                    | Analog Vss.                                                                                |

| 18, 25, 26,<br>45, 46 | AVDD     |                    | Analog VDD                                                                                 |

| 19                    | TESTMODE | AVDD W             | Test mode.<br>High: Output state<br>Low: Output fixed                                      |

| 20                    | LINV     | AVDD W             | Output inversion. High: D0 to D8 are inverted and output. Low: D0 to D8 are normal output. |

| Pin No. | Symbol | Equivalent circuit | Description                                                                  |

|---------|--------|--------------------|------------------------------------------------------------------------------|

| 21      | MINV   | AVDD W             | Output inversion. High: D9 is inverted and output. Low: D9 is normal output. |

| 22      | CLK    | AVDD WW AVSS AVSS  | Clock.                                                                       |

| 23      | OE     | AVDD AVSS AVSS     | D0 to D9 output enable. Low: Output state High: High impedance state         |

| 24      | CE     | AVDD W AVSS AVSS   | Chip enable.<br>Low: Active state<br>High: Standby state                     |

| Pin No. | Symbol | Equivalent circuit                              | Description                      |

|---------|--------|-------------------------------------------------|----------------------------------|

| 29      | VRTS   | AVDD (29)                                       | Self-bias.<br>(Reference top)    |

| 30      | VRT    | AVss V<br>AVDD AVDD AVDD AVDD AVDD AVDD AVDD AV | Reference top.                   |

| 31      | VRTC   | AVss V<br>AVDD A                                | Reference top output.            |

| 32      | VMC    | AVss V<br>AVdd AVdd AVdd AVdd AVdd AVdd AVdd AV | Reference middle output.         |

| 33      | VRBC   | AVss \( \frac{1}{2} \) AVDD \( \triangle \) 33  | Reference bottom output.         |

| 34      | VRB    | AVss AVDD A                                     | Reference bottom.                |

| 35      | VRBS   | AVss AVDD AVDD AVDD AVDD AVDD AVDD AVDD         | Self-bias.<br>(Reference bottom) |

| 36      | BE     | AVss AVss AVss                                  | Bias enable.                     |

| Pin No. | Symbol | Equivalent circuit   | Description                                        |

|---------|--------|----------------------|----------------------------------------------------|

| 37      | TSTR   |                      | Test signal input. Normally fixed to AVDD or AVss. |

| 38      | AT     |                      | Test signal output. High impedance when TS = High. |

| 39      | VIN    | AVDD WATER AVSS AVSS | Analog input.                                      |

| 41      | CAL    | AVDD AVSS AVSS       | Calibration pulse input.                           |

| 42      | TS     |                      | Test signal input. Normally fixed to AVDD.         |

## **Digital Output**

The following table shows the correlation between the analog input voltage and the digital output code (TESTMODE = 1, LINV, MINV = 0)

| Input signal voltage | Step | Digital output code MSB | LSB |

|----------------------|------|-------------------------|-----|

| VRT<br>:             | 1023 | 1111111                 | 1 1 |

|                      | 512  | 1000000000              | 0 0 |

|                      | 511  | 01111111                | 1 1 |

| VRB                  | 0    | 000000000               | 0 0 |

The following table shows the output state for the combination of TESTMODE, LINV, and MINV states.

| TESTMODE | LINV | MINV | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 |

|----------|------|------|----|----|----|----|----|----|----|----|----|----|

| 1        | 0    | 0    | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  |

| 1        | 1    | 0    | N  | N  | N  | N  | N  | N  | N  | N  | N  | P  |

| 1        | 0    | 1    | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  | N  |

| 1        | 1    | 1    | N  | N  | N  | N  | N  | N  | N  | N  | N  | N  |

| 0        | 0    | 0    | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| 0        | 1    | 0    | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  |

| 0        | 0    | 1    | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  |

| 0        | 1    | 1    | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

P: Forward-phase output N: Inverted output

## **Electrical Characteristics**

(Fc = 20MSPS, AVDD = 3V, DVDD = 3V, VRB = 1V, VRT = 2V, Ta = 25°C)

| Item                | 1             | Symbol       | Conditions                                                                         |                                                    | Min.    | Тур. | Max.    | Unit   |

|---------------------|---------------|--------------|------------------------------------------------------------------------------------|----------------------------------------------------|---------|------|---------|--------|

| Max. conversion     | rate          | Fc max       | Fin = 1.0kHz triangular wave input                                                 |                                                    | 20      |      |         | MSPS   |

| Min. conversion     | rate          | Fc min       |                                                                                    |                                                    |         |      | 0.5     | IVIOFO |

| Cummbu valtama      | Analog        | IAdd         | Fin = 1.0kHz                                                                       | Fin = 1.0kHz triangular wave                       |         | 10   |         |        |

| Supply voltage      | Digital       | IDDD         | input                                                                              | _                                                  |         | 3.0  |         | mA     |

| Standby             | Analog        | IAst         | CF /\/22                                                                           |                                                    |         | 1.0  |         | mA     |

| current             | Digital       | IDsт         | CE = AVDD                                                                          |                                                    |         | 1.0  |         | μΑ     |

| Potoronoo nin o     | irrant 1      | IRT1         | VRTS, VRB                                                                          | S: Open                                            |         | 100  |         | ^      |

| Reference pin cu    | ineni i       | IRB1         | Between VR                                                                         | RT and VRB                                         |         | -100 |         | μΑ     |

| Potoronoo nin o     | irrant 2      | Irt2         | BE = AVDD                                                                          |                                                    |         | 2    |         | mΛ     |

| Reference pin cu    | irrent Z      | IRB2         | Between VR                                                                         | RTC and VRBC                                       |         | -2   |         | mA     |

| Analog input ban    | ıd            | BW           | -1dB                                                                               |                                                    |         | TBD  |         | MHz    |

| Analog input cap    | acitance      | Cin          |                                                                                    |                                                    |         | 10   |         | pF     |

| Reference resist    | ance value 1  | RREF1        |                                                                                    | RTS and VRT, VRT<br>RB and VRBS                    |         | 10k  |         | Ω      |

| Reference resist    | ance value 2  | Rref2        | Between VRTC and VRBC                                                              |                                                    |         | 500  |         | Ω      |

| Offset voltage      |               | Еот          | EOT = Theoretical value – Measured value  EOB = Measured value – Theoretical value |                                                    |         | TBD  |         | mV     |

| Oliset voltage      |               | Еов          |                                                                                    |                                                    |         | TBD  |         |        |

| Digital input volta | age           | Vін          | AVDD = 2.7 to 3.3V                                                                 |                                                    | 0.7AVDD |      |         | V      |

|                     |               | VIL          |                                                                                    |                                                    |         |      | 0.2AVDD |        |

| Analog input curi   | rent          | Аін          | Vin = 2V                                                                           |                                                    |         | 20   |         | μA     |

|                     |               | AıL          | Vin = 1V                                                                           |                                                    |         | -20  |         | μ, ,   |

| Digital input curre | ent           | Іін          | AVDD = 3.3V                                                                        | VIH = AVDD                                         |         |      | 5       | μA     |

|                     |               | lı∟          |                                                                                    | VIL = AVSS                                         |         |      | 5       | μΛ     |

| Digital output cur  | rent          | Іон          | OE = AVss                                                                          | VOH = DVDD - 0.4V                                  | 8.0     |      |         | mA     |

| Digital output out  |               | lol          | DV <sub>DD</sub> = 2.7V                                                            | Vol = 0.4V                                         | 8.0     |      |         | 1117 ( |

| Digital output cur  | rent          | Іохн         | OE = AVDD                                                                          | Voh = DVdd                                         |         |      | 1       | μΑ     |

| Digital output out  | TOTIL         | lozL         | DVDD = 3.3V                                                                        | Vol = 0V                                           |         |      | 1       | μΛ     |

| Tri-state output of | lisable time  | <b>t</b> PEZ | ,                                                                                  | Clock not synchronized for active → high impedance |         | 2    |         | ns     |

| Tri-state output e  | enable time   | <b>t</b> pze | Clock not synchronized for high impedance → active                                 |                                                    |         | 2    |         | ns     |

| Integral nonlinea   | rity error    | EL           |                                                                                    |                                                    |         | ±1.0 |         | LSB    |

| Differential nonlin | nearity error | Eb           |                                                                                    |                                                    |         | ±0.5 |         | LSB    |

| Differential gain   | error         | DG           | NTSC 40 IRE mod                                                                    |                                                    |         | TBD  |         | %      |

| Differential phase  | e error       | DP           | ramp, Fc = 1                                                                       |                                                    |         | TBD  |         | deg    |

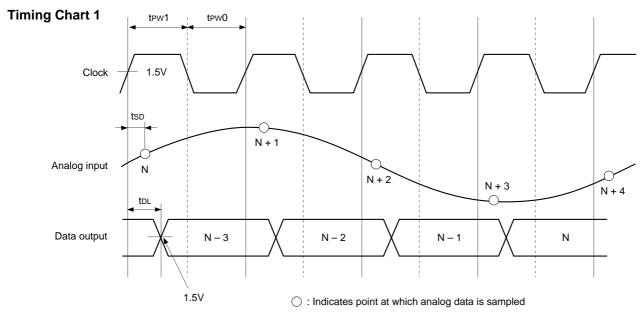

| Output data dela    | у             | <b>t</b> DL  | C <sub>L</sub> = 20pF                                                              |                                                    |         | 3    |         | ns     |

| Sampling delay      |               | tsp          |                                                                                    |                                                    |         | 2    |         | ns     |

| Item  | Symbol | Conditions   | Min. | Тур. | Max. | Unit |

|-------|--------|--------------|------|------|------|------|

|       |        | Fin = 100kHz |      | TBD  |      |      |

|       |        | Fin = 500kHz |      | TBD  |      |      |

| SNR   | SNR    | Fin = 1MHz   |      | TBD  |      | dB   |

| SIVIX | SINK   | Fin = 3MHz   |      | TBD  |      | ub   |

|       |        | Fin = 7MHz   |      | TBD  |      |      |

|       |        | Fin = 10MHz  |      | TBD  |      |      |

|       |        | Fin = 100kHz |      | TBD  |      |      |

|       |        | Fin = 500kHz |      | TBD  |      |      |

| SFDR  | SFDR   | Fin = 1MHz   |      | TBD  |      | dB   |

| SFDR  | SFUR   | Fin = 3MHz   |      | TBD  |      | uБ   |

|       |        | Fin = 7MHz   |      | TBD  |      |      |

|       |        | Fin = 10MHz  |      | TBD  |      |      |

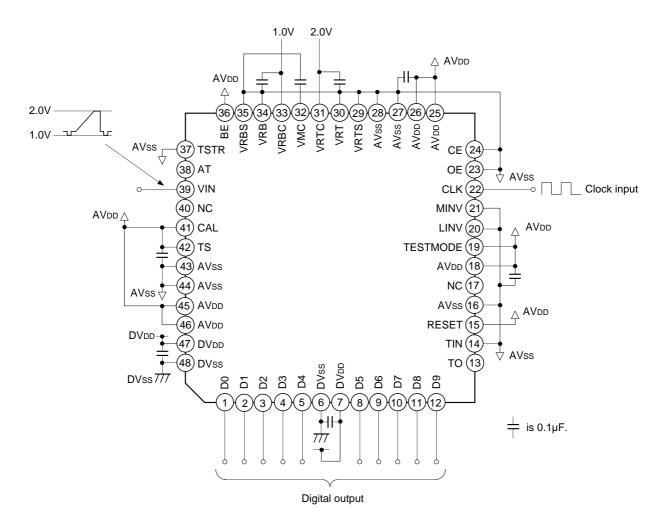

## **Application Circuit 1**

When not using self-bias and the internal bias circuits, and supplying the reference voltage from an external source.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

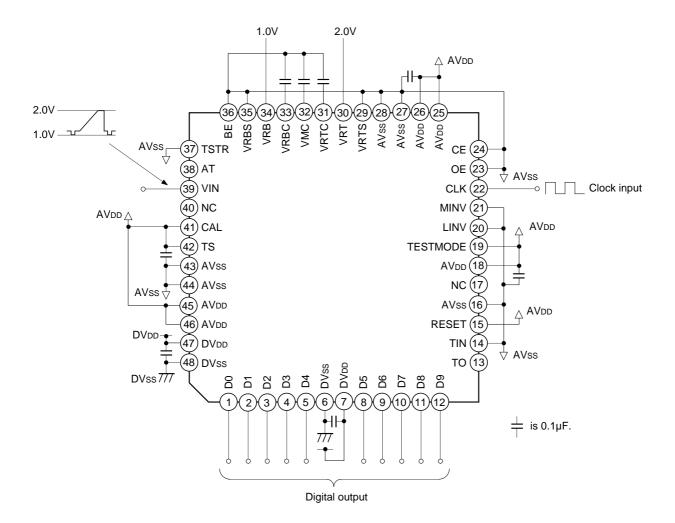

#### **Application Circuit 2**

When not using self-bias circuit, using only the internal bias circuit, and supplying the reference voltage from an external source.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

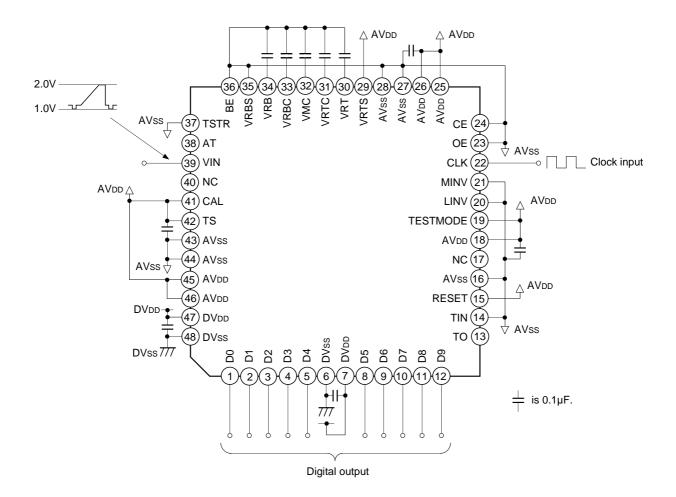

#### **Application Circuit 3**

When using the self-bias and internal bias circuits, and supplying the reference voltage.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

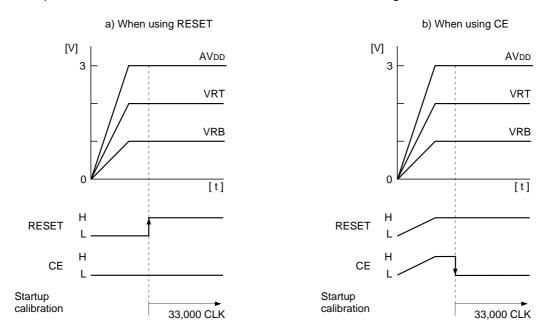

#### 1. Calibration function

#### 1) Activating startup calibration

To achieve superior linearity, the CXD3300R has a built-in calibration circuit. When using this IC, therefore, startup calibration must be activated when the power supply and reference voltage have risen and stabilized. Care should be taken as only the upper five bits may be output in the worst case if startup calibration is not activated.

Startup calibration can be activated either at the rise of the RESET pin (Pin 15) or at the fall of the CE pin (Pin 24). The startup calibration activation method for each case is shown in Fig. 1.

Fig. 1. Startup Calibration Activation Methods

As shown in the figure above, startup calibration must be activated after the supply voltage has risen and stabilized (full scale of 90% or more). After activation, startup calibration is performed for an interval of about 33,000 clocks. Therefore, care should be taken as the output data during this interval (about 2.3ms at 14.3MHz) cannot be used.

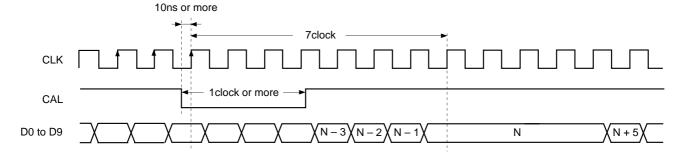

## 2) Calibration pulse supply

The IC's operating status with changes due to fluctuations in the supply voltage and ambient temperature during use can be constantly monitored and then compensated appropriately by inputting a pulse at regular intervals to the CAL pin (Pin 41). Fig. 2 shows the timing chart.

Fig. 2. Calibration Timing Chart

Calibration starts when the fall of the pulse input to the CAL pin (Pin 41) is detected at the clock rise. At this time, the comparator is used in an exclusive manner for a four clock interval. So, the output data holds the immediately previous data for a four clock interval after seven clocks from the rise of the clock where the fall of the calibration pulse was detected, and then the data during this interval is missing.

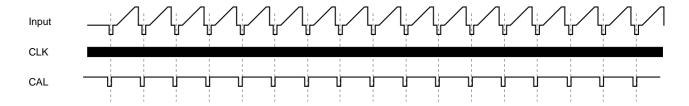

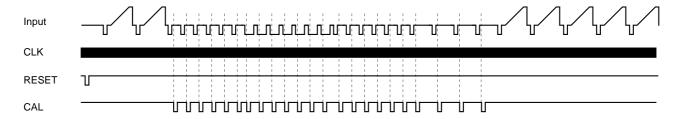

Therefore, the effects of this function can be avoided by inputting a sync or other signal as the calibration pulse so that calibration is performed outside of the interval of the actually used video signal. An input example is shown below.

#### [1] Input every H sync

### [2] Input every V sync

#### 2. Latch-up

Ensure that the AVDD and DVDD pins share the same power supply on a board to prevent latch-up which may be caused by power-ON time lag.

#### 3. Board

To obtain full-expected performance from this IC, be sure that the mounting board has a large ground pattern for lower impedance. It is recommended that the IC be mounted on a board without using a socket to evaluate its characteristics adequately.

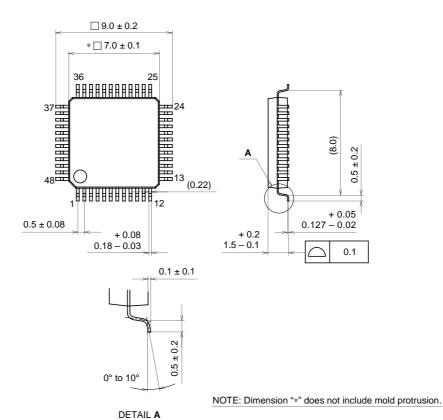

# Package Outline Unit: mm

# 48PIN LQFP (PLASTIC)

|            |                | PACKAGE MATERIAL | EPOXY RESIN                 |

|------------|----------------|------------------|-----------------------------|

| SONY CODE  | LQFP-48P-L01   | LEAD TREATMENT   | SOLDER/PALLADIUM<br>PLATING |

| EIAJ CODE  | LQFP048-P-0707 | LEAD MATERIAL    | 42/COPPER ALLOY             |

| JEDEC CODE |                | PACKAGE MASS     | 0.2g                        |