# **Timing Generator for LCD Panels**

# Description

The CXD2453Q is a timing signal generator for driving the LCX017AL and LCX023AL LCD panels. This chip outputs timing signals which support XGA signals (1024  $\times$  768 dots) and S-XGA signals (1280  $\times$  1024 dots).

#### **Features**

- Supports various XGA signals (1024 × 768 dots) having horizontal scanning frequencies of 44-69kHz and vertical scanning frequencies of 55 to 85Hz.

- Supports S-XGA (1280  $\times$  1024 dots) pulse eliminator (horizontal scanning frequency of 69kHz or less).

- Controls the sample-and-hold position of the CXA2112R sample-and-hold driver.

- Line inversion and field inversion signal generation

- AC drive of LCD panels during no signal.

# **Applications**

LCD projectors, etc.

#### Structure

Silicon gate CMOS IC

**Note:** Company names and product names, etc. contains in these materials are the trademarks or registered trademarks of the respective companies.

# **Absolute Maximum Ratings** (Vss = 0V)

| Vdd   | Vss - 0.5 to +4.0               | V                                                                                                      |

|-------|---------------------------------|--------------------------------------------------------------------------------------------------------|

| Vı    |                                 |                                                                                                        |

| in)   | Vss - 0.5 to $Vdd + 0.5$        | V                                                                                                      |

| in)   | Vss - 0.5 to $Vdd + 2.5$        | V                                                                                                      |

| Vo    | Vss - 0.5 to $Vdd + 0.5$        | V                                                                                                      |

| ature |                                 |                                                                                                        |

| Tstg  | -55 to +125                     | °C                                                                                                     |

|       | VI<br>in)<br>in)<br>Vo<br>ature | $V_{I}$ in) $V_{SS} - 0.5$ to $V_{DD} + 0.5$ in) $V_{SS} - 0.5$ to $V_{DD} + 2.5$ $V_{OD} + 0.5$ ature |

## **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | VDD     | +3.0 to +3.6 | V  |

|------------------------------------|---------|--------------|----|

| Operating temperating temperature  | erature |              |    |

|                                    | Topr    | -20 to +75   | °C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

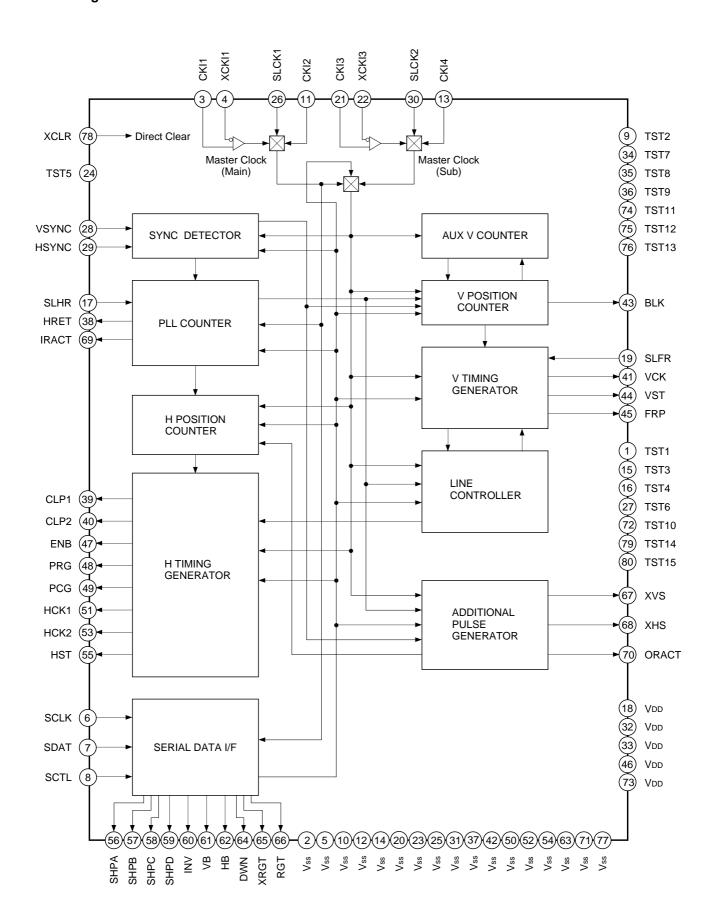

#### **Block Diagram**

# **Pin Description**

| Pin<br>No. | Symbol | I/O | Description                                                                         | Input pin for open status |

|------------|--------|-----|-------------------------------------------------------------------------------------|---------------------------|

| 1          | TST1   | _   | Test pin (Not connected.)                                                           | _                         |

| 2          | Vss    | _   | GND                                                                                 | _                         |

| 3          | CKI1   | ı   | Master clock input 1 (differential)                                                 |                           |

| 4          | XCKI1  | '   | Master clock input 1 (differential)                                                 |                           |

| 5          | Vss    | _   | GND                                                                                 |                           |

| 6          | SCLK   | I   | Serial data clock input                                                             | _                         |

| 7          | SDAT   | I   | Serial data input                                                                   | _                         |

| 8          | SCTL   | I   | Serial data control signal input                                                    | _                         |

| 9          | TST2   | _   | Test pin (connect to GND)                                                           | _                         |

| 10         | Vss    | _   | GND                                                                                 |                           |

| 11         | CKI2   | I   | Master clock input 2                                                                | _                         |

| 12         | Vss    | _   | GND                                                                                 | _                         |

| 13         | CKI4   | I   | Master clock input 4                                                                | _                         |

| 14         | Vss    | _   | GND                                                                                 | _                         |

| 15         | TST3   | _   | Test pin (Not connected.)                                                           | _                         |

| 16         | TST4   | _   | Test pin (Not connected.)                                                           | _                         |

| 17         | SLHR   | I   | Reset by HSYNC of PLL counter (High: Disabled, Low: Enabled)                        | Н                         |

| 18         | VDD    | _   | Power supply                                                                        | _                         |

| 19         | SLFR   | I   | FRP polarity inversion cycle selection (High: Field inversion, Low: Line inversion) | L                         |

| 20         | Vss    | _   | GND                                                                                 | _                         |

| 21         | CKI3   | ı   | Master clock input 2 (differential)                                                 |                           |

| 22         | XCKI3  | '   | Master clock input 3 (differential)                                                 |                           |

| 23         | Vss    | _   | GND                                                                                 | _                         |

| 24         | TST5   | _   | Test pin (Not connected.)                                                           |                           |

| 25         | Vss    | _   | GND                                                                                 | _                         |

| 26         | SLCK1  | I   | Clock input selection 1 (High: CKI2, Low: CKI1)                                     | L                         |

| 27         | TST6   | _   | Test pin (Not connected.)                                                           | _                         |

| 28         | VSYNC  | I   | Vertical sync signal input                                                          | _                         |

| 29         | HSYNC  | I   | Horizontal sync signal input                                                        | _                         |

| 30         | SLCK2  | I   | Clock input selection 2 (High: CKI4, Low: CKI3)                                     | L                         |

| 31         | Vss    | _   | GND                                                                                 | _                         |

| 32         | VDD    | _   | Power supply                                                                        | _                         |

| 33         | VDD    | _   | Power supply                                                                        | _                         |

| 34         | TST7   | _   | Test pin (connect to VDD)                                                           | _                         |

| 35         | TST8   | _   | Test pin (connect to VDD)                                                           | _                         |

| 36         | TST9   | _   | Test pin (connect to VDD)                                                           | _                         |

| 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin<br>No. | Symbol | I/O | Description                                           | Input pin for open status |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-----|-------------------------------------------------------|---------------------------|

| CLP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37         | Vss    | _   | GND                                                   | _                         |

| 40         CLP2         O         Pedestal clamp pulse 2 output         —           41         VCK         O         V clock pulse output         —           42         Vss         —         GND         —           43         BLK         O         BLK pulse output         —           44         VST         O         V start pulse output         —           45         FRP         O         AC drive inversion pulse output         —           46         Vob         —         Power supply         —           47         ENB         O         ENB pulse output         —           48         PRG         O         PRG pulse output         —           49         PCG         O         PCG pulse output         —           50         Vss         —         GND         —           51         HCK1         O         H clock 1 pulse output         —           52         Vss         —         GND         —           53         HCK2         O         H clock 2 pulse output         —           54         Vss         —         GND         —           55         HST         O                                                                                         | 38         | HRET   | 0   | Phase comparison pulse output                         | _                         |

| 41         VCK         O         V clock pulse output         —           42         Vss         —         GND         —           43         BLK         O         BLK pulse output         —           44         VST         O         V start pulse output         —           45         FRP         O         AC drive inversion pulse output         —           46         Vob         —         Power supply         —           47         ENB         O         ENB pulse output         —           48         PRG         O         PRG pulse output         —           49         PCG         O         PCG pulse output         —           50         Vss         —         GND         —           51         HCK1         O         H clock 1 pulse output         —           52         Vss         —         GND         —           53         HCK2         O         H clock 2 pulse output         —           54         Vss         —         GND         —           55         HST         O         H start pulse output         —           56         SHPA         O         <                                                                                        | 39         | CLP1   | 0   | Pedestal clamp pulse 1 output                         | _                         |

| 42         Vss         —         GND         —           43         BLK         O         BLK pulse output         —           44         VST         O         V start pulse output         —           45         FRP         O         AC drive inversion pulse output         —           46         Vob         —         Power supply         —           47         ENB         O         ENB pulse output         —           48         PRG         O         PRG pulse output         —           49         PCG         O         PCG pulse output         —           50         Vss         —         GND         —           51         HCK1         O         H clock 1 pulse output         —           52         Vss         —         GND         —           53         HCK2         O         H clock 2 pulse output         —           54         Vss         —         GND         —           55         HST         O         H start pulse output         —           54         Vss         —         GND         —           55         HST         O         External sample                                                                                            | 40         | CLP2   | 0   | Pedestal clamp pulse 2 output                         | _                         |

| 43         BLK         O         BLK pulse output         —           44         VST         O         V start pulse output         —           45         FRP         O         AC drive inversion pulse output         —           46         Vob         —         Power supply         —           47         ENB         O         ENB pulse output         —           48         PRG         O         PRG pulse output         —           49         PCG         O         PCG pulse output         —           50         Vss         —         GND         —           51         HCK1         O         H clock 1 pulse output         —           52         Vss         —         GND         —           53         HCK2         O         H clock 2 pulse output         —           54         Vss         —         GND         —           55         HST         O         H start pulse output         —           56         SHPA         O         External sample-and-hold driver control signal output         —           57         SHPB         O         External sample-and-hold driver control signal output         —                                                 | 41         | VCK    | 0   | V clock pulse output                                  | _                         |

| 44         VST         O         V start pulse output         —           45         FRP         O         AC drive inversion pulse output         —           46         Vop         —         Power supply         —           47         ENB         O         ENB pulse output         —           48         PRG         O         PCG pulse output         —           49         PCG         O         PCG pulse output         —           50         Vss         —         GND         —           51         HCK1         O         H clock 1 pulse output         —           52         Vss         —         GND         —           53         HCK2         O         H clock 2 pulse output         —           54         Vss         —         GND         —           55         HST         O         H start pulse output         —           55         HST         O         External sample-and-hold driver control signal output         —           57         SHPB         O         External sample-and-hold driver control signal output         —           58         SHPC         O         External sample-and-hold driver control signa                              | 42         | Vss    | _   | GND                                                   | _                         |

| 45         FRP         O         AC drive inversion pulse output         —           46         Vob         —         Power supply         —           47         ENB         O         ENB pulse output         —           48         PRG         O         PCG pulse output         —           49         PCG         O         PCG pulse output         —           50         Vss         —         GND         —           51         HCK1         O         H clock 1 pulse output         —           52         Vss         —         GND         —           53         HCK2         O         H clock 2 pulse output         —           54         Vss         —         GND         —           55         HST         O         H start pulse output         —           56         SHPA         O         External sample-and-hold driver control signal output         —           57         SHPB         O         External sample-and-hold driver control signal output         —           59         SHPD         O         External sample-and-hold driver control signal output         —           60         INV         O         External sa                              | 43         | BLK    | 0   | BLK pulse output                                      | _                         |

| 46         Vop         — Power supply         —           47         ENB         O ENB pulse output         —           48         PRG         O PRG pulse output         —           49         PCG         O PCG pulse output         —           50         Vss         — GND         —           51         HCK1         O H clock 1 pulse output         —           52         Vss         — GND         —           53         HCK2         O H clock 2 pulse output         —           54         Vss         — GND         —           55         HST         O H start pulse output         —           55         HST         O H start pulse output         —           56         SHPA         O External sample-and-hold driver control signal output         —           57         SHPB         O External sample-and-hold driver control signal output         —           69         SHPD         O External sample-and-hold driver control signal output         —           60         INV         O External sample-and-hold driver control signal output         —           61         VB         O VB signal output         —           62         HB         O HB signal ou | 44         | VST    | 0   | V start pulse output                                  | _                         |

| 47         ENB         O         ENB pulse output         —           48         PRG         O         PRG pulse output         —           49         PCG         O         PCG pulse output         —           50         Vss         —         GND         —           51         HCK1         O         H clock 1 pulse output         —           52         Vss         —         GND         —           53         HCK2         O         H clock 2 pulse output         —           54         Vss         —         GND         —           55         HST         O         H start pulse output         —           56         SHPA         O         External sample-and-hold driver control signal output         —           57         SHPB         O         External sample-and-hold driver control signal output         —           59         SHPD         O         External sample-and-hold driver control signal output         —           60         INV         O         External sample-and-hold driver control signal output         —           61         VB         O         VB signal output         —           62         HB         O                          | 45         | FRP    | 0   | AC drive inversion pulse output                       | _                         |

| 48         PRG         O         PRG pulse output         —           49         PCG         O         PCG pulse output         —           50         Vss         —         GND         —           51         HCK1         O         H clock 1 pulse output         —           52         Vss         —         GND         —           53         HCK2         O         H clock 2 pulse output         —           54         Vss         —         GND         —           55         HST         O         H start pulse output         —           56         SHPA         O         External sample-and-hold driver control signal output         —           57         SHPB         O         External sample-and-hold driver control signal output         —           58         SHPC         O         External sample-and-hold driver control signal output         —           60         INV         O         External sample-and-hold driver control signal output         —           61         VB         O         VB signal output         —           62         HB         O         HB signal output         —           63         Vss         —                          | 46         | Vdd    | _   | Power supply                                          | _                         |

| 49 PCG O PCG pulse output —  50 Vss — GND —  51 HCK1 O H clock 1 pulse output —  52 Vss — GND —  53 HCK2 O H clock 2 pulse output —  54 Vss — GND —  55 HST O H start pulse output —  56 SHPA O External sample-and-hold driver control signal output —  57 SHPB O External sample-and-hold driver control signal output —  58 SHPC O External sample-and-hold driver control signal output —  59 SHPD O External sample-and-hold driver control signal output —  60 INV O External sample-and-hold driver control signal output —  61 VB O VB signal output —  62 HB O HB signal output —  63 Vss — GND —  64 DWN O Up/down inversion signal output —  65 XRGT O Left/right inversion signal output —  66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —  67 Nys — GND —  68 Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND                                                                                                                                                                                                                      | 47         | ENB    | 0   | ENB pulse output                                      | _                         |

| 50         Vss         —         GND         —           51         HCK1         O         H clock 1 pulse output         —           52         Vss         —         GND         —           53         HCK2         O         H clock 2 pulse output         —           54         Vss         —         GND         —           55         HST         O         H start pulse output         —           56         SHPA         O         External sample-and-hold driver control signal output         —           57         SHPB         O         External sample-and-hold driver control signal output         —           58         SHPC         O         External sample-and-hold driver control signal output         —           60         INV         O         External sample-and-hold driver control signal output         —           61         VB         O         VB signal output         —           61         VB         O         VB signal output         —           62         HB         O         HB signal output         —           63         Vss         —         GND         —           64         DWN         O         U                              | 48         | PRG    | 0   | PRG pulse output                                      | _                         |

| 51       HCK1       O       H clock 1 pulse output       —         52       Vss       —       GND       —         53       HCK2       O       H clock 2 pulse output       —         54       Vss       —       GND       —         55       HST       O       H start pulse output       —         56       SHPA       O       External sample-and-hold driver control signal output       —         57       SHPB       O       External sample-and-hold driver control signal output       —         58       SHPC       O       External sample-and-hold driver control signal output       —         60       INV       O       External sample-and-hold driver control signal output       —         61       VB       O       VB signal output       —         61       VB       O       VB signal output       —         62       HB       O       HB signal output       —         63       Vss       —       GND       —         64       DWN       O       Up/down inversion signal output       —         65       XRGT       O       Left/right inversion signal output       —         67       XVS <td>49</td> <td>PCG</td> <td>0</td> <td>PCG pulse output</td> <td>_</td>            | 49         | PCG    | 0   | PCG pulse output                                      | _                         |

| 52       Vss       —       GND       —         53       HCK2       O       H clock 2 pulse output       —         54       Vss       —       GND       —         55       HST       O       H start pulse output       —         56       SHPA       O       External sample-and-hold driver control signal output       —         57       SHPB       O       External sample-and-hold driver control signal output       —         58       SHPC       O       External sample-and-hold driver control signal output       —         60       INV       O       External sample-and-hold driver control signal output       —         61       VB       O       VB signal output       —         61       VB       O       VB signal output       —         62       HB       O       HB signal output       —         63       Vss       —       GND       —         64       DWN       O       Up/down inversion signal output       —         65       XRGT       O       Left/right inversion signal output       —         66       RGT       O       Auxiliary pulse output       —         68       XHS <td>50</td> <td>Vss</td> <td>_</td> <td>GND</td> <td>_</td>                          | 50         | Vss    | _   | GND                                                   | _                         |

| HCK2 O H clock 2 pulse output —  S4 Vss — GND —  S5 HST O H start pulse output —  S6 SHPA O External sample-and-hold driver control signal output —  S7 SHPB O External sample-and-hold driver control signal output —  S8 SHPC O External sample-and-hold driver control signal output —  S9 SHPD O External sample-and-hold driver control signal output —  60 INV O External sample-and-hold driver control signal output —  61 VB O VB signal output —  62 HB O HB signal output —  63 Vss — GND —  64 DWN O Up/down inversion signal output —  65 XRGT O Left/right inversion signal output —  66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —  64 OND —  65 IRACT O Auxiliary pulse output —  71 Vss — GND —  67 Vss — GND —  68 Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —  72 OND —  74 Vss — GND —  75 OND —  76 OND —  77 ONACT O Auxiliary pulse output —  78 OND —  78 OND —  78 OND —  79 ONACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND                                                | 51         | HCK1   | 0   | H clock 1 pulse output                                | _                         |

| 54       Vss       —       GND       —         55       HST       O       H start pulse output       —         56       SHPA       O       External sample-and-hold driver control signal output       —         57       SHPB       O       External sample-and-hold driver control signal output       —         58       SHPC       O       External sample-and-hold driver control signal output       —         69       INV       O       External sample-and-hold driver control signal output       —         60       INV       O       External sample-and-hold driver control signal output       —         61       VB       O       VB signal output       —         62       HB       O       HB signal output       —         63       Vss       —       GND       —         64       DWN       O       Up/down inversion signal output       —         65       XRGT       O       Left/right inversion signal output       —         66       RGT       O       Left/right inversion signal output       —         67       XVS       O       Auxiliary pulse output       —         69       IRACT       O       Auxiliary pulse output                                             | 52         | Vss    | _   | GND                                                   | _                         |

| 55 HST O H start pulse output —  56 SHPA O External sample-and-hold driver control signal output —  57 SHPB O External sample-and-hold driver control signal output —  58 SHPC O External sample-and-hold driver control signal output —  59 SHPD O External sample-and-hold driver control signal output —  60 INV O External sample-and-hold driver control signal output —  61 VB O VB signal output —  62 HB O HB signal output —  63 Vss — GND —  64 DWN O Up/down inversion signal output —  65 XRGT O Left/right inversion signal (reverse polarity) output —  66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  69 IRACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                   | 53         | HCK2   | 0   | H clock 2 pulse output                                | _                         |

| SHPA O External sample-and-hold driver control signal output —  57 SHPB O External sample-and-hold driver control signal output —  58 SHPC O External sample-and-hold driver control signal output —  59 SHPD O External sample-and-hold driver control signal output —  60 INV O External sample-and-hold driver control signal output —  61 VB O VB signal output —  62 HB O HB signal output —  63 Vss — GND —  64 DWN O Up/down inversion signal output —  65 XRGT O Left/right inversion signal (reverse polarity) output —  66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  69 IRACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54         | Vss    | _   | GND                                                   | _                         |

| SHPB O External sample-and-hold driver control signal output —  S8 SHPC O External sample-and-hold driver control signal output —  S9 SHPD O External sample-and-hold driver control signal output —  60 INV O External sample-and-hold driver control signal output —  61 VB O VB signal output —  62 HB O HB signal output —  63 Vss — GND —  64 DWN O Up/down inversion signal output —  65 XRGT O Left/right inversion signal (reverse polarity) output —  66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  69 IRACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55         | HST    | 0   | H start pulse output                                  | _                         |

| SHPC O External sample-and-hold driver control signal output —  59 SHPD O External sample-and-hold driver control signal output —  60 INV O External sample-and-hold driver control signal output —  61 VB O VB signal output —  62 HB O HB signal output —  63 Vss — GND —  64 DWN O Up/down inversion signal output —  65 XRGT O Left/right inversion signal (reverse polarity) output —  66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  69 IRACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56         | SHPA   | 0   | External sample-and-hold driver control signal output | _                         |

| 59 SHPD O External sample-and-hold driver control signal output — 60 INV O External sample-and-hold driver control signal output — 61 VB O VB signal output — 62 HB O HB signal output — 63 Vss — GND — 64 DWN O Up/down inversion signal output — 65 XRGT O Left/right inversion signal (reverse polarity) output — 66 RGT O Left/right inversion signal output — 67 XVS O Auxiliary pulse output — 68 XHS O Auxiliary pulse output — 69 IRACT O Auxiliary pulse output — 70 ORACT O Auxiliary pulse output — 71 Vss — GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57         | SHPB   | 0   | External sample-and-hold driver control signal output | _                         |

| 60 INV O External sample-and-hold driver control signal output — 61 VB O VB signal output — 62 HB O HB signal output — 63 Vss — GND — 64 DWN O Up/down inversion signal output — 65 XRGT O Left/right inversion signal (reverse polarity) output — 66 RGT O Left/right inversion signal output — 67 XVS O Auxiliary pulse output — 68 XHS O Auxiliary pulse output — 69 IRACT O Auxiliary pulse output — 70 ORACT O Auxiliary pulse output — 71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58         | SHPC   | 0   | External sample-and-hold driver control signal output | _                         |

| 61 VB O VB signal output —  62 HB O HB signal output —  63 Vss — GND —  64 DWN O Up/down inversion signal output —  65 XRGT O Left/right inversion signal (reverse polarity) output —  66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  69 IRACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59         | SHPD   | 0   | External sample-and-hold driver control signal output | _                         |

| 62 HB O HB signal output —  63 Vss — GND —  64 DWN O Up/down inversion signal output —  65 XRGT O Left/right inversion signal (reverse polarity) output —  66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  69 IRACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60         | INV    | 0   | External sample-and-hold driver control signal output | _                         |

| 63 Vss — GND —  64 DWN O Up/down inversion signal output —  65 XRGT O Left/right inversion signal (reverse polarity) output —  66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  69 IRACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61         | VB     | 0   | VB signal output                                      | _                         |

| 64       DWN       O       Up/down inversion signal output       —         65       XRGT       O       Left/right inversion signal (reverse polarity) output       —         66       RGT       O       Left/right inversion signal output       —         67       XVS       O       Auxiliary pulse output       —         68       XHS       O       Auxiliary pulse output       —         69       IRACT       O       Auxiliary pulse output       —         70       ORACT       O       Auxiliary pulse output       —         71       Vss       —       GND       —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 62         | НВ     | 0   | HB signal output                                      | _                         |

| 65 XRGT O Left/right inversion signal (reverse polarity) output — 66 RGT O Left/right inversion signal output — 67 XVS O Auxiliary pulse output — 68 XHS O Auxiliary pulse output — 69 IRACT O Auxiliary pulse output — 70 ORACT O Auxiliary pulse output — 71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63         | Vss    | _   | GND                                                   | _                         |

| 66 RGT O Left/right inversion signal output —  67 XVS O Auxiliary pulse output —  68 XHS O Auxiliary pulse output —  69 IRACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64         | DWN    | 0   | Up/down inversion signal output                       | _                         |

| 67 XVS O Auxiliary pulse output — 68 XHS O Auxiliary pulse output — 69 IRACT O Auxiliary pulse output — 70 ORACT O Auxiliary pulse output — 71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65         | XRGT   | 0   | Left/right inversion signal (reverse polarity) output | _                         |

| 68 XHS O Auxiliary pulse output —  69 IRACT O Auxiliary pulse output —  70 ORACT O Auxiliary pulse output —  71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66         | RGT    | 0   | Left/right inversion signal output                    | _                         |

| 69 IRACT O Auxiliary pulse output — 70 ORACT O Auxiliary pulse output — 71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67         | XVS    | 0   | Auxiliary pulse output                                | _                         |

| 70 ORACT O Auxiliary pulse output — 71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68         | XHS    | 0   | Auxiliary pulse output                                | _                         |

| 71 Vss — GND —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69         | IRACT  | 0   | Auxiliary pulse output                                | _                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70         | ORACT  | 0   | Auxiliary pulse output                                | _                         |

| 72 TST10 — Test pin (Not connected.) —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71         | Vss    | _   | GND                                                   | _                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72         | TST10  | _   | Test pin (Not connected.)                             | _                         |

| Pin<br>No. | Symbol | I/O | Description                   | Input pin for open status |

|------------|--------|-----|-------------------------------|---------------------------|

| 73         | VDD    | _   | Power supply                  | _                         |

| 74         | TST11  | _   | Test pin (connect to VDD)     | _                         |

| 75         | TST12  | _   | Test pin (connect to VDD)     | _                         |

| 76         | TST13  | _   | Test pin (connect to VDD)     | _                         |

| 77         | Vss    | _   | GND                           | _                         |

| 78         | XCLR   | I   | System clear (Low: All clear) | Н                         |

| 79         | TST14  | _   | Test pin (Not connected.)     | _                         |

| 80         | TST15  | _   | Test pin (Not connected.)     | _                         |

<sup>\*</sup> H: Pull-up, L: Pull-down

# **Electrical Characteristics**

# • DC characteristics

$(Topr = -20 \text{ to } +75^{\circ}C, Vss = 0V)$

| Item                | Symbol                  | Conditions                                               | Min.                                  | Тур.                    | Max.                            | Unit | Applicable pins   |  |

|---------------------|-------------------------|----------------------------------------------------------|---------------------------------------|-------------------------|---------------------------------|------|-------------------|--|

| Supply voltage      | VDD                     | _                                                        | 3.0                                   | 3.3                     | 3.6                             |      | _                 |  |

| Input voltage 1     | Vıн1                    | 3.3V CMOS input                                          | 0.65VDD                               | _                       | VDD                             |      | SLHR, SLFR,       |  |

| input voltage i     | VıL1                    | 3.3V CIVIOS IIIput                                       | Vss                                   | _                       | 0.25Vpd                         |      | XCLR, SLCK1/2     |  |

| Input voltage 2     | Vıн2                    | 5.0V CMOS input                                          | 0.65VDD                               | _                       | VDD + 1.9                       |      | CKI2, CKI4        |  |

| mpar remage _       | VıL2                    | 5.07 CIVIOS IIIput                                       | Vss                                   | _                       | 0.25Vpd                         |      | CKIZ, CKI4        |  |

| Input voltage 3     | Vıн3                    | 5.0V CMOS                                                | 0.8Vpd                                | _                       | VDD + 1.9                       |      | SCLK, SDAT, SCTL, |  |

| mp at remage e      | VıL3                    | Schmitt trigger input                                    | Vss                                   | _                       | 0.2Vdd                          | V    | VSYNC, HSYNC      |  |

| Input voltage 4     | Vc<br>(center<br>level) | Low amplitude                                            | (V <sub>DD</sub> ×<br>0.606)<br>- 0.1 | V <sub>DD</sub> × 0.606 | (V <sub>DD</sub> × 0.606) + 0.1 |      | CKI1/XCKI1,       |  |

| Input voltage       | Vін4*1                  | differential input                                       | VIL4 + 0.3                            | _                       | VDD                             |      | CKI3/XCKI3        |  |

|                     | V1L4*1                  |                                                          | Vss                                   | _                       | Vін4 — 0.3                      |      |                   |  |

| Output voltage 1    | Vон                     | Iон = −4mA                                               | VDD - 0.5                             | _                       | VDD                             |      | *2                |  |

| Output voitage i    | Vol                     | IoL = 4mA                                                | Vss                                   | _                       | 0.4                             |      | _                 |  |

| Output voltage 2    | Vон                     | Iон = −8mA                                               | VDD - 0.5                             |                         | VDD                             |      | VCK, BLK, VST,    |  |

| Output voitage 2    | Vol                     | IoL = 8mA                                                | Vss                                   |                         | 0.4                             |      | ENB, PCG          |  |

| Output voltage 3    | Vон                     | Iон = −12mA                                              | VDD - 0.5                             |                         | VDD                             |      | HCK1, HCK2,       |  |

| Output voltage 3    | Vol                     | IoL = 12mA                                               | Vss                                   |                         | 0.4                             |      | HST               |  |

| Input pull-up/pull- | Rp                      | Pull-up Vı = 0V                                          | 25                                    | 50                      | 200                             | kΩ   | SLHR, XCLR        |  |

| down resistance     | I KP                    | Pull-down VI = VDD                                       | 25                                    | 30                      | 200                             | K32  | SLFR, SLCK1/2     |  |

| Current consumption | loo                     | Master clock = 95MHz<br>VDD = 3.3V<br>Output load = 30pF | _                                     |                         | 40                              | mA   | _                 |  |

<sup>\*1</sup> VIH4 > (max. value of Vc) and <math>VIL4 < (min. value of Vc)

$<sup>^{*2}</sup>$  Output pins other than those indicated in items output voltage 2 and output voltage 3.

# AC characteristics

| Item                        | Symbol        | Applicable pins            | Conditions | Min.       | Тур. | Max. | Unit |

|-----------------------------|---------------|----------------------------|------------|------------|------|------|------|

| Clock input cycle           | _             | CKI1/XCKI1,<br>CKI3/XCKI3  | _          | 10.5       | _    | _    |      |

|                             |               | CKI2, CKI4                 | _          | 10.5       |      | _    |      |

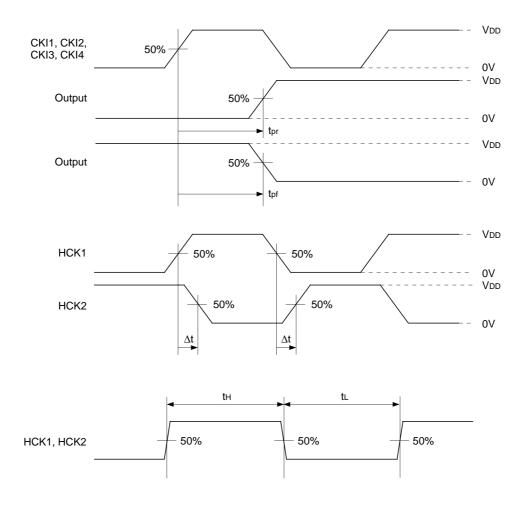

| Output rise/fall delay time | tpr/tpf       | HCK1, HCK2, HST            | CL = 90pF  |            |      |      | ns   |

| Output rise/fall delay time | tpr/tpf       | VCK, BLK, VST,<br>ENB, PCG | CL = 50pF  | _          | _    | 25   | 115  |

| Output rise/fall delay time | tpr/tpf       | Other output pins          | CL = 30pF  |            |      |      |      |

| Cross-point time difference | Δt            | HCK1, HCK2                 | CL = 90pF  | <b>-</b> 5 | _    | 5    |      |

| Duty ratio                  | tн/ (tн + t∟) | HCK1, HCK2                 | CL = 90pF  | 48         | 50   | 52   | %    |

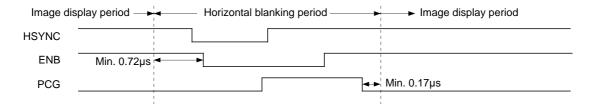

# **Timing Definitions**

# **Serial Interface AC Characteristics**

| (Topr = -20 to - | +75°C Vpp =             | 3.3V + 0.3V   | $V_{SS} = 0V$ |

|------------------|-------------------------|---------------|---------------|

| (1001 - 2010     | 110 O, VDD <del>-</del> | 0.0 v ± 0.0 v | , voo – o v   |

| Item                                         | Symbol | Min. | Тур. | Max. |

|----------------------------------------------|--------|------|------|------|

| SCTL setup time with respect to rise of SCLK | ts0    | 8T*3 | _    | _    |

| SCTL hold time with respect to rise of SCLK  | th0    | 8T   | _    | _    |

| SDAT setup time with respect to rise of SCLK | ts1    | 4T   | _    | _    |

| SDAT hold time with respect to rise of SCLK  | th1    | 4T   | _    | _    |

| SCLK pulse width                             | tw1    | 4T   | _    | _    |

<sup>\*3</sup> T: Master clock cycle (ns)

# **Timing Definitions**

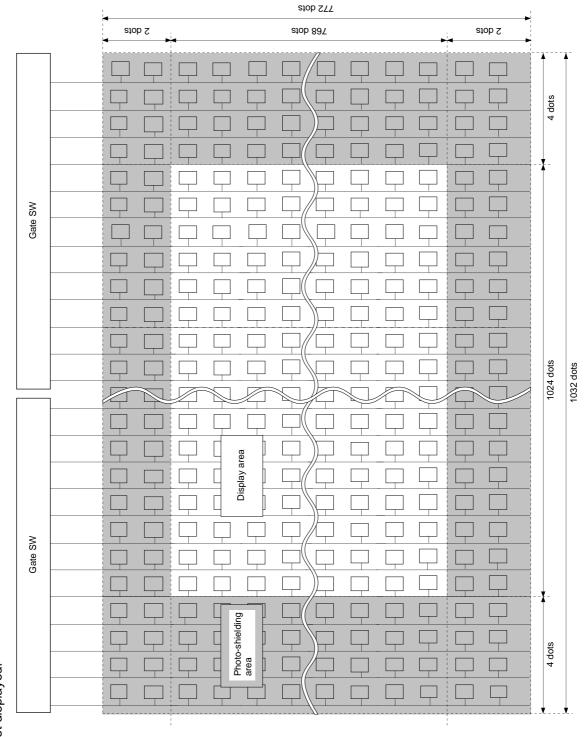

# **LCD Panel Dot Arrangement**

The dot arrangement of the LCD panel (LCX017AL) driven with this IC is shown below. The dot arrangement is a square arrangement. The shaded region in the diagram is not displayed.

#### **Description of Operation**

#### Sync signal input pins (HSYNC, VSYNC)

Horizontal and vertical separate SYNC signals are input to the HSYNC (Pin 29) and VSYNC (Pin 28). The sync signals are compatible with both positive and negative polarity according to serial data settings. (Refer to the section on serial data interface for details regarding serial data.)

The CXD2453Q supports signals which are shown in the following table.

| Effective dots      | Horizontal scanning frequency | Vertical scanning frequency | Remarks                                                  |

|---------------------|-------------------------------|-----------------------------|----------------------------------------------------------|

| 1024 × 768 (XGA)    | 44kHz to 69kHz                | 55Hz to 85Hz                |                                                          |

| 1280 × 1024 (S-XGA) | ≤ 69kHz                       | Roughly ≤ 65Hz              | Scanning line conversion from 1024 to 768 vertical lines |

In the case of signals defined by special protocols that do not satisfy the conditions in the diagram below, it may not be possible to obtain a complete display even for the above signals when the image display position is properly set on the LCD panel. This IC does not support interlace signals.

#### Master clock input pins (CKI1/XCKI1, CKI2, CKI3/XCKI3, CKI4) and Clock Selection Pins (SLCK1, SLCK2)

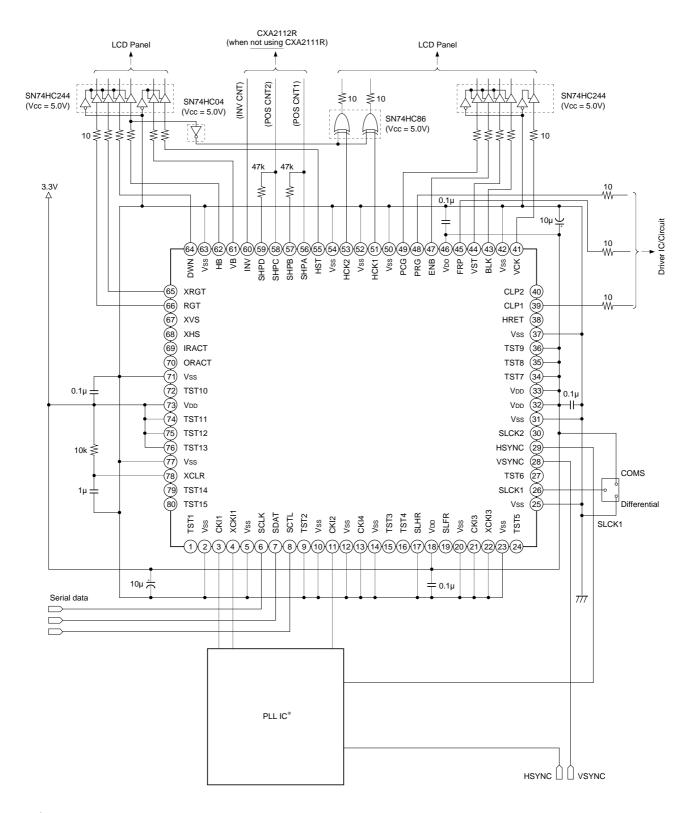

Since this IC does not contain a built-in phase comparator, phase comparison is performed externally and a divided clock is input. The 1/N (N is the clock number during 1 horizontal period) frequency divider output is output from the HRET (Pin 38) for the external phase comparator.

The clock input pin consists of two channels for small amplitude differential input (center level: 2.0V, amplitude:  $\pm 0.4$ V), and two channels for CMOS level input for a total of four channels. These are selected according to the SLCK1 (Pin 26), SLCK2 (Pin 30) and serial data.

- (1) During normal operation (serial data SLLAP = 0) All internal circuits of the IC operate with CKI1 or CKI2. CKI1/XCKI1 are selected when SLCK1 = L (Pins 3/4, small amplitude differential input), and CKI2 is selected when SLCK1 = H (Pin 11, CMOS level input).

- (2) When using scan converter (serial data SLLAP = 1) This is used when the input signal clock and output signal clock are different such as when performing dot conversion using a scan converter. Only the serial data interface and PLL counter of the IC internal circuits operate with CKI1 or CKI2 (clock synchronized with input signal). All other blocks operate with CKI3 or CKI4 (output signal clock). CKI3/XCKI13 are selected when SLCK2 = L (Pins 21/22, small amplitude differential input), and CKI4 is selected when SLCK2 = H (Pin 13, CMOS level input).

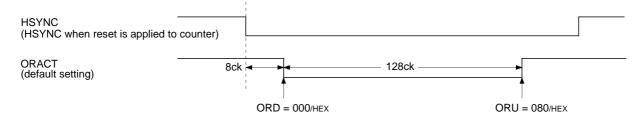

#### Internal frequency divider reset selection pin (SLHR)

This selects whether reset of the PLL counter (loop counter) with HSYNC is to be enabled or disabled. In the case of performing phase comparison of the HSYNC and HRET pulses with an external phase comparator, the SLHR (Pin 17) is set to H (reset disabled). When phase comparison and frequency division are performed externally and HRET pulses for phase comparison are not used, the SLHR is set to L (reset enabled). At this time, the output of each pulse is delayed by approximately 8 clocks as compared with using HRET pulses for phase comparison.

#### Signal inversion type selection pin (SLFR)

This selects the inversion cycle of the polarity inversion pulse (FRP pulse) for AC driving. Setting the SLFR (Pin 19) to H results in field inversion, while setting the SLFR to L results in line inversion.

# System clear pin (XCLR)

All internal circuits are initialized when the XCLR (Pin 78) is L. Always make sure to initialize all internal circuits when the power has been turned on.

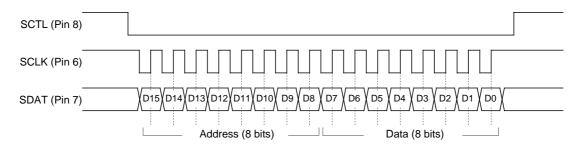

#### Serial data interface

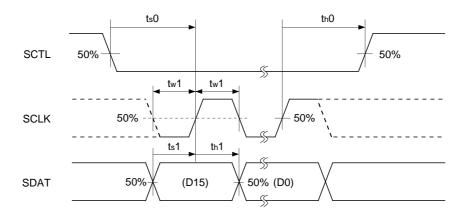

Operating mode and other settings in this IC are performed by serial data. When the power is turned on, all data are set to the default values when the internal circuits are initialized. When the power supply is turned on, the value of SDAT is read with the rise of SCLK in groups of 16 bits consisting of 8 address bits and 8 data bits as shown in the Timing Chart below. The data that has been read is enabled by being transferred to the register corresponding to each address 10 clocks after the rise of SCLK of the 16th bit.

The Timing Chart and Data Format during transmission of serial data are as shown below.

# **Timing Chart**

#### **Data Format**

| Address   | Data |      |      |       |       |       |      |      | Settings                   |

|-----------|------|------|------|-------|-------|-------|------|------|----------------------------|

| D15 to D8 | D7   | D6   | D5   | D4    | D3    | D2    | D1   | D0   | Settings                   |

| F0        | _    | _    | _    | _     | _     | PLP10 | PLP9 | PLP8 | PLL counter frequency      |

| F1        | PLP7 | PLP6 | PLP5 | PLP4  | PLP3  | PLP2  | PLP1 | PLP0 | division ratio             |

| F2        | HP7  | HP6  | HP5  | HP4   | HP3   | HP2   | HP1  | HP0  | Screen horizontal position |

| F3        | VP7  | VP6  | VP5  | VP4   | VP3   | VP2   | VP1  | VP0  | Screen vertical position   |

| F4        | _    | _    | _    | INV   | SHP3  | SHP2  | SHP1 | SHP0 | CXA2112R S/H control       |

| F5        | _    | _    | VPOL | HPOL  | VSCN  | HSCN  | SLXG | SLSX | Operating mode, etc.       |

| F6        | _    | _    | НВ   | VB    | SLLAP | IRD10 | IRD9 | IRD8 | Operating mode, etc./      |

| F7        | IRD7 | IRD6 | IRD5 | IRD4  | IRD3  | IRD2  | IRD1 | IRD0 | IRACT fall position        |

| F8        | _    | _    | _    | _     |       | IRU10 | IRU9 | IRU8 | IRACT rise position        |

| F9        | IRU7 | IRU6 | IRU5 | IRU4  | IRU3  | IRU2  | IRU1 | IRU0 | TRACT fise position        |

| FA        | _    | _    | _    | ORRS1 | ORRS0 | ORP10 | ORP9 | ORP8 | ORACT reset cycle/         |

| FB        | ORP7 | ORP6 | ORP5 | ORP4  | ORP3  | ORP2  | ORP1 | ORP0 | ORACT division frequency   |

| FC        | _    | _    | _    | _     |       | ORD10 | ORD9 | ORD8 | OBACT fall position        |

| FD        | ORD7 | ORD6 | ORD5 | ORD4  | ORD3  | ORD2  | ORD1 | ORD0 | ORACT fall position        |

| FE        |      |      |      |       |       | ORU10 | ORU9 | ORU8 | ORACT rise position        |

| FF        | ORU7 | ORU6 | ORU5 | ORU4  | ORU3  | ORU2  | ORU1 | ORU0 | ONACT TISE POSITION        |

Note) —: Don't care

The following provides a detailed description of each setting.

#### (a) Setting of PLL counter frequency division ratio

This is used to set the frequency division ratio of the 1/N frequency divider (PLL counter) for phase comparison. The value of (total number of dots of 1 horizontal period N) – 1 is set with PLP10 (MSB) through PLP0 (LSB). The frequency division ratio can be set up to 2048. Only even numbers can be set for the value of N. When it is necessary to set an odd number, use an external frequency divider. In this case, set the value of the frequency division ratio of the PLL counter to N-2.

The default value is 101001111111 (N = 1344).

#### (b) Setting of screen horizontal position

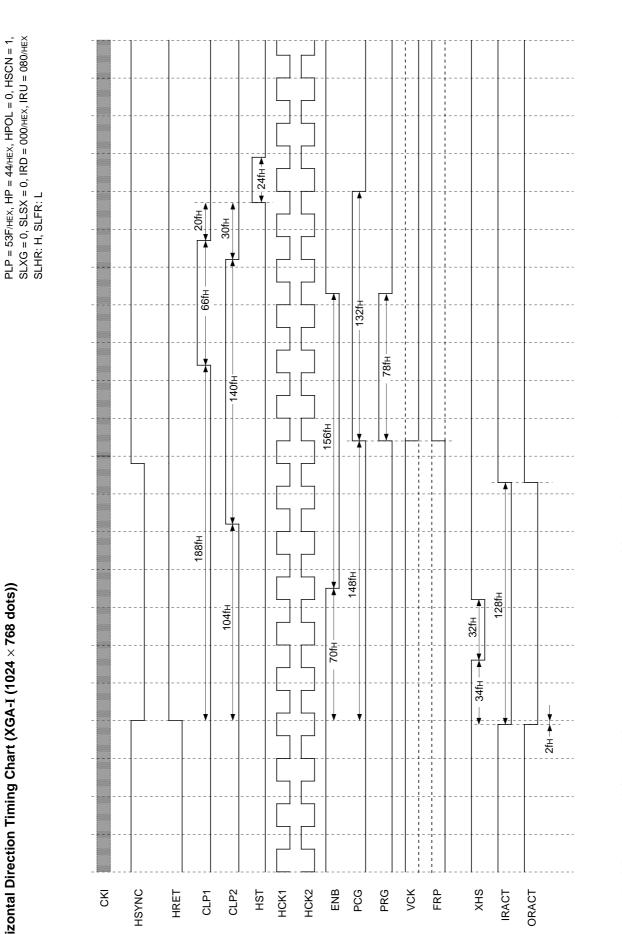

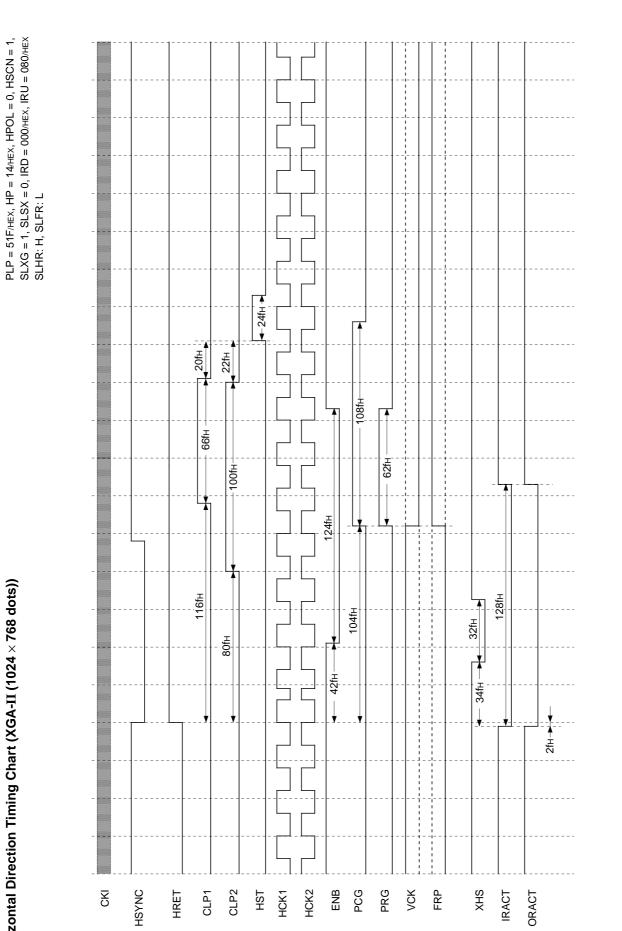

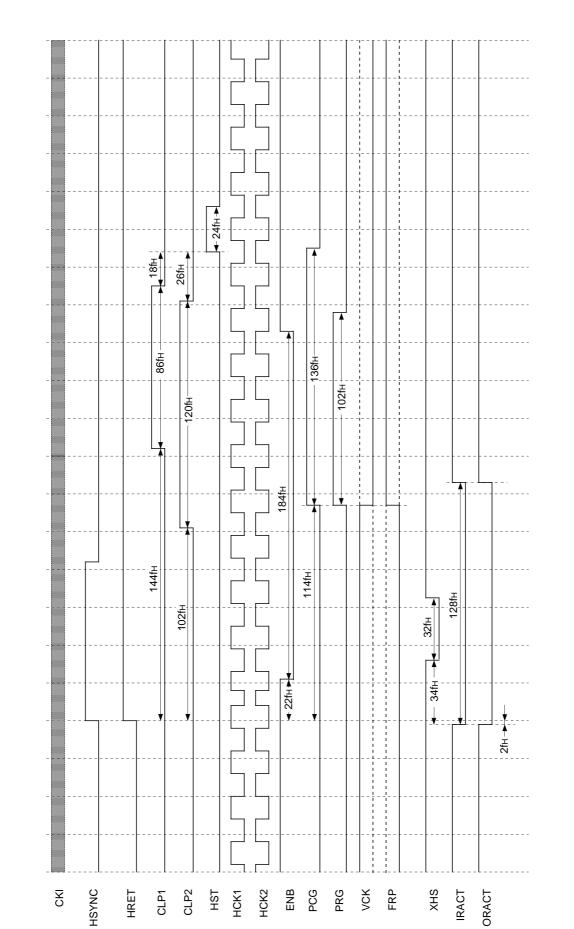

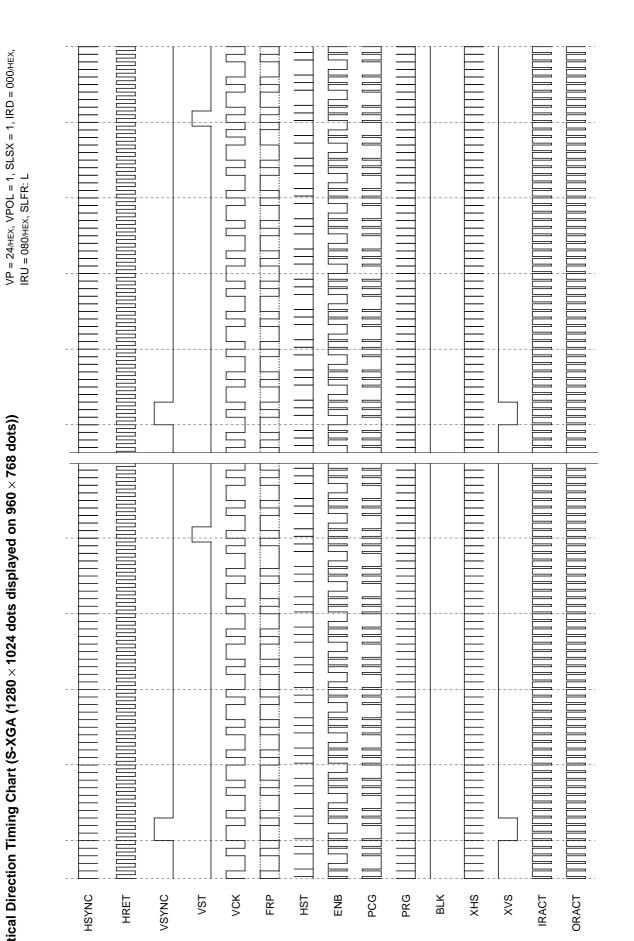

The horizontal display start position is set with HP7 (MSB) through HP0 (LSB). This setting enables the phase relationships of pulses HST, HCK1/2, ENB, PCG, PRG and CLP1/2 as well as the changing positions of VCK/FRP relative to HSYNC to change in an interlocked manner. Settings can be made in 1 dot units. Refer to the Timing Chart for the relationship between the set value and each pulse position.

The default value is 01000100.

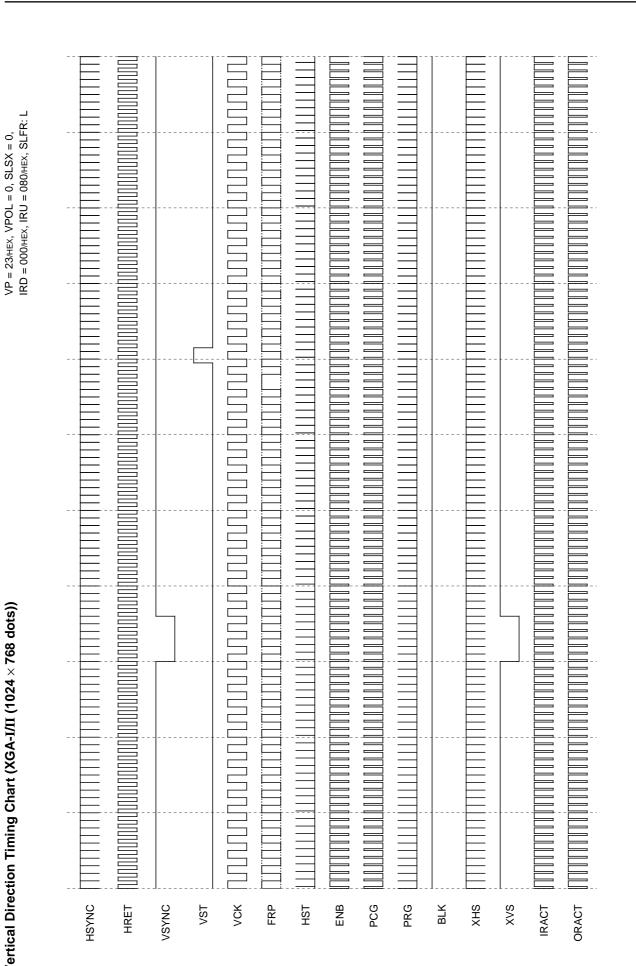

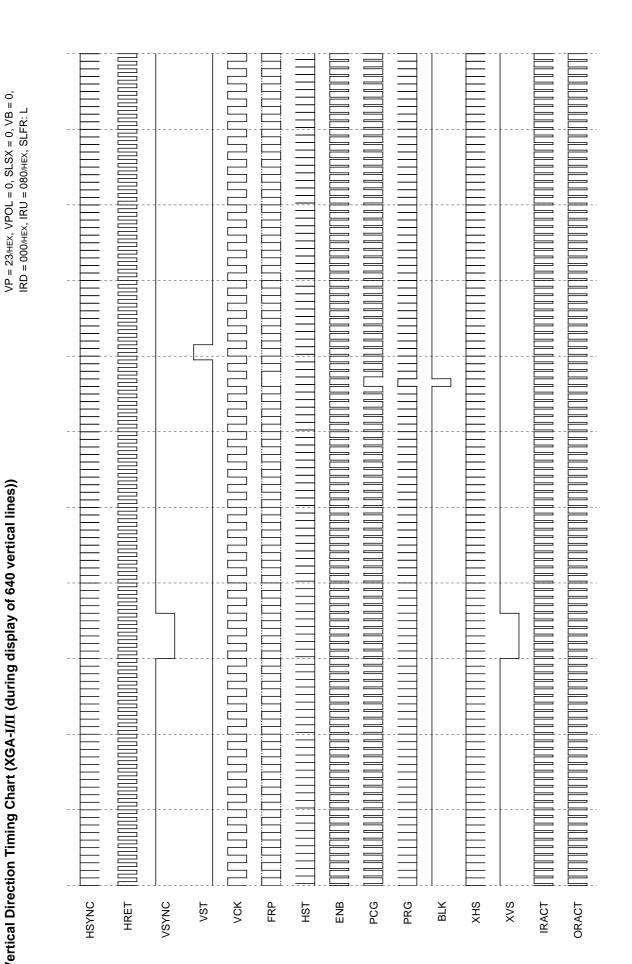

## (c) Setting of screen vertical position

The vertical display start position is set with VP7 (MSB) through VP0 (LSB). This setting enables the phase relationships of signals VST, VCK and FRP to change relative to VSYNC in an interlocked manner. Settings can be made in 1 line units. Refer to the Timing Chart for the relationship between the set value and each signal.

The default value is 00100011. 00000000 and 11111111 are not used.

### (d) S/H control of CXA2112R

This is used to set the sample-and-hold position for the CXA2112R (sample-and-hold driver). INV setting data is output directly from the INV (Pin 60). Setting data of SHP3 (MSB) through SHP0 (LSB) is reflected as shown below in the SHPA through SHPD (Pins 56 to 59). Refer to the specifications of the CXA2112R for details.

| Setting data |      | Out  | tput |      | Setting data |      | Out  | tput |      |

|--------------|------|------|------|------|--------------|------|------|------|------|

| SHP3 to SHP0 | SHPA | SHPB | SHPC | SHPD | SHP3 to SHP0 | SHPA | SHPB | SHPC | SHPD |

| 0000         | L    | L    | L    | L    | 1000         | L    | L    | Z    | L    |

| 0001         | Н    | Н    | L    | L    | 1001         | Н    | Н    | Z    | L    |

| 0010         | Z    | L    | L    | L    | 1010         | Z    | L    | Z    | L    |

| 0011         | Z    | Н    | L    | L    | 1011         | Z    | Н    | Z    | L    |

| 0100         | L    | L    | Н    | Н    | 1100         | L    | L    | Z    | Н    |

| 0101         | Н    | Н    | Н    | Н    | 1101         | Н    | Н    | Z    | Н    |

| 0110         | Z    | L    | Н    | Н    | 1110         | Z    | L    | Z    | Н    |

| 0111         | Z    | Н    | Н    | Н    | 1111         | Z    | Н    | Z    | Н    |

Note) Z: High impedance state

#### (e) Setting of operating mode, etc.

• VPOL, HPOL: These are used to set the polarity of VSYNC and HSYNC. A setting of "1" denotes positive polarity, while a setting of "0" denotes negative polarity.

The default values are VPOL = 0, HPOL = 0.

VSCN, HSCN: These are used to set the vertical and horizontal scanning directions of the LCD panel. VSCN = 1 denotes downward scanning, while VSCN = 0 denotes upward scanning. HSCN = 1 denotes rightward scanning, while HSCN = 0 denotes leftward scanning. Setting data of VSCN is output from the DWN (Pin 64), while setting data of HSCN is output from the RGT (Pin 66).

The default values are VSCN = 0, HSCN = 1.

SLXG, SLSX: These are used to set the input signals (operating mode). This IC has the following three

operating modes.

The default values are SLXG = 0, SLSX = 0.

| Operating mode | SLXG | SLSX |  |

|----------------|------|------|--|

| XGA-I          | 0    | 0    |  |

| XGA-II         | 1    | 0    |  |

| S-XGA          | Х    | 1    |  |

Note) X: Don't care

The XGA-I mode supports typical XGA signals. The XGA-II mode is for XGA signals in which there is a low number of dots during a portion of the horizontal blanking period (typically when HSYNC + back porch is 240 dots or less). Select the appropriate operating mode to satisfy the conditions in the diagram on page 6 corresponding to the input signal. In the S-XGA mode, 1024 vertical lines are displayed decimating to 768 lines corresponding to the S-XGA signal  $(1280 \times 1024 \text{ dots})$ .

• HB, VB: These are used to switch the number of display dots on the LCD panel. The display is set to 960 dots horizontally when HB = 0, and to 640 lines vertically when VB = 0. The data of each setting is output from the HB (Pin 62) and VB (Pin 61), respectively. Refer to the specifications of the LCX017AL for details.

The default values are HB = 1, VB = 1.

• SLLAP: This is used when the input signal clock and output signal clock differ such as when converting the number of dots using a scan converter. When SLLAP = 1, only the serial data interface and PLL counter of the IC internal circuits operate with CKI1 or CKI2 (clock synchronized with input signal), while other sections operated with CKI3 or CKI4 (output signal clock). When SLLAP = 0, all internal IC circuits operate with CKI1 or CKI2.

The default value is 0.

# (f) Setting of IRACT fall/rise positions

IRACT pulse

A pulse synchronized with HSYNC of the input signal can be output at any position and width. The fall position of the pulse is set with IRD10 (MSB) through IRD0 (LSB), while the rise position is set with IRU10 (MSB) through IRU0 (LSB). The values of IRD0 and IRU0 are ignored, and settings are made in 2-dot increments. The setting range is from "0" to (N-2). The same value cannot be set for IRD and IRU. Refer to the Timing Chart for the relationship between setting values and pulse positions.

The default values are IRD10 through IRD0 = 00000000000, and IRU10 through IRU0 = 00010000000.

# (g) Setting of ORACT reset cycle/ORACT frequency division ratio

#### ORACT pulses