# **CXD2107M**

# **Hi8 System Detection IC**

#### Description

The CXD2107M is a Hi8 system detection IC that uses composite sync and RF signal input to determine whether the Hi8 system or the standard 8 mm system is being used.

#### **Features**

- TTL level-compatible at I/O level

- Single 5V power supply

## **Applications**

Hi8 system detection

# Absolute Maximum Ratings (Ta=25 ℃)

| <ul> <li>Supply voltage</li> </ul>        | $V_{DD}$ | Vss-0.5 to +7.0    | ٧  |

|-------------------------------------------|----------|--------------------|----|

| <ul><li>Input voltage</li></ul>           | Vı       | Vss-0.5 to Vpp+0.5 | ٧  |

| <ul> <li>Output voltage</li> </ul>        | Vo       | Vss-0.5 to Vpp+0.5 | ٧  |

| <ul> <li>Operating temperature</li> </ul> | Topr     | -20 to +75         | °C |

| <ul> <li>Storage temperature</li> </ul>   | Tstg     | -55 to +150        | °C |

\* Vss=0V

# **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul>        | V <sub>DD</sub> +4.5 to +5.5 |            | V  |  |

|-------------------------------------------|------------------------------|------------|----|--|

| <ul> <li>Operating temperature</li> </ul> | Topr                         | -20 to +75 | °C |  |

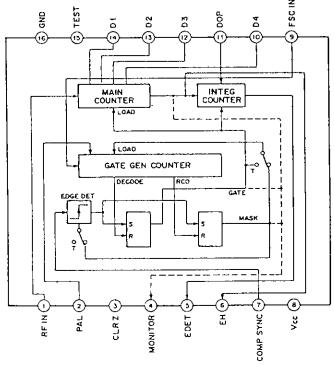

## **Block Diagram**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

#### Structure

Silicon gate CMOS IC

#### **Description of Functions**

This IC counts the number of pulses in the RF signal during the composite sync interval in order to discriminate between E (Hi8) mode and L (standard) mode.

Theoretical values (4.5 µs interval during composite sync)

| 8mm (standard) | 19 |

|----------------|----|

| (Hi8)          | 26 |

| VHS            | 15 |

| S-VHS          | 24 |

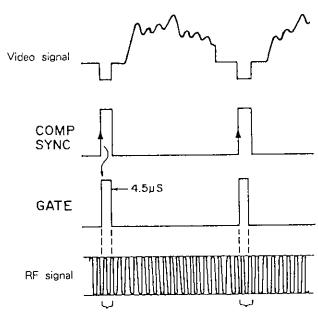

An approximately 4.5 µs interval gate is created using the rising edge of COMP SYNC as a reference.

The count value can be changed according to the settings of D1 through D4 pins, and when the number of pulses in the RF signal exceeds the count value, the EH pin is judged to be high.

For example, by setting the count value between 19 and 26 for an 8 mm VCR, it is possible to discriminate between standard and Hi8.

In addition, for EDET, mode discrimination is made when either L mode or E mode continues for 16H. If the mode does not continue for 16H, the internal counter is reset and the count is restarted. In such instances, the previous mode is held.

E/L discrimination is made by counting the number of pulses in the RF signal corresponding to the Sync Tip portion.

# Pin Description

| Pin No. | Symbol   | I/O         | Description                                                                                       |  |  |  |  |  |  |

|---------|----------|-------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1       | RFIN     | 1           | PBY RF signal input.                                                                              |  |  |  |  |  |  |

| 2       | PAL      | ı           | PAL/NTSC switching. High: PAL; Low: NTSC                                                          |  |  |  |  |  |  |

| 3       | CLRZ     | Į.          | Internal counter clear. Normally high.                                                            |  |  |  |  |  |  |

| 4       | MONITOR  | O<br>3STATE | Monitor of GATE pulse, MASK pulse and counter output pulse.  H H Z MASK  GATE  COUNT              |  |  |  |  |  |  |

| 5       | EDET     | 0           | E discrimination output. Output 16H continuous detection for EH output. High: E mode; Low: L mode |  |  |  |  |  |  |

| 6       | EH       | 0           | E discrimination output monitored in 1H units. High: E mode; Low: L mode                          |  |  |  |  |  |  |

| 7       | COMPSYNC | I           | Composite sync input.                                                                             |  |  |  |  |  |  |

| 8       | Vcc      |             | Power supply (+5V)                                                                                |  |  |  |  |  |  |

| 9       | FSCIN    | I           | Color subcarrier (fsc) input. Used as reference clock. NTSC: 3.579545MHz; PAL: 4.433619MHz        |  |  |  |  |  |  |

| 11      | DOP      | I           | Drop-out compensation pulse input, EDET output is maintained when high.                           |  |  |  |  |  |  |

| 10      | D4       | l           | MAIN COUNTER DATA setting.                                                                        |  |  |  |  |  |  |

|         |          |             |                                                                                                   |  |  |  |  |  |  |

| 12      | D3       | 1           | D2                                                                                                |  |  |  |  |  |  |

| 10      | D0       | ,           | D3                                                                                                |  |  |  |  |  |  |

| 13      | D2       | !           | D4 L L L L L L L H H H H H H H                                                                    |  |  |  |  |  |  |

| 14      | D1       | I           | Count 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17                                             |  |  |  |  |  |  |

| 15      | TEST     | l           | TEST control input. Composite sync input MASK is turned off when high. Normally low.              |  |  |  |  |  |  |

| 16      | GND      |             | GND.                                                                                              |  |  |  |  |  |  |

# **Electrical Characteristics**

# • DC characteristics

(V<sub>DD</sub>=5V  $\pm$  10%, Vss=0V, Topr=-20 to +75  $^{\circ}$ C )

| Item                   | Symbol | Conditions           | Min.        | Тур. | Max. | Unit         |

|------------------------|--------|----------------------|-------------|------|------|--------------|

| Supply voltage         | VDD    |                      | 4.5         | 5.0  | 5.5  | V            |

| Input voltage          | VIHT   | - TTL input cell     | 2.2         |      |      | V            |

|                        | VILT   |                      | _           |      | 0.8  | ٧            |

| Input amplitude        | Vin    | RFIN and FSCIN pin * | 0.3         |      |      | <b>V</b> p-p |

| Output voltage Voн VoL | Voн    | loн=-4mA             | 3.7         |      |      | V            |

|                        | Vol    | loL=4mA              | • • •       |      | 0.4  | V            |

| Input leak current     | lu     |                      | -10         |      | 10   | μA           |

| Output leak current    | loz    |                      | <i>–</i> 40 |      | 40   | μА           |

<sup>\*</sup> Maximum input frequency: 10MHz

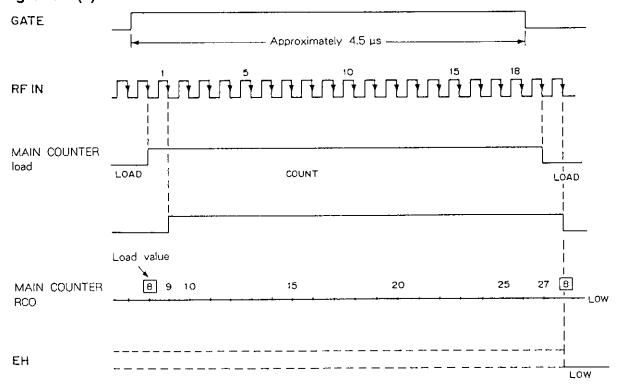

### Timing Chart (1)

For Hi8 (In the example where MAIN COUNT is 24, D1 to 3 are low and D4 is high.)

\* When Hi8 is being used, the MAIN COUNTER counts 24 pulses and EH is high.

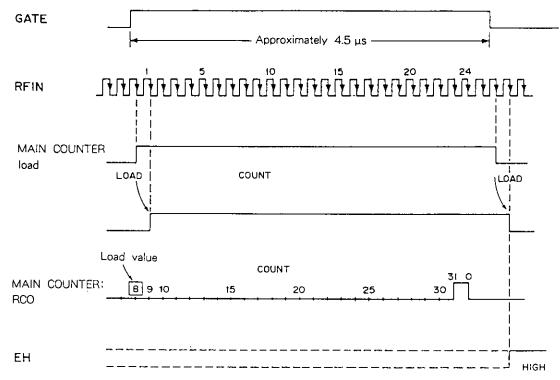

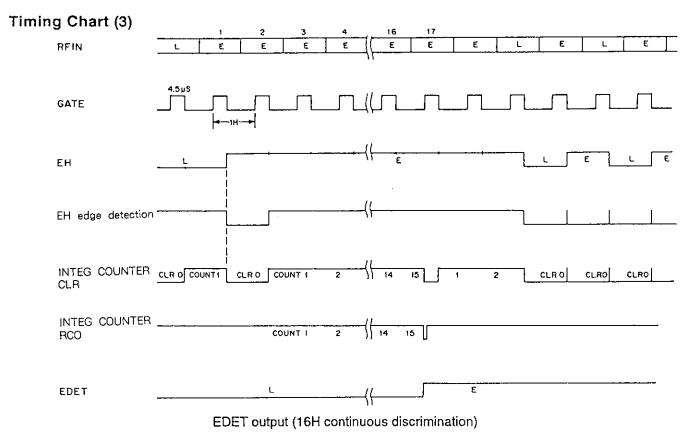

# Timing Chart (2)

For standard (In the example where MAIN COUNT is 24, D1 to 3 are low and D4 is high.)

\* When standard is being used, the MAIN COUNTER can not count 24 pulses and EH is low.

\* If EH output is fixed at one level for 16H continuously, EDET is judged to be E or L. If the level is not fixed for 16H continuously, the previous judgment is maintained.

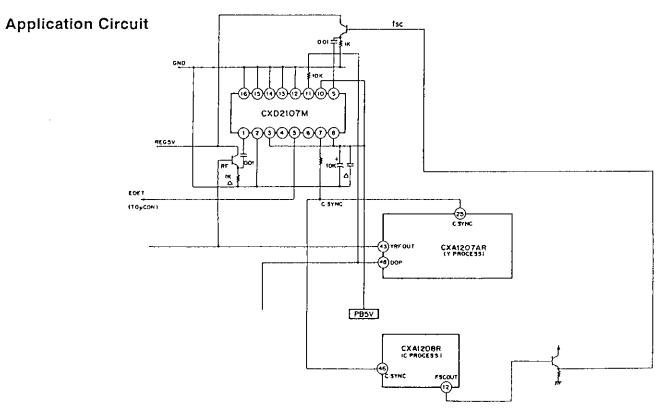

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

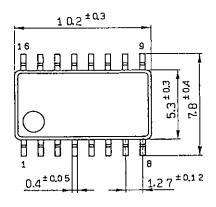

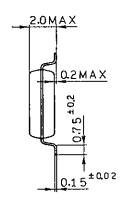

# Package Outline

Unit: mm

16pin 50P (Plastic) 300mil

SONY NAME SOP-16P-L121

EIAJ NAME \*SOP016-P-0300-AX

JEDEC CODE ----