# **CXA1779P**

## **Predriver for High Resolution Computer Displays**

### **Description**

The CXA1779P is a bipolar IC developed for high resolution computer displays.

#### **Features**

- Wide bandwidth (150MHz/-3dB typ.)

- RGB single package

- Permits RGB common and independent contrast control

- Permits RGB independent pedestal level control

- Input D-range: 0.7Vp-p (min.)

#### **Applications**

High resolution computer displays

#### Structure

Bipolar silicon monolithic IC

#### **Absolute Maximum Ratings**

| • | Supply voltage              | Vcc  | 14          | V  |

|---|-----------------------------|------|-------------|----|

| • | Operating temperature       | Topr | -20 to +75  | °C |

| • | Storage temperature         | Tstg | -65 to +150 | °C |

| • | Allowable power dissipation | PD   | 2.8         | W  |

#### **Recommended Operating Conditions**

Supply voltage Vcc 12 ± 0.6 V

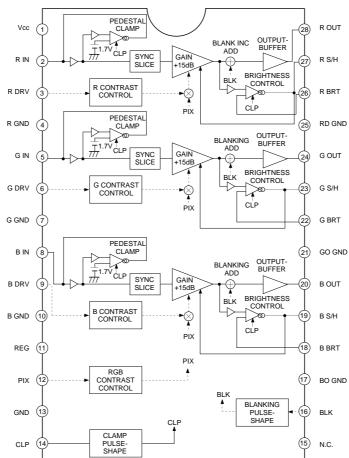

## **Block Diagram and Pin Configuration**

(Top View)

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

## **Pin Description**

| Pin<br>No. | Symbol | Pin voltage | Equivalent circuit          | Description                                                                                                                                      |                           |

|------------|--------|-------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1          | Vcc    | 12V         |                             | Power supply pin.                                                                                                                                |                           |

| 2          | R IN   |             | Vcc200μA                    | RGB input pins.                                                                                                                                  |                           |

| 5          | G IN   | 3.0V        | 2<br>5<br>8<br><b>A</b> 129 | The pedestal level of the input signal is 3.0V during clamping. Connect 0.01µF in series as                                                      |                           |

| 8          | BIN    |             | (8) Δ 129 1 200μA GND       | the clamping capacitor.                                                                                                                          |                           |

| 3          | R DRV  |             | Vcc                         | RGB contrast adjustment                                                                                                                          |                           |

| 6          | G DRV  |             | W 60k                       | pins. The variable range of the pin                                                                                                              |                           |

| 9          | B DRV  | _           | 3 + 1/29                    | 3 voltages is nom (                                                                                                                              | voltages is from 0 to 5V. |

| 12         | PIX    |             | 9 <b>A</b> (12) GND         | RGB simultaneous contrast adjustment pin. The variable range of the pin voltage is from 0 to 5V.                                                 |                           |

| 4          | R GND  |             |                             | OND 1 ( ) 1                                                                                                                                      |                           |

| 7          | G GND  | 0V          |                             | GND pins for the input amplifier block.                                                                                                          |                           |

| 10         | B GND  |             |                             |                                                                                                                                                  |                           |

| 11         | REG    | 5V          | Vcc<br>11                   | <ul> <li>Internal regulator stabilizing pin.</li> <li>5V regulator output pin.</li> <li>Attaches the decoupling capacitance (0.01µF).</li> </ul> |                           |

| 13         | GND    | 0V          |                             | GND pin.                                                                                                                                         |                           |

| 17         | BO GND |             |                             |                                                                                                                                                  |                           |

| 21         | GO GND | 0V          |                             | GND pins for the output stage buffer amplifier block.                                                                                            |                           |

| 25         | RO GND |             |                             | ,                                                                                                                                                |                           |

| Pin<br>No. | Symbol | Pin voltage | Equivalent circuit         | Description                                                                                                                                                                 |

|------------|--------|-------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14         | CLP    | _           | Vcc  129  \$\begin{align*} | <ul> <li>Clamp pulse input pin.</li> <li>Turns the input clamp and the bright level adjustment circuit on and off when high.</li> <li>VH = 3V</li> <li>VL = 1.5V</li> </ul> |

| 15         | N.C.   | _           |                            | Leave this pin open. Connect to GND.                                                                                                                                        |

| 16         | BLK    | _           | Vcc                        | Blanking pulse input pin. Threshold level at approximately 2.25V. VH = 3V VL = 1.5V                                                                                         |

| 18         | B BRT  |             | Vcc200μA200μA              |                                                                                                                                                                             |

| 22         | G BRT  | _           | 18 W 50k                   | RGB bright level adjustment pins. The variable range of the pin voltages is from 0 to 5V.                                                                                   |

| 26         | R BRT  |             | (22)<br>(26) A<br>(SND     |                                                                                                                                                                             |

| 19         | B S/H  |             | Vcc \$                     |                                                                                                                                                                             |

| 23         | G S/H  |             | 19<br>23<br>27             | Pins to externally attach the sample-and-hold capacitor (0.01µF).                                                                                                           |

| 27         | R S/H  |             | GND 200μA 100μA            |                                                                                                                                                                             |

| 20         | B OUT  |             | Vcc                        |                                                                                                                                                                             |

| 24         | G OUT  |             | 20 24                      | RGB output pins.                                                                                                                                                            |

| 28         | R OUT  |             | (24)<br>(28)<br>GND        |                                                                                                                                                                             |

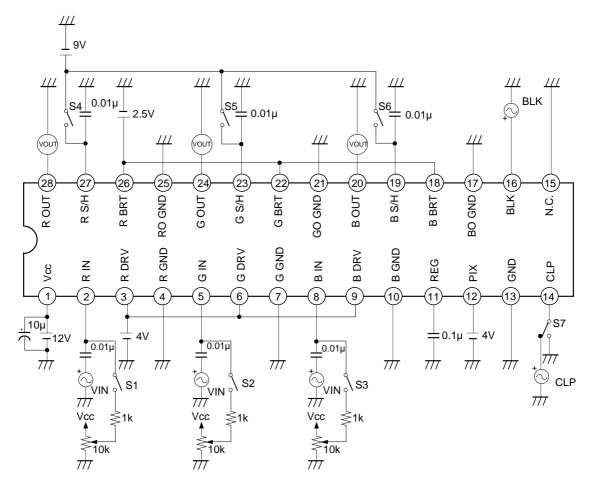

## **Electrical Characteristics**

## (Ta = 25°C, Vcc = 12V, See Electrical Characteristics Measurement Circuit.)

| No. | Item                                                                              | Symbol  | Measurement contents                                                                                                                                                                                                                                               | Min.  | Тур. | Max. | Unit |

|-----|-----------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| 1   | Current consumption                                                               | Icc     | S1 to S7: OFF<br>Input signal: None                                                                                                                                                                                                                                | 50    | 88   | 120  | mA   |

| 2   | Frequency response                                                                | f100MHz | S1 to S7: ON Input continuous 1MHz and 100MHz sine waves at 0.7Vp-p, and measure the gain difference of the output amplitudes.  Gain difference [dB] = 20log (Vout 100M)  RGB input signal (RGB input pin)  RGB input Signal (RGB input pin)  CLP potential        | -3    | -1.5 | _    | dB   |

| 3   | Contrast control                                                                  | CONTMAX | S1 to S7: OFF Input video signal 0.7Vp-p and measure output signal amplitude Vout. Calculate the contrast gain from this Vout.  CONTMAX [dB] = $20log\left(\frac{Vout}{0.7}\right)$ RGB input signal  0.7Vpp  Measuring is possible with or without a sync signal. | 13    | 14   | _    | dB   |

|     | Brightness                                                                        | BRTmax  | S1 to S7: OFF CLP pulse width: 300ns Measure the pedestal level of the RGB output signal.  RGB output signal                                                                                                                                                       | — 3.5 | 3.5  | _    | V    |

| 4   | BRTmin  Pedestal level  GND  Measuring is possible with or without a sync signal. | _       | 1.9                                                                                                                                                                                                                                                                | _     | V    |      |      |

| 5   | Sub contrast gain                                                                 | DRVgain | S1 to S7: OFF Input video signal 0.7Vp-p and measure the variable width of output signal Vout.  Gain difference [dB] = 20log (Vout DRVmin Vout DRVmax)  RGB output signal DRVmax  DRVmin  Measuring is possible with or without a sync signal.                     | _     | -6   | _    | dB   |

| No. | Item                            | Symbol | Measurement contents                                                                                                                                | Min. | Тур. | Max. | Unit |

|-----|---------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| 6   | Input D-range                   | D rang | S1 to S7: OFF Measure the level which maintains the output gain when the input video signal level is varied.                                        | _    | 0.8  |      | Vp-p |

| 7   | Minimum<br>clamp pulse<br>width | CLPmin | S1 to S7: OFF Measure the clamp pulse width where the pedestal level of output signal Vout does not fluctuate.  Video input  Pulse width  CLP pulse | _    | 300  | _    | ns   |

#### **Electrical Characteristics Measurement Circuit**

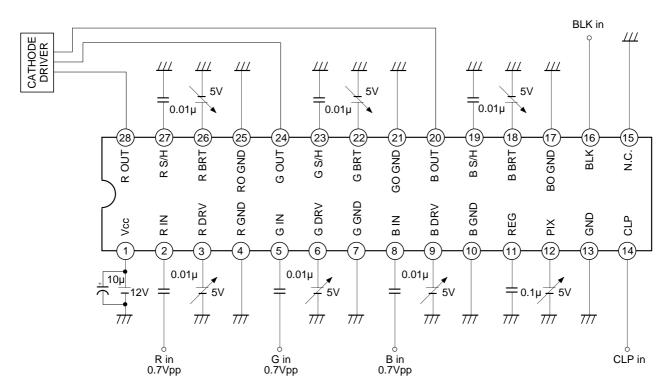

#### **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Description of Operation**

#### 1. Contrast control

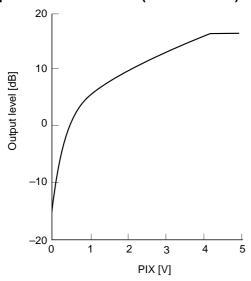

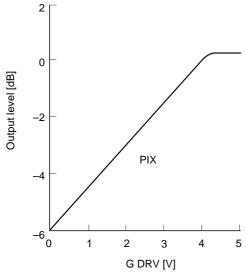

The contrast for RGB IN (Pins 2, 5 and 8) input signals is adjusted using a DC externally input to the PIX pin (Pin 12). In addition, the contrast for each RGB channel can be adjusted independently using a DC externally input to the DRV pins (Pins 3, 6 and 9). (See Graphs 1 and 2.)

#### 2. Pedestal clamp and brightness control

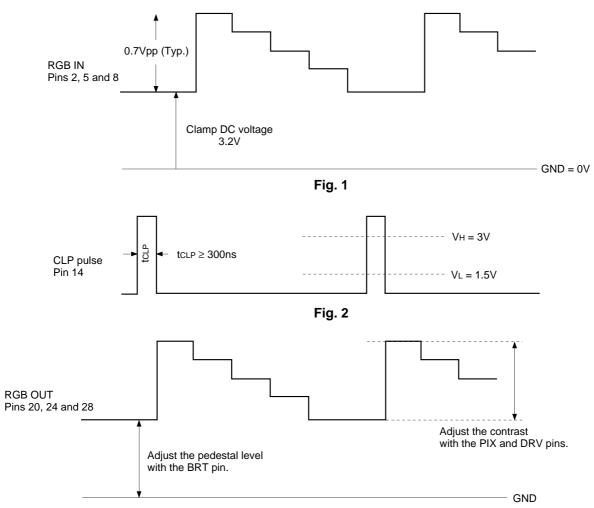

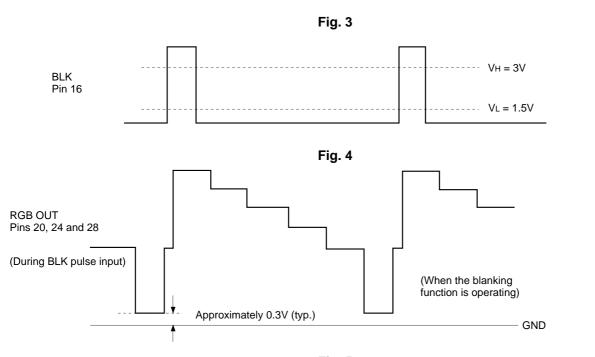

The pedestal clamp clamps the pedestal level when the CLP pin (Pin 14) is high. The RGB IN pin voltage at the pedestal is approximately 3.2V when the pedestal is clamped. The CLP pin threshold level is 3V for VH and 1.5V for VL. (See Fig. 2.)

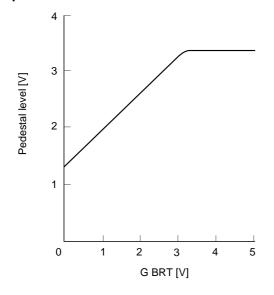

Using a DC externally input to the R, G and B BRT pins (Pins 26, 22 and 18), the brightness control samples and holds the pedestal with the capacitance connected to the RGB SH pins (Pins 27, 23 and 19) when the CLP pin (Pin 14) is high, thereby adjusting the pedestal level of the R, G and B channels. (See Graph 3.)

#### 3. Blanking additional function

Output is blanked when the BLK pin (Pin 16) is high. The BLK pin threshold level is 3V for V<sub>H</sub> and 1.5V for V<sub>L</sub>. See the Example of Input/Output Signals for output signal levels. The output signal is 0.3V during the blanking interval. (See Figs. 4 and 5.)

## **Example of Input/Output Signals**

When a sync signal is added to the RGB input signal, after the signal is sliced into approximately 60mVp-p inside the IC, it is amplified by the gain from the PIX and DRV pins and output.

Fig. 5

## **Example of Representative Characteristics**

Graph 1. Contrast control (RGB common) characteristics

Input conditions for each control pin

| Р  | in name | Pin vo | Pin voltage |  |  |

|----|---------|--------|-------------|--|--|

| 12 | PIX     | 0 to 5 | [V]         |  |  |

| 3  | R DRV   | 4      | [V]         |  |  |

| 6  | G DRV   | 4      | [V]         |  |  |

| 9  | B DRV   | 4      | [V]         |  |  |

| 26 | R BRT   | 2.5    | [V]         |  |  |

| 22 | G BRT   | 2.5    | [V]         |  |  |

| 18 | B BRT   | 2.5    | [V]         |  |  |

| 5  | G IN    | 0.65 [ | Vpp]        |  |  |

Graph 2. DRV control (RGB independent) characteristics (Gch)

Input conditions for each control pin

| Р  | in name | Pin vol | in voltage |  |  |

|----|---------|---------|------------|--|--|

| 12 | PIX     | 4       | [V]        |  |  |

| 3  | R DRV   | 4       | [V]        |  |  |

| 6  | G DRV   | 0 to 5  | [V]        |  |  |

| 9  | B DRV   | 4       | [V]        |  |  |

| 26 | R BRT   | 2.5     | [V]        |  |  |

| 22 | G BRT   | 2.5     | [V]        |  |  |

| 18 | B BRT   | 2.5     | [V]        |  |  |

| 5  | G IN    | 0.65 [  | Vpp]       |  |  |

**Graph 3. BRT control characteristics**

Input conditions for each control pin

| Р  | in name | Pin vol | tage |

|----|---------|---------|------|

| 12 | PIX     | 2.5     | [V]  |

| 3  | R DRV   | 2.5     | [V]  |

| 6  | G DRV   | 2.5     | [V]  |

| 9  | B DRV   | 2.5     | [V]  |

| 26 | R BRT   | 2.5     | [V]  |

| 22 | G BRT   | 0 to 5  | [V]  |

| 18 | B BRT   | 2.5     | [V]  |

| 5  | GIN     | 0.65 [  | Vpp] |

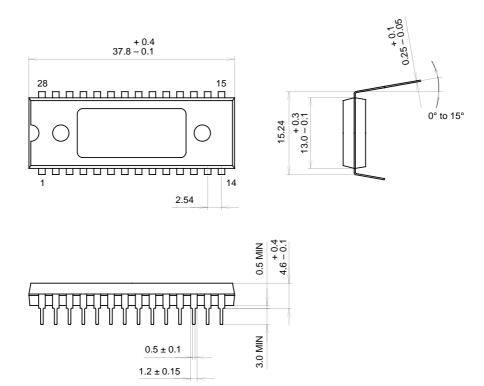

## Package Outline Unit: mm

## 28PIN DIP (PLASTIC) 600mil

#### PACKAGE STRUCTURE

| SONY CODE  | DIP-28P-03       |

|------------|------------------|

| EIAJ CODE  | *DIP028-P-0600-C |

| JEDEC CODE |                  |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | COPPER         |

| PACKAGE WEIGHT   | 4.2g           |