## Read/Write Amplifier (with Built-in Filters) for FDDs

## **Description**

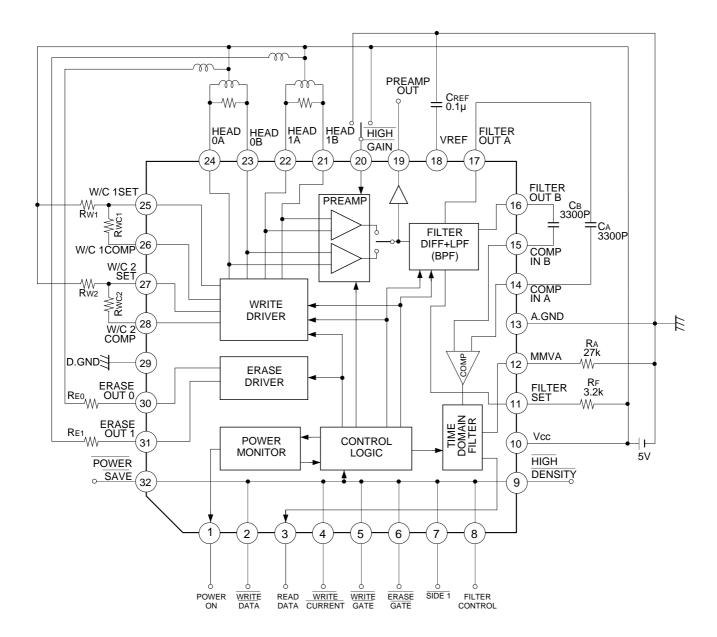

The CXA1720Q is an IC for use with floppy disk drives, and contains a Read circuit (with built-in filters), Write circuit, Erase circuit, and supply voltage detection circuit, all into a single chip.

#### **Features**

- Single 5 V power supply.

- Filter system can be switched among four modes: 1M/2M, and inner track/outer track. This allows for a significant reduction in the number of external parts such as differentiator constants, low-pass filters, and switches. (Compared with conventional Sony products, the number of parts has been reduced by one-half.)

- Filter characteristics can be customized.

- Low pre-amplifier input conversion noise voltage of 2.0 nV/ √Hz (typ.) keeps Read data output jitter to a minimum. The pre-amplifier voltage gain can be selected as either 100× or 200×.

- The monostable multivibrator No. 1 pulse width switching function for the time domain filter permits switching between 1M and 2M mode.

- Write current switching function permits switching of the Write current among four modes: 1M/2M and inner track/outer track. (Filter inner track/outer track switching is separate.)

- Supply voltage detection circuit prohibits error writing during power ON/OFF or abnormal voltage.

- Power consumption is kept down to 115 mW (typ.) and this IC is suitable for use with battery-driven FDDs.

- Built in Time constant capacitors for monostable multivibrator Nos. 1 and 2. (The pulse width for monostable multivibrator No. 2 is fixed.)

- Power saving function reduces power consumption when the IC is not in use. When in power saving mode (5 mW typ.), only the power supply ON/OFF detector functions.

- The Write driver has a built-in reset circuit. When the mode is switched from Read mode to Write mode, the Write current flows from head 0A if head side 0 is selected and from head 1A if head side 1 is selected.

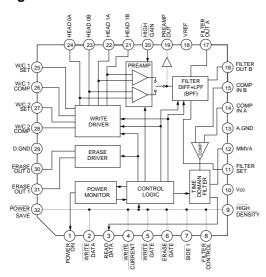

#### **Block Diagram and Pin Configuration**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

## Structure

Bipolar silicon monolithic IC

## **Absolute Maximum Ratings** (Ta = 25°C)

| Supply voltage                                      | Vcc  | 7               | V  |

|-----------------------------------------------------|------|-----------------|----|

| Digital signal input pin (note) input voltage       |      | -0.5 to Vcc+0.3 | V  |

| <ul> <li>Power ON output applied voltage</li> </ul> |      | Vcc+0.3         | V  |

| Erase output applied voltage                        |      | Vcc+0.3         | V  |

| • Head 0A, 0B, 1A, 1B applied voltage               |      | 15              | V  |

| <ul> <li>Power ON output sink current</li> </ul>    |      | 7               | mΑ |

| Erase output sink current                           |      | 30              | mΑ |

| Operating temperature                               | Topr | -20 to +75      | °C |

| Storage temperature                                 | Tstg | -65 to +150     | °C |

| <ul> <li>Allowable power dissipation</li> </ul>     | PD   | 500             | mW |

|                                                     |      |                 |    |

| Supply Voltage Range                                |      |                 |    |

|                                                     | Vcc  | 4.4 to 6.0      | V  |

Note) WRITE DATA, WRITE CURRENT, WRITE GATE, ERASE GATE

SIDE1, FILTER CONTROL, HIGH DENSITY, HIGH GAIN, POWER SAVE

## **Pin Description**

$(Ta = 25^{\circ}C, VCC = 5 V)$

| Pin D      | escription        |             |                           | $(1a = 25^{\circ}C, VCC = 5 V)$                                                                                                                                                                           |

|------------|-------------------|-------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Symbol            | Pin voltage | Equivalent circuit        | Description                                                                                                                                                                                               |

| 1          | POWER ON          | _           | Vcc<br>100k<br>1<br>A.GND | Reduced voltage detection output. This is an open collector that outputs a low signal when Vcc is below the specified value.                                                                              |

| 2          | WRITE<br>DATA     | _           | Vcc Vcc Vcc Vcc Vcc A.GND | Write data input. This pin is a Schmitt-type input and is triggered when the logical voltage goes from high to low.                                                                                       |

| 3          | READ<br>DATA      | _           | 3<br>D.GND                | Read data output. This pin is active when the logical voltage of the Write gate signal and the Erase gate signal is high.                                                                                 |

| 4          | WRITE             | _           |                           | Write current control. The Write current is                                                                                                                                                               |

| 5          | CURRENT<br>WRITE  | _           |                           | increased when the logical voltage is low.  Write gate signal input. The Write system is                                                                                                                  |

| 6          | GATE<br>ERASE     | _           |                           | active when the logical voltage is low.  Erase gate signal input. The Erase system                                                                                                                        |

| 7          | GATE<br>SIDE1     |             |                           | is active when the logical voltage is low.  Head side switching signal input. The                                                                                                                         |

|            | SIDET             | _           | Vcc                       | HEAD1 system is active when the logical voltage is low, and the HEAD0 system is active when the logical voltage is high, but only when the logical voltage for the Write gate and the Erase gate is high. |

| 8          | FILTER<br>CONTROL | _           | 20 6 2.1V A.GND           | Filter inner track/outer track mode control. Inner track mode is selected when the logical voltage is low.                                                                                                |

| 9          | HIGH<br>DENSITY   | _           |                           | Filter, time domain filter and Write current 1M/2M mode control. 2M mode is selected when the logical voltage is low.                                                                                     |

| 20         | HIGH<br>GAIN      | _           |                           | Pre-amplifier voltage gain selection. Gain of 100x is selected when the logical voltage is high; gain of 200x is selected when the logical voltage is low.                                                |

| Pin<br>No. | Symbol               | Pin voltage | Equivalent circuit          | Description                                                                                                                                                                                               |

|------------|----------------------|-------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10         | Vcc<br>FILTER<br>SET | 3.8 V       | 1.2V                        | Power supply (5 V) connection.  Connection for filter cut-off frequency setting resistor. Connect the filter cut-off frequency setting resistor RF between this pin and Vcc to set the cut-off frequency. |

| 12         | MMVA                 | 0.5 V       | 147<br>W 12<br>A.GND        | Time domain filter monostable multivibrator No. 1 pulse width setting pin. Connect the monostable multivibrator No. 1 pulse width setting resistor RA between this pin and A.GND.                         |

| 13         | A. GND               | _           |                             | Analog system GND connection.                                                                                                                                                                             |

| 14         | COMP IN A            | 3.3 V       | 10k 10k Vcc 16k 16k 147 147 | Comparator differential inputs.                                                                                                                                                                           |

| 15         | COMP IN B            | 3.3 V       | 15 147 A.GND                |                                                                                                                                                                                                           |

| 16         | FILTER<br>OUT B      | 3.3 V       | Vcc<br>140 ≥ ≥140           | Filter differential outputs.                                                                                                                                                                              |

| 17         | FILTER<br>OUT A      | 3.3 V       | 500µ A.GND                  |                                                                                                                                                                                                           |

| Pin<br>No. | Symbol        | Pin voltage | Equivalent circuit              | Description                                                                                                                                                                                                                                                           |

|------------|---------------|-------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18         | VREF          | 2.8 V       | 500<br>W 18                     | Connection for internal reference voltage decoupling capacitor. Connect the decoupling capacitor CREF between this pin and A.GND.                                                                                                                                     |

| 19         | PREAMP<br>OUT | 2.8 V       | Vcc<br>₹140<br>19<br>320µ A.GND | Pre-amplifier output.                                                                                                                                                                                                                                                 |

| 21         | HEAD 1B       | _           | 24 23 22 21                     | Connection for magnetic head input/output.  Connect the recording/playback magnetic                                                                                                                                                                                   |

| 22         | HEAD 1A       | _           |                                 | head to these pins, and connect the center tap to Vcc. When the logical voltage for Pin                                                                                                                                                                               |

| 23         | HEAD 0B       | <u> </u>    |                                 | 7 (SIDE1) is low, the HEAD1 system is active; when the logical voltage is high, the                                                                                                                                                                                   |

| 24         | HEAD 0A       | _           | A.GND                           | HEAD0 system is active.                                                                                                                                                                                                                                               |

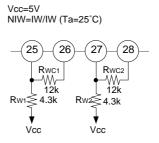

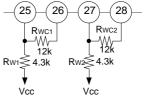

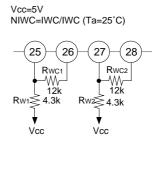

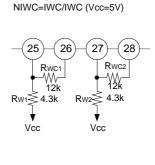

| 25         | W/C1SET       |             | 1.2V Vcc                        | Connection for 1M write current setting resistor. Connect the Write current setting resistor Rw1 between this pin and Vcc to set the Write current.                                                                                                                   |

| 27         | W/C2SET       |             | A.GND                           | Connection for 2M Write current setting resistor. Connect the Write current setting resistor Rw2 between this pin and Vcc to set the Write current.                                                                                                                   |

| 26         | W/C1<br>COMP  | _           | Vcc                             | Connection for 1M Write current compensation resistor. Connect the Write current compensation resistor Rwc1 between this pin and Pin 25                                                                                                                               |

| 28         | W/C2<br>COMP  | _           | 26<br>28<br>A.GND               | (W/C1SET) to set the amount of increase in the Write current.  Connection for 2M Write current compensation resistor.  Connect the Write current compensation resistor Rwc2 between this pin and Pin 27 (W/C2SET) to set the amount of increase in the Write current. |

| Pin<br>No. | Symbol        | Pin voltage | Equivalent circuit    | Description                                                                                                                                                                  |

|------------|---------------|-------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29         | D. GND        | _           |                       | Digital system GND connection.                                                                                                                                               |

| 30         | ERASE<br>OUT0 | _           | Vcc                   | Erase current output for the HEAD0 system.                                                                                                                                   |

| 31         | ERASE<br>OUT1 | _           | 30<br>31<br>D.GND     | Erase current output for the HEAD1 system.                                                                                                                                   |

| 32         | POWER<br>SAVE |             | 32 Vcc Vcc 2.1V A.GND | Power saving signal input.  When the logical voltage is low, the IC is in power saving mode. In power saving mode, only the power supply ON/OFF detection function operates. |

## **Electrical Characteristics**

## **Current Consumption**

(Ta = 25°C, Vcc = 5 V)

| ltem                                    | Symbol | Conditions               | Measure-<br>ment<br>circuit | Measure-<br>ment<br>point | Min. | Тур. | Max. | Unit |

|-----------------------------------------|--------|--------------------------|-----------------------------|---------------------------|------|------|------|------|

| Current consumption for Read            | ICCR   | Vcc=5V<br>WG="H"         | _                           |                           | 13.0 | 23.0 | 33.0 |      |

| Current consumption for Write/Erase     | ICCWE  | Vcc=5V<br>WG="L", EG="L" | _                           |                           | 8.0  | 14.0 | 20.0 | mA   |

| Current consumption for<br>Power saving | ICCPS  | Vcc=5V<br>PS="L"         | _                           | _                         |      | 0.9  | 1.8  |      |

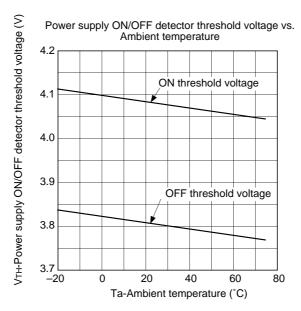

## Power Supply Monitoring System

$(Ta = 25^{\circ}C)$

| Item                                           | Symbol | Conditions        | Measure-<br>ment<br>circuit | Measure-<br>ment<br>point | Min. | Тур. | Max. | Unit |

|------------------------------------------------|--------|-------------------|-----------------------------|---------------------------|------|------|------|------|

| Power supply ON/OFF detector threshold voltage | VTH    |                   | _                           | _                         | 3.5  | 3.9  | 4.3  | V    |

| Power ON output saturation voltage             | VSP    | Vcc=3.5V<br>I=1mA | _                           | _                         |      |      | 0.5  | V    |

## Read System

| Item                                               | Symbol | Conditions                                            | Measure-<br>ment<br>circuit | Measure-<br>ment<br>point | Min.          | Тур.  | Max.          | Unit  |

|----------------------------------------------------|--------|-------------------------------------------------------|-----------------------------|---------------------------|---------------|-------|---------------|-------|

| Pre-amplifier voltage gain SIDE0*                  | GV0    | f=100kHz<br>SW4=a, b                                  |                             |                           |               |       |               |       |

| Pre-amplifier voltage gain SIDE1*                  | GV1    | f=100kHz<br>SW4=a, b<br>SW1, 5=b                      | 1                           | G                         | 38.1/<br>44.1 | 40/46 | 41.6/<br>47.6 | dB    |

| Pre-amplifier frequency response SIDE0*            | BW0    | Av/Avo=-3dB<br>SW4=a, b                               |                             |                           |               |       |               |       |

| Pre-amplifier frequency response SIDE1*            | BW1    | Av/Av1=-3dB<br>SW4=a, b<br>SW1, 5=b                   | 1                           | G                         | 5             |       |               | MHz   |

| Pre-amplifier input conversion noise voltage SIDE0 | EN0    | Bandwidth=400Hz<br>to 1MHz Vi=0,<br>SW4=b             |                             |                           |               |       |               |       |

| Pre-amplifier input conversion noise voltage SIDE1 | EN1    | Bandwidth=400Hz<br>to 1MHz<br>SW4=b<br>Vi=0, SW1, 5=b | 1                           | G                         |               | 2.0   | 2.9           | μVrms |

<sup>\*</sup> When SW4 = a: Vi = 10 mVp-p When SW4 = b: Vi = 5 mVp-p

(vs. VREF)

amplitude\*\*

amplitude

precision

(fixed)

## Read System

Symbol

VOFSP

VOP

VOF

ETM1

ETM1'

T2

VOL

VOH

TR

TF

PS

VOFSF | Vi=0

Conditions

Vi=0

SW4=a, b,

SW4=a, b,

f=100kHz

$Ra=27k\Omega$

$Ra=27k\Omega$

IoL=2mA

$RL=2k\Omega$

CL=20pF  $RL=2k\Omega$

CL=20pF

f=62.5kHz Refer to Fig. 1

Vi=0.25mVp-p to 10mVp-p

IOH=-0.4mA

Vi=60mVp-p

Refer to Fig. 1

Refer to Fig. 1

SW1, 5=a, b

SW1, 5=a, b f=100kHz

Item

Pre-amplifier output offset voltage

Pre-amplifier output voltage

Filter differential output offset

Filter differential output voltage

Time domain filter monostable

multivibrator No. 1 pulse width

Time domain filter monostable

multivibrator No. 2 pulse width

Read data output low voltage

Read data output high voltage

Read data output\*\*\* rise time

Read data output\*\*\* fall time

Peak shift\*\*\*\*

| $(Ta = 25^{\circ}C, Vcc = 5 V)$ |      |      |      |  |  |  |  |

|---------------------------------|------|------|------|--|--|--|--|

| Min.                            | Тур. | Max. | Unit |  |  |  |  |

| -500                            |      | +500 | mV   |  |  |  |  |

| 1.8                             |      |      | Vp-p |  |  |  |  |

| -100                            |      | +100 | mV   |  |  |  |  |

| 2.8                             |      |      | Vp-p |  |  |  |  |

| -10                             |      | +10  | %    |  |  |  |  |

| 260                             | 400  | 540  | ns   |  |  |  |  |

|                                 |      |      |      |  |  |  |  |

0.5

100

100

1

ns

%

Measure- Measure-

ment

point

F, G

G

D, E

D, E

B, C

Α

Α

Α

Α

Α

Α

Α

2.8

ment

circuit

1

1

1

1

1

1

1

1

1

1

| ** | When SW4 = a: Vi = 60 mVp-p |

|----|-----------------------------|

|    | When SW4 = b: Vi = 30 mVp-p |

<sup>\*\*\*</sup> Read data output between 0.5 V to 2.4 V

<sup>\*\*\*\*</sup> For Vi = 0.25 mVp-p to 5m Vp-p: SW4 = b (pre-amplifier voltage gain: 46 dB)

For Vi = 0.5 mVp-p to 10 mVp-p: SW4 = a (pre-amplifier voltage gain: 40 dB)

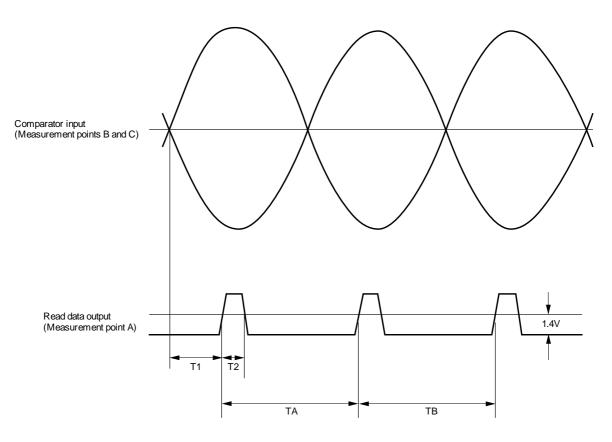

Fig. 1 Monostable multivibrator Nos. 1 and 2 pulse width precision and peak shift measurement conditions

Monostable multivibrator No. 1 pulse width precision When HD = high:

ETM1 =

$$\left(\frac{T_1}{2.45\mu S} - 1\right) \times 100 (\%)$$

When HD is low:

ETM1' =

$$\left(\frac{T_1}{1.25\mu S} - 1\right) \times 100 \text{ (%)}$$

- Monostable multivibrator No. 2 pulse width = T2

- Peak shift

$$PS = \frac{1}{2} \left| \frac{TA - TB}{TA + TB} \right| \times 100 \text{ (\%)}$$

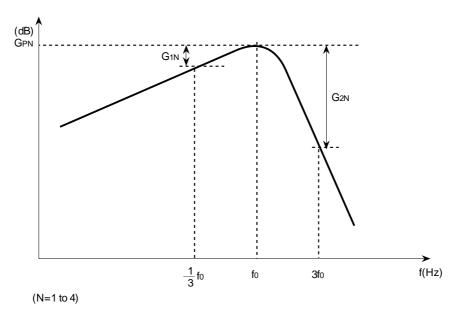

## Read System (Filters)

(Ta = 25°C, Vcc = 5 V)

|                 | -,                     |                 |                                       |                             |                           |       |       | -,    |      |

|-----------------|------------------------|-----------------|---------------------------------------|-----------------------------|---------------------------|-------|-------|-------|------|

|                 | Item                   | Symbol          | Conditions                            | Measure-<br>ment<br>circuit | Measure-<br>ment<br>point | Min.  | Тур.  | Max.  | Unit |

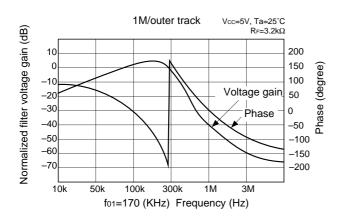

|                 | Peak frequency         | Fo1             | Vi=3mVp-p HG="L"<br>HD="H" FC="H"     | 1                           | D, E                      | 153.0 | 170.0 | 187.0 | kHz  |

| 1M/             | Peak voltage gain***** | GP1             | Refer to Fig. 2<br>at fo1             | 1                           | G<br>D, E                 | 3.6   | 5.5   | 7.1   |      |

| outer<br>track  | Frequency response (1) | G11             | Refer to Fig. 2 at $\frac{1}{3}$ for  | 1                           | D, E                      | -7.6  | -7.1  | -6.6  | dB   |

|                 | Frequency response (2) | G12             | Refer to Fig. 2<br>at 3fo1            | 1                           | D, E                      | -25.0 | -23.1 | -21.5 |      |

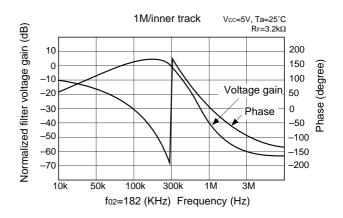

|                 | Peak frequency         | fo2             | Vi=3mVp-p<br>HG=":L"<br>HD="H" FC="L" | 1                           | D, E                      | 163.8 | 182.0 | 200.2 | kHz  |

| 1M/             | Peak voltage gain****  | GP2             | Refer to Fig. 2<br>at fo2             | 1                           | G<br>D, E                 | 3.6   | 5.5   | 7.1   |      |

| inner-<br>track | Frequency response (1) | G21             | Refer to Fig. 2 at $\frac{1}{3}$ fo2  | 1                           | D, E                      | -7.6  | -7.1  | -6.6  | dB   |

|                 | Frequency response (2) | G22             | Refer to Fig. 2<br>at 3fo2            | 1                           | D, E                      | -25.0 | -23.1 | -21.5 |      |

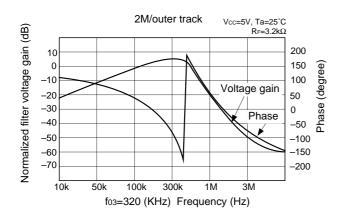

|                 | Peak frequency         | fоз             | Vi=3mVp-p HG="L"<br>HD="L" FC="H"     | 1                           | D, E                      | 288.0 | 320.0 | 352.0 | kHz  |

| 2M/             | Peak voltage gain***** | G <sub>P3</sub> | Refer to Fig. 2 at fo3                | 1                           | G<br>D, E                 | 3.6   | 5.5   | 7.1   |      |

| outer<br>track  | Frequency response (1) | <b>G</b> 31     | Refer to Fig. 2 at $\frac{1}{3}$ fo3  | 1                           | D, E                      | -7.6  | -7.1  | -6.6  | dB   |

|                 | Frequency response (2) | G32             | Refer to Fig. 2<br>at 3fo3            | 1                           | D, E                      | -25.0 | -23.1 | -21.5 |      |

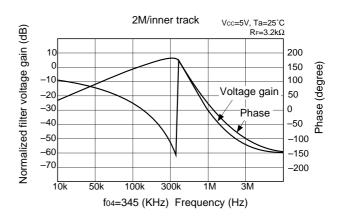

|                 | Peak frequency         | fO4             | Vi=3mVp-p HG="L"<br>HD="L" FC="L"     | 1                           | D, E                      | 310.5 | 345.0 | 379.5 | kHz  |

| 2M              | Peak voltage gain****  | GP4             | Refer to Fig. 2<br>at fo4             | 1                           | G<br>D, E                 | 5.3   | 7.2   | 8.8   |      |

| inner<br>track  | Frequency response (1) | G41             | Refer to Fig. 2 at $\frac{1}{3}$ fo4  | 1                           | D, E                      | -8.6  | -8.1  | -7.6  | dB   |

|                 | Frequency response (2) | G42             | Refer to Fig. 2<br>at 3fo4            | 1                           | D, E                      | -36.2 | -34.3 | -32.7 |      |

\*\*\*\*\* GPN = 20Log10 (VFilterout/VPreout)

VFilterout: Filter differential output voltage

(N = 1 to 4)

Fig. 2 Filter frequency response measurement conditions

## Write/Erase System

$(Ta = 25^{\circ}C, VCC = 5 V)$

| Item                                               | Symbol | Conditions                                             | Measure-<br>ment<br>circuit | Measure-<br>ment<br>point | Min. | Тур. | Max. | Unit |

|----------------------------------------------------|--------|--------------------------------------------------------|-----------------------------|---------------------------|------|------|------|------|

| Write current output precision*                    | EW     | $\overline{\text{WG}}$ ="L" Rw=4.3k $\Omega$           | 2                           | LKJI                      | -7   |      | +7   |      |

| Write current output unbalance                     | DW     | $\overline{\text{WG}}$ ="L" Rw=4.3k $\Omega$           | 2                           | LKJI                      | -1   |      | +1   | %    |

| Write current compensation current precision**     | EWC    | $\overline{WG}$ ="L" Rw=4.3k $\Omega$ Rwc=12k $\Omega$ | 2                           | LKJI                      | -10  |      | +10  |      |

| Head I/O pin leak current for Write                | ILKW   | WG="L"                                                 | 2                           | LKJI                      |      |      | 10   | μΑ   |

| Head I/O pin saturation voltage for Write          | VSW    | WG="L"<br>SW1=6                                        | 2                           | L'K'J'I'                  |      |      | 1    | V    |

| Leak current for Erase current switch              | ILKE   | EG="L"                                                 | 2                           | MN                        |      |      | 10   | μA   |

| Output saturation voltage for Erase current switch | VSE    | EG="L"<br>I=30mA<br>SW2=b                              | 2                           | M'N'                      |      |      | 500  | mV   |

\* Write current output precision

Ew =

$$\left(\frac{IW}{2.70\text{mA}} - 1\right) \times 100 \text{ (%)}$$

\*\*Write current compensation current precision  $EWC = \left(\frac{IW'-IW}{0.90mA} - 1\right) \times 100 (\%)$

IW: WRITE CURRENT = "H" IW': WRITE CURRENT = "L"

Logic Input Block

| Item                                    | Symbol | Conditions | Measure-<br>ment<br>circuit | Measure-<br>ment<br>point | Min. | Тур. | Max. | Unit |

|-----------------------------------------|--------|------------|-----------------------------|---------------------------|------|------|------|------|

| Digital low input voltage               | VLD    |            | 2                           | BCDE<br>FGHP              |      |      | 0.8  |      |

| Digital high input voltage              | VHD    |            | 2                           | BCDE<br>FGHP              | 2.0  |      |      | .,   |

| Schmitt-type digital low input voltage  | VLSD   |            | 2                           | А                         |      |      | 0.8  | V    |

| Schmitt-type digital high input voltage | VHSD   |            | 2                           | А                         | 2.0  |      |      |      |

| Digital low input current               | ILD    | VL=0V      | 2                           | ABCD<br>EFGHP             | -20  |      |      |      |

| Digital high input current              | IHD    | VH=5V      | 2                           | ABCD<br>EFGHP             |      |      | 10   | μA   |

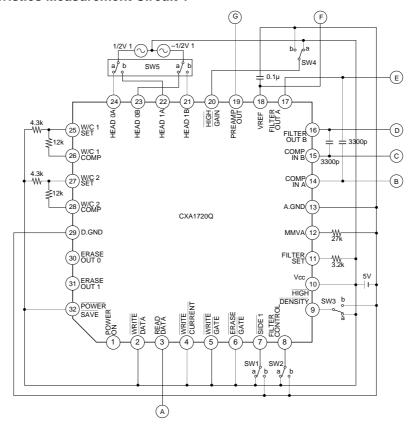

#### **Electrical Characteristics Measurement Circuit 1**

Note) Unless otherwise specified, switches are assumed to be set to "a".

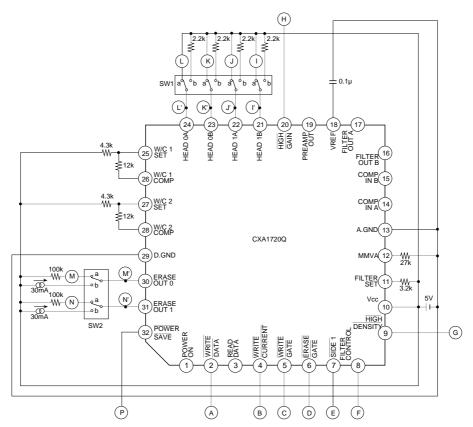

## **Electrical Characteristics Measurement Circuit 2**

Note) Unless otherwise specified, switches are assumed to be set to "a".

SONY CXA1720Q

## **Description of Operation**

## (1) Read system

## Pre-amplifier

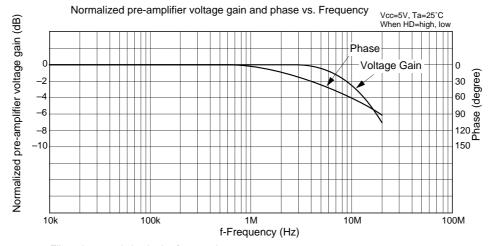

The pre-amplifier amplifies input signals. The voltage gain can be switched between 40 dB and 46 dB, using Pin 20.

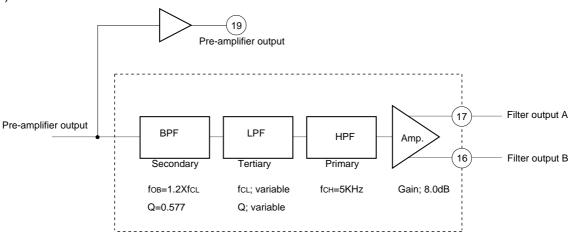

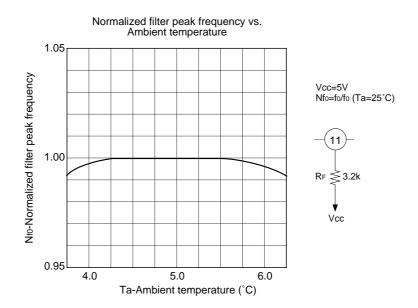

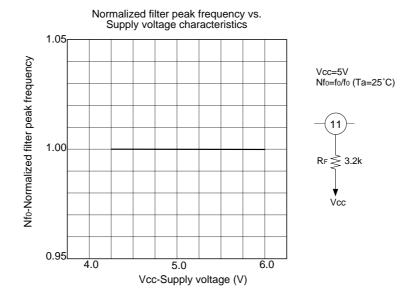

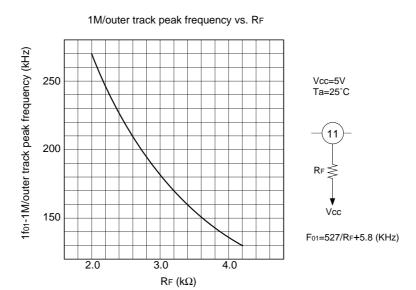

#### **Filters**

The filters differentiate the signals amplified by the pre-amplifier. The high-band noise components are attenuated by the low-pass filter. The filters can be switched among four modes, depending on the settings of Pins 8 and 9. In 1M/outer track mode, the peak frequency fo1 is set by external resistor RF. fo for the other three modes is switched by the internal settings of the IC, with fo1 used as a reference (1.00).

The filters are explained below.

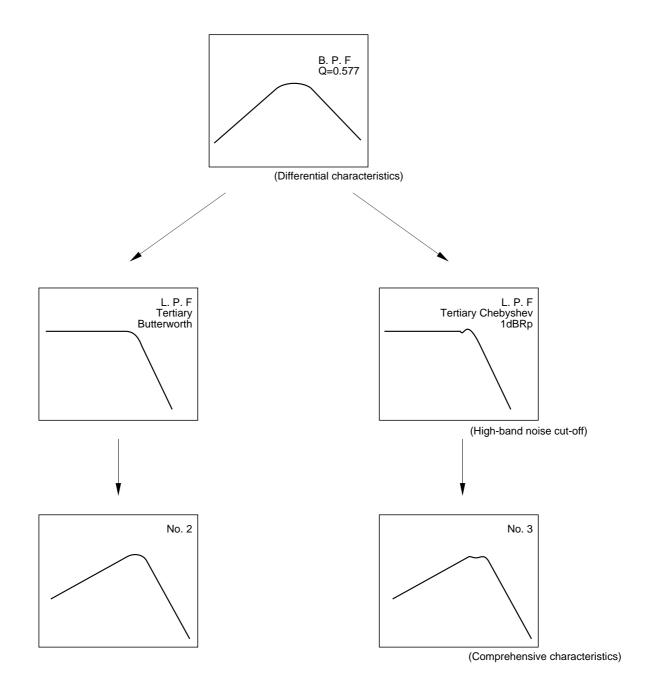

## 1) Active filter block

Filter Characteristics

Table 1

| Pin 8 | Pin 9 | LPF characteristics                        | fo ratio |

|-------|-------|--------------------------------------------|----------|

| Н     | Н     | 1M/outer track mode: Butterworth           | 1.00     |

| L     | Н     | 1M/inner track mode: Butterworth           | 1.07     |

| н     | L     | 2M/outer track mode: Butterworth           | 1.88     |

| L     | L     | 2M/inner track mode: Chebyshev 1 dB ripple | 2.03     |

The formula for the peak frequency for 1M/outer track mode is shown below:

fo1 = 527/RF + 5.8 (kHz) fo1: peak frequency in 1M/outer track mode

RF: filter setting resistance ( $k\Omega$ )

The relationship between f01 and f0 in the four modes is as follows:

1M/outer track:  $f01 = 1.0 \times f01$ 1M/inner track:  $f02 = 1.07 \times f01$ 2M/outer track:  $f03 = 1.88 \times f01$ 2M/inner track:  $f04 = 2.03 \times f01$

Note that these filters can be customized.

Customization is explained on pages 17 and 18.

#### Comparator

The comparator detects the crosspoint of the filter differential output.

#### Time domain filter

The time domain filter converts the comparator output to Read data.

This filter is equipped with two monostable multivibrators. Monostable multivibrator No. 1 eliminates unnecessary pulses, and monostable multivibrator No. 2 determines the pulse width of Read data.

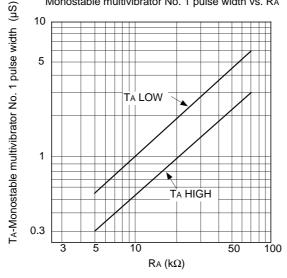

The monostable multivibrator No. 1 pulse width TA is determined by the resistor RA between Pin 12 and A.GND. TA can be switched as follows by the setting of Pin 9:

```

\overline{\text{HIGH DENSITY}} = "H" TA LOW = 84RA + 180 (nS) RA (kΩ)

\overline{\text{HIGH DENSITY}} = "L" TA HIGH = 42RA + 110 (nS)

```

The pulse width for monostable multivibrator No. 2 is fixed at 400 ns.

#### (2) Write System

Write data input through Pin 2 is frequency-divided by the T flip-flop and generates the head recording current. The recording current can be switched by the setting of Pin 9.

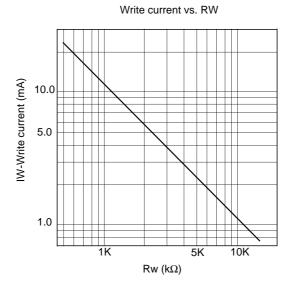

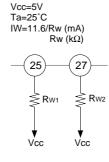

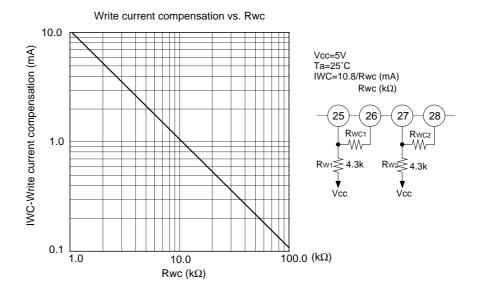

The Write current Iw is set by the resistor Rw connected between Pin 25 and Vcc and between Pin 27 and Vcc.

```

IW = 11.6/RW (mA) RW (k\Omega)

```

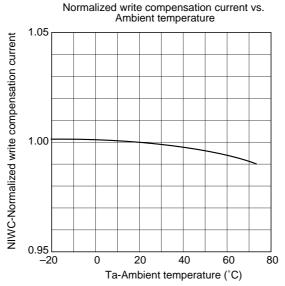

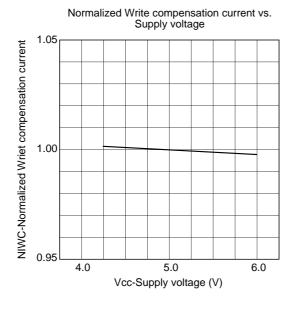

Furthermore, the Write current compensation lwc is set by the resistor Rwc connected between Pin 25 and Pin 26, and between Pin 27 and Pin 28.

Iwc =

$$10.8$$

/Rwc (mA) Rwc (k $\Omega$ )

#### (3) Erase System

Pins 30 and 31 are open collector outputs; the Erase current is set by the resistance between these pins and the Erase head.

## (4) Power ON/OFF Detection System

The power ON/OFF detection system detects a reduced voltage.

When Vcc is below the stipulated voltage, the Write system and Erase system cease operation, disabling the Write and Erase functions

## Notes on Operation

- Select the voltage gain so that the pre-amplifier output amplitude is 1 Vp-p or less.

If the pre-amplifier output amplitude exceeds 1 Vp-p, the filter output waveform becomes distorted.

- Observe the following points when mounting this IC.

- Connect a VCC decoupling capacitor of approximately 0.1µF close to the IC.

- The ground should be as large as possible.

## Application Circuit (for 1M/2M devices)

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

## Customization

Filter frequency response

In 2M/inner track mode, the filter frequency response can be changed as shown below.

#### **Filter Customization Selections/Combinations**

In filter settings, use the LPF cut-off frequency fc1 in 1M/outer track mode as 1.00 as shown in Table 1 to select fc ratios and LPF types for the other three modes. The 1M/outer track to 2M/outer track modes for the LPF are fixed to Butterworth, while either Butterworth or Chebyshev 1 dB ripple can be selected in 2M/inner track mode.

Note that the BPF center frequency foB is fixed at 1.2 times the LPF cut-off frequency fc. In addition, the relationship between the peak frequencies fo and fc in regards to the comprehensive characteristics is as follows, depending on differences in LPFs.

Butterworth characteristics: fC = 1.28fo Chebyshev 1 dB ripple characteristics: fC = 1.12fo

Table 1 LPF fc Ratios and Types

| Mode           | LPF type                            |                      | fc ratio w           | hen fc1 is as:       | sumed as 1.0 | 00           |

|----------------|-------------------------------------|----------------------|----------------------|----------------------|--------------|--------------|

| 1M/outer track | Butterworth                         | 1.00                 |                      |                      |              |              |

| 1M/inner track | Butterworth                         | 1.07<br>1.60         | 1.14<br>2.00         | 1.23                 | 1.33         | 1.45         |

| 2M/outer track | Butterworth                         | 1.33<br>1.68<br>2.29 | 1.39<br>1.78<br>2.46 | 1.45<br>1.88<br>2.67 | 1.52<br>2.00 | 1.60<br>2.13 |

| 2M/inner track | Butterworth Chebyshev (1 dB ripple) | 1.33<br>1.68<br>2.29 | 1.39<br>1.78<br>2.46 | 1.45<br>1.88<br>2.67 | 1.52<br>2.00 | 1.60<br>2.13 |

Note) The boxed item indicates the setting for the CXA1720Q.

Filter characteristics in the four modes (These characteristics are based on pre-amplifier output. 0dB=pre-amplifier output level)

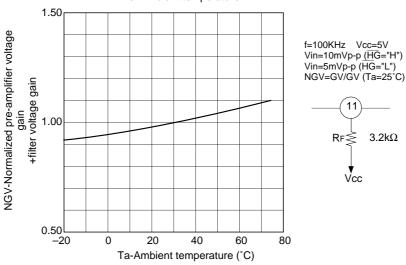

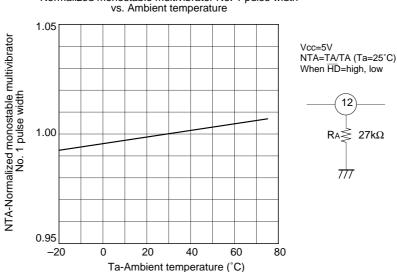

# Normalized pre-amplifier voltage gain+filter voltage gain vs. Ambient temperature

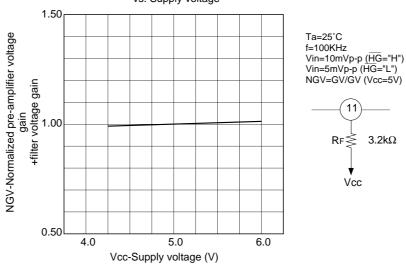

# Normalized pre-amplifier voltage gain+filter voltage gain vs. Supply voltage

## Normalized monostable multivibrator No. 1 pulse width

Normalized monostable multivibrator No. 1 pulse width vs. Supply voltage

NTA-Normalized monostable multivibrator

NO. 1 bnlse width

No. 1 bnlse width

No. 1 bnlse width

No. 1 bnlse width

Vcc-Supply voltage (V)

Ta=25°C NTA=TA/TA (Ta=25°C) When HD=high, low

Monostable multivibrator No. 1 pulse width vs. RA

TA LOW=84RA+180 (ns) TA HIGH=42RA+110 (ns) RA  $(k\Omega)$

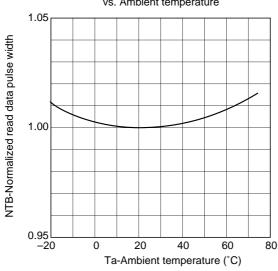

# Normalized read data pulse width vs. Ambient temperature

Vcc=5V NTB=TB/TB (Ta=25°C)

Normalized read data pulse width vs. Supply voltage

1.05

1.00

1.00

0.95

4.0

Vcc-Supply voltage (V)

Ta=25°C NTB=TB/TB (Vcc=5V)

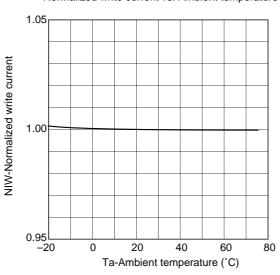

Normalized write current vs. Ambient temperature

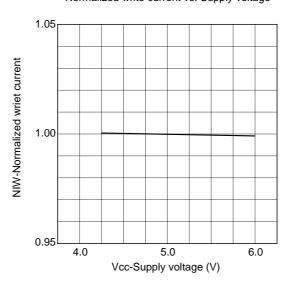

Normalized write current vs. Supply voltage

Ta=25°C NIW=IW/IW (Vcc=5V)

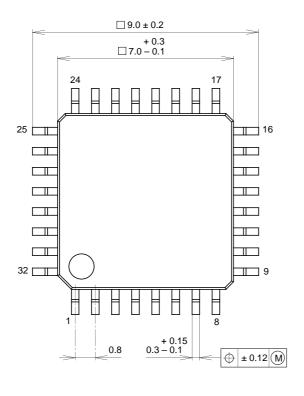

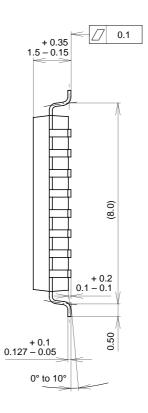

## Package Outline Unit: mm

## 32PIN QFP (PLASTIC)

| SONY CODE  | QFP-32P-L01      |  |  |  |

|------------|------------------|--|--|--|

| EIAJ CODE  | *QFP032-P-0707-A |  |  |  |

| JEDEC CODE |                  |  |  |  |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | 42 ALLOY       |

| PACKAGE WEIGHT   | 0.2g           |