# Pre-driver for Ultra-High Resolution Computer Display

### Description

The CXA1709P is a bipolar IC designed for use in ultra-high resolution computer displays.

#### **Features**

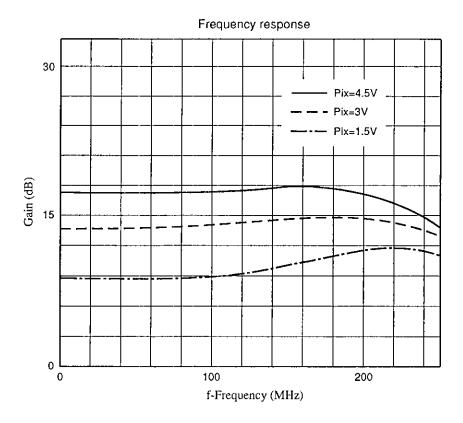

- · Built-in super wide-band amplifier (250 MHz/-3dB typ.)

- 1 channel to 1 package

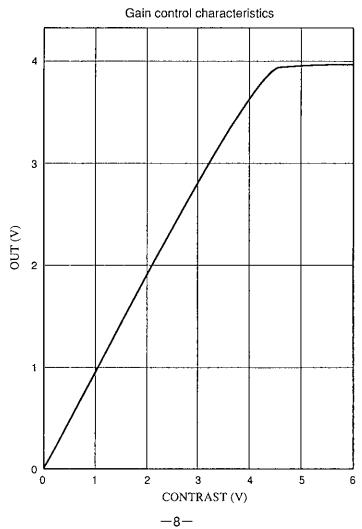

- Contrast can be controlled by DC.

- Rise/fall time of 2ns or less due to output amplitude of 4 VP-P

- Drive adjustment for the three channels (R, G, B) is easily accomplished because the contrast characteristic is linear.

#### Absolute Maximum Ratings (Ta=25°C)

| <ul> <li>Supply voltage</li> </ul> | Vcc  | 14          | V  |

|------------------------------------|------|-------------|----|

| Operating temperature              | Topr | -20 to +75  | °C |

| Storage temperature                | Tstg | -65 to +150 | °C |

| • Allowable power dissipa          | tion |             |    |

|                                    | Po   | 1040        | mW |

### **Operating Conditions**

| <ul> <li>Recommended supply voltage</li> </ul> | 12.0    | V |

|------------------------------------------------|---------|---|

| Operating range                                | 12 ±0.5 | V |

#### Structure

Bipolar silicon monolithic IC

#### **Applications**

Pre-driver for ultra-high resolution computer displays

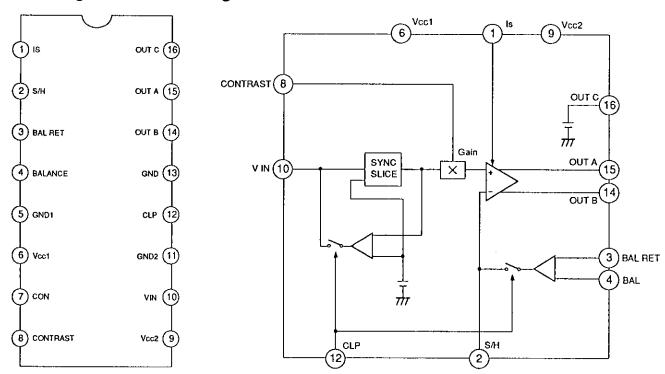

# **Block Diagram and Pin Configuration**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

## **Pin Description**

| Pin No. | Symbol   | Pin voltage | Equivalent circuit                              | Description                                                                                               |

|---------|----------|-------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 1       | IS       | 3V          | 3v — 129 — 17/1                                 | Determines a reference current source. Connect a 15 k $\Omega$ metal film resistor between Pin 1 and GND. |

| 2       | S/H      | 8V          | Vcc1                                            | Connect a capacitor for clamp.                                                                            |

| 3       | BAL RET  | 4V          | 3 W-W 2                                         | Inputs a feedback signal from the drive stage to stabilize the DC bias at cathode drive stage.            |

| 4       | BALANCE  | 4V          | CLP CLP 7/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1 | Sets a output DC level.                                                                                   |

| 8       | CONTRAST |             | 10μA<br>8<br>129<br>7///                        | Contrast control. Control is possible between 0 to 5 V DC.                                                |

| 10      | VIN      |             | 10 Vcc2<br>129 400µА                            | Video signal input.                                                                                       |

| 12      | CLP      |             | O Vcc1                                          | Clamp pulse input.                                                                                        |

| Pin No. | Symbol | Pin voltage | Equivalent circuit | Description                             |

|---------|--------|-------------|--------------------|-----------------------------------------|

| 14      | OUT B  |             | Vcc2               | Negative polarity output signal.        |

| 15      | OUT A  |             | 14) (15)           | Positive polarity output signal.        |

| 16      | OUT C  | 2.6V        | 3.5V 1.4V 16       | 2.6V power supply output.               |

| 6       | Vcc1   | 12V         |                    | Supply voltage for control system.      |

| 9       | Vcc2   | 12V         |                    | Supply voltage for pre-amplifier block. |

| 5       | GND1   | 0           |                    | GND for control system.                 |

| 11      | GND2   | 0           |                    | GND for pre-amplifier block.            |

| 7       | CON    | 0           |                    | Connect to GND.                         |

## **Electrical Characteristics Measurement Circuit**

# **Electrical Characteristics**

| No.     | Item               | Symbol  | Input conditions and measurements                                                                                                                                                                                                                                | Min.  | Тур.  | Max. | Unit     |

|---------|--------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|----------|

| 1       | Supply current     | lcc     | Measure the inflow current at Pins 6 and 9                                                                                                                                                                                                                       |       | 33    | 45   | mA       |

| <u></u> |                    |         | at no signal, no load.                                                                                                                                                                                                                                           |       |       |      | <u> </u> |

| 2       | Frequency response | f150MHz | R. G. B input  O.7VP-P  The signal portion is 1MHz  or 150MNz.                                                                                                                                                                                                   | - 3.0 | + 1.0 | _    | dB       |

|         |                    |         | R. G. B output  Vsig                                                                                                                                                                                                                                             |       |       |      |          |

|         |                    |         | Input: Input 0.7 VP-P, 1 MHz or 150 MHz and measure the output amplitude VSIG.  Specifications can be obtained through the following formula, assuming VSIG1 for1MHz and VSIG150 for 150MHz.  f1-150 = 20 log (VSIG150 VSIG1) (dB)  * Measure VSIG peak to peak. |       |       |      |          |

| 3       | Contrast control   | CONTMAX | R. G. B input  The signal portion is 1MHz.  R. G. B output  Wasaure the output amplitude VSIG at 0.7 VP-P, 1 MHz. The specifications can be obtained though the following formula.  CONTMAX (MIN) = 20 log (VSIG 0.7) (dB)                                       | 13.5  | 15.0  |      | dΒ       |

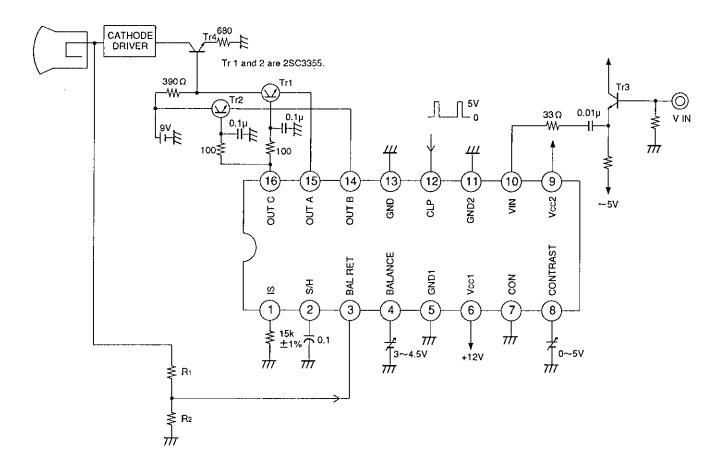

## **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party and other right due to same.

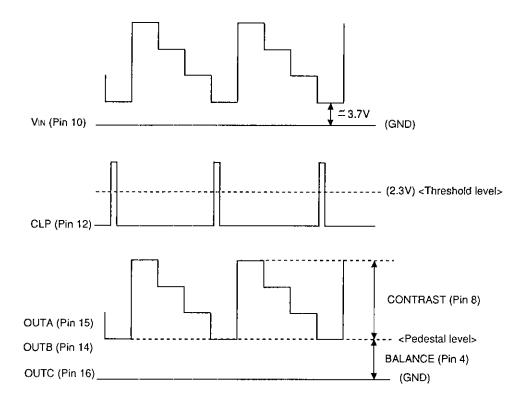

#### Input/Output Pulse Waveforms and Description of Operation

#### 1. Contrast

Gain is controlled on the VIN (Pin 10) input signal, using the DC voltage input from CONTRAST (Pin 8). The control range is from -20 to 15 dB (typ.).

#### 2. Pedestal Clamp

The pedestal level is clamped while CLAMP (Pin 12) is high. The threshold level of the clamp pulse is approximately 2.3 V. Note that 300 ns are required for clamp time.

The output DC level can be varied by the DC input from BALANCE (Pin 4). In this time, the emitter follower output at the external transistor should not be below 2 V or low.

3. The output signal is amplified by the external power amplifier and drives the CRT. The amplified signal voltage is fed back to Pin 3. Then, set the R1 and R2 values so that the pedestal level at Pin 3 is  $4 \pm 0.5$  V.

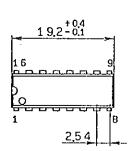

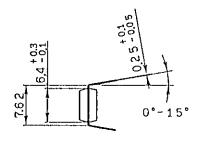

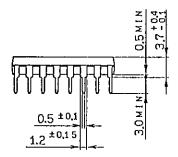

# Package Outline Unit: mm

16pin DIP (Plastic) 300mil 1.0g

| SONYNAME   | DIP-16P-01        |

|------------|-------------------|

| ETAJNAME   | *DIP016-P-0300-A  |

| JEDEC CODE | MO-001-AE similar |