# 3.3V/250mA, 5V/100mA Micropower Low Dropout Regulator with ENABLE

## Description

The CS8481 is a precision, dual micropower linear voltage regulator. The switched 3.3V primary output ( $V_{OUT1}$ ) supplies up to 250mA while the secondary 5V ( $V_{OUT2}$ ) is capable of supplying 100mA. Both outputs have a maximum dropout voltage of 600mV and low reverse current. Quiescent current drain is typically 150 $\mu$ A when supplying 100 $\mu$ A from each output.

The ENABLE input provides logic level control of the primary output.

With the primary output disabled, quiescent current drain is typically  $100\mu A$  when supplying  $100\mu A$  from the secondary output.

The CS8481 is extremely robust with protection provided for reverse battery, short circuit, overvoltage, and overtemperature on both outputs.

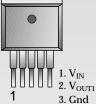

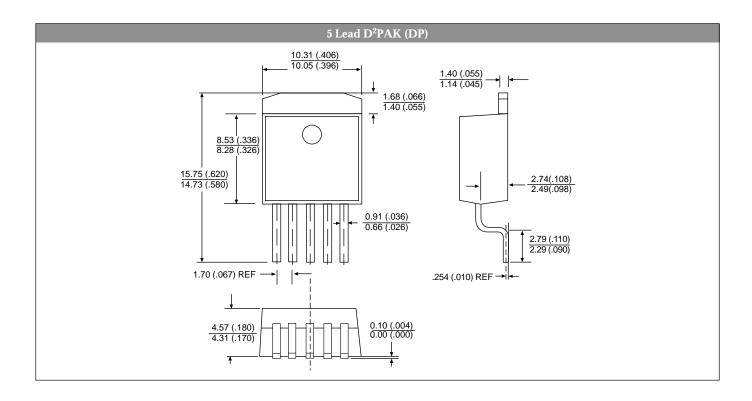

The CS8481 is available in a 5-lead  $D^2PAK$ .

#### **Features**

- 3.3V, 250mA Primary Output

- 5V, 100mA Secondary Output

- 3% Tolerance, Both Outputs

- ON/OFF Control for Primary Output

- Low Quiescent Current Drain (100µA V<sub>OUT2</sub>)

- Low Reverse Current

- Protection Features

Reverse Battery (-15V)

74V Peak Transient

Voltage

Short Circuit

Overtemperature

Overvoltage (34V)

### **Package Options**

# 5 Lead D<sup>2</sup>PAK Tab (Gnd)

4. V<sub>OUT2</sub> 5. ENABLE

Consult factory for 8L and 16L SO, 8L and 16L PDIP, 7L D<sup>2</sup>PAK and 5L TO-220.

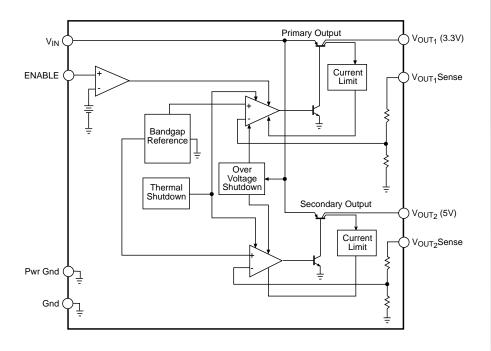

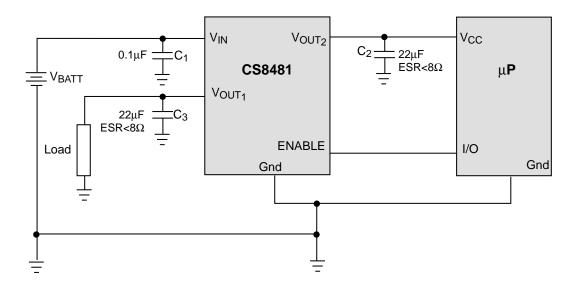

#### **Block Diagram**

ON Semiconductor 2000 South County Trail, East Greenwich, RI 02818 Tel: (401)885–3600 Fax: (401)885–5786 N. American Technical Support: 800-282-9855 Web Site: www.cherry-semi.com

Overvoltage Shutdown

|                                             | Absolute Maximum Ratings                                                                                           |                         |                      |                                  |                                                         |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------|----------------------------------|---------------------------------------------------------|

| Reverse Battery                             | DV Load Dump @ 14V V <sub>IN</sub> )re                                                                             |                         |                      | Internally<br>40°C to<br>55°C to | 15V<br>74V<br>10V<br>Limited<br>+150°C<br>+150°C<br>4kV |

| Electrical Characteristics: $6V \le V_{IN}$ | $I_{\rm I} \leq 26 V,  I_{\rm OUT1} = I_{\rm OUT2} = 100 \mu A,  -40^{\circ} C \leq T_{\rm A} \leq 125^{\circ} C,$ | $-40^{\circ}C \leq T_C$ | ≤ <b>125°C, un</b> l | less otherwise                   | e specifi                                               |

| PARAMETER                                   | TEST CONDITIONS                                                                                                    | MIN                     | TYP                  | MAX                              | UNI                                                     |

| ■ Primary Output Stage (V <sub>O</sub>      | <sub>UT1</sub> )                                                                                                   |                         |                      |                                  |                                                         |

| Output Voltage, V <sub>OUT1</sub>           | $100\mu A \le I_{OUT1} \le 250mA$                                                                                  | 3.2                     | 3.3                  | 3.4                              | V                                                       |

| Line Regulation                             | $6V \leq V_{IN} \leq 26V$                                                                                          |                         | 5                    | 50                               | m <sup>v</sup>                                          |

| Load Regulation                             | $1mA \leq I_{OUT1} \leq 250mA,\ V_{IN} = 14V$                                                                      |                         | 5                    | 50                               | m'                                                      |

| Quiescent Current                           | $\begin{split} &ENABLE = HIGH,  V_{IN} = 16V, \\ &I_{OUT1} = 250mA \end{split}$                                    |                         | 22                   | 50                               | m                                                       |

| Ripple Rejection                            | $f = 120Hz, I_{OUT1} = 125mA, 7V \le V_{IN} \le 17V$                                                               | 60                      | 70                   |                                  | dl                                                      |

| Current Limit                               | $9V \leq V_{IN} \leq 26V$                                                                                          | 260                     | 400                  |                                  | m                                                       |

| Short Circuit Current Limit                 | $V_{OUT1} = 0V$ , $V_{IN} = 16V$                                                                                   | 25                      |                      |                                  | m                                                       |

| Reverse Current                             | $V_{OUT1} = 3.3V, V_{IN} = 0V$                                                                                     |                         | 100                  | 1500                             | μΑ                                                      |

| Secondary Output (V <sub>OUT2</sub> )       |                                                                                                                    |                         |                      |                                  |                                                         |

| Output Voltage, V <sub>OUT2</sub>           | $100\mu A \le I_{OUT2} \le 100mA$                                                                                  | 4.85                    | 5.00                 | 5.15                             | V                                                       |

| Dropout Voltage                             | $\begin{split} &I_{OUT2} = 100 mA \\ &I_{OUT2} = 100 \mu A \end{split}$                                            |                         | 400<br>100           | 600<br>150                       | m<br>m                                                  |

| Line Regulation                             | $6V \leq V_{IN} \leq 26V$                                                                                          |                         | 5                    | 50                               | m                                                       |

| Load Regulation                             | $100\mu A \leq I_{OUT2} \leq 100mA,~V_{IN}=14V$                                                                    |                         | 5                    | 50                               | m                                                       |

| Quiescent Current                           | $\begin{split} &ENABLE = LOW,  V_{IN} = 12.8V \\ &ENABLE = HIGH,  V_{IN} = 16V, \\ &I_{OUT2} = 100mA \end{split}$  |                         | 100<br>8             | 150<br>30                        | μ<br>m                                                  |

| Dinnla Dajaatian                            | $I_{OUT2} = IUUIIIA$ $f = 190 \text{ Hz}  I = -10 \text{ m/s}  7 \text{ V} < V < 17 \text{ V}$                     | eo                      | 70                   |                                  | a                                                       |

|                                            | $I_{OUT2} = IUUIIIA$                               |     |     |     |        |

|--------------------------------------------|----------------------------------------------------|-----|-----|-----|--------|

| Ripple Rejection                           | $f=120Hz,~I_{OUT2}=10mA,~7V\leq V_{IN}\leq 17V$    | 60  | 70  |     | dB     |

| Current Limit                              | $9V \le V_{IN} \le 26V$                            | 105 | 200 |     | mA     |

| Short Circuit Current Limit                | $V_{OUT2} = 0V$ , $V_{IN} = 16V$ , $I_{OUT1} = 0A$ | 25  |     |     | mA     |

| Reverse Current                            | $V_{OUT2} = 5V$ , $V_{IN} = 0V$                    |     | 100 | 250 | μΑ     |

| ■ Enable Function (ENABLE) Input Threshold |                                                    | 2.0 | 1.2 | 0.8 | V<br>V |

| Input Bias Current                         | $0V \le V_{ENABLE} \le 5V$                         | -2  | 0   | 2   | μΑ     |

| ■ Protection Circuits                      |                                                    |     |     |     |        |

| Overtemperature Threshold                  | Guaranteed by Design                               |     |     |     |        |

#### **Package Lead Description**

| PACKAGE LEAD #            | LEAD SYMBOL | FUNCTION                                                                                        |

|---------------------------|-------------|-------------------------------------------------------------------------------------------------|

| 5 Lead D <sup>2</sup> PAK |             |                                                                                                 |

| 1                         | $V_{ m IN}$ | Supply voltage to IC, usually direct from battery.                                              |

| 2                         | $V_{OUT1}$  | 3.3V regulated output which is activated by ENABLE input.                                       |

| 3                         | Gnd         | Ground connection.                                                                              |

| 4                         | $V_{OUT2}$  | Standby output 5V, 100mA capability; always on.                                                 |

| 5                         | ENABLE      | CMOS compatible input lead; switches $V_{OUT1}. \ When \ ENABLE$ is high, $V_{OUT1}$ is active. |

#### **Definition of Terms**

#### **Current Limit**

Peak current that can be delivered to the output.

#### **Dropout Voltage**

The input-output voltage differential at which the circuit ceases to regulate against further reduction in input voltage. Measured when the output voltage has dropped 100mV from the nominal value obtained at 14V input, dropout voltage is dependent upon load current and junction temperature.

#### **Input Output Differential**

The voltage difference between the unregulated input voltage and the regulated output voltage for which the regulator will operate.

#### **Input Voltage**

The DC voltage applied to the input terminals with respect to ground.

#### **Line Regulation**

The change in output voltage for a change in the input voltage. The measurement is made under conditions of low dissipation or by using pulse techniques such that the average chip temperature is not significantly affected.

#### **Load Regulation**

The change in output voltage for a change in load current at constant chip temperature.

#### **Long Term Stability**

Output voltage stability under accelerated life-test conditions after 1000 hours with maximum rated voltage and junction temperature.

#### **Quiescent Current**

The part of the positive input current that does not contribute to the positive load current. i.e., the regulator ground lead current.

#### **Ripple Rejection**

The ratio of the peak-to-peak input ripple voltage to the peak-to-peak output ripple voltage.

#### **Short Circuit Current Limit**

Peak current that can be delivered by the output when forced to 0V.

#### Temperature Stability of Vout

The percentage change in output voltage for a thermal variation from room temperature to either temperature extreme.

#### **Application Notes**

#### General

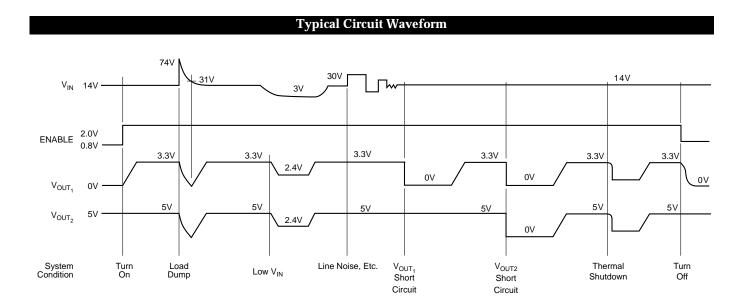

The CS8481 is a micropower dual regulator. All bias required to operate the internal circuitry is derived from the standby output,  $V_{OUT2}$ . If this output experiences an over current situation and collapses, then  $V_{OUT1}$  will also collapse (see timing diagrams).

If there is critical circuitry that must remain active under most conditions it should be connected to  $V_{OUT2}$ . Any circuitry that is likely to be subjected to a short circuit, e.g., circuitry outside the module, should be connected to  $V_{OUT1}$ .

#### **External Capacitors**

Output capacitors are required for stability with the CS8481. Without them, the regulator outputs will oscillate. Actual size and type may vary depending upon the application load and temperature range. Capacitor effective series resistance (ESR) is also a factor in the IC stability. Worst-case is determined at the minimum ambient temperature and maximum load expected.

Output capacitors can be increased in size to any desired value above the minimum. One possible purpose of this would be to maintain the output voltages during brief conditions of negative input transients that might be characteristic of a particular system.

Capacitors must also be rated at all ambient temperatures expected in the system. To maintain regulator stability down to -40°C, capacitors rated at that temperature must be used.

More information on capacitor selection for Smart Regulators<sup>TM</sup> is available in the Smart Regulator application note, *Compensation for Linear Regulators*.

#### **ENABLE**

The ENABLE function controls  $V_{\text{OUT1}}$ . When ENABLE is high,  $V_{\text{OUT1}}$  is on. When ENABLE is low,  $V_{\text{OUT1}}$  is off.

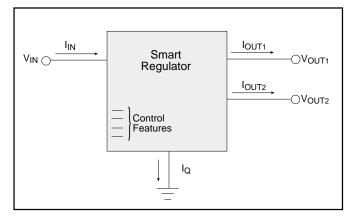

# Calculating Power Dissipation in a Dual Output Linear Regulator

The maximum power dissipation for a dual output regulator (Figure 1) is:

$$\begin{split} P_{D(MAX)} &= (V_{IN(MAX)} - V_{OUTI(MIN)})(I_{OUT1(MAX)}) \\ &+ (V_{IN(MAX)} - V_{OUT2(MIN)})(I_{OUT2(MAX)}) \\ &+ (V_{IN(MAX)})(I_{Q}) \end{split} \tag{1}$$

where

$V_{IN(MAX)}$  is the maximum input voltage;

$V_{OUT1(MIN)}$  is the minimum output voltage from  $V_{OUT1}$ ;  $V_{OUT2(MIN)}$  is the minimum output voltage from  $V_{OUT2}$ ;  $I_{OUT1(MAX)}$  is the maximum output current for the application;

$I_{OUT2(MAX)}$  is the maximum output current for the application; and

$I_Q$  is the quiescent current the regulator consumes at both  $I_{OUT1(MAX)}$  and  $I_{OUT2(MAX)}$ .

Once the value of  $P_{D(MAX)}$  is known, the maximum permissible value of  $R_{OJA}$  can be calculated:

$$R_{\Theta JA} = \frac{150^{\circ} \text{C} - \text{T}_{A}}{P_{D}} \tag{2}$$

The value of  $R_{\Theta JA}$  can then be compared with those in the package section of the data sheet. Those packages with  $R_{\Theta JA}$ 's less than the calculated value in equation 2 will keep the die temperature below  $150^{\circ}C.$

In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heat sink will be required.

Figure 1: Dual output regulator with key performance parameters labeled.

#### **Heat Sinks**

A heat sink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R_{\Theta IA}$ .

$$R_{\Theta IA} = R_{\Theta IC} + R_{\Theta CS} + R_{\Theta SA} \tag{3}$$

where:

$R_{\Theta JC}$  = the junction-to-case thermal resistance;

$R_{\Theta CS}$  = the case-to-heat sink thermal resistance; and

$R_{\Theta SA}$  = the heat sink-to-ambient thermal resistance.

$R_{\Theta JC}$  appears in the package section of the data sheet. Like  $R_{\Theta JA}$ , it too is a function of package type.  $R_{\Theta CS}$  and  $R_{\Theta SA}$  are functions of the package type, heat sink and the interface between them. These values appear in heat sink data sheets of heat sink manufacturers.

- \* C1 required if regulator is located far from power supply filter.

\*\* C2 and C3 required for stability. Capacitor must operate at minimum temperature expected during system operations.

#### Package Specification

#### PACKAGE DIMENSIONS IN MM(INCHES)

#### PACKAGE THERMAL DATA

| Thermal         | Data              | 5 Lead D <sup>2</sup> PAK                           |                         |

|-----------------|-------------------|-----------------------------------------------------|-------------------------|

| $R_{\Theta JC}$ | typ               | 2.4                                                 | °C/W                    |

| $R_{\Theta JA}$ | typ               | 10-50*                                              | °C/W                    |

| * Dependin      | g on thermal prop | erties of substrate. $R_{\Theta JA} = R_{\Theta J}$ | $I_{C} + R_{\Theta CA}$ |

| Ordering Information |                                         |  |

|----------------------|-----------------------------------------|--|

| Part Number          | Description                             |  |

| CS8481YDP5           | 5 Lead D <sup>2</sup> PAK               |  |

| CS8481YDPR5          | 5 Lead D <sup>2</sup> PAK (tape & reel) |  |

ON Semiconductor and the ON Logo are trademarks of Semiconductor Components Industries, LLC (SCILLC). ON Semiconductor reserves the right to make changes without further notice to any products herein. For additional information and the latest available information, please contact your local ON Semiconductor representative.