# **Enhanced Current Mode PWM Controller**

## Description

The CS51021A/2A/3A/4A Fixed Frequency PWM Current Mode Controller family provides all necessary features required for AC-DC or DC-DC primary side control. Several features are included eliminating the additional components needed to implement them externally. In addition to low start-up current (75 $\mu$ A) and high frequency operation capability, the CS51021A/2A/3A/4A family includes overvoltage and undervoltage monitoring, externally pro-

grammable dual threshold overcurrent protection, current sense leading edge blanking, current slope compensation, accurate duty cycle control and an externally available 5V reference. The CS51021A and CS51023A feature bidirectional synchronization capability, while the CS51022A and CS51024A offer a sleep mode with  $100\mu A$  maximum IC current consumption. The CS51021A/2A/3A/4A family is available in a 16 lead narrow body SO package.

| Device   | Sleep/Synch | V <sub>CC</sub> Start/Stop |

|----------|-------------|----------------------------|

| CS51021A | Synch       | 8.25V/7.7V                 |

| CS51022A | Sleep       | 8.25V / 7.7V               |

| CS51023A | Synch       | 13V/7.7V                   |

| CS51024A | Sleep       | 13V/7.7V                   |

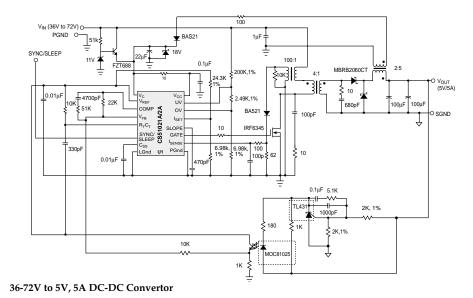

#### **Typical Application Diagram**

### **Features**

- 75μA Max. Startup Current

- Fixed Frequency Current Mode Control

- **1MHz Switching Frequency**

- Undervoltage Protection Monitor

- Overvoltage Protection

Monitor with

Programmable Hysteresis

- Programmable Dual

Threshold Overcurrent

Protection with Delayed

Restart

- Programmable Soft Start

- Accurate Maximum Duty Cycle Limit

- Programmable Slope Compensation

- Leading Edge Current Sense Blanking

- 1A Sink/Source Gate Drive

- Bidirectional Synchronization (CS51021A/3A)

- 50ns PWM Propagation Delay

- 100μA Max Sleep Current (CS51022A/4A)

# Package Options 16 Lead SO Narrow

GATE 1  $\square V_{C}$ ISENSE [ PGnd SLEEP C □Vcc □V<sub>REF</sub> SLOPE [ LGnd UV ∃ss OVI COMP R<sub>T</sub>C<sub>T</sub> ISET □V<sub>FB</sub>

Consult factory for other package options.

ON Semiconductor 2000 South County Trail, East Greenwich, RI 02818 Tel: (401)885–3600 Fax: (401)885–5786 N. American Technical Support: 800-282-9855 Web Site: www.cherry-semi.com

| Absolute Maximum Ratings                                                                                                                   |                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Power Supply Voltage, V <sub>CC</sub>                                                                                                      | –0.3V, 20V                          |

| Driver Supply Voltage, V <sub>C</sub>                                                                                                      | –0.3V, 20V                          |

| SYNC, SLEEP, R <sub>T</sub> C <sub>T</sub> , SOFT START, V <sub>FB</sub> , SLOPE, I <sub>SENSE</sub> , UV, OV, I <sub>SET</sub> (Logic Pir | ns)0.25V to V <sub>REF</sub>        |

| Peak GATE Output Current                                                                                                                   | 1A                                  |

| Steady State Output Current                                                                                                                | ± 0.2A                              |

| Operating Junction Temperature, T <sub>J</sub>                                                                                             | 150°C                               |

| Storage Temperature Range, T <sub>S</sub>                                                                                                  | 65 to 150°C                         |

| ESD (Human Body Model)                                                                                                                     | 2kV                                 |

| Lead Temperature Soldering: Reflow                                                                                                         | 60 sec. max above 183°C, 230°C peak |

# Electrical Characteristics: Unless otherwise stated, specifications apply for $-40^{\circ}\text{C} < T_{\text{A}} < 85^{\circ}\text{C}$ , $-40^{\circ}\text{C} < T_{\text{J}} < 150^{\circ}\text{C}$ , $3\text{V} < \text{V}_{\text{C}} < 20\text{V}$ , $8.2\text{V} < \text{V}_{\text{CC}} < 20\text{V}$ , $R_{\text{T}} = 12\text{k}\Omega$ , $C_{\text{T}} = 390\text{pF}$ .

| PARAMETER                               | TEST CONDITIONS                                                           | MIN                  | TYP                  | MAX                   | UNI     |

|-----------------------------------------|---------------------------------------------------------------------------|----------------------|----------------------|-----------------------|---------|

| <b>Under Voltage Lockout</b>            |                                                                           |                      |                      |                       |         |

| START Threshold (CS51021A/2A            | )                                                                         | 7.95                 | 8.25                 | 8.8                   | V       |

| START Threshold (CS51023A/4A            | A)                                                                        | 12.4                 | 13                   | 13.4                  | V       |

| STOP Threshold                          |                                                                           | 7.4                  | 7.7                  | 8.2                   | V       |

| Hysteresis (CS51021A/2A)                |                                                                           | 0.50                 | 0.75                 | 1.00                  | V       |

| Hysteresis (CS51023A/4A)                |                                                                           | 4                    | 5                    | 6                     | V       |

| I <sub>CC</sub> @ Startup (CS51021A/2A) | V <sub>CC</sub> < UV <sub>START</sub> Threshold                           |                      | 40                   | 75                    | μA      |

| I <sub>CC</sub> @ Startup (CS51023A/4A) | $V_{CC}$ < $UV_{START}$ Threshold                                         |                      | 45                   | 75                    | $\mu A$ |

| I <sub>CC</sub> Operating (CS51021A/3A) |                                                                           |                      | 7                    | 9                     | mA      |

| I <sub>CC</sub> Operating (CS51022A/4A) |                                                                           |                      | 6                    | 8                     | mA      |

| I <sub>C</sub> Operating                | Includes 1nF Load                                                         |                      | 7                    | 12                    | mA      |

| 77. lv . D . (                          |                                                                           |                      |                      |                       |         |

| Voltage Reference Initial Accuracy      | $\frac{1}{T_{A} = 25C, I_{REF} = 2mA, V_{CC} = 14V \text{ (Note1)}}$      | 4.95                 |                      | 5.05                  | V       |

| Total Accuracy                          | 1mA <i<sub>REF&lt;10mA</i<sub>                                            | 4.9                  | 5                    | 5.15                  | V       |

| Line Regulation                         | $8.2V < V_{CC} < 18V, I_{REF} = 2mA$                                      | 4.9                  | 6                    | 20                    | mV      |

|                                         |                                                                           |                      | 6                    | 15                    | mV      |

| Load Regulation                         | $1 \text{mA} < I_{\text{REF}} < 10 \text{mA}$                             |                      |                      | 13                    |         |

| NOISE Voltage                           | (Note 1)                                                                  |                      | 50                   | 20                    | μV      |

| OP Life Shift                           | T=1000 Hours (Note 1)                                                     | 00 × V               | 02 v V               | 20<br>05 × V          | mV      |

| FAULT Voltage                           | Force V <sub>REF</sub>                                                    |                      |                      | $.95 \times V_{REF}$  | V       |

| OK Voltage                              | Force V <sub>REF</sub>                                                    | $.94 \times V_{REF}$ | $.96 \times V_{REF}$ | $.985 \times V_{REF}$ | V       |

| OK Hysteresis                           | Force $V_{REF}$                                                           | 75                   | 165                  | 250                   | mV      |

| Current Limit                           | Force V <sub>REF</sub>                                                    | -20                  |                      |                       | mΑ      |

| T 4 110                                 |                                                                           |                      |                      |                       |         |

| Error Amplifier                         | T 250C I 2 A 37 1437                                                      | 2.465                | 2.515                | 2.575                 | <b></b> |

| Initial Accuracy                        | $T_A$ =25°C, $I_{REF}$ = 2mA, $V_{CC}$ = 14V,<br>$V_{FB}$ = COMP (Note 1) | 2.465                | 2.515                | 2.565                 | V       |

| Reference Voltage                       | $V_{FB} = COMP$                                                           | 2.440                | 2.515                | 2.590                 | V       |

| V <sub>FB</sub> Leakage Current         | $V_{FB} = 0V$                                                             |                      | -0.2                 | -2                    | μΑ      |

| Open Loop Gain                          | 1.4V < COMP < 4V (Note 1)                                                 | 60                   | 90                   |                       | dB      |

| Unity Gain Bandwidth                    | (Note 1)                                                                  | 1.5                  | 2.5                  |                       | MH      |

| COMP Sink Current                       | COMP = 1.5V, $V_{FB} = 2.7V$                                              | 2                    | 6                    |                       | mA      |

| COMP Source Current                     | $COMP = 1.5V, V_{FB} = 2.3V$                                              | -0.2                 | -0.5                 |                       | mΑ      |

# Electrical Characteristics: $-40^{\circ}\text{C} < T_{\text{A}} < 85^{\circ}\text{C}$ , $-40^{\circ}\text{C} < T_{\text{J}} < 150^{\circ}\text{C}$ , $3\text{V} < \text{V}_{\text{C}} < 20\text{V}$ , $8.2\text{V} < \text{V}_{\text{CC}} < 20\text{V}$ , $R_{\text{T}} = 12\text{k}\Omega$ , $C_{\text{T}} = 390\text{pF}$ , unless otherwise stated

| PARAMETER                                                                              | TEST CONDITIONS                                                                                            | MIN        | TYP                     | MAX              | UNIT             |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------|-------------------------|------------------|------------------|

| Error Amplifier continued                                                              |                                                                                                            |            |                         |                  |                  |

| COMP High Voltage                                                                      | $V_{FB} = 2.3V$                                                                                            | 4.35       | 4.8                     | 5                | V                |

| COMP Low Voltage                                                                       | $V_{FB} = 2.7V$                                                                                            | 0.4        | 0.8                     | 1.2              | V                |

| PS Ripple Rejection                                                                    | FREQ = 120Hz (Note 1)                                                                                      | 60         | 85                      |                  | dB               |

| SS Clamp, V <sub>COMP</sub>                                                            | $V_{SS}$ =2.5V, $V_{FB}$ = 0V, $I_{SET}$ = 2V                                                              | 2.4        | 2.5                     | 2.6              | V                |

| I <sub>LIM(SET)</sub> Clamp                                                            | (Note 1)                                                                                                   | 0.95       | 1                       | 1.15             | V                |

| Oscillator                                                                             |                                                                                                            |            |                         |                  |                  |

| Accuracy                                                                               | $R_T = 12k$ , $C_T = 390pF$                                                                                | 230        | 255                     | 280              | kHz              |

| Voltage Stability                                                                      | Delta Frequency 8.2V < V <sub>CC</sub> < 20V                                                               |            | 2                       | 3                | %                |

| Temperature Stability                                                                  | $T_{MIN} < T_A < T_{MAX}$ (Note1)                                                                          |            | 8                       |                  | %                |

| Min Charge & Discharge Time                                                            | (Note1)                                                                                                    | 0.333      |                         |                  | μs               |

| Duty Cycle Accuracy                                                                    | $R_T = 12k$ , $C_T = 390pF$                                                                                | 70         | 77                      | 83               | %                |

| Peak Voltage                                                                           | (Note 1)                                                                                                   |            | 3                       |                  | V                |

| Valley Voltage                                                                         | (Note 1)                                                                                                   |            | 1.5                     |                  | V                |

| Valley Clamp Voltage                                                                   | $10k$ Resistor to ground on $R_TC_T$                                                                       | 1.2        | 1.4                     | 1.6              | V                |

| Discharge Current                                                                      |                                                                                                            | 0.8        | 1                       | 1.2              | mA               |

| Discharge Current                                                                      | T <sub>A</sub> =25°C (Note 1)                                                                              | 0.925      | 1                       | 1.075            | mA               |

| Input Threshold<br>Output Pulsewidth                                                   |                                                                                                            | 1.0<br>160 | 1.5<br>260              | 2.7<br>400       | V<br>ns          |

| Output Pulsewidth                                                                      |                                                                                                            | 160        | 260                     | 400              | ns               |

| Output High Voltage                                                                    | $I_{SYNC} = 100\mu A$                                                                                      | 3.5        | 4.3                     | 4.8              | V                |

| Input Resistance                                                                       | (Note 1)                                                                                                   | 35         | 70                      | 140              | kΩ               |

| Drive Delay                                                                            | SYNC to GATE RESET                                                                                         | 80         | 120                     | 150              | ns               |

| Output Drive Current                                                                   | 1k Load                                                                                                    | 1.25       | 2                       | 3.5              | mA               |

| SLEEP (CS51022A/4A)                                                                    |                                                                                                            |            |                         |                  |                  |

| SLEEP Input Threshold                                                                  | Active High                                                                                                | 1.0        | 1.5                     | 2.7              | V                |

| SLEEP Input Current                                                                    | $V_{SLEEP} = 4V$                                                                                           | 11         | 25                      | 46               | μΑ               |

| I <sub>CC</sub> @ SLEEP                                                                | V <sub>CC</sub> ≤15V                                                                                       |            | 50                      | 100              | μA               |

| GATE Driver                                                                            |                                                                                                            |            |                         |                  |                  |

|                                                                                        |                                                                                                            |            |                         |                  |                  |

| HIGH Voltage                                                                           | Measure $V_C$ -GATE, $V_C$ = 10V, 150mA Lo                                                                 | oad        | 1.5                     | 2.2              | V                |

|                                                                                        | Measure $V_C$ -GATE, $V_C$ = 10V, 150mA Lo<br>Measure GATE-PGnd, 150mA SINK                                | oad        | 1.5<br>1.2              | 2.2<br>1.5       | V<br>V           |

| HIGH Voltage                                                                           |                                                                                                            | oad<br>11  |                         |                  |                  |

| HIGH Voltage<br>LOW Voltage                                                            | Measure GATE-PGnd, 150mA SINK                                                                              |            | 1.2                     | 1.5              | V                |

| HIGH Voltage<br>LOW Voltage<br>HIGH Voltage Clamp                                      | Measure GATE-PGnd, 150mA SINK $V_C = 20V$ , 1nF                                                            |            | 1.2<br>13.5             | 1.5<br>16        | V<br>V           |

| HIGH Voltage<br>LOW Voltage<br>HIGH Voltage Clamp<br>LOW Voltage Clamp                 | Measure GATE-PGnd, 150mA SINK $V_C = 20V$ , 1nF Measured at 10mA Output Current                            |            | 1.2<br>13.5<br>0.6      | 1.5<br>16        | V<br>V<br>V      |

| HIGH Voltage<br>LOW Voltage<br>HIGH Voltage Clamp<br>LOW Voltage Clamp<br>Peak Current | Measure GATE-PGnd, 150mA SINK $V_C = 20V$ , 1nF Measured at 10mA Output Current $V_C = 20V$ , 1nF (Note 1) |            | 1.2<br>13.5<br>0.6<br>1 | 1.5<br>16<br>0.8 | V<br>V<br>V<br>A |

| PARAMETER                              | TEST CONDITIONS                                         | MIN   | TYP   | MAZ |

|----------------------------------------|---------------------------------------------------------|-------|-------|-----|

| <b>SLOPE Compensation</b>              |                                                         |       |       |     |

| Charge Current                         | SLOPE = 2V                                              | -63   | -53   | -4  |

| COMP Gain                              | Fraction of slope voltage added to $I_{SENSE}$ (Note 1) | 0.095 | 0.100 | 0.1 |

| Discharge Voltage                      | SYNC = 0V                                               |       | 0.1   | 0.  |

| Current Sense OFFSET Voltage           | (Note 1)                                                | 0.09  | 0.10  |     |

|                                        | (Note 1)                                                | 0.09  |       | 0.  |

| Blanking Time Blanking Disable Voltage | Adjust V <sub>FB</sub>                                  | 1.8   | 2     | 10  |

| Second Current Threshold Gain          | Aujust v <sub>FB</sub>                                  | 1.21  | 1.33  | 1.  |

| I <sub>SENSE</sub> Input Resistance    |                                                         |       | 5     |     |

| Minimum On Time                        | GATE High to Low                                        | 30    | 70    | 13  |

| Gain                                   | (Note 1)                                                | 0.78  | 0.80  | 0.  |

$T_{J} < 150^{\circ}C$ ,

UNIT

μA V/V

V

$V \\ ns \\ V \\ V/V \\ k\Omega \\ ns \\ V/V$

V

$\mu A$

V

mV

$\mu A$

μΑ

V

V

2.6

-15

1.52

100

-40

5

0.30

2.4

-10

1.38

25

-70

250

4.4

0.25

2.5

-12.5

1.45

75

-55

1000

4.7

0.27

Note 1: Guaranteed by Design, not 100% tested in production.

SS = 2V

SS = 2V

OV Monitor Threshold

**OV Hysteresis Current**

UV Monitor Threshold

UV Monitor Hysteresis

SOFT START (SS)

Charge Current

Discharge Current

Charge Voltage,  $V_{SS}$

Discharge Voltage, V<sub>SS</sub>

| Package Pin Description |                        |                                                                                                       |  |

|-------------------------|------------------------|-------------------------------------------------------------------------------------------------------|--|

| PACKAGE PIN #           | PIN SYMBOL             | FUNCTION                                                                                              |  |

| 16 Lead SO Narrow       |                        |                                                                                                       |  |

| 1                       | GATE                   | External power switch driver with 1.0A peak capability.                                               |  |

| 2                       | I <sub>SENSE</sub>     | Current sense amplifier input.                                                                        |  |

| 3                       | SYNC<br>(CS51021A/3A)  | Bi-directional synchronization. Locks to the highest frequency.                                       |  |

| 3                       | SLEEP<br>(CS51022A/4A) | Active high chip disable. In sleep mode, $V_{\text{REF}}$ and GATE are turned off.                    |  |

| 4                       | SLOPE                  | Additional slope to the current sense signal. Internal current source charges the external capacitor. |  |

| 5                       | UV                     | Undervoltage protection monitor.                                                                      |  |

| 6                       | OV                     | Overvoltage protection monitor.                                                                       |  |

|               | Package Pin Description: continued |                                                                                                                                                  |  |

|---------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PACKAGE PIN # | PIN SYMBOL                         | FUNCTION                                                                                                                                         |  |

| 7             | $R_TC_T$                           | Timing resistor $R_T$ and capacitor $C_T$ determine oscillator frequency and maximum duty cycle, $D_{MAX}$ .                                     |  |

| 8             | $I_{SET}$                          | Voltage at this pin sets pulse-by-pulse overcurrent threshold, and second threshold (1.33 times higher) with Soft Start retrigger (hiccup mode). |  |

| 9             | $V_{FB}$                           | Feedback voltage input. Connected to the error amplifier inverting input.                                                                        |  |

| 10            | COMP                               | Error amplifier output. Frequency compensation network is usually connected between COMP and $V_{\text{FB}}$ pins.                               |  |

| 11            | SS                                 | Charging external capacitor restricts error amplifier output voltage during the start or fault conditions (hiccup).                              |  |

| 12            | LGnd                               | Logic ground.                                                                                                                                    |  |

| 13            | $V_{ m REF}$                       | 5.0V reference voltage output.                                                                                                                   |  |

| 14            | $V_{CC}$                           | Logic supply voltage.                                                                                                                            |  |

| 15            | PGnd                               | Output power stage ground connection.                                                                                                            |  |

| 16            | $V_{C}$                            | Output power stage supply voltage.                                                                                                               |  |

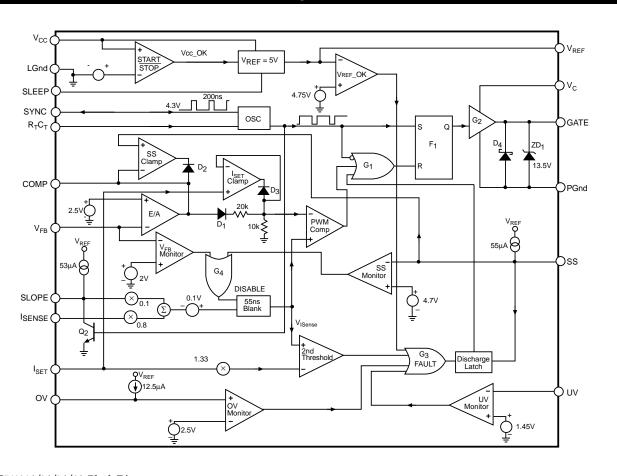

### Block Diagram

Figure 1: CS51021A/2A/3A/4A Block Diagram

#### **Circuit Description**

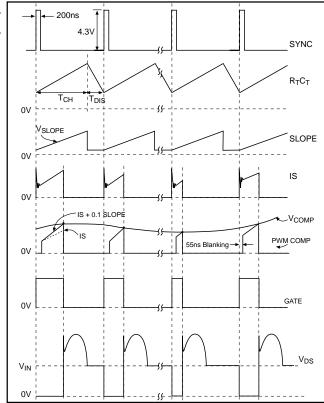

Figure 2: Typical Waveforms

#### Theory of Operation

#### Powering the IC

The IC has two supply and two ground pins.  $V_C$  and PGnd pins provide high speed power drive for the external power switch.  $V_{CC}$  and LGnd pins power the control portion of the IC. The internal logic monitors the supply voltage,  $V_{CC}$ . During abnormal operating conditions, the output is held low. The CS51021A/2A/3A/4A requires only  $75\mu A$  of startup current.

#### Voltage Feedback

The output voltage is monitored via the  $V_{FB}$  pin and is compared with the internal 2.5V reference. The error amplifier output minus one diode drop is divided by 3 and connected to the negative input of the PWM comparator. The positive input of the PWM comparator is connected to the modified current sense signal. The oscillator turns the external power switch on at the beginning of each cycle. When current sense ramp voltage exceeds the reference side of PWM comparator, the output stage latches off. It is turned on again at the beginning of the next oscillator cycle.

#### **Current Sense and Protection**

The current is monitored at the  $I_{SENSE}$  pin. The CS51021A/2A/3A/4A has leading edge blanking circuitry that ignores the first 55ns of each switching period.

Blanking is disabled when  $V_{FB}$  is less than 2V so that the minimum on-time of the controller does not have an additional 55ns of delay time during fault conditions. For the remaining portion of the switching period, the current sense signal, combined with a fraction of the slope compensation voltage, is applied to the positive input of the PWM comparator where it is compared with the divided by three error amplifier output voltage. The pulse-by-pulse overcurrent protection threshold is set by the voltage at the  $I_{SET}$  pin. This voltage is passed through the  $I_{SET}$  Clamp and appears at the non-inverting input of the PWM comparator, limiting its dynamic range according to the following formula:

Overcurrent Threshold=  $0.8 \times V_{I(SENSE)}$  +0.1V + 0.1  $V_{SLOPE}$  where

V<sub>I(SENSE)</sub> is voltage at the I<sub>SENSE</sub> pin

and

V<sub>SLOPE</sub> is voltage at the SLOPE pin.

During extreme overcurrent or short circuit conditions, the slope of the current sense signal will become much steeper than during normal operation. Due to loop propagation delay, the sensed signal will overshoot the pulse-by-pulse threshold eventually reaching the second overcurrent protection threshold which is 1.33 times higher than the first threshold and is described by the following equation:

2nd Threshold =

$$1.33 \times V_{I(SET)}$$

Exceeding the second threshold will reset the Soft Start capacitor  $C_{SS}$  and reinitiate the Soft Start sequence, repeating for as long as the fault condition persists.

#### **Soft Start**

During power up, when the output filter capacitor is discharged and the output voltage is low, the voltage across the Soft Start capacitor ( $V_{SS}$ ) controls the duty cycle. An internal current source of  $55\mu A$  charges  $C_{SS}$ . The maximum error amplifier output voltage is clamped by the SS Clamp. When the Soft Start capacitor voltage exceeds the error amplifier output voltage, the feedback loop takes over the duty cycle control. The Soft Start time can be estimated with the following formula:

$$t_{SS} = 9 \times 10^4 \times C_{SS}$$

The Soft Start voltage,  $V_{SS}$ , charges and discharges between 0.25V and 4.7V.

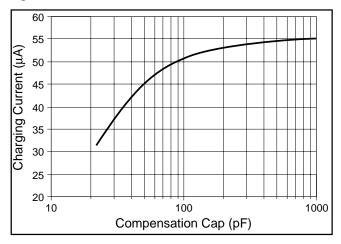

#### Slope Compensation

DC-DC converters with current mode control require a current sense signal with slope compensation to avoid instability at duty cycles greater than 50%. Slope capacitor  $C_S$  is charged by an internal  $53\mu A$  current source and is discharged during the oscillator discharge time. The slope compensation voltage is divided by 10 and is added to the current sense voltage,  $V_{I(SENSE)}$ . The signal applied to the

input of the PWM comparator is a combination of these

two voltages. The slope compensation,  $\frac{dV_{SLOPE}}{dt}$ , is calculated using the following formula:

$$\frac{dV_{SLOPE}}{dt} = 0.1 \times \frac{53\mu A}{C_S}$$

It should be noted that internal capacitance of the IC will cause an error when determining slope compensation capacitance  $C_S$ . This error is typically small for large values of  $C_S$ , but increases as  $C_S$  becomes small and comparable to the internal capacitance. The effect is apparent as a reduction in charging current due to the need to charge the internal capacitance in parallel with  $C_S$ . Figure 3 shows a typical curve indicating this decrease in available charging current.

Figure 3: The slope compensation pin charge current reduces when a small capacitor is used.

#### Undervoltage (UV) and Overvoltage (OV) Monitor

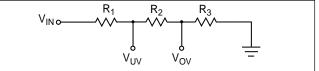

Two independent comparators monitor OV and UV conditions. A string of three resistors is connected in series between the monitored voltage (usually the input voltage) and ground (see Figure 4). When voltage at the OV pin exceeds 2.5V, an overvoltage condition is detected and GATE shuts down. An internal  $12.5\mu A$  current source turns on and feeds current into the external resistor,  $R_3$ , creating a hysteresis determined by the value of this resistor (the higher the value, the greater the hysteresis). The hysteresis voltage of the OV monitor is determined by the following formula:

$$V_{OV(HYST)} = 12.5 \mu A \times R_3$$

where  $R_3$  is a resistor connected from the OV pin to ground. When the monitored voltage is low and the UV pin is less than 1.45V, GATE shuts down. The UV pin has fixed 75mV hysteresis.

Both OV and UV conditions are latched until the Soft Start capacitor is discharged. This way, every time a fault condition is detected the controller goes through the power up sequence.

Figure 4: UV/OV Monitor Divider

To calculate the OV/UV resistor divider:

1. Solve for R<sub>3</sub>, based on OV hysteresis requirements.

$$R_3 = \frac{V_{OV(HYST)} \times 2.5V}{V_{MAX} \times 12.5\mu A},$$

where  $V_{\rm OV(HYST)}$  is the desired amount of overvoltage hysteresis, and  $V_{\rm MAX}$  is the input voltage at which the supply will shut down.

2. Find the total impedance of the divider.

$$R_{TOT} = R_1 + R_2 + R_3 = \frac{V_{MAX} \times R_3}{2.5}$$

3. Determine the value of  $R_2$  from the UV threshold conditions.

$$R_2 = \frac{1.45 \times R_{TOT}}{V_{MIN}} - R_{3}$$

where  $V_{\mbox{\scriptsize MIN}}$  is the UV voltage at which the supply will shut down.

4. Calculate R<sub>1</sub>.

$$R_1 = R_{TOT} - R_2 - R_3$$

5. The undervoltage hysteresis is given by:

$$V_{UV(HYST)} = \frac{V_{MIN} \times 0.075}{1.45}$$

#### **V**<sub>REF</sub> Monitor

The 5.0V reference voltage is internally monitored to ensure that it remains within specifications. The monitor, which outputs a fault, can be tripped by two methods:

- If the reference voltage drops below 4.75V

- If V<sub>CC</sub> falls below the STOP threshold

As indicated in the block diagram, any fault causes the output to stop switching and begins the discharge of the Soft Start capacitor  $C_{\rm SS}$ .

#### Synchronization

A bi-directional synchronization is provided to synchronize several controllers. When SYNC pins are connected together, the converters will lock to the highest switching frequency. The fastest controller becomes the master, producing a 4.3V, 200ns pulse train. Only one, the highest frequency SYNC signal, will appear on the SYNC line.

#### Circuit Description: continued

#### Sleep

The sleep input is an active high input. The CS51022A/4A is placed in sleep mode when SLEEP is driven high. In sleep mode, the controller and MOSFET are turned off. Connect to Gnd for normal operation. The sleep mode operates at  $V_{CC} \le 15V$ .

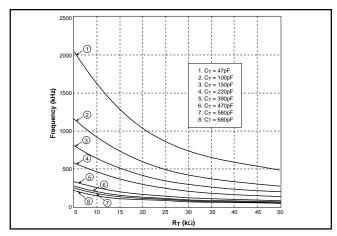

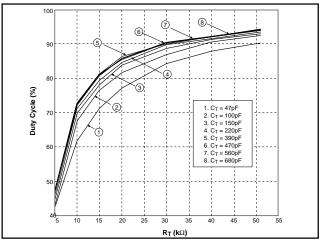

#### Oscillator and Duty Cycle Limit

The switching frequency is set by  $R_T$  and  $C_T$  connected to the  $R_TC_T$  pin.  $C_T$  charges and discharges between 3V and 1.5V.

The maximum duty cycle is set by the ratio of the on time,  $\mathbf{t}_{ON}$ , and the whole period,  $T = \mathbf{t}_{ON} + \mathbf{t}_{OFF}$ . Because the timing capacitor's discharge current is trimmed, the maximum duty cycle is well defined. It is determined by the ratio between the timing resistor  $R_T$  and the timing capacitor  $C_T$ . Refer to figures 5 and 6 to select appropriate values for  $R_T$  and  $C_T$ .

$$f_{SW} = \frac{1}{T_{SW}}$$

;  $T_{SW} = t_{CH} + t_{DIS}$

Figure 5: Frequency vs. R<sub>T</sub> for Discrete Capacitor Values.

Figure 6: Duty Cycle vs. R<sub>T</sub> for Discrete Capacitor Values.

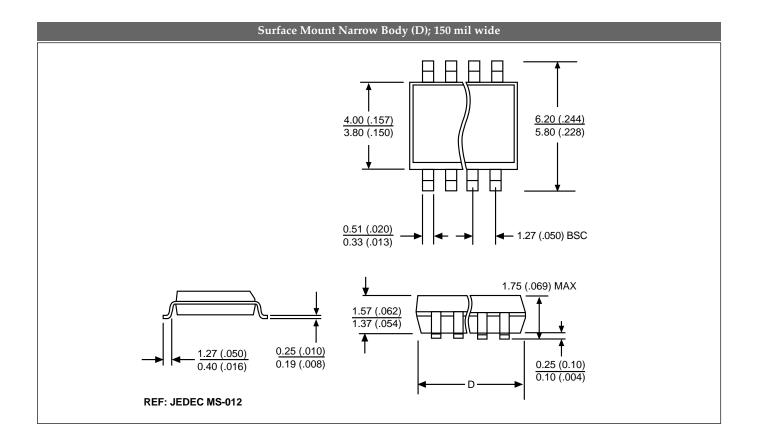

#### **Package Specification**

#### PACKAGE DIMENSIONS IN mm (INCHES)

|                   | D     |      |      |       |

|-------------------|-------|------|------|-------|

| Lead Count        | Me    | tric | Eng  | glish |

|                   | Max   | Min  | Max  | Min   |

| 16 Lead SO Narrow | 10.00 | 9.80 | .394 | .386  |

| PACKAGE THERMAL DATA |     |                   |      |

|----------------------|-----|-------------------|------|

| Thermal Data         |     | 16 Lead SO Narrow |      |

| $R_{\Theta JC}$      | typ | 28                | °C/W |

| $R_{\Theta JA}$      | typ | 115               | °C/W |

| Ordering Information            |  |  |

|---------------------------------|--|--|

| Description                     |  |  |

| 16 Lead SO Narrow               |  |  |

| 16 Lead SO Narrow (tape & reel) |  |  |

| 16 Lead SO Narrow               |  |  |

| 16 Lead SO Narrow (tape & reel) |  |  |

| 16 Lead SO Narrow               |  |  |

| 16 Lead SO Narrow (tape & reel) |  |  |

| 16 Lead SO Narrow               |  |  |

| 16 Lead SO Narrow (tape & reel) |  |  |

|                                 |  |  |

ON Semiconductor and the ON Logo are trademarks of Semiconductor Components Industries, LLC (SCILLC). ON Semiconductor reserves the right to make changes without further notice to any products herein. For additional information and the latest available information, please contact your local ON Semiconductor representative.

### Notes