# **Contents**

| Page            | Section           | Title                                      |

|-----------------|-------------------|--------------------------------------------|

| 7               | 1.                | Introduction                               |

| 7               | 1.1.              | Features                                   |

| 9               | 1.2.              | Abbreviations                              |

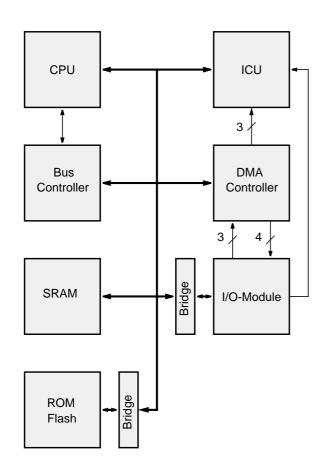

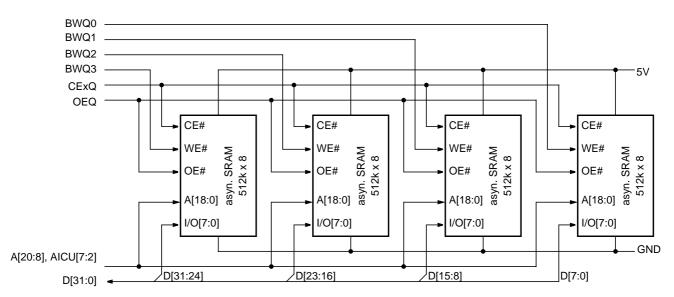

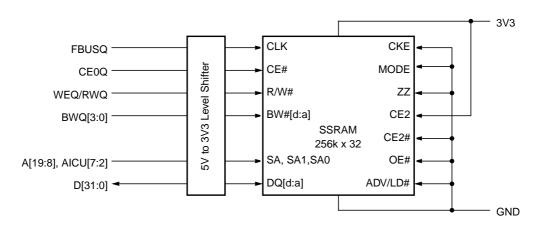

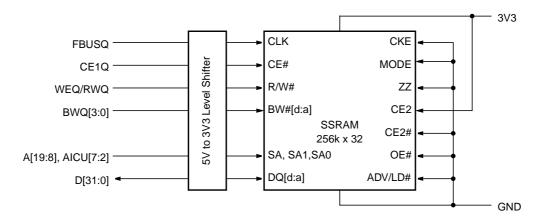

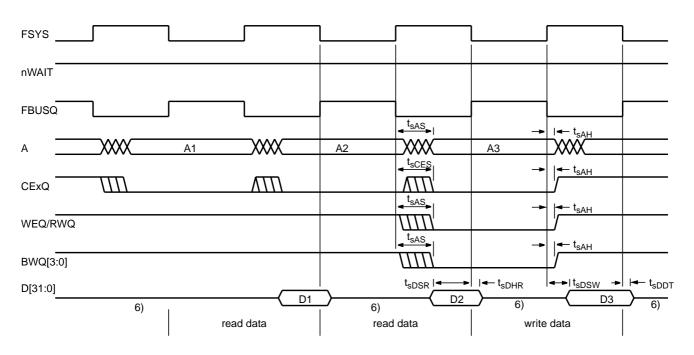

| 10              | 1.3.              | Block Diagrams                             |

| 13              | 2.                | Packages and Pins                          |

| 13              | 2.1.              | Pin Assignment                             |

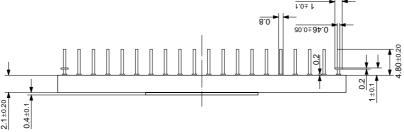

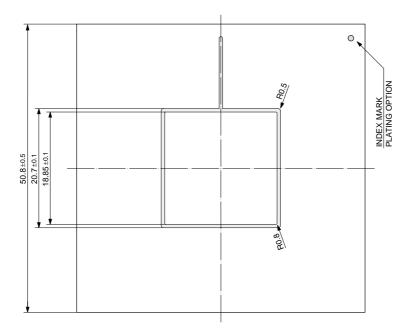

| 16              | 2.2.              | Package Outline Dimensions                 |

| 17              | 2.3.              | Multiple Function Pins                     |

| 17              | 2.4.              | Pin Function Description                   |

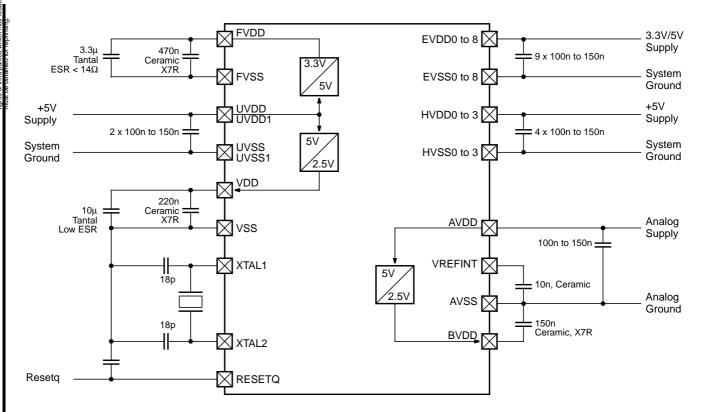

| 21              | 2.5.              | External Components                        |

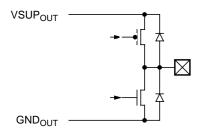

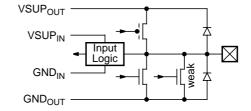

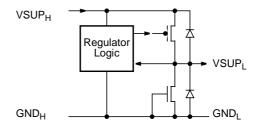

| 22              | 2.6.              | Pin Circuits                               |

| 25              | 3.                | Electrical Characteristics                 |

| 25              | 3.1.              | Absolute Maximum Ratings                   |

| 26              | 3.2.              | Recommended Operating Conditions           |

| 27              | 3.3.              | Characteristics                            |

| 34              | 3.4.              | Recommended Quartz Crystal Characteristics |

| 35              | 4.                | CPU and Clock System                       |

| 35              | 4.1.              | ARM7TDMI' CPU                              |

| 35              | 4.2.              | CPU Modes                                  |

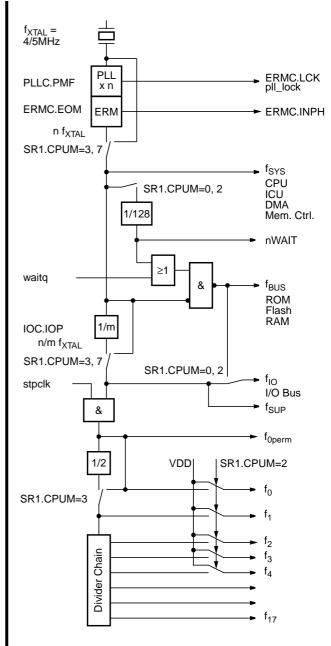

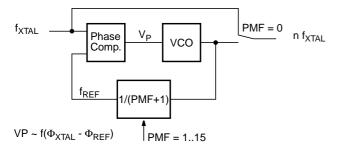

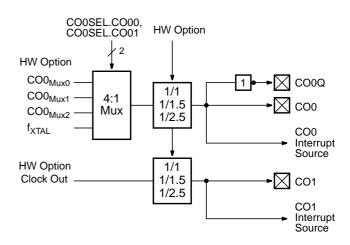

| 37              | 4.3.              | Clock System                               |

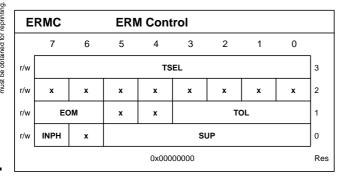

| 39              | 4.4.              | EMI Reduction Module (ERM)                 |

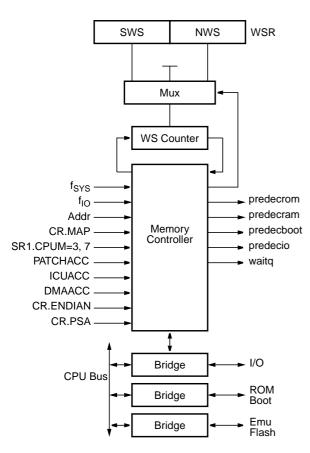

| 40              | 4.5.              | Memory Controller                          |

| 41              | 4.6.              | Registers                                  |

| 43              | 4.7.              | PLL/ERM Application Notes                  |

| 45              | 5.                | Memory and Boot System                     |

| 46              | 5.1.              | RAM and ROM                                |

| 47              | 5.2.              | I/O Map                                    |

| 48              | 5.3.              | Boot System                                |

| 49              | 6.                | Core Logic                                 |

| 49              | 6.1.              | Control Word CW                            |

| 50              | 6.2.              | Standby Registers                          |

| 52              | 6.3.              | UVDD Analog Section                        |

| 54              | 6.4.              | Reset Logic                                |

| 57              | 6.5.              | Test Registers                             |

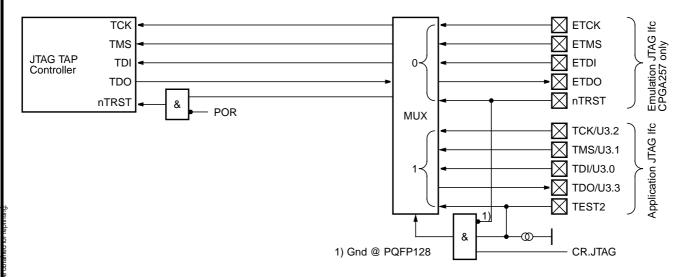

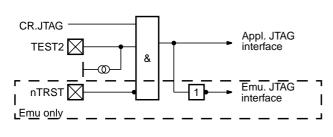

| 59              | 7.                | JTAG Interface                             |

| 59              | 7.1.              | Functional Description                     |

| 60              | 7.2.              | External Circuit Layout                    |

| 60              | 7.3.              | JTAG ID                                    |

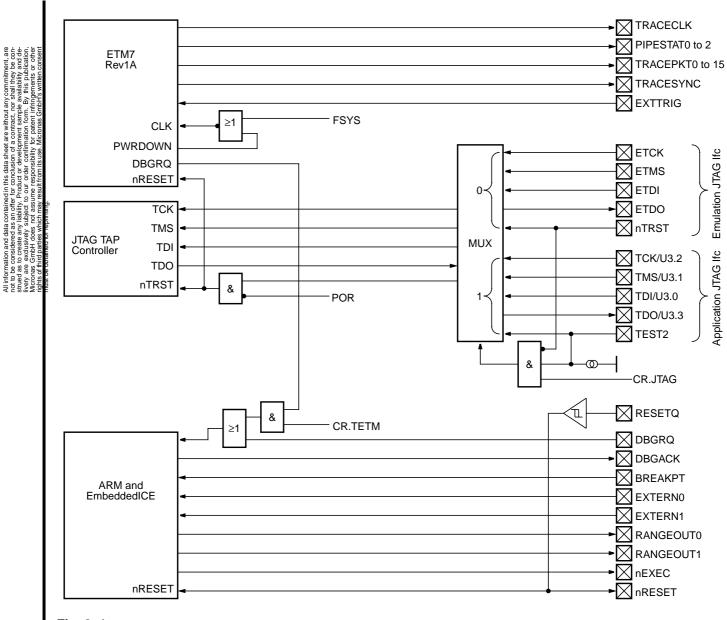

| 61              | 8.                | Embedded Trace Module (ETM)                |

| 61              | 8.1.              | Functional Description                     |

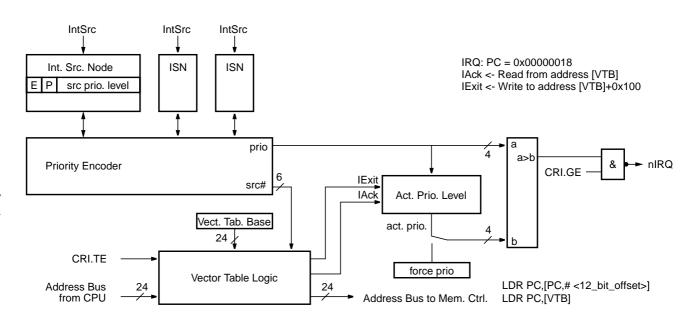

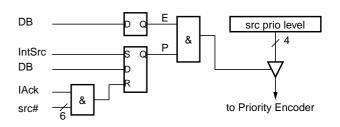

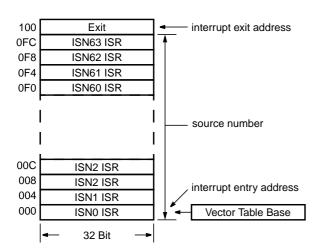

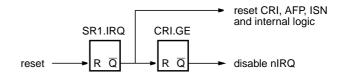

| <b>63</b><br>63 | <b>9.</b><br>9.1. | IRQ Interrupt Controller Unit (ICU)        |

| 00              | J. I.             | Functional Description                     |

In information and data contained in this data sheat are without any commitment, are not to be considered as an offer for conclusion of a contract, not shall they be contract as to create any liability. Product or development sample availability and delivery are exclusively subject to our order confirmation form. By this publication, Microras Gribth does not assume responsibility to patent infringements or other rights of third paties which may result from its use. Microras Gribth down as which may result from its use. Microras Gribth's written consent

| All information and data-contained in this data sheat are without any commitment are into the constitution to be considered as an offer for conclusion of a contract, not shall they be consistened as the contract of the construction of a contract, not shall they be consistened as the contract of the co | Microras GrnbH does not assume responsibility for patent infingements or other rights of third patters which may result from its use. Microras GrnbH's written consent must be obtained for reprinting. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contents        |                     |                                            |

|-----------------|---------------------|--------------------------------------------|

| Page            | Section             | Title                                      |

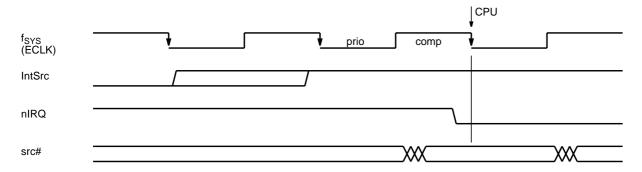

| 66              | 9.2.                | Timing                                     |

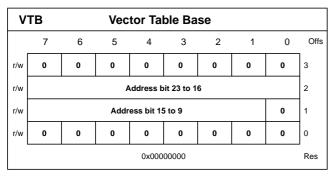

| 66              | 9.3.                | Registers                                  |

| 68              | 9.4.                | Principle of Operation                     |

| 68              | 9.5.                | Application Hints                          |

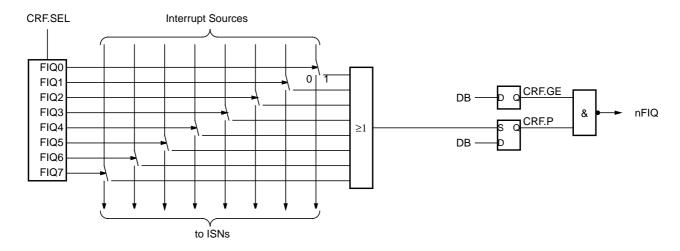

| <b>71</b><br>71 | <b>10.</b><br>10.1. | FIQ Interrupt Logic Functional Description |

| 71              | 10.2.               | Registers                                  |

| 72              | 10.3.               | Principle of Operation                     |

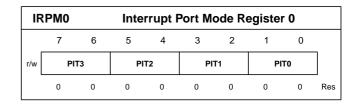

| 73              | 11.                 | Port Interrupts                            |

| 75              | 12.                 | Ports                                      |

| 75              | 12.1.               | Analog Input Port                          |

| 76              | 12.2.               | Universal Ports U0 to U8                   |

| 78              | 12.3.               | Universal Port Registers                   |

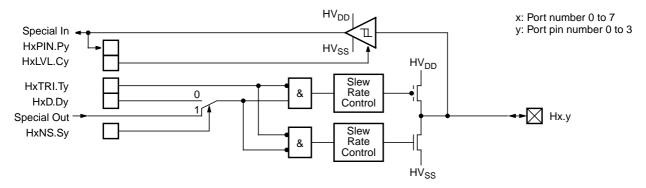

| 80              | 12.4.               | High Current Ports H0 to H7                |

| 81              | 12.5.               | High Current Port Registers                |

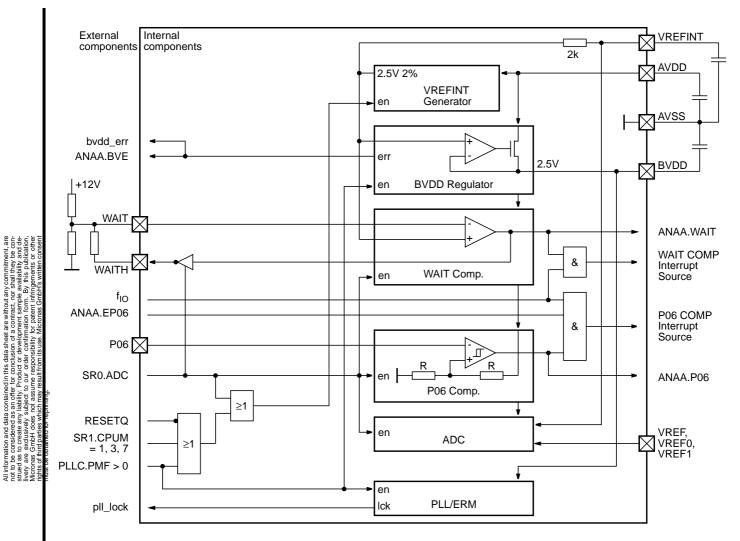

| 83              | 13.                 | AVDD Analog Section                        |

| 84              | 13.1.               | VREFINT Generator                          |

| 84              | 13.2.               | BVDD Regulator                             |

| 84              | 13.3.               | Wait Comparator                            |

| 84              | 13.4.               | P0.6 Comparator                            |

| 85              | 13.5.               | PLL/ERM                                    |

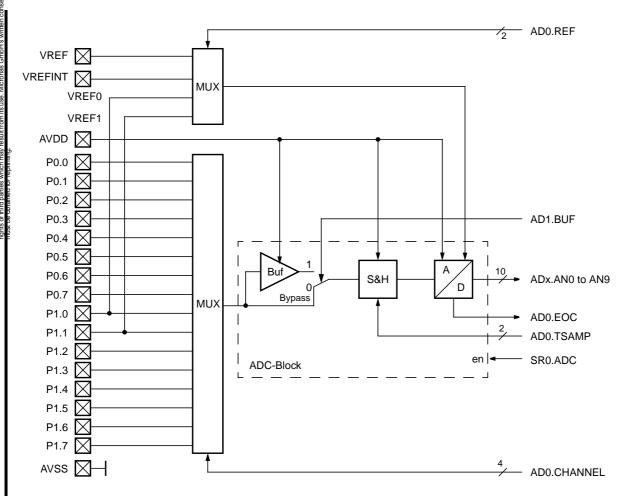

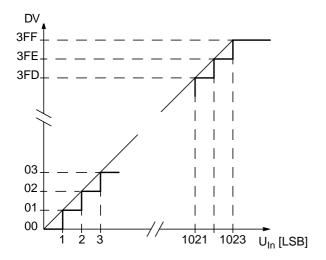

| 85              | 13.6.               | A/D Converter (ADC)                        |

| 87              | 13.7.               | Registers                                  |

| 89              | 14.                 | Timers (TIMER)                             |

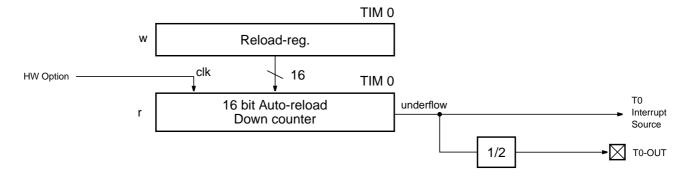

| 89              | 14.1.               | Timer T0                                   |

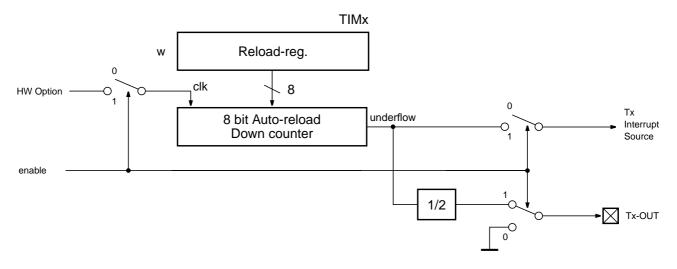

| 91              | 14.2.               | Timer T1 to T4                             |

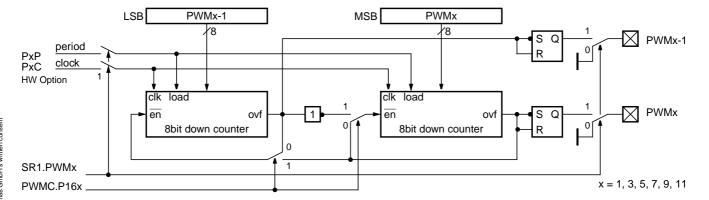

| 93              | 15.                 | Pulse Width Modulator (PWM)                |

| 93              | 15.1.               | Principle of Operation                     |

| 94              | 15.2.               | Registers                                  |

| 97              | 16.                 | Pulse Frequency Modulator (PFM)            |

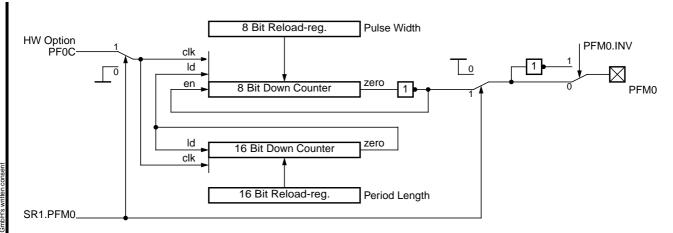

| 97              | 16.1.               | Principle of Operation                     |

| 98              | 16.2.               | Registers                                  |

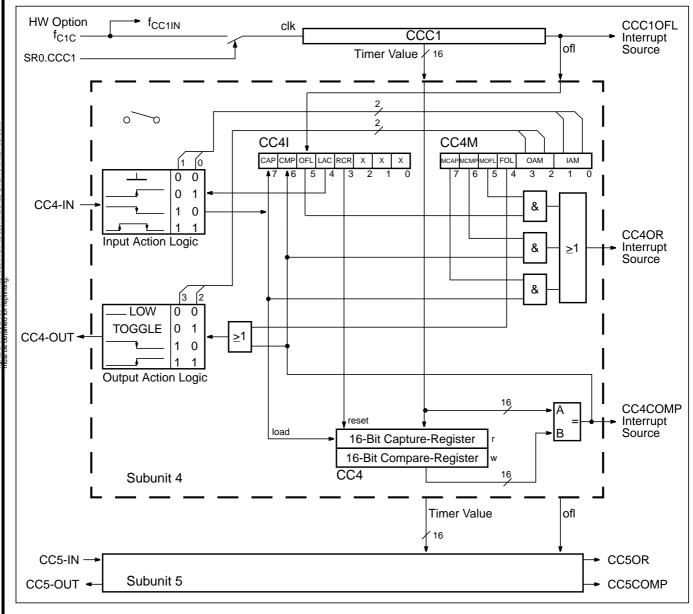

| 99              | 17.                 | Capture Compare Module (CAPCOM)            |

| 101             | 17.1.               | Principle of Operation                     |

| 103             | 17.2.               | Registers                                  |

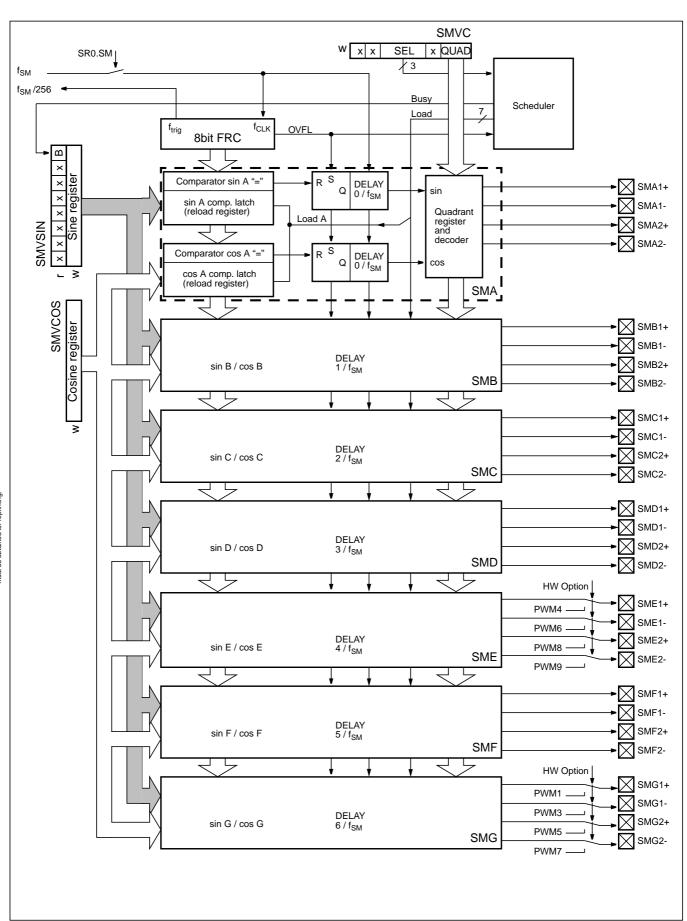

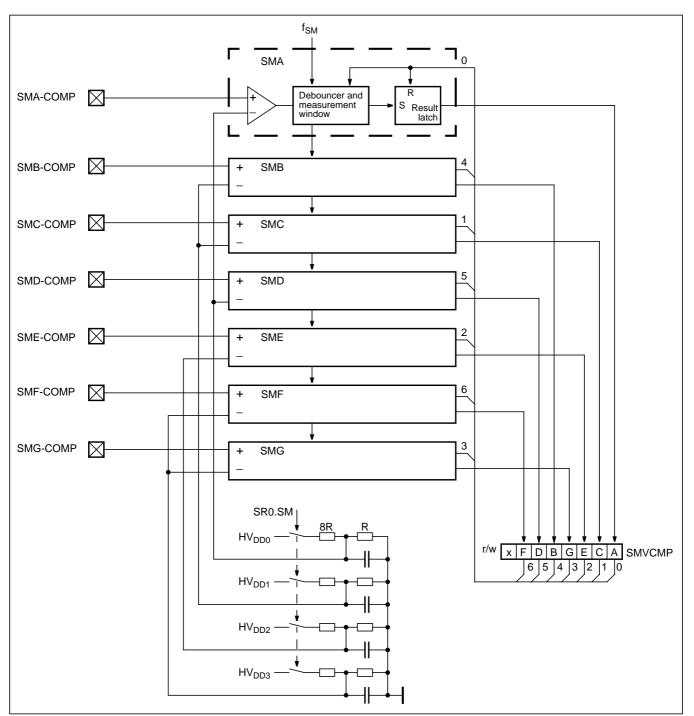

| 105             | 18.                 | Stepper Motor Module VDO (SMV)             |

| 105             | 18.1.               | Principle of Operation                     |

| 109             | 18.2.               | Registers                                  |

| 110             | 18.3.               | Timing                                     |

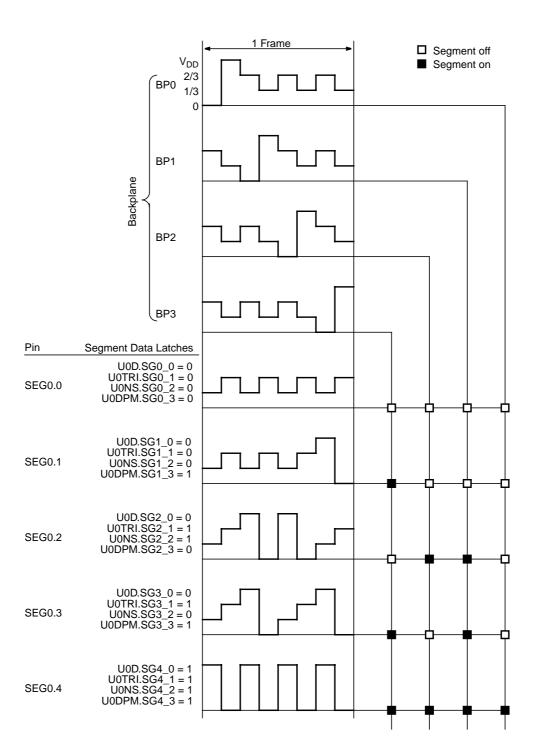

| 111             | 19.                 | LCD Module                                 |

| 111             | 19.1.               | Principle of Operation                     |

# **Contents**

| Contents                               |                                                  |                                                                                                          |

|----------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Page                                   | Section                                          | Title                                                                                                    |

| 114<br>114                             | 19.2.<br>19.3.                                   | Registers Application Hints for Cascading LCD Modules                                                    |

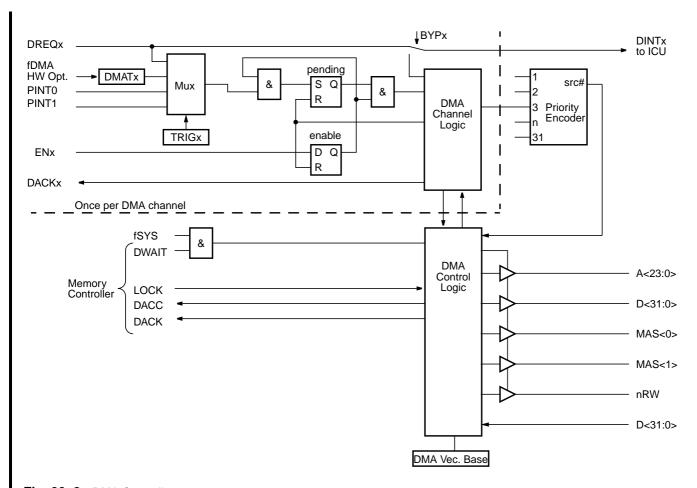

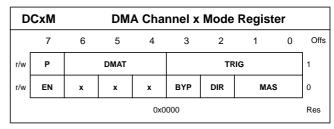

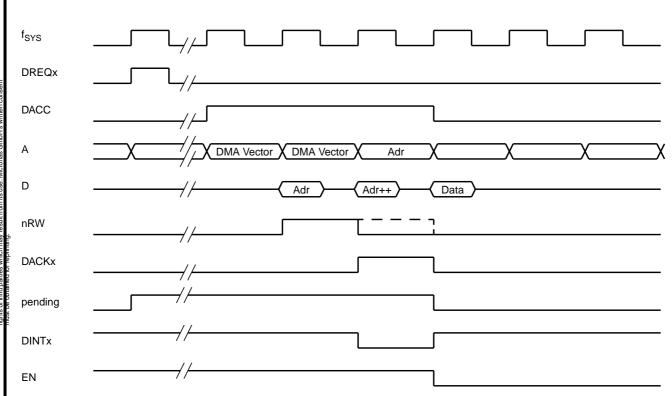

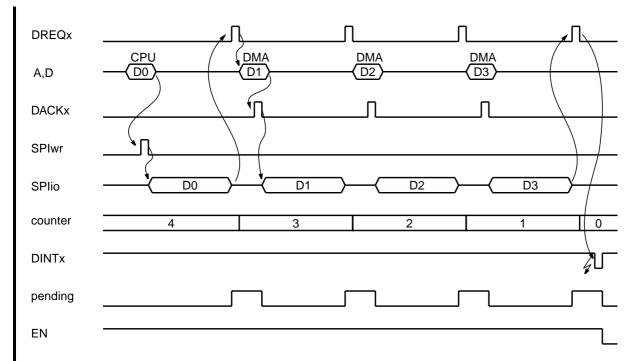

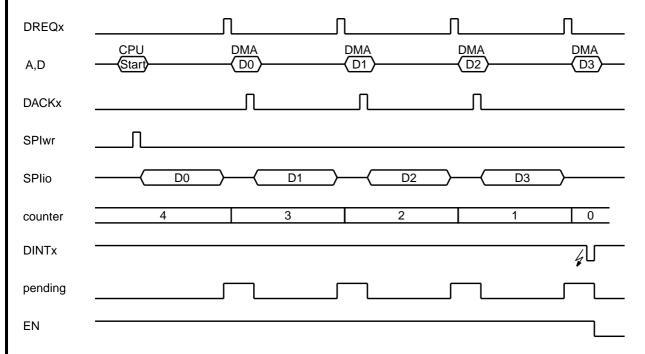

| <b>115</b> 115 117 118 119             | 20.<br>20.1.<br>20.2.<br>20.3.<br>20.4.          | DMA Controller Functions Registers Principle of Operation Timing Diagrams                                |

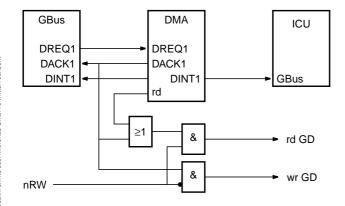

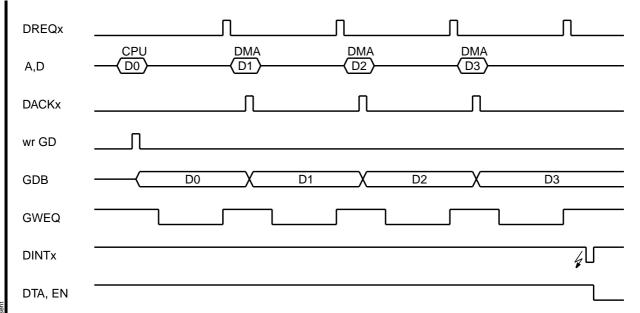

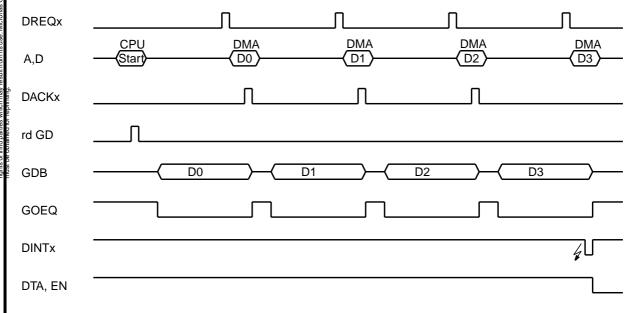

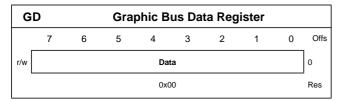

| <b>123</b> 123 123 124                 | <b>21.</b> 21.1. 21.2. 21.3.                     | Graphic Bus Interface Functions GB Registers Principle of Operation                                      |

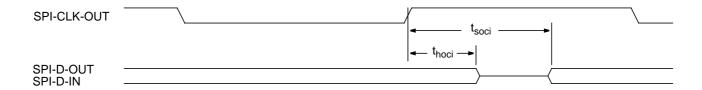

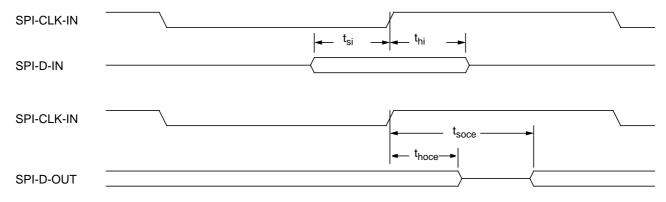

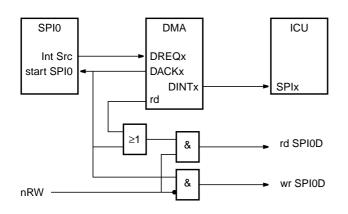

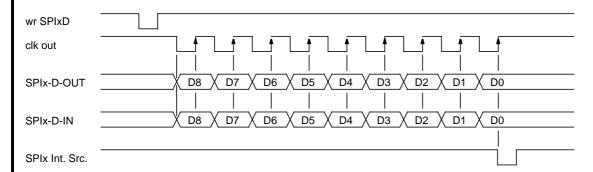

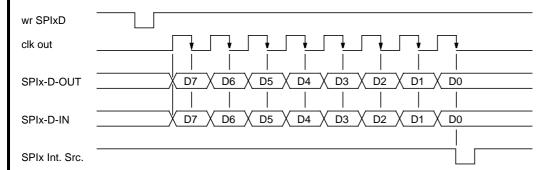

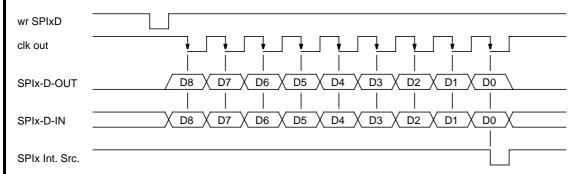

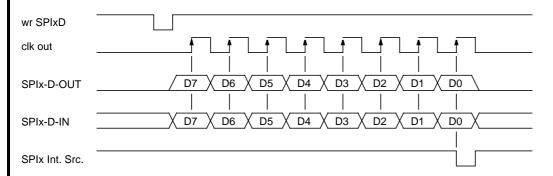

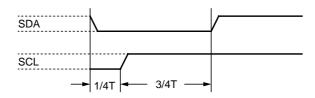

| <b>127</b><br>128<br>129<br>130        | 22.<br>22.1.<br>22.2.<br>22.3.                   | Serial Synchronous Peripheral Interface (SPI) Principle of Operation Registers Timing                    |

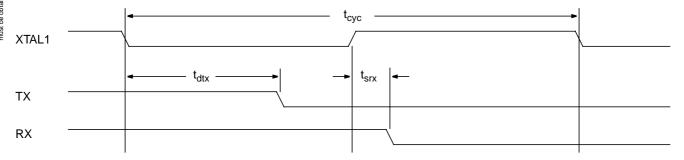

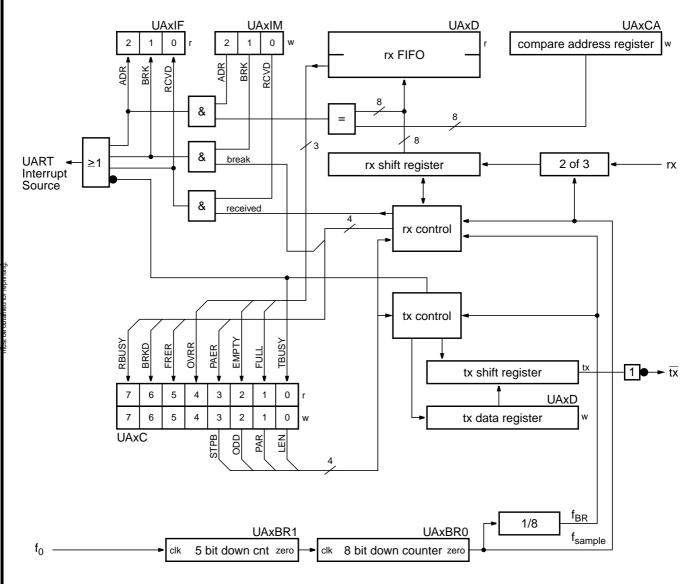

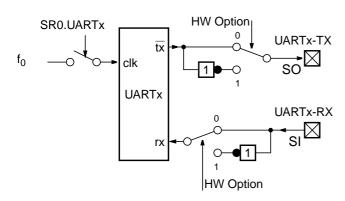

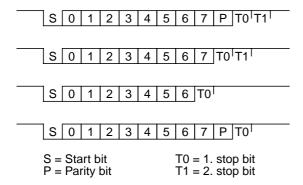

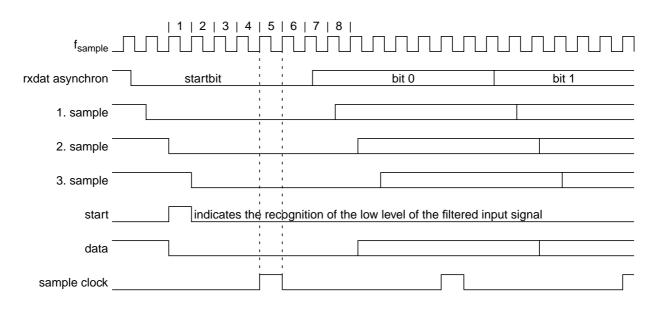

| <b>131</b> 132 134 136                 | 23. 23.1. 23.2. 23.3.                            | Universal Asynchronous Receiver Transmitter (UART) Principle of Operation Timing Registers               |

| <b>139</b><br>140<br>141               | <b>24.</b><br>24.1.<br>24.2.                     | I2C-Bus Master Interface Principle of Operation Registers                                                |

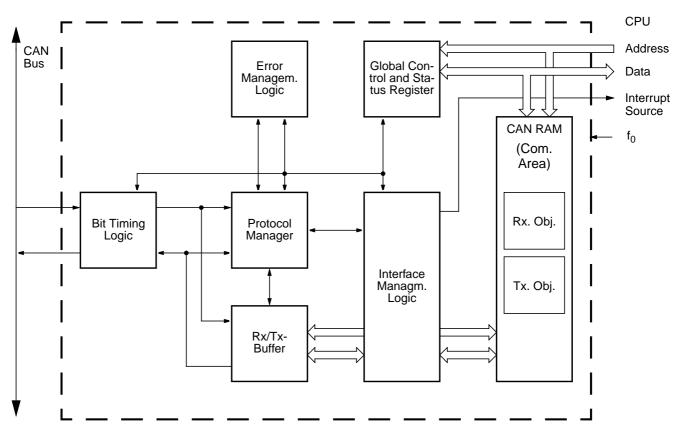

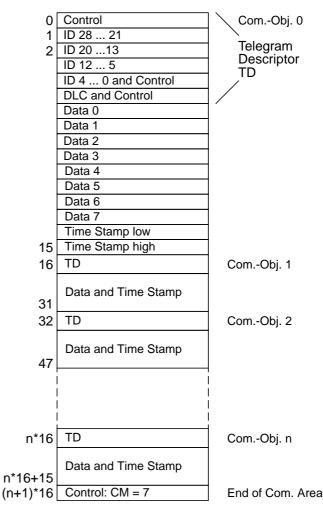

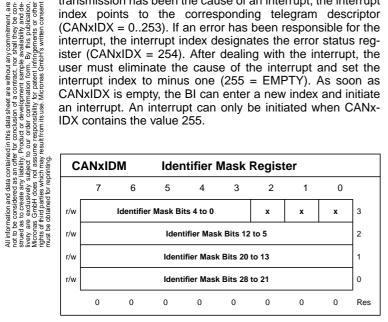

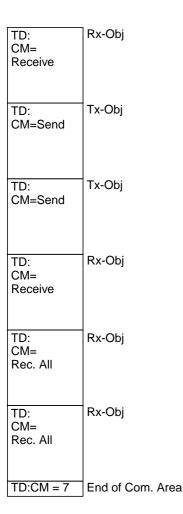

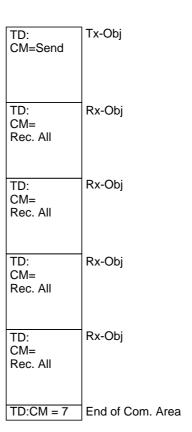

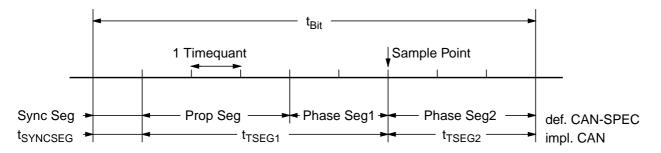

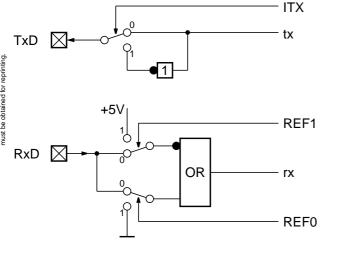

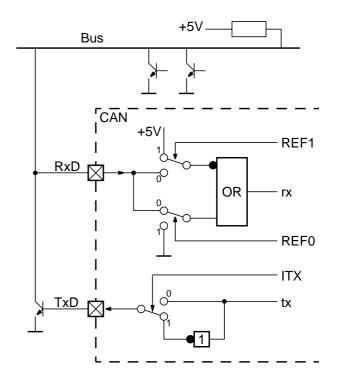

| 143<br>144<br>144<br>150<br>155<br>157 | 25.<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5. | CAN Manual Abbreviations Functional Description Application Notes Bit Timing Logic Bus Coupling          |

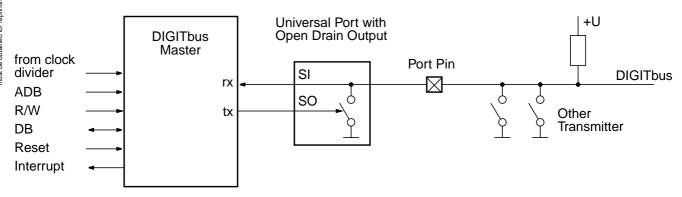

| 159<br>159<br>159<br>160<br>161        | <b>26.</b> 26.1. 26.2. 26.3. 26.4.               | DIGITbus System Description Bus Signal and Protocol Other Features Standard Functions Optional Functions |

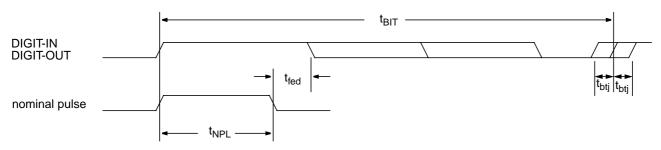

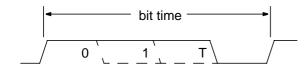

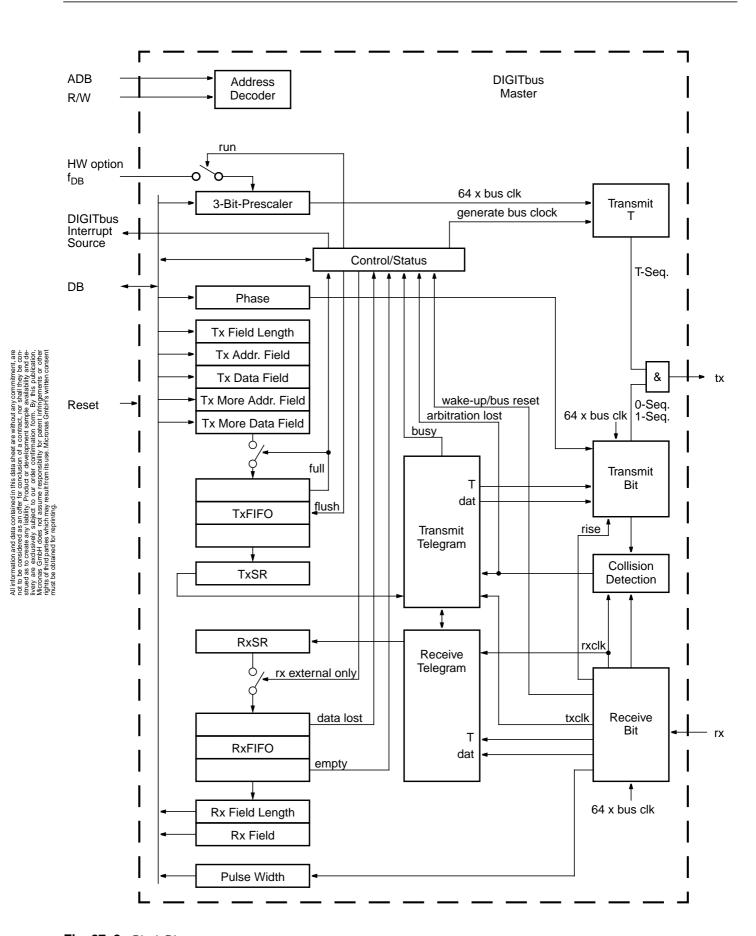

| 163<br>163<br>164<br>166<br>169<br>172 | 27.<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5. | DIGITbus Master Module Context Functional Description Registers Principle of Operation Timings           |

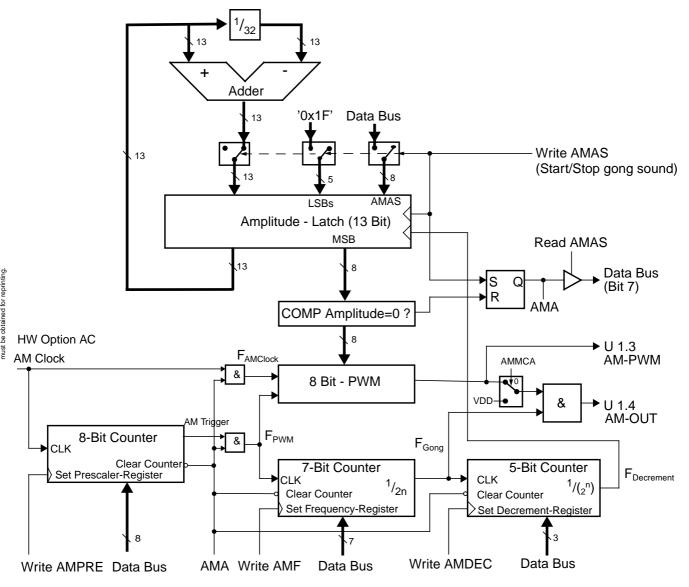

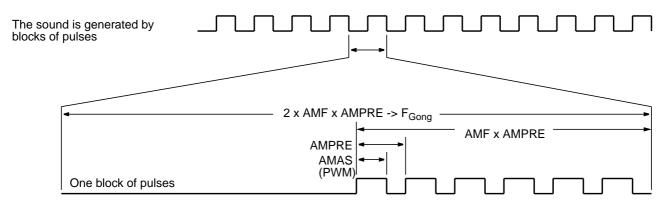

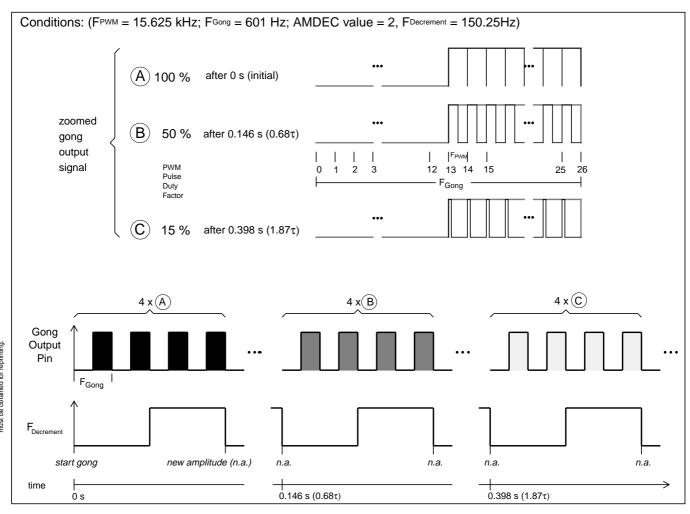

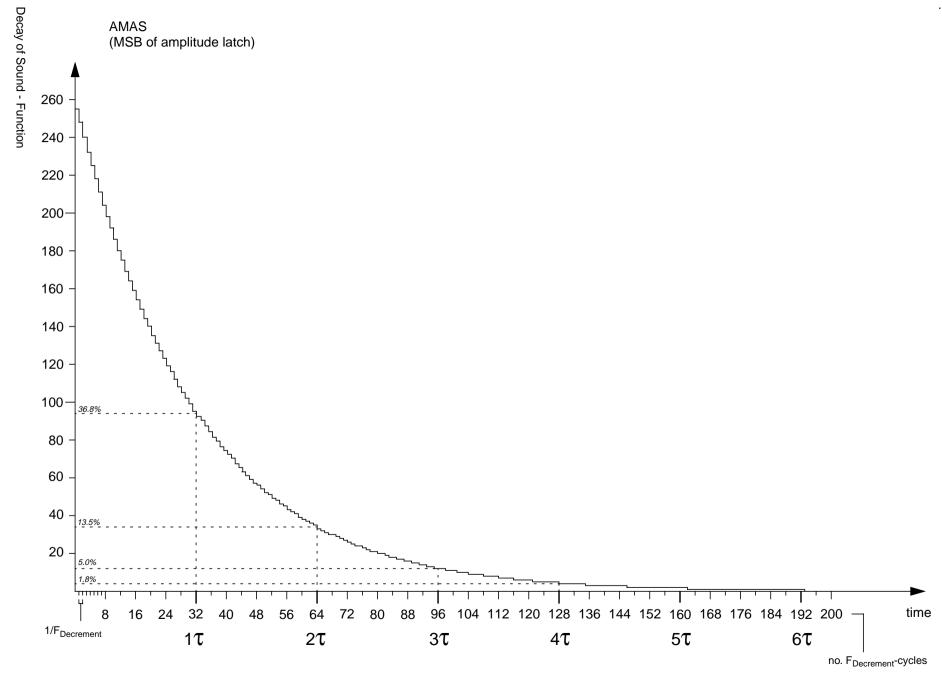

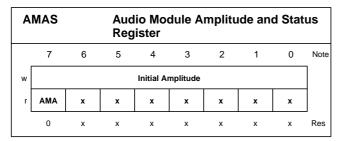

| <b>173</b><br>174                      | <b>28.</b><br>28.1.                              | Audio Module (AM) Functional Description                                                                 |

Influormation and data contained in this data sheet are without any commitment, are not to be considered as an offer for conclusion of a contract, nor shall they be contract to stocked as any liability. Froods or development sample availability and delivery are exclassively subject to our order confirmation form. By this publication, fluctorias GmbH does not assume responsibility for parent infinityments or other rights of third parties which may result from its use. Microrias GmbH does not assume responsibility for parent infinityments or other rights of third parties which may result from its use. Microrias GmbH's written consent

# Contents

| Page                            | Section                      | Title                                                                                                                              |

|---------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 178                             | 28.2.                        | Registers                                                                                                                          |

| <b>179</b><br>179<br>180<br>181 | <b>29.</b> 29.1. 29.2. 29.3. | Hardware Options Functional Description Listing of Dedicated Addresses of the Hardware Options Field HW Options Registers and Code |

| <b>187</b><br>187<br>192        | <b>30.</b> 30.1. 30.2.       | Register Cross Reference Table<br>8 Bit I/O Region<br>32 Bit I/O Region                                                            |

| 193                             | 31.                          | Register Quick Reference                                                                                                           |

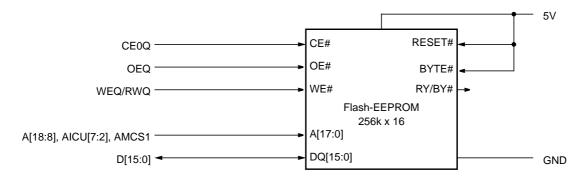

| <b>217</b><br>217<br>220        | <b>32.</b> 32.1. 32.2.       | Control Register and Memory Interface<br>Control Register CR<br>External Memory Interface                                          |

| 226                             | 33.                          | Data Sheet History                                                                                                                 |

In this healoff studies and institute of miss sale are are without any built mill refuse are more mill refuse as considered and sale although the contract the scale built being a likely as a exclusively will being to our order confirmation from By this obligation of the confirmation from By this obligation will decrease and assume responsibility for patient infinitements or other citypts of third panies which may result from its use. Microrias GmbH does not exceed a particular to the consent mill although the consent must be ablational for retaining.

1

**Contents**

Page Section Title

All information and data contained in this data sheer are without any commitment, are not to be considered as an offer for conclusion of a contract, nor shall they be constructed as to create any failing. Product or development sample availability and de-livery are exclassively subject to our order confirmation form. By this publication, Microrous Gribth does not assume responsibility for patent infringements or other dipties of this production with the confirmation from the confirmation forms of the production of the dipties of the production of the confirmation is the confirmation of the confirmation in the confirmation of the confirmat

# 1. Introduction

The device is a microcontroller for use in automotive applications. The on-chip CPU is ARM® processor ARM7TDMI with 32bit data and address bus, which supports Thumb format instructions.

The chip contains timer/counters, interrupt controller, multi channel AD converter, stepper motor and LCD driver, CAN interfaces and PWM outputs and a crystal clock multiplying PLI

# 1.1. Features

Table 1-1: CDC32xxG Family Feature List

This Device:

| Item                                         | CDC3205G-A<br>EMU                                                                                                          | CDC3205G-B<br>EMU                                                                                                          | CDC3207G-B<br>MCM-Flash                                                               | Example<br>Mask ROM Part |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------|--|--|--|

| Core                                         | Core                                                                                                                       |                                                                                                                            |                                                                                       |                          |  |  |  |

| CPU                                          | 32bit ARM7TDMI <sup>™</sup>                                                                                                |                                                                                                                            |                                                                                       |                          |  |  |  |

| CPU operation modes                          | DEEP SLOW, SLOW                                                                                                            | /, FAST and PLL                                                                                                            |                                                                                       |                          |  |  |  |

| CPU clock multiplication                     | PLL delivering up<br>to 24MHz                                                                                              |                                                                                                                            |                                                                                       |                          |  |  |  |

| EMI Reduction Mode                           | -                                                                                                                          | selectable in PLL mo                                                                                                       | ode                                                                                   |                          |  |  |  |

| Quartz oscillator                            | 4 to 5MHz                                                                                                                  |                                                                                                                            |                                                                                       |                          |  |  |  |

| RAM, 32bit wide                              | 16kByte                                                                                                                    | 32kByte                                                                                                                    | 32kByte                                                                               | 12kByte                  |  |  |  |

| ROM                                          | ROMless, Flash<br>Port for connection<br>of external program<br>storage with up to<br>16Mbyte, internal<br>4KByte Boot ROM | ROMless, Flash<br>Port for connection<br>of external program<br>storage with up to<br>16Mbyte, internal<br>8KByte Boot ROM | 512kByte Flash<br>EEPROM, top boot<br>configuration, inter-<br>nal 8KByte Boot<br>ROM | 256kByte ROM             |  |  |  |

| Digital Watchdog                             | ·                                                                                                                          |                                                                                                                            |                                                                                       |                          |  |  |  |

| Central Clock Divider                        | V                                                                                                                          |                                                                                                                            |                                                                                       |                          |  |  |  |

| Interrupt Controller expanding IRQ           | 40 inputs,16 priority levels  32 inputs,16 priority levels                                                                 |                                                                                                                            |                                                                                       |                          |  |  |  |

| Port Interrupts including Slope<br>Selection | 6 inputs                                                                                                                   |                                                                                                                            |                                                                                       |                          |  |  |  |

| Boot System                                  | allows in-system downloading of external code to Flash memory via JTAG                                                     |                                                                                                                            |                                                                                       |                          |  |  |  |

All information and data contained in this data sheet are without any commitment, are not to be considered as an after for conclusion of a confirmation visit they be constituted as to create any liability. Product or development sample availability and delivery are exclusively subject to our order confirmation form. By this publication, Microras Cinhal does not assume responsibility to patient infringements or other rights of third parea which may result from its use. Microras CinhAl swritten consent mass or course.

I

Table 1-1: CDC32xxG Family Feature List

# This Device:

|                                                                                        |                                                                                        | Tills Device.                                                                                                             |                                                                |                                             |                                                                      |  |  |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------|--|--|

|                                                                                        | Item                                                                                   | CDC3205G-A<br>EMU                                                                                                         | CDC3205G-B<br>EMU                                              | CDC3207G-B<br>MCM-Flash                     | Example<br>Mask ROM Part                                             |  |  |

|                                                                                        | Analog                                                                                 |                                                                                                                           |                                                                |                                             |                                                                      |  |  |

|                                                                                        | Reset/Alarm                                                                            | Combined Input for I                                                                                                      | Combined Input for Regulator Input Supervision                 |                                             |                                                                      |  |  |

|                                                                                        | Clock and Supply Supervision                                                           | V                                                                                                                         |                                                                |                                             |                                                                      |  |  |

|                                                                                        | 10 Bit ADC, charge balance type                                                        | 16 channels (6 selectable as digital input)                                                                               | selectable as digi-                                            |                                             |                                                                      |  |  |

|                                                                                        | ADC Reference                                                                          | VREF Pin                                                                                                                  | VREF Pin, P1.0 Pin, selectable                                 | P1.1 Pin or VREFINT                         | Internal Bandgap                                                     |  |  |

| Comparators  P06COMP with 1/2 AVDD reference, WAITCOMP with Internal Bandgap reference |                                                                                        |                                                                                                                           |                                                                | ce                                          |                                                                      |  |  |

|                                                                                        | LCD                                                                                    | Internal processing                                                                                                       | of all analog voltages for                                     | or the LCD driver                           |                                                                      |  |  |

|                                                                                        | Communication                                                                          |                                                                                                                           |                                                                |                                             |                                                                      |  |  |

|                                                                                        | DMA                                                                                    | 1 DMA Channel for servicing a port or an SPI  3 DMA Channels, one each for servicing the Graphics Bus face, SPI0 and SPI1 |                                                                |                                             |                                                                      |  |  |

|                                                                                        | UART                                                                                   | 2: UART0 and UART                                                                                                         | 1                                                              |                                             |                                                                      |  |  |

|                                                                                        | Synchronous Serial Peripheral<br>Interfaces                                            | 2: SPI0 and SPI1                                                                                                          |                                                                |                                             |                                                                      |  |  |

|                                                                                        | Full CAN modules V2.0B                                                                 | 3: CAN0, CAN1<br>and CAN2 with<br>256bytes of object<br>RAM each<br>(LCAN0009)                                            | of object RAM each (LCAN0009) with object                      |                                             | 2: CAN0 and CAN<br>with 512bytes of<br>object RAM each<br>(LCAN0009) |  |  |

| ľ                                                                                      | DIGITbus                                                                               | 1 master module                                                                                                           |                                                                |                                             |                                                                      |  |  |

|                                                                                        | I <sup>2</sup> C                                                                       | 2 master modules: I                                                                                                       | 2C0 and I2C1                                                   |                                             |                                                                      |  |  |

|                                                                                        | Input & Output                                                                         |                                                                                                                           |                                                                |                                             |                                                                      |  |  |

|                                                                                        | Universal Ports selectable as 4:1 mux LCD Segment/Backplane lines or Digital I/O Ports | up to 54 I/O or 50<br>LCD segment lines<br>(=200 segments)                                                                | up to 52 I/O or 48 LO individually configura                   | CD segment lines (=19<br>able as I/O or LCD | 2 segments),                                                         |  |  |

|                                                                                        | Universal Port Slew Rate                                                               | Mask selectable                                                                                                           | SW selectable                                                  |                                             |                                                                      |  |  |

|                                                                                        | Stepper Motor Control Modules with high current ports                                  | 7 Modules,<br>32 dl/dt controlled ports                                                                                   |                                                                |                                             |                                                                      |  |  |

|                                                                                        | PWM Modules, each configurable<br>as two 8Bit PWMs or one 16Bit<br>PWM                 | 6 Modules: PWM0/1                                                                                                         | 6 Modules: PWM0/1, PWM2/3, PWM4/5, PWM6/7, PWM8/9 and PWM10/11 |                                             |                                                                      |  |  |

|                                                                                        | Phase-Frequency Modulator                                                              | -                                                                                                                         | 1: PFM0                                                        |                                             |                                                                      |  |  |

|                                                                                        | Audio Module with auto-decay                                                           | V                                                                                                                         |                                                                |                                             |                                                                      |  |  |

|                                                                                        | SW selectable Clock outputs                                                            | 2                                                                                                                         |                                                                |                                             |                                                                      |  |  |

| _                                                                                      |                                                                                        |                                                                                                                           |                                                                |                                             |                                                                      |  |  |

All information and data contained in this data sheat are without any commitment, are not to be considered as an offer for conclusion of a contract, nor shall they be considered as any liability. Product or development sample availability and development sample availability and development sample availability and development sample availability and development as exclusively subject to our order confirmation from. By this publication, wild-norm desponsibility for patient infringements or other tights of third parties which may result from its use. Micronas GmbH's written consent

Table 1-1: CDC32xxG Family Feature List

#### This Device:

| Item                                                     | CDC3205G-A<br>EMU CDC3205G-B<br>EMU                                |             | CDC3207G-B<br>MCM-Flash       | Example<br>Mask ROM Part                        |  |

|----------------------------------------------------------|--------------------------------------------------------------------|-------------|-------------------------------|-------------------------------------------------|--|

| Timers & Counters                                        |                                                                    |             |                               |                                                 |  |

| 16bit free running counters with Capture/Compare modules | CCC0 with 4 CAPC0                                                  |             |                               |                                                 |  |

| 16bit timers                                             | 1: T0                                                              |             |                               |                                                 |  |

| 8bit timers                                              | 4: T1, T2, T3 and T4                                               | ļ           |                               |                                                 |  |

| Miscellaneous                                            |                                                                    |             |                               |                                                 |  |

| Scalable layout in CAN, RAM and ROM                      | -                                                                  |             | V                             | ~                                               |  |

| Various randomly selectable HW options                   | Most options SW programmable, copy from age during system start-up |             | n user program stor-          | Mask programmed according to user specification |  |

| JTAG test interface                                      | V                                                                  |             | allows Flash pro-<br>gramming | <b>'</b>                                        |  |

| On Chip Debug Aids                                       | Embedded Trace Mo                                                  | odule, JTAG | JTAG                          |                                                 |  |

| Core Bond-Out                                            | ore Bond-Out                                                       |             | -                             |                                                 |  |

| Supply Voltage                                           | 4.5 to 5.5V 3.5 to 5.5V (limited I                                 |             | I/O performance below 4.5V)   |                                                 |  |

| Ambient Temperature Range                                | -40 to +85C                                                        |             |                               |                                                 |  |

| Package                                                  |                                                                    |             |                               |                                                 |  |

| Туре                                                     | Ceramic 257PGA                                                     |             | Plastic 128QFP<br>0.5mm pitch |                                                 |  |

| Bonded Pins                                              | 256                                                                |             | 128                           |                                                 |  |

$\mathsf{ARM}^{\circledR}$  and  $\mathsf{Thumb}^{\circledR}$  are the registered trademarks of ARM Limited. ARM7TDMITM is the trademark of ARM Limited.

# 1.2. Abbreviations

| AM      | Audio Module                            |

|---------|-----------------------------------------|

| CAN     | Controller Area Network Module          |

| CAPCOM  | Capture/Compare Module                  |

| CCC     | Capture/Compare Counter                 |

| CPU     | Central Processing Unit                 |

| DMA     | Direct Memory Access Module             |

| ERM     | EMI Reduction Mode                      |

| ETM     | Embedded Trace Module                   |

| ICU     | Interrupt Controller                    |

| I2C     | I <sup>2</sup> C Interface Module       |

| LCD     | Liquid Crystal Display Module           |

| P06COMP | P0.6 Alarm Comparator                   |

| PINT    | Port Interrupt Module                   |

| PWM     | 8Bit Pulse Width Modulator Module       |

| SM      | Stepper Motor Control Module            |

| SPI     | Serial Synchronous Peripheral Interface |

| T       | Timer                                   |

UART Universal Asynchronous Receiver Transmitter WAITCOMP Wait Comparator

All information and dates contained in this date sheet are without any commitment are not to be considered as an office for conclusion of a contained, not shell they be converted as a contained as a contained and a shell they contained as to create any liability. Prototod of development sample availability and definity are so closely as liability and conformation from. By this bulbarion, which are a conformation from the problemation, and the shell are a conformation of the conformation from the problemation, and the conformation of the con

I

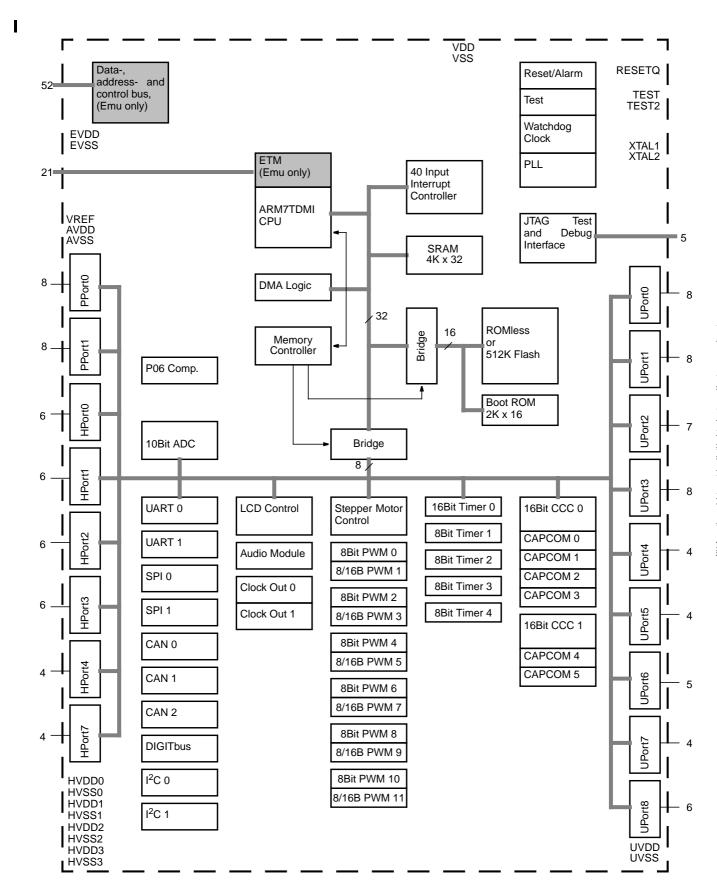

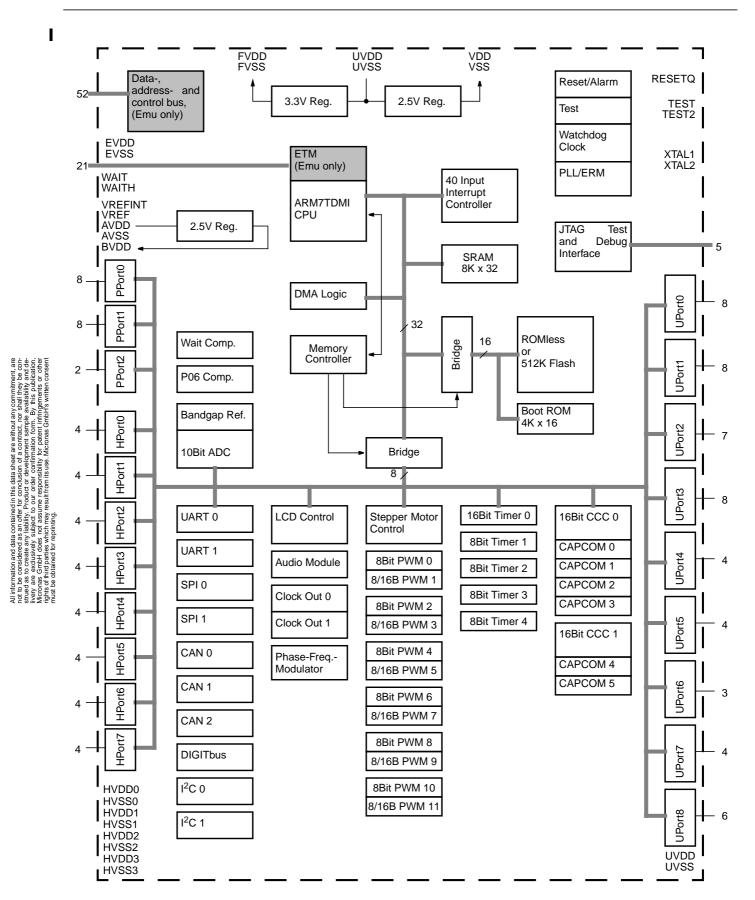

# 1.3. Block Diagrams

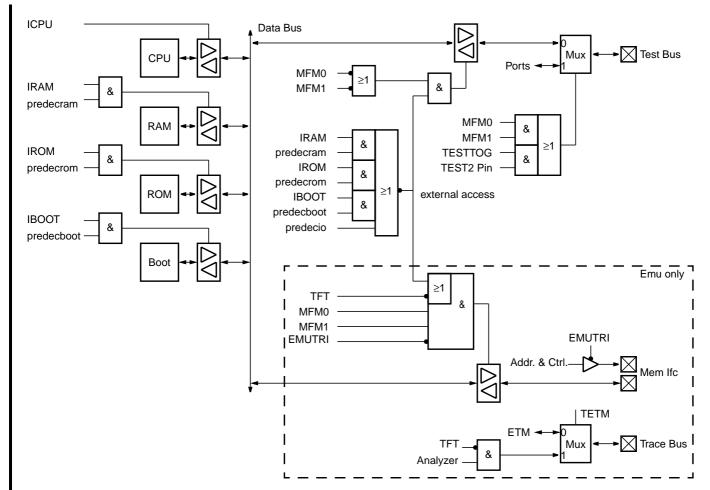

Fig. 1–1: CDC3205G-A block diagram

All information and data contained in this data sheet are without any commitment, are not be considered as an offer for conclusion of a contract, nor shall they be considered any latellity. Product of development sample availability and delivery are acktalswelly subject to our order confirmation form. By his publication, Microras Gribh does not assume responsibility for patent infinigements or other fights of third patients which may result thom its use. Microras Gribb! swritten consent must be obtained for reprinting.

Fig. 1-2: CDC3205G-B block diagram

All information and data contained in this data sheet are without any commitment, are not to be considered as an offer for conclusion of a contract, nor shall they be considered any lability. Product or development sample availability and development assume responsibility for patent infringements or other rights of third parties which may result from its use. Microras GmbH's written consent

# 2. Packages and Pins

# 2.1. Pin Assignment

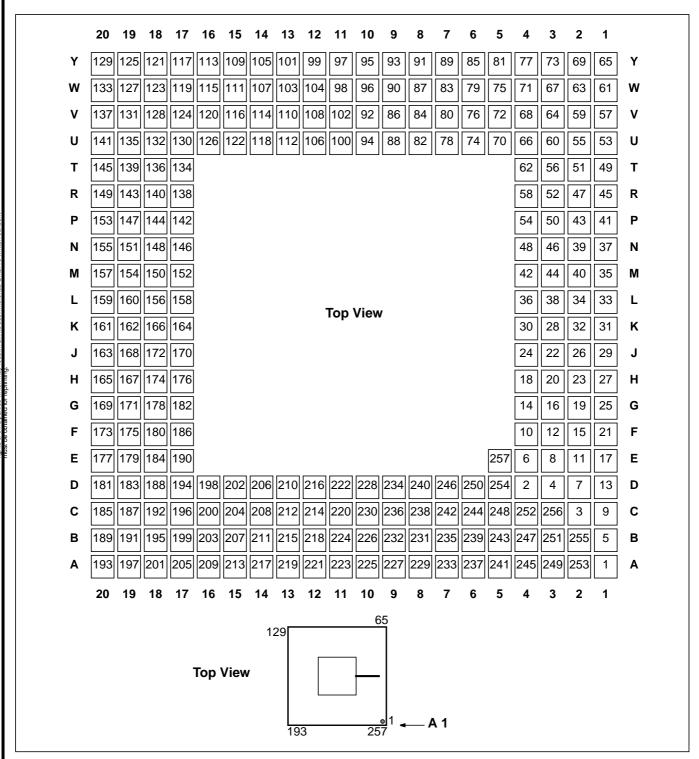

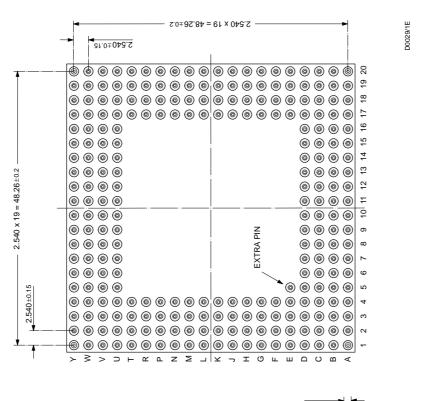

Fig. 2-1: Pin Map of CPGA257 Package

All information and data contained in this data sheet are without any commitment, are not to be considered as an orfer for conclusion of a contract, nor shall they be constructed as to create any liability. Product or development sample availability and delivery are exclusively subject to our order confirmation form. By this publication, Microras GmbH does not assume responsibility for patent infingaments or other invents of this order or assume responsibility for patent infingaments or other invents of the invents of the invents of such and expensibility to patent infingaments or other invents of the invents of the invents of such resulting in the consent infinite orders or the invents of the invents

Table 2-1: Pin Assignment for CPGA257 Package

| Pin      | Co-  | Pin Functions |              |                |         |  |

|----------|------|---------------|--------------|----------------|---------|--|

| No.      | ord. | Basic         | Port         | Port           | LCD     |  |

|          |      | Function      | Special In   | Special Out    | Mode    |  |

| 1        | A1   | U5.3/GD3      | CC4-IN       | CC4-OUT        | SEG5.3  |  |

| 2        | D4   | U5.2/GD2      | SDA1         | SDA1           | SEG5.2  |  |

| 3        | C2   | U5.1/GD1      | SCL1         | SCL1           | SEG5.1  |  |

| 4        | D3   | U5.0/GD0      |              | PFM0           | SEG5.0  |  |

| 5        | B1   | U2.1          | SDA0/CAN0-RX | SDA0           | SEG2.1  |  |

| 6        | E4   | U2.0          | SCL0         | SCL0/CAN0-TX   | SEG2.0  |  |

| 7        | D2   | U1.7          | PINT0        | PFM0           | SEG1.7  |  |

| 8        | E3   | U1.6          | PINT1        | CO0/INTRES     | SEG1.6  |  |

| 9        | C1   | U1.5          | PINT2        | CO0Q/CO1       | SEG1.5  |  |

| 10       | F4   | TEST          | 1 11412      | 0000/001       | OLO 1.5 |  |

| 11       | E2   | RESETQ/A      | LADMO        |                |         |  |

| 12       | F3   | XTAL2         | ALARIVIQ     |                |         |  |

|          | _    | 1             |              |                |         |  |

| 13       | D1   | XTAL1         |              |                |         |  |

| 14       | G4   | VSS           |              |                |         |  |

| 15       | F2   | VDD           |              |                |         |  |

| 16       | G3   | U1.4          |              | ITSTOUT/AM-OUT | SEG1.4  |  |

| 17       | E1   | U1.3          |              | MTO/AM-PWM     | SEG1.3  |  |

| 18       | H4   | U1.2          | MTI/ITSTIN   | T0-OUT/INTRES  | SEG1.2  |  |

| 19       | G2   | U1.1          |              | T1-OUT         | SEG1.1  |  |

| 20       | НЗ   | U1.0          |              | T2-OUT         | SEG1.0  |  |

| 21       | F1   | U0.7          |              | T3-OUT         | SEG0.7  |  |

| 22       | J3   | U0.6          | CC3-IN       | T4-OUT/CC3-OUT | SEG0.6  |  |

| 23       | H2   | U0.5          | PINT4        | CC3-OUT        | SEG0.5  |  |

| 24       | J4   | U0.4          | PINT5        | CO1            | SEG0.4  |  |

| 25       | G1   | U0.3          | 1 11413      | PWM0           | SEG0.3  |  |

| 26<br>26 | J2   | U0.2          |              | PWM1           | SEG0.2  |  |

|          | -    |               |              |                |         |  |

| 27       | H1   | U0.1          |              | PWM2           | SEG0.1  |  |

| 28       | K3   | U0.0          |              | PWM3           | SEG0.0  |  |

| 29       | J1   | D31           |              |                |         |  |

| 30       | K4   | D30           |              |                |         |  |

| 31       | K1   | D29           |              |                |         |  |

| 32       | K2   | D28           |              |                |         |  |

| 33       | L1   | D27           |              |                |         |  |

| 34       | L2   | D26           |              |                |         |  |

| 35       | M1   | D25           |              |                |         |  |

| 36       | L4   | EVDD8         |              |                |         |  |

| 37       | N1   | EVSS8         |              |                |         |  |

| 38       | L3   | D24           |              |                |         |  |

| 39       | N2   | D23           |              |                |         |  |

| 40       | M2   | D22           |              |                |         |  |

| 41       | P1   | D21           |              |                |         |  |

|          | M4   |               |              |                |         |  |

| 42       |      | D20           |              |                |         |  |

| 43       | P2   | D19           |              |                |         |  |

| 44       | M3   | D18           |              |                |         |  |

| 45       | R1   | D17           |              |                |         |  |

| 46       | N3   | D16           |              |                |         |  |

| 47       | R2   | D15           |              |                |         |  |

| 48       | N4   | D7            |              |                |         |  |

| 49       | T1   | D14           |              |                |         |  |

| 50       | P3   | EVDD7         |              |                |         |  |

| 51       | T2   | EVSS7         |              |                |         |  |

| 52       | R3   | D6            |              |                |         |  |

| 53       | U1   | D13           |              |                |         |  |

| 54       | P4   | D5            |              |                |         |  |

| 55       | U2   | D12           |              |                |         |  |

|          | _    |               |              |                |         |  |

| 56       | T3   | D4            |              |                |         |  |

| 57       | V1   | D11           |              |                |         |  |

| 58       | R4   | D3            |              |                |         |  |

| 59       | V2   | D10           |              |                |         |  |

| 60       | U3   | D2            |              |                |         |  |

| 61       | W1   | D9            |              |                |         |  |

| 62       | T4   | D1            |              |                |         |  |

| 63       | W2   | D8            |              |                |         |  |

| 64       | V3   | EVDD6         |              |                |         |  |

| 63<br>64 |      | _             |              |                |         |  |

Table 2-1: Pin Assignment for CPGA257 Package

| Pin        | Co-        | Pin Functions      |              |                                       |      |  |  |

|------------|------------|--------------------|--------------|---------------------------------------|------|--|--|

| No.        | ord.       | Basic              | Port         | Port                                  | LCD  |  |  |

|            |            | Function           | Special In   | Special Out                           | Mode |  |  |

| 65         | Y1         | EVSS6              | 1            |                                       |      |  |  |

| 66         | U4         | D0                 |              |                                       |      |  |  |

| 67         | W3         | OEQ                |              |                                       |      |  |  |

| 68         | V4         | CE0Q               |              |                                       |      |  |  |

| 69         | Y2         | BWQ3               |              |                                       |      |  |  |

| 70         | U5         | BWQ2               |              |                                       |      |  |  |

| 71         | W4         | BWQ1               |              |                                       |      |  |  |

| 72         | V5         | BWQ0               |              |                                       |      |  |  |

| 73         | Y3         | EMUTRI             |              |                                       |      |  |  |

| 74         | U6<br>W5   | ABORT              |              |                                       |      |  |  |

| 75<br>76   | VV5<br>V6  | EXTERN0<br>EXTERN1 |              |                                       |      |  |  |

| 76<br>77   | Y4         | H7.3               | 1            | SME1+/PWM4                            |      |  |  |

| 78         | U7         | H7.2               |              | SME1-/PWM6                            |      |  |  |

| 79         | W6         | H7.1               |              | SME2+/PWM8                            |      |  |  |

| 80         | V7         | H7.0               | SME-COMP     | SME2-/PWM9                            |      |  |  |

| 81         | Y5         | HVDD2              | 0            | 027. *******                          |      |  |  |

| 82         | U8         | HVSS2              |              |                                       |      |  |  |

| 83         | W7         | H6.3               |              | PWM8                                  |      |  |  |

| 84         | V8         | H6.2               |              | PWM9                                  |      |  |  |

| 85         | Y6         | H6.1               |              | PWM10                                 |      |  |  |

| 86         | V9         | H6.0               |              | PWM11                                 |      |  |  |

| 87         | W8         | H5.3               |              | SMD1+                                 |      |  |  |

| 88         | U9         | H5.2               |              | SMD1-                                 |      |  |  |

| 89         | Y7         | HVDD0              | •            |                                       |      |  |  |

| 90         | W9         | HVSS0              |              |                                       |      |  |  |

| 91         | Y8         | H5.1               |              | SMD2+                                 |      |  |  |

| 92         | V10        | H5.0               | SMD-COMP     | SMD2-                                 |      |  |  |

| 93         | Y9         | H4.3               |              | SMA1+                                 |      |  |  |

| 94         | U10<br>Y10 | H4.2<br>H4.1       |              | SMA1-<br>SMA2+                        |      |  |  |

| 95<br>96   | W10        | H4.1               | SMA-COMP     | SMA2+<br>SMA2-                        |      |  |  |

| 97         | Y11        | H3.3               | SIVIA-COIVIF | SMB1+                                 | _    |  |  |

| 98         | W11        | H3.2               |              | SMB1-                                 |      |  |  |

| 99         | Y12        | H3.1               |              | SMB2+                                 |      |  |  |

| 100        | U11        | H3.0               | SMB-COMP     | SMB2-                                 |      |  |  |

| 101        | Y13        | H2.3               |              | SMC1+                                 |      |  |  |

| 102        | V11        | H2.2               |              | SMC1-                                 |      |  |  |

| 103        | W13        | HVDD1              |              |                                       |      |  |  |

| 104        | W12        | HVSS1              |              |                                       |      |  |  |

| 105        | Y14        | H2.1               |              | SMC2+                                 |      |  |  |

| 106        | U12        | H2.0               | SMC-COMP     | SMC2-                                 |      |  |  |

| 107        | W14        | H1.3               |              | SMF1+                                 |      |  |  |

| 108        | V12        | H1.2               |              | SMF1-                                 |      |  |  |

| 109        | Y15        | H1.1               | OME COME     | SMF2+                                 |      |  |  |

| 110<br>111 | V13<br>W15 | H1.0<br>HVDD3      | SMF-COMP     | SMF2-                                 |      |  |  |

| 112        | U13        | HVSS3              |              |                                       |      |  |  |

| 113        | Y16        | H0.3               | 1            | SMG1+/PWM1                            | 1    |  |  |

| 114        | V14        | H0.2               |              | SMG1-/PWM3                            |      |  |  |

| 115        | W16        | H0.1               |              | SMG2+/PWM5                            |      |  |  |

| 116        | V15        | H0.0               | SMG-COMP     | SMG2-/PWM7                            |      |  |  |

| 117        | Y17        | nTRST              |              |                                       |      |  |  |

| 118        | U14        | ETDI               |              |                                       |      |  |  |

| 119        | W17        | ETMS               |              |                                       |      |  |  |

| 120        | V16        | ETCK               |              |                                       |      |  |  |

| 121        | Y18        | ETDO               |              |                                       |      |  |  |

| 122        | U15        | ABE                |              |                                       |      |  |  |

| 123        | W18        | CE1Q               |              |                                       |      |  |  |

| 124        | V17        | FBUSQ              |              | · · · · · · · · · · · · · · · · · · · |      |  |  |

| 125        | Y19        | AMCS1              |              |                                       |      |  |  |

| 126        | U16        | AICU2              |              |                                       |      |  |  |

| 127        | W19        | AICU3              |              |                                       |      |  |  |

| 128        | V18        | EVSS5              |              |                                       |      |  |  |

All information and data contained in this data sheet are without any commitment, are not to be considered as an offer for conclusion of a contract, nor shall they be construed as any liability. Froduct or development sample availability and development sample availability and development sample availability and development sample availability and development and they are exclusively subject to four order confirmation form. By this publication, Microbas GmbH does not assume responsibility for patent infinigements or other ights of third parties which may result from its use. Microbas GmbH swritten consent

3 DEC 01

Table 2-1: Pin Assignment for CPGA257 Package

| Pin                             | Co-                      | Pin Functions        |                 |              |                  |  |

|---------------------------------|--------------------------|----------------------|-----------------|--------------|------------------|--|

| No.                             | ord.                     | Dasic   Oit   I oit  |                 |              |                  |  |

| 100                             | 1/00                     | Function             | Special In      | Special Out  | Mode             |  |

| 129                             | Y20                      | EVDD5                |                 |              |                  |  |

| 130                             | U17                      | AICU4                |                 |              |                  |  |

| 131                             | V19                      | AICU5                |                 |              |                  |  |

| 132                             | U18                      | AICU6                |                 |              |                  |  |

| 133                             | W20                      | AICU7                |                 |              |                  |  |

| 134                             | T17                      | A8                   |                 |              |                  |  |

| 135                             | U19                      | A18                  |                 |              |                  |  |

| 136                             | T18                      | A19                  |                 |              |                  |  |

| 137                             | V20                      | EVDD4                |                 |              |                  |  |

| 138                             | R17                      | EVSS4                |                 |              |                  |  |

| 139                             | T19                      | WEQ/RW0              | 2               |              |                  |  |

| 140                             | R18                      | A9                   |                 |              |                  |  |

| 141                             | U20                      | A10                  |                 |              |                  |  |

| 142                             | P17                      | A11                  |                 |              |                  |  |

| 143                             | R19                      | A12                  |                 |              |                  |  |

| 144                             | P18                      | A13                  |                 |              |                  |  |

| 145                             | T20                      | A14                  |                 |              |                  |  |

| 146                             | N17                      | A15                  |                 |              |                  |  |

| 147                             | P19                      | EVDD3                |                 |              |                  |  |

| 148                             | N18                      | EVSS3                |                 |              |                  |  |

| 149                             | R20                      | A16                  |                 |              |                  |  |

| 150                             | M18                      | A17                  |                 |              |                  |  |

| 151                             | N19                      | A20                  |                 |              |                  |  |

| 152                             | M17                      | A21                  |                 |              |                  |  |

| 153                             | P20                      | A22                  |                 |              |                  |  |

| 154                             | M19                      | A23                  |                 |              |                  |  |

| 155                             | N20                      | AMCM21               |                 |              |                  |  |

| 156                             | L18                      | AMCM22               |                 |              |                  |  |

| 157                             | M20                      | EVDD2                |                 |              |                  |  |

| 158                             | L17                      | EVSS2                |                 |              |                  |  |

| 159                             | L20                      | AMCM23               |                 |              |                  |  |

| 160                             | L19                      | SEQ                  |                 |              |                  |  |

| 161                             | K20                      | nMREQ                |                 |              |                  |  |

| 162                             | K19                      | MAS0                 |                 |              |                  |  |

| 163                             | J20                      | MAS1                 |                 |              |                  |  |

| 164                             | K17                      | nRESET               |                 |              |                  |  |

| 165                             | H20                      | P1.7                 | PINT5           |              |                  |  |

| 166                             | K18                      | P1.6                 | PINT4           |              |                  |  |

| 167                             | H19                      | P1.5                 | PINT3           |              |                  |  |

| 168                             | J19                      | P1.4                 | PINT2           |              |                  |  |

| 169                             | G20                      | P1.3                 | PINT1           |              |                  |  |

| 170                             | J17                      | P1.2                 | PINT0           |              |                  |  |

| 171                             | G19                      | P1.1                 | VREF1           |              |                  |  |

| 172                             | J18                      | P1.0                 | VREF0           |              |                  |  |

| 173                             | F20                      | VREF                 |                 |              |                  |  |

| 174                             | H18                      | VREFINT              |                 |              |                  |  |

| 175                             | F19                      | AVDD                 |                 |              |                  |  |

| 176                             | H17                      | AVSS                 |                 |              |                  |  |

| 177                             | E20                      | BVDD                 |                 |              |                  |  |

| 178                             | G18                      | WAIT                 |                 |              |                  |  |

| 179                             | E19                      | WAITH                |                 |              |                  |  |

| 180                             | F18                      | P0.7                 |                 |              |                  |  |

| 181                             | D20                      | P0.6                 | P0.6 Comp.      |              |                  |  |

| 182                             | G17                      | P0.5                 | <u> </u>        |              |                  |  |

| 183                             | D19                      | P0.4                 | 1               |              |                  |  |

|                                 | E18                      | P0.3                 | †               |              |                  |  |

| 184                             | C20                      | P0.2                 | †               |              |                  |  |

| 184<br>185                      | 1020                     |                      | 1               |              |                  |  |

| 185                             | F17                      | P0.1                 |                 |              | I                |  |

| 185<br>186                      | F17                      | P0.1<br>P0.0         | CC4-IN          |              |                  |  |

| 185<br>186<br>187               |                          |                      | CC4-IN          |              |                  |  |

| 185<br>186<br>187<br>188        | F17<br>C19               | P0.0                 | CC4-IN          |              |                  |  |

| 185<br>186<br>187<br>188<br>189 | F17<br>C19<br>D18<br>B20 | P0.0<br>P2.1<br>P2.0 | CC4-IN          | GWEO         | SEG6 2           |  |

|                                 | F17<br>C19<br>D18        | P0.0<br>P2.1         | CC4-IN  CAN1-RX | GWEQ<br>GOEQ | SEG6.2<br>SEG6.1 |  |

Table 2-1: Pin Assignment for CPGA257 Package

| 194<br>195<br>196<br>197<br>198<br>199<br>200<br>201<br>202<br>203<br>204<br>205<br>206<br>207<br>208<br>209<br>211<br>212<br>213<br>214               | A20   D17   B18   C17   A19   D16   B17   C16   A18   D15   B16   C15   A17   D14   B15   C14   A16   | Basic<br>Function<br>U8.5<br>U8.4<br>U8.3<br>U8.2<br>U8.1<br>U8.0<br>U4.3<br>U4.2<br>U4.1<br>U4.0<br>U3.7 | Port<br>Special In<br>CAN2-RX/PINT3<br>LCD-SYNC-IN<br>(CAN3-RX)<br>LCD-CLK-IN<br>CAN0-RX | Port<br>Special Out<br>LCD-SYNC-OUT<br>CAN2-TX<br>LCD-CLK-OUT<br>(CAN3-TX)<br>CC3-OUT<br>CC4-OUT<br>TO2<br>CAN0-TX | SEG8.5<br>SEG8.4<br>SEG8.3<br>SEG8.2<br>SEG8.1<br>SEG8.0 |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|

| 193<br>194<br>195<br>196<br>197<br>198<br>199<br>200<br>201<br>202<br>203<br>204<br>205<br>206<br>207<br>208<br>209<br>210<br>211<br>212<br>213<br>214 | D17<br>B18<br>C17<br>A19<br>D16<br>B17<br>C16<br>A18<br>D15<br>B16<br>C15<br>A17<br>D14<br>B15<br>C14 | U8.5<br>U8.4<br>U8.3<br>U8.2<br>U8.1<br>U8.0<br>U4.3<br>U4.2<br>U4.1<br>U4.0<br>U3.7                      | CAN2-RX/PINT3 LCD-SYNC-IN (CAN3-RX) LCD-CLK-IN  CAN0-RX  CC0-IN  SPI1-D-IN               | LCD-SYNC-OUT CAN2-TX LCD-CLK-OUT (CAN3-TX) CC3-OUT CC4-OUT TO2 CAN0-TX                                             | SEG8.5<br>SEG8.4<br>SEG8.3<br>SEG8.2<br>SEG8.1<br>SEG8.0 |  |  |  |  |

| 194<br>195<br>196<br>197<br>198<br>199<br>200<br>201<br>202<br>203<br>204<br>205<br>206<br>207<br>208<br>209<br>211<br>212<br>213<br>214               | D17<br>B18<br>C17<br>A19<br>D16<br>B17<br>C16<br>A18<br>D15<br>B16<br>C15<br>A17<br>D14<br>B15<br>C14 | U8.4<br>U8.3<br>U8.2<br>U8.1<br>U8.0<br>U4.3<br>U4.2<br>U4.1<br>U4.0<br>U3.7                              | LCD-SYNC-IN (CAN3-RX) LCD-CLK-IN  CAN0-RX  CC0-IN  SPI1-D-IN                             | CAN2-TX<br>LCD-CLK-OUT<br>(CAN3-TX)<br>CC3-OUT<br>CC4-OUT<br>TO2<br>CAN0-TX                                        | SEG8.4<br>SEG8.3<br>SEG8.2<br>SEG8.1<br>SEG8.0           |  |  |  |  |

| 195<br>196<br>197<br>198<br>199<br>200<br>201<br>202<br>203<br>204<br>205<br>206<br>207<br>208<br>209<br>211<br>212<br>213<br>214                      | B18<br>C17<br>A19<br>D16<br>B17<br>C16<br>A18<br>D15<br>B16<br>C15<br>A17<br>D14<br>B15<br>C14        | U8.3<br>U8.2<br>U8.1<br>U8.0<br>U4.3<br>U4.2<br>U4.1<br>U4.0<br>U3.7                                      | (CAN3-RX)<br>LCD-CLK-IN<br>CAN0-RX<br>CC0-IN<br>SPI1-D-IN                                | CCA-OUT (CAN3-TX) (C3-OUT (C4-OUT TO2 CAN0-TX                                                                      | SEG8.3<br>SEG8.2<br>SEG8.1<br>SEG8.0                     |  |  |  |  |

| 196<br>1197<br>1198<br>1199<br>200<br>201<br>202<br>203<br>204<br>205<br>206<br>207<br>208<br>209<br>210<br>211<br>212<br>213<br>214                   | C17 A19 D16 B17 C16 A18 D15 B16 C15 A17 D14 B15 C14                                                   | U8.2<br>U8.1<br>U8.0<br>U4.3<br>U4.2<br>U4.1<br>U4.0<br>U3.7                                              | CANO-RX  CCO-IN  SPI1-D-IN                                                               | (CAN3-TX) CC3-OUT CC4-OUT TO2 CAN0-TX                                                                              | SEG8.2<br>SEG8.1<br>SEG8.0                               |  |  |  |  |

| 197<br>1198<br>1199<br>2000<br>201<br>202<br>203<br>204<br>205<br>206<br>207<br>208<br>209<br>211<br>211<br>212<br>213<br>214                          | A19<br>D16<br>B17<br>C16<br>A18<br>D15<br>B16<br>C15<br>A17<br>D14<br>B15<br>C14                      | U8.1<br>U8.0<br>U4.3<br>U4.2<br>U4.1<br>U4.0<br>U3.7                                                      | CANO-RX CC0-IN SPI1-D-IN                                                                 | CC3-OUT CC4-OUT TO2 CAN0-TX                                                                                        | SEG8.1<br>SEG8.0                                         |  |  |  |  |

| 1198<br>1199<br>2200<br>2201<br>2202<br>2203<br>2204<br>2205<br>2206<br>2207<br>2208<br>2209<br>2210<br>2211<br>2212<br>2213<br>2214                   | D16<br>B17<br>C16<br>A18<br>D15<br>B16<br>C15<br>A17<br>D14<br>B15<br>C14                             | U8.0<br>U4.3<br>U4.2<br>U4.1<br>U4.0<br>U3.7                                                              | CC0-IN<br>SPI1-D-IN                                                                      | CC4-OUT<br>TO2<br>CAN0-TX                                                                                          | SEG8.0                                                   |  |  |  |  |

| 1199<br>2200<br>2201<br>2202<br>2203<br>2204<br>2205<br>2206<br>2207<br>2208<br>2209<br>2210<br>2211<br>2212<br>2213<br>2214                           | B17<br>C16<br>A18<br>D15<br>B16<br>C15<br>A17<br>D14<br>B15<br>C14                                    | U4.3<br>U4.2<br>U4.1<br>U4.0<br>U3.7                                                                      | CC0-IN<br>SPI1-D-IN                                                                      | TO2<br>CAN0-TX                                                                                                     |                                                          |  |  |  |  |

| 200<br>201<br>202<br>203<br>204<br>205<br>206<br>207<br>208<br>209<br>210<br>211<br>212<br>213<br>214                                                  | C16 A18 D15 B16 C15 A17 D14 B15 C14                                                                   | U4.2<br>U4.1<br>U4.0<br>U3.7                                                                              | CC0-IN<br>SPI1-D-IN                                                                      | CAN0-TX                                                                                                            | D D O                                                    |  |  |  |  |

| 201<br>202<br>203<br>204<br>205<br>206<br>207<br>208<br>209<br>210<br>211<br>212<br>213<br>214                                                         | A18<br>D15<br>B16<br>C15<br>A17<br>D14<br>B15<br>C14                                                  | U4.1<br>U4.0<br>U3.7                                                                                      | SPI1-D-IN                                                                                |                                                                                                                    | BP3                                                      |  |  |  |  |

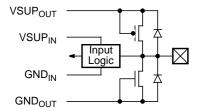

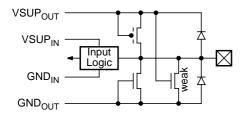

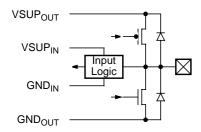

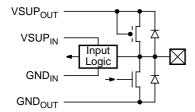

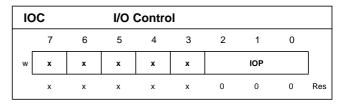

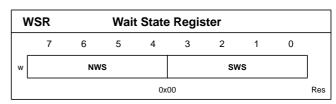

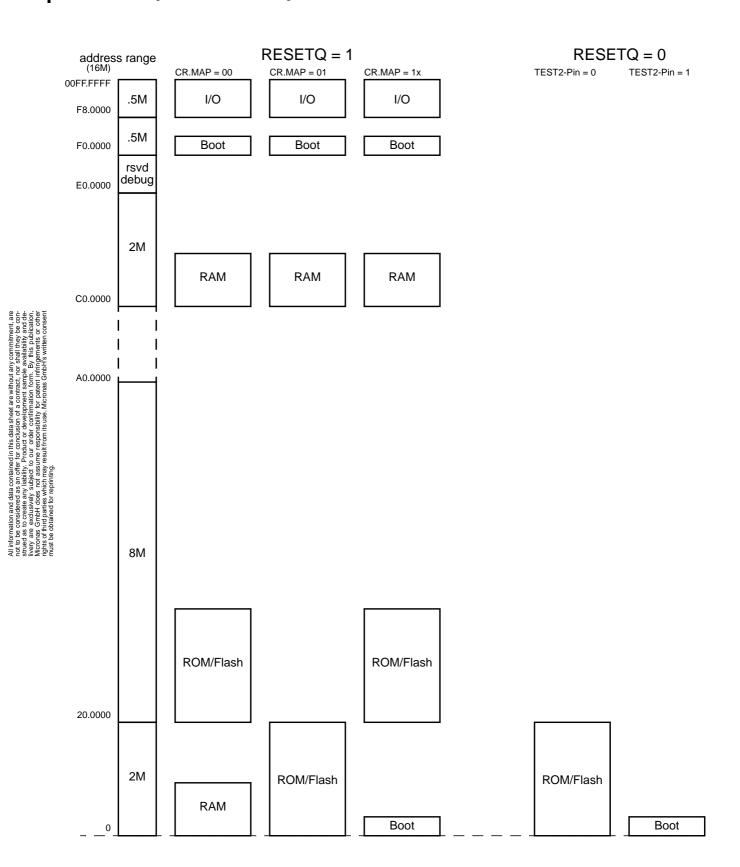

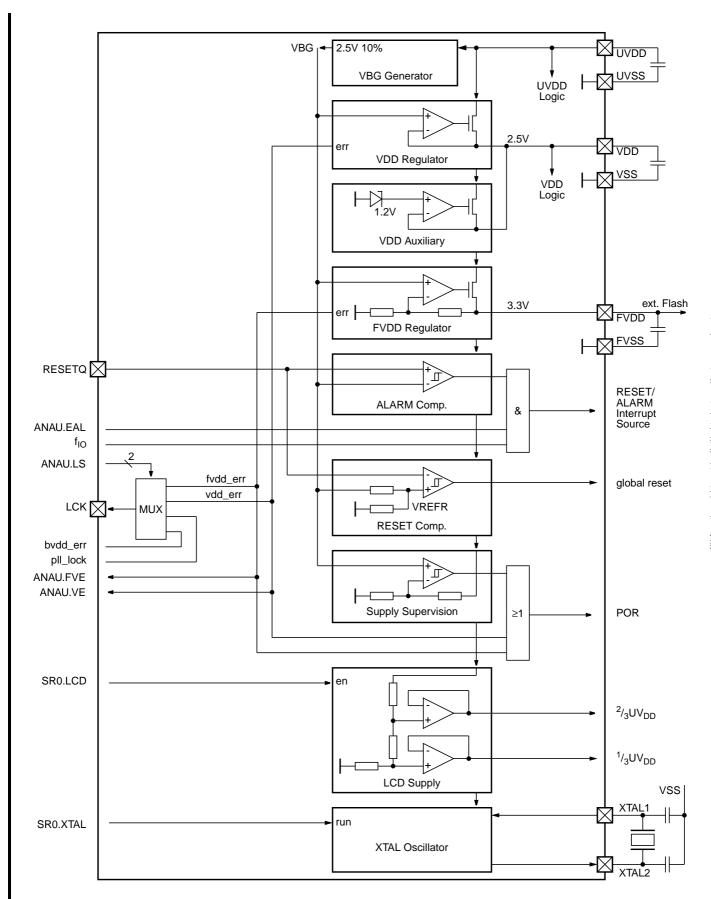

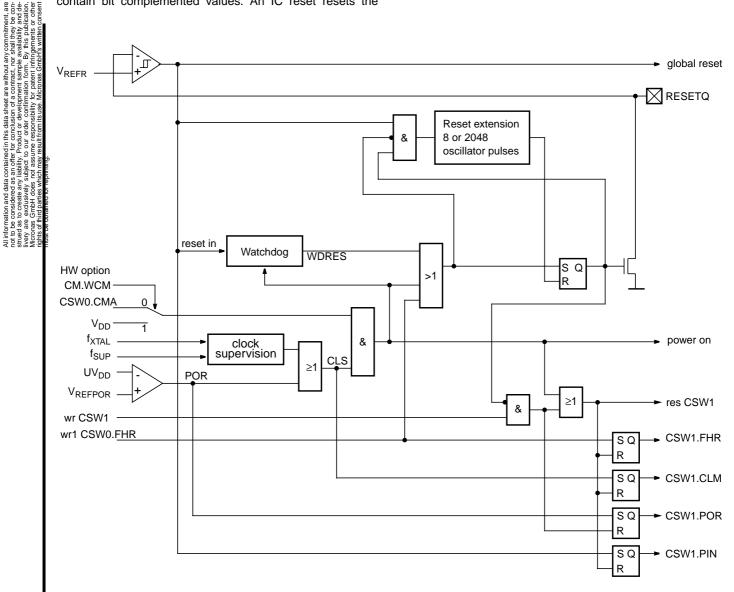

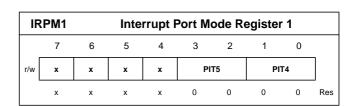

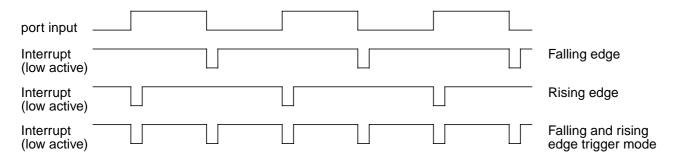

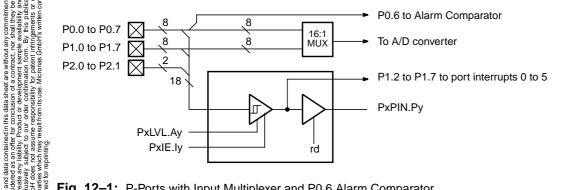

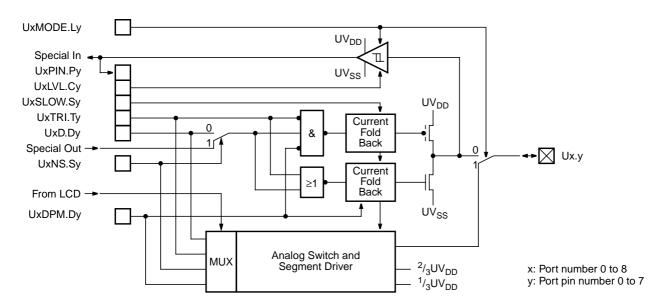

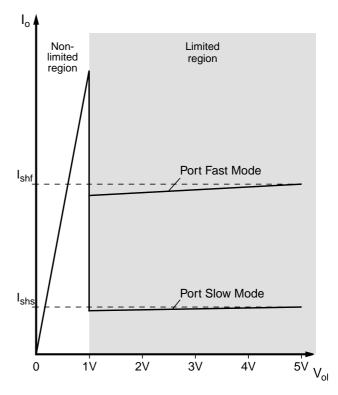

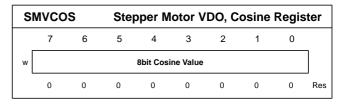

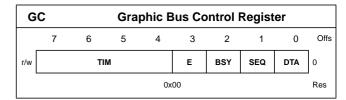

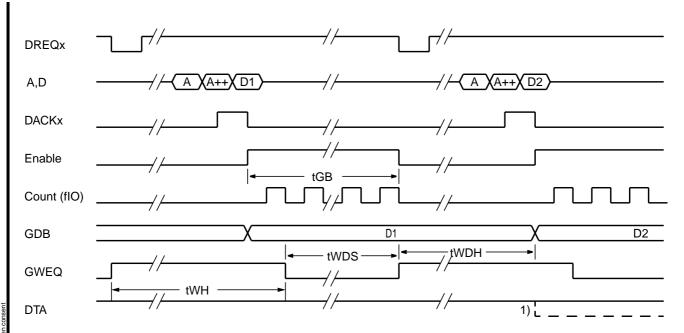

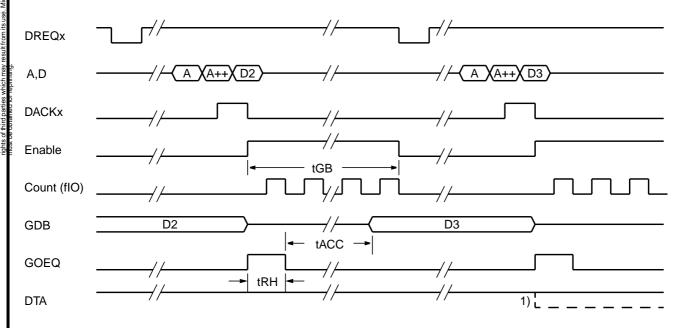

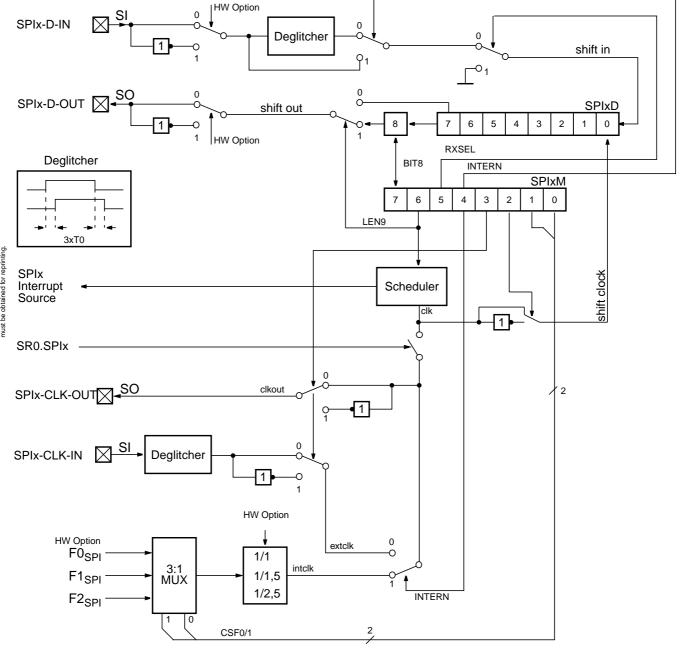

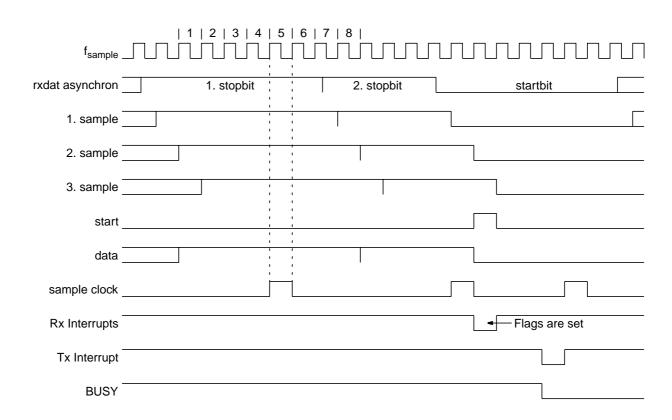

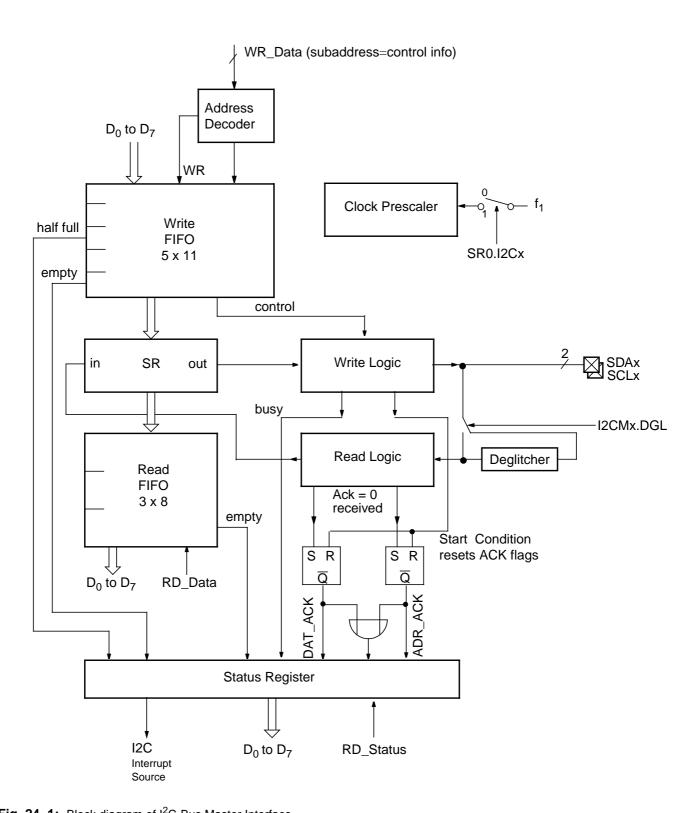

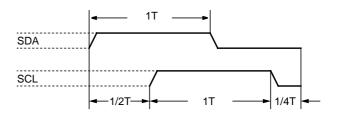

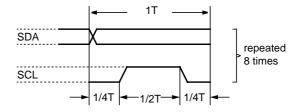

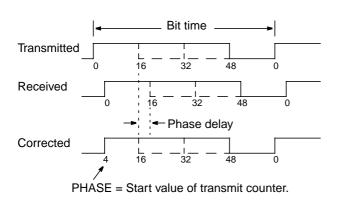

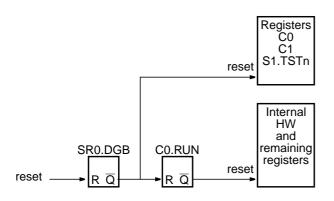

| 202<br>203<br>204<br>205<br>206<br>207<br>208<br>209<br>210<br>211<br>212<br>213<br>214                                                                | D15<br>B16<br>C15<br>A17<br>D14<br>B15<br>C14                                                         | U4.0<br>U3.7                                                                                              | SPI1-D-IN                                                                                | 0011 - 01                                                                                                          | BP2                                                      |  |  |  |  |