# Contents

| Page | Section | Title                                                      |

|------|---------|------------------------------------------------------------|

| 4    | 1.      | Introduction                                               |

| 4    | 1.1.    | Features of the CCU 3000, CCU 3000-I, CCU 3001, CCU 3001-I |

| 5    | 2.      | Functional Description                                     |

| 5    | 2.1.    | ROM                                                        |

| 5    | 2.2.    | RAM                                                        |

| 5    | 2.3.    | CPU                                                        |

| 5    | 2.4.    | Clock Generator                                            |

| 5    | 2.5.    | PORT 1 to PORT 3, PORT 6 to PORT 8                         |

| 5    | 2.6.    | PORT 4                                                     |

| 5    | 2.7.    | I/O-Lines P50 to P55                                       |

| 6    | 2.8.    | Special Mode of Port 7                                     |

| 7    | 2.8.1.  | Power-down Control External Memory (Special Mode P77)      |

| 7    | 2.8.2.  | R/W Output (Special Mode P76)                              |

| 7    | 2.8.3.  | Banking Address (Special Mode P70 to P75)                  |

| 8    | 2.9.    | Reset Function                                             |

| 8    | 2.10.   | Control Register                                           |

| 10   | 2.11.   | Interrupt Controller                                       |

| 12   | 2.12.   | IM Bus Interface                                           |

| 14   | 2.13.   | Multifunctional Timer                                      |

| 19   | 2.14.   | Watchdog                                                   |

| 21   | 2.15.   | IR-Input                                                   |

| 21   | 2.16.   | Mask Options                                               |

| 22   | 3.      | Definitions                                                |

| 22   | 3.1.    | Interrupt Definitions                                      |

| 22   | 3.2.    | Memory Mappings                                            |

| 22   | 3.3.    | I/O Definitions                                            |

| 23   | 4.      | Specifications                                             |

| 23   | 4.1.    | Outline Dimensions                                         |

| 24   | 4.2.    | Pin Configuration                                          |

| 25   | 4.3.    | Pin Connections and Short Descriptions                     |

| 28   | 4.4.    | Pin Descriptions                                           |

| 31   | 4.5.    | Pin Circuits                                               |

| 32   | 4.6.    | Electrical Characteristics                                 |

| 32   | 4.6.1.  | Absolute Maximum Ratings                                   |

| 32   | 4.6.2.  | Recommended Operating Conditions                           |

| 32   | 4.6.3.  | Recommended Crystal Characteristics                        |

| 33   | 4.6.4.  | DC Characteristics                                         |

| 34   | 4.6.5.  | Using External Devices                                     |

| 34   | 4.6.6.  | AC Characteristics                                         |

| 36   | 4.6.7.  | IM Bus Waveforms                                           |

| 36   | 4.6.8.  | Description of the IM Bus                                  |

| 37   | 4.6.9.  | Recommended Operating Conditions of IM Bus                 |

| 38   | 4.6.10. | Registers                                                  |

| 59   | 5.      | Index                                                      |

| 61   | 6.      | Addendum: CCU 3000, CCU 3000-I EMU Versions                |

| 62   | 7.      | Addendum: CCU 3000 1 μm Version                            |

# Contents, continued

| Page | Section | Title                                                 |

|------|---------|-------------------------------------------------------|

| 62   | 7.1.    | Electrical Characteristics                            |

| 62   | 7.1.1.  | Absolute Maximum Ratings                              |

| 63   | 7.1.2.  | Recommended Operating Conditions                      |

| 63   | 7.1.3.  | Recommended Crystal Characteristics                   |

| 64   | 7.1.4.  | DC Characteristics                                    |

| 65   | 7.1.5.  | AC Characteristics                                    |

| 66   | 8.      | Addendum: CCU 3000-I Specification                    |

| 66   | 8.1.    | Changes to CCU3000                                    |

| 66   | 8.2.    | Definitions                                           |

| 66   | 8.3.    | Interrupt Definitions                                 |

| 66   | 8.4.    | Memory Mappings                                       |

| 66   | 8.5.    | I/O Definitions                                       |

| 67   | 8.6.    | I <sup>2</sup> C and IM Bus Interface                 |

| 71   | 8.7.    | Pin Connections and Short Descriptions                |

| 73   | 8.7.1.  | DC Parameters I <sup>2</sup> C Bus Master Interface   |

| 74   | 8.8.    | List of Registers that Differ from CCU 3000, CCU 3001 |

| 76   | 9.      | Data Sheet History                                    |

#### 1. Introduction

The CCU 3000, CCU 3000-I, CCU 3001, CCU 3001-I are integrated circuits designed in 1.2  $\mu m$  CMOS technology, with the exception of CCU 3000, TC18 and TC19, which is designed in 1  $\mu m$  CMOS technology. The CPU contained on the chips is a functionally unchanged 65C02-core, which means that for program development, systems can be used which are on the market; including high level language compilers.

The pin numbers mentioned in this data sheet refer to the 68-pin PLCC package unless otherwise designated.

The CCU 3000-I is described separately in an addendum on page 66.

# 1.1. Features of the CCU 3000, CCU 3000-I, CCU 3001, CCU 3001-I

- CCU 3000 = ROM-less version of the CCU 3001

- 65C02 CPU with max. 8 MHz clock

- 32 kByte internal ROM (CCU 3001 only)

- 1344 internal Bytes RAM with stand-by option

- 51 I/O lines (CCU 3001)

- 26 I/O lines (CCU 3000)

- clock generator with programmable clock frequency

- 8 level interrupt controller

- CCU 3000, CCU 3001:2 Multimaster IM bus interfaces

- CCU 3000-I, CCU 3001-I: 1I<sup>2</sup>C/IM bus and 1 Multimaster IM bus interface (see addendum)

- IR-input for software-decoded IR-systems

- on-chip power on, stand-by and clock supervision logic

- on-chip watchdog

- 3 multifunctional timers

- supports memory banking (external 2MBytes)

- power down signal for external memory

- mask option: EMU mode

- programs can be written in Assembler or in "C"

- CCU 3000 TC 18/19: 1.0 μm CMOS technology, (see addendum)

- application software available

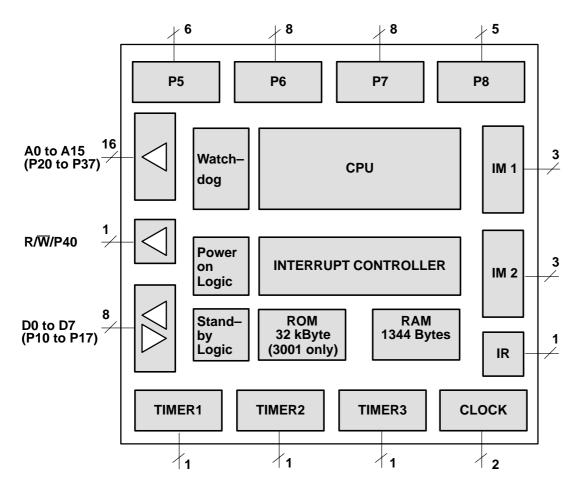

Fig. 1-1: CCU 3000, CCU 3001 block diagram

#### 2. Functional Description

#### 2.1. ROM

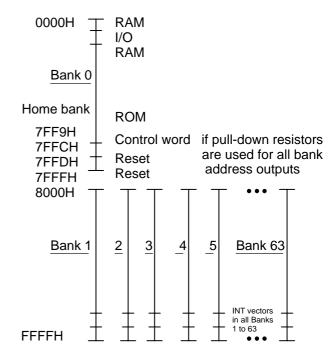

The chip is equipped with 32 kByte mask-programmable ROM. The ROM uses up the address space from 8000H to FFFFH. This ROM can be supplemented or replaced externally. Only the CCU 3001 has an internal ROM.

#### 2.2. RAM

The RAM area is split into three parts:

– page 0 (address 0 to FFH)

- page 1 (address 100H to 1FFH)- page 3, 4, 5, 6 (address 300H to 63FH)

Page 0 offers a particularly fast access to the 65C02 and is therefore very valuable for fast, compact programs. Page 1 contains the stack and must therefore also have RAM. The remaining RAM-memory follows in pages 3, 4, 5, 6, as page 2 is reserved as I/O address space. The RAM can be kept in the stand-by mode via stand-by pin.

#### 2.3. CPU

The CPU core is fully compatible with the 65C02 microprocessor. However, not all the pins of the 65C02 processor are accessible for the user outside the chip. One switch in the control register allows the CPU to be switched off, so that an external processor can take over its tasks. This external processor can of course also be an in-circuit emulator, which makes near-hardware emulation possible, even though the status and control lines of the internal CPU are not accessible. If an external processor is used, all hardware blocks of the chip are as accessible to it as if it were the internal CPU.

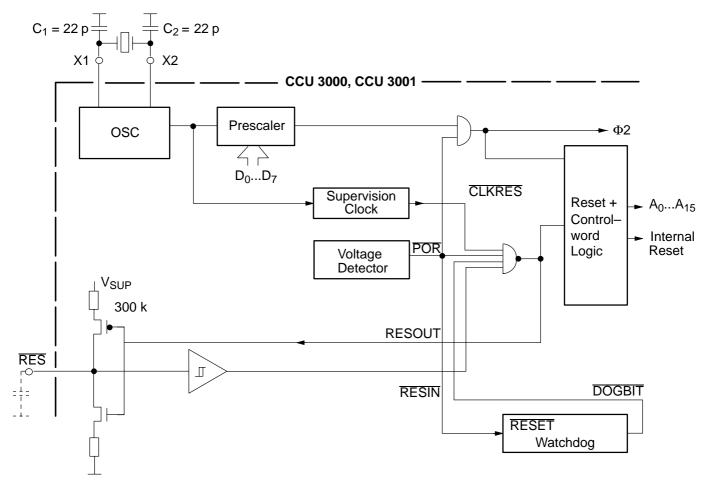

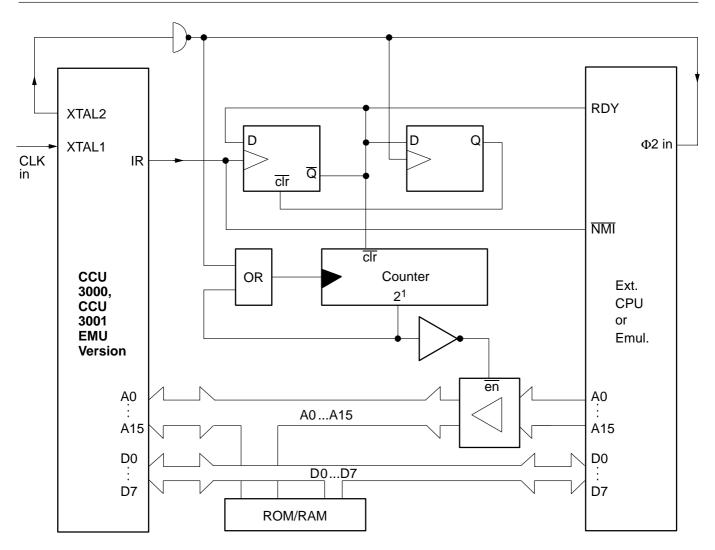

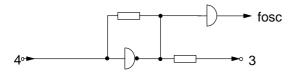

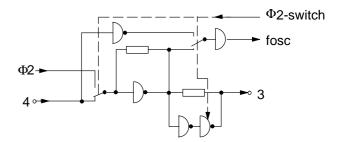

### 2.4. Clock Generator

An integrated two-pin oscillator generates the clock for the microcontroller. The frequency created by the oscillator can be programmed to be reduced with a divider by the factor 1 ... 255. This enables the user to decrease the current consumption by the controller by reducing the working frequency as well as to increase the access time for the (slower) external memory. This divider contains the value 4 after a reset, so that the system can also start with a slow external memory. If the mask-option OSC is set (EMU version), a switch in the control register makes it possible to receive the internal clock  $\Phi 2$  at XTAL2. In this case the oscillator must be external and the clock must be fed to the pin XTAL1. In this way, the user gets a time reference for internal operations in the microcomputer. This is especially important with the interrupt controller. The production version of the CCU does not have this function!

## 2.5. PORT 1 to PORT 3, PORT 6 to PORT 8

8 ports belong to the system, of which 5 are 8 bits wide, one 6 bit, one 4 bit and one 1 bit wide. All port lines of PORTS 1 to 3 and 6 to 8 can be used as inputs or outputs independently from each other. One register per port defines the direction. PORT1 to PORT3 have push-pull outputs and PORT6 to PORT8 have open drain outputs. Even a line defined as output can be read, the pin level being important. This property makes it possible for the software to find desired and undesired short circuits. Each port reserves a byte for the direction register and the data in the I/O page. If the corresponding bit in the direction register is set to 0, the output mode is switched on. After a reset, all bits of a direction register are set to 1. The falling edge of bit 7 of PORT 8 generates interrupts if the priority of the corresponding interrupt controller source (7) is not set to 0.

#### 2.6. PORT 4

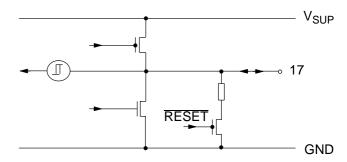

PORT 4 consists of only one line (LSB, P40). After a reset, PORT 4 operates as an input only. As soon as PORT 4 is written for the first time, it is switched to output mode (push-pull). Later read accesses read the actual level at port 4. If bit 3 in the control word is active, P4 is used as an R/W-line. If the internal CPU is active, R/W is an output line, otherwise it is an input. But P4 has another, very important function during RESET. The level at P4 during RESET decides whether the control word is read from the internal ROM (FFF9H) or from the external memory. It is therefore important that the desired level during RE-SET is set at P4. An internal pull-down resistor of approx. 100 k $\Omega$  is integrated in the CCU 3001, which ensures that the control word is read by the internal ROM. The external control word access is obtained via an external pull-up resistor of approx. 5 k $\Omega$ . The CCU 3000 has an internal pull-up resistor at P4 (external ROM access). The further mode of operation of the CCU 3000, CCU 3001 depends only on the control word though.

Please note that this mode is always necessary for the CCU 3000 since this device does not have internal ROM!

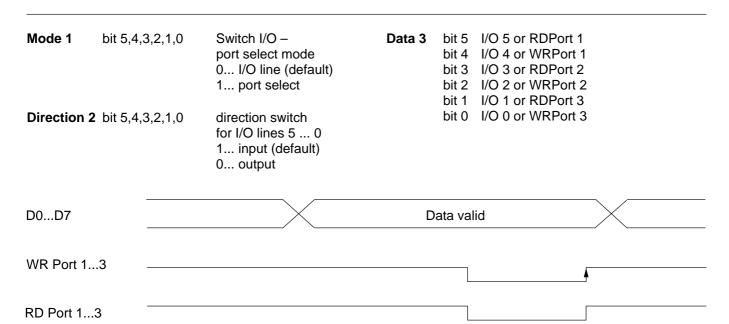

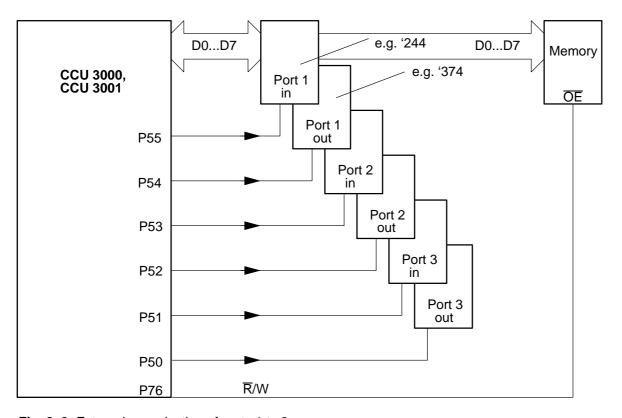

## 2.7. I/O-Lines P50 to P55

The 6 additional I/O-lines have a two-fold function:

- input or output line (open drain output) or

- fully decoded I/O-select lines (push-pull outputs)

As a rule these lines can be used as input or output lines. As soon as ports 1 to 4 are used as system bus, they are lost as I/O-channels. However, a total of 48 port lines (24 inputs and outputs each) can be reconstructed without difficulties (1 housing for 8 lines), if the additional 6 I/O-lines of the CCU 3000, CCU 3001 are switched into the port select mode. They then represent the select lines of the original ports 1 to 3. Each line can be defined as I/O or port select line separately. In the I/O-page three bytes are needed.

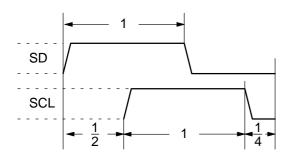

Fig. 2-1: Timing diagram

Fig. 2-2: External reproduction of ports 1 to 3

## 2.8. Special Mode of Port 7

Each line of port 7 can be switched independently into a special mode. This mode is selected by the mode control register. After reset this register is set to 0 (= Port mode). A "1" in this register turns this line into the special mode. As the control signals are all outputs, the direction for those lines must be defined as outputs (reset condition = inputs)

| Special Mode of | Function                                                              |

|-----------------|-----------------------------------------------------------------------|

| P77             | Power-down control for ext.                                           |

| P76<br>P75P70   | memory R/W output 6 bit banking addresses with common home bank logic |

All special mode signals have push-pull outputs. (Port mode: open drain).

# 2.8.1. Power-down Control External Memory (Special Mode P77)

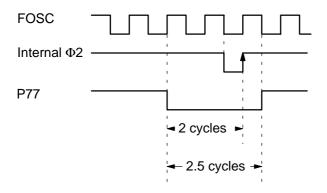

In many applications the power consumption of the controller should be reduced when the system goes into standby mode. The programmable clock of the CCU allows this, but external memories do not automatically reduce their power consumptions when the access speed is slower. These devices need a separate control signal for power down. Special out of P77 delivers such a signal. It is low for the last two XTAL cycles before, and 0.5 cycles after the rising edge of the internal PHI2 clock. This guarantees a wake-up and address time of 2 cycles and a maximum active time of 2.5 clock cycles for each PHI2 period. At higher speeds the P77 special out stays low

Fig. 2-3: Power-down control

Please note that during and after reset P77 is a port line (= tristate) until the special mode and the direction register is set by software. A pull-down resistor on the power-down input of the memory is necessary to allow the CCU the access to the control word and the first instructions.

## 2.8.2. R/W Output (Special Mode P76)

This is the negated R/W-line of the CPU. Can be used for  $\overline{\text{CE}}$  or  $\overline{\text{OE}}$  control on memories. With a pull-down resistor on this pin it is active during RESET.

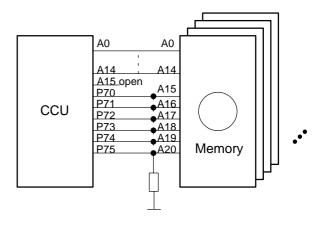

#### 2.8.3. Banking Address (Special Mode P70 to P 75)

Banking is done in 32 KByte banks. The first bank (000H to 7FFFH) includes the RAM, the I/O-page and ROM (all other locations) and is used as a home-bank for the banking controller, interrupt routines, common subroutines etc. The second half of the address space (8000H to FFFFH) is banked.

In the special mode of Port 70 to 75 the content of the data register is output as long as the address A15=1.

A low level of A15 forces all special outs of P70 to P75 to become '0'. The data register can contain the bank ad-

dresses 1 to 63. This bank is used for CPU accesses from 8000H to FFFFH. Low accesses are always done to bank 0, independent of the data of Port 7.

#### Note:

- all upper banks must contain the interrupt vectors.

Bank 0 must have the control word and reset vector.

- during and after reset P7 is in the Tristate-Port-Mode. To make sure that the control word and the reset vector can be accessed use high impedance pull-down resistors on all special-out P7 lines. The control word and the reset vector are then accessed out from bank 0. The init routine (where P7 will be defined as special out) must be in bank 0.

Fig. 2-4: Memory Map, up to 2 MByte

Fig. 2-5: Banking with 32 kByte banks

#### 2.9. Reset Function

The internal reset provides a correct basic setup of the complete hardware on the chip. For this the internal control register is loaded during reset. One reserved byte in the ROM is accessed by the reset circuit and its content is copied into the control register. The internal voltage supervision resets the IC if the voltage is too low. The reset pin is also used as output for internal reset sources (watchdog, power-down detector, clock supervisor). Internal resistors limit the maximum current.

## 2.10. Control Register (address 201H)

This is a combination of control switches in an 8-bit register. During reset it is loaded with the contents of the address FFF9H, but it can also be read and written via software. The controller starts operation with the setting

dictated by reset. The switches have the following functions:

| bit 0      | CPU_disable  | (low active) |

|------------|--------------|--------------|

| bit 1      | RAM_disable  | (low active) |

| bit 2      | ROM_disable  | (low active) |

| bit 3      | R/W-mode P4  | (low active) |

| bit 4      | Bus external | (low active) |

| bit 5 to 7 | set to 1     |              |

The setting at the R/ $\overline{W}$ -pin decides whether the control word is read internally or externally. Bit 0 to bit 2 are the switches which can disable RAM, ROM and CPU. For external access a pull-up resistor must be connected to the R/ $\overline{W}$  pin (CCU 3001). Bit 4 switches P1, P2 and P3 into the system bus mode. If the internal CPU is active, the direction of the data bus drivers is automatically set correctly, so that no additional decoding is necessary. Bit 3 switches P4 into the R/ $\overline{W}$  mode. If no external write access is necessary, (ext. EPROM), P4 can stay in the port mode.

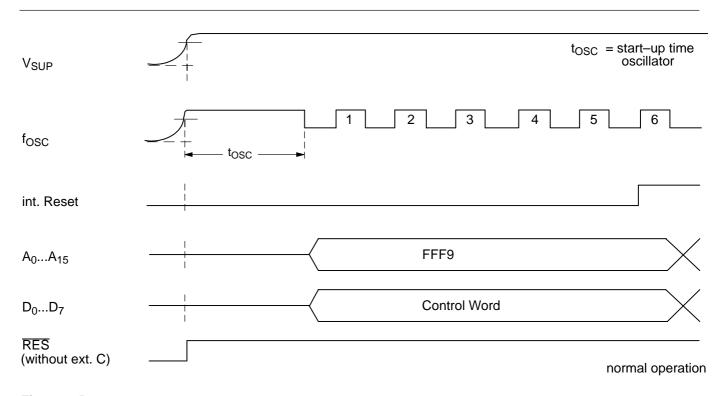

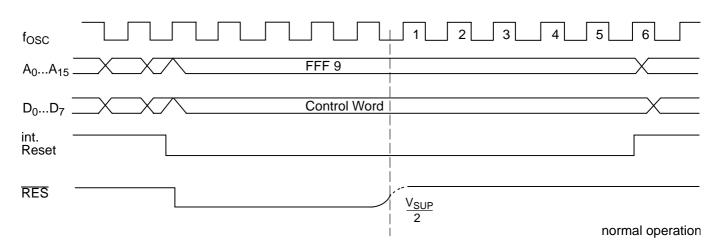

Fig. 2-6: Oscillator and reset

Fig. 2-7: Power-on sequence

Fig. 2-8: External reset sequence

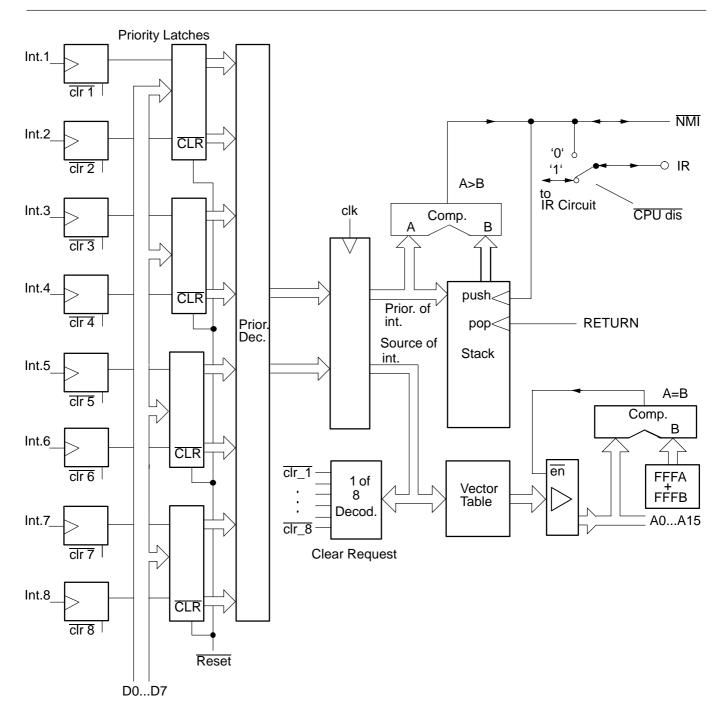

#### 2.11. Interrupt Controller

The most important properties of this controller are:

- 8 sources

- 8 freely programmable priorities for every source

- maximum delay of 3 clock cycles

- vectorized interrupts, i.e., automatically the correct routine is accessed

- also to be used for external CPU

- option: disable after interrupt (resettable by software)

Running service routines are only interrupted if interrupts are enabled and a request of higher priority arrives. All others are stored and executed when interrupts of higher priority have been finished. Priority 0 means that the corresponding interrupt is disabled. (Priorities 1-7 lead to interrupts). One property of the controller is that the CPU is not modified, but vectorization takes place all the same. Thus the use of this controller is also possible for external CPUs (emulator!).

Solely the return from a service program differs slightly in software from the methods normally used for the 65C02. The last command before the "RTI" must be a write operation into the return register of the controller. This tells the controller that the service routine has been completed. Apart from this return register the controller occupies further 5 bytes. One of these serves as a control byte, the others incorporate the priorities for 8 sources. The controller therefore needs 6 bytes of the I/O-page. The control byte comprises:

| bit 0 | CLEAR_ALL_REQUESTS  | (low active) |

|-------|---------------------|--------------|

| bit 1 | ALLOW_ONE_INTERRUPT | (low active) |

| bit 2 | DISABLE_INTERRUPTS  | (low active) |

| bit 3 | DISABLE_AFTER_INT   | (low active) |

| bit 4 | RESET_CONTROLLER    | (low active) |

All bits reset to 1 (inactive).

CLEAR\_ALL\_REQUESTS clears all interrupt flags at the same time. ALLOW\_ONE\_INTERRUPT is used in connection with the DISABLE\_AFTER\_INT (bit 3), to allow access to the next interrupt. DISABLE\_INTERRUPT does not allow any interrupts, the request flags are set however. With the exception of bits 3 and 2 (DISABLE\_INTERRUPTS, DISABLE\_AFTER\_INT) these are all dynamic signals, that is, the write process itself

sends an appropriate signal. This has the same impulse length as the 65C02. Each of the 4 priority registers contains the priorities for 2 interrupt sources.

| bit 7, 6, 5, 4 | Priority for sources                             |

|----------------|--------------------------------------------------|

| bit 3, 2, 1, 0 | 8, 6, 4, 2<br>Priority for sources<br>7, 5, 3, 1 |

To connect an external CPU (emulator) with the controller, only two ICs of the 74-family are needed.

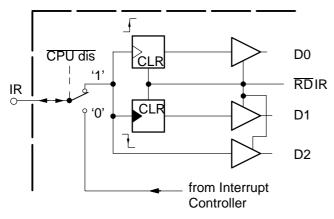

**Fig. 2–9:** Dynamic control signals interrupt Bits 0, 1, 4

**Fig. 2–10:** Static control signals interrupt Bits 2, 3

Fig. 2-11: Interrupt controller

Fig. 2-12: Using an external CPU

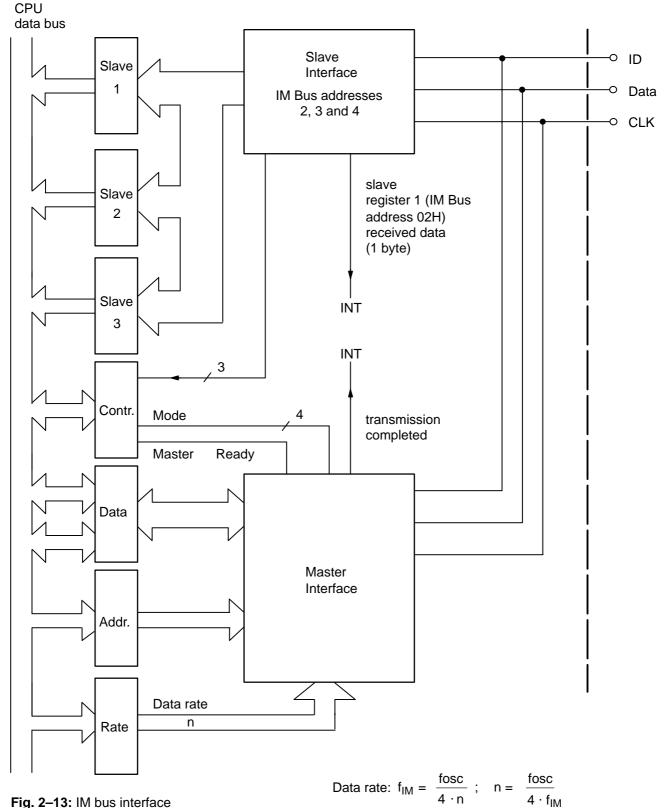

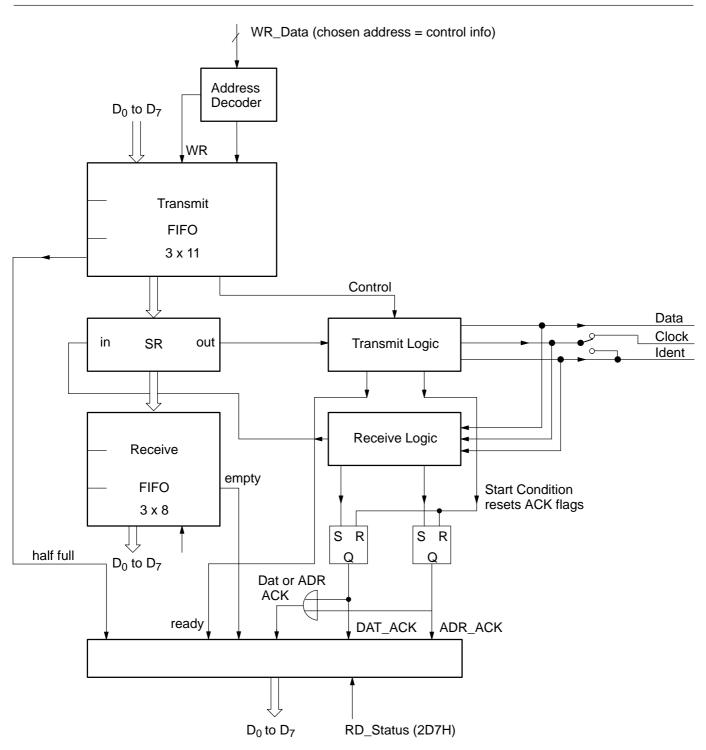

## 2.12. IM Bus Interface

The IM bus has been improved in its characteristics for the CCU 3000, CCU 3001. In comparison to the interface of the CCU 2000 series it differs in:

- multimaster ability

- 3 slave registers (8 bit wide)

- higher speed possible

The multimaster ability permits the use of several CCUs on the same IM bus without impeding each other. Specially in add-on systems or systems with need of high computing power and/or I/O requirements, this offers great advantages. If several CCUs are admitted in a system, it must be ascertained that these can communicate with each other. A slave IM bus interface has been installed for this purpose. Parallel to the lines of the master, three completely independent receiver registers have been installed. All of these are constantly alert, whether the master itself is active or not. As all CCUs have the same IM bus addresses for these registers, the contents of these registers (that is, for all CCUs that are

in the system) will be the same. The handshake amongst these is realized in software, and one register each is reserved for the device address, the request and the data to be transported. The data rate can now be adjusted per software. It is possible to attain 1 MBit/s, if the bus participants in question are devised to support this rate. Also the actual realization of the bus can forbid such a high data rate. The IM bus interface needs external pull-up resistors.

In the I/O-page the IM bus interface reserves 8 bytes:

| 3 bytes | slave receiving registers (read)          |

|---------|-------------------------------------------|

| 1 byte  | master address (write)                    |

| 2 bytes | master data register (read/write)         |

| 1 byte  | control register (read/write)             |

| read:   | bit 0 0 IM bus master ready               |

|         | 1 IM bus master busy                      |

|         | bit 1 1 Byte received in slave register 1 |

|         | (may generate interrupt)                  |

|         | bit 2 IM-bus 1 control and status         |

|         | (may generate interrupt)                  |

|         | bit 3 Word 3 Received (may generate       |

|         | interrupt)                                |

|         |                                           |

bit 0 1... Write 8 bit write:

bit 1 1... Write 16 bit

bit 2 1... Read 8 bit

bit 3 1... Read 16 bit

1 byte Data rate (5 bits) =  $\frac{\text{fosc}}{4 \cdot \text{n}}$

Only one of the bits 0 to 3 in the control register should be set. If all bits are set to '0', a reset of the interface is done, thus deleting telegrams still waiting for access to the bus. The IM bus addresses for the slave registers

| Slave register | IM bus address |

|----------------|----------------|

| 1              | 02 H           |

| 2              | 03 H           |

| 3              | 04 H           |

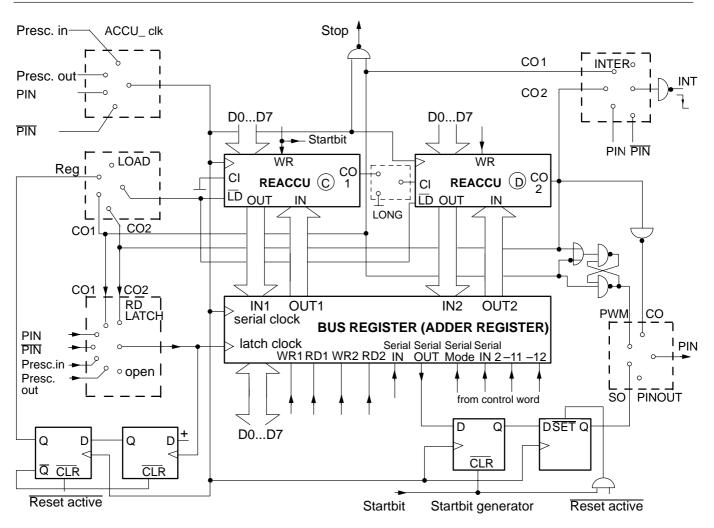

Fig. 2-13: IM bus interface

#### 2.13. Multifunctional Timer

The multifunctional timer for the CCU 3000, CCU 3001 has quite an unusual structure. It can serve as:

- event counter

- frequency counter

- pulse-length meter

- timer

- rate multiplier

- PWM

- asynchronous, serial interface

Each timer has a reserved pin and an interrupt. The pin is either input or output, depending on its function. Used as an output it has a push-pull structure. The timer consists of three main parts:

- start and stop detector

- internal time reference

- accumulator and arithmetic unit

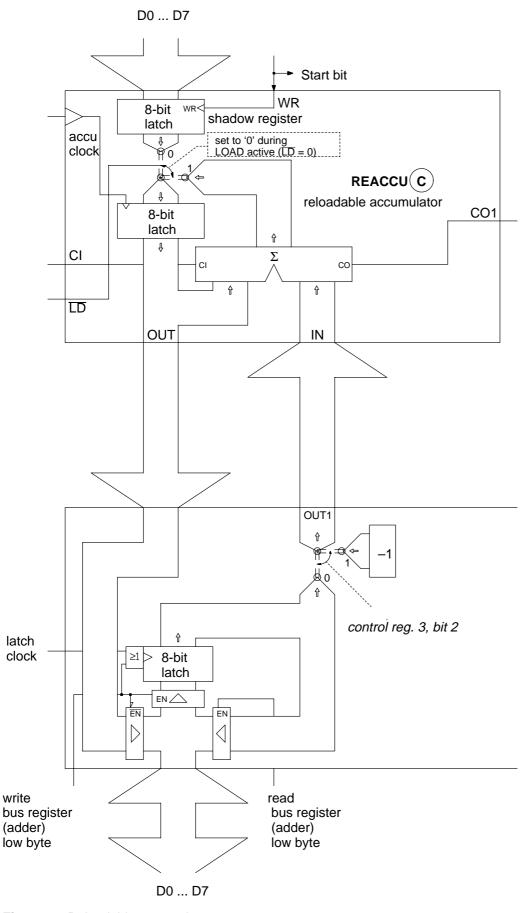

The start and stop detector controls the internal pulse generator to synchronize counter and meter operations. The timer itself does not consist of a counter circuit, but of an accumulator and an adder. This configuration works as a counter with adjustable step length, as a shift register, as a PWM and as a rate multiplier. Change-over of operation modes can easily be effected.

Each of the multifunctional timer circuits of the CCU is realized as two 8-bit accumulators. In addition, there is

a separate adder register for each of them. Both the accumulator and the adder may be accessed by the CPU via data bus. The accumulator has a shadow register the CPU may write to and the adder bus register may be read and written to.

While the adder register forms one side of the adder, the other side is either the output of the adder or the content of the accu shadow register. With every accu clock pulse either of these bytes is used. If no "LOAD" signal is active, the adder output is used. With "LOAD" active, the following accu clock pulse uses the content of the accu shadow register as adder input. The "LOAD" signal is derived from 1 out of 4 sources, selectable with bits 3 and 4 of control byte 3. Accu clock is selectable with bits 1 and 2 in control byte 2. Instead of the content of the adder register, accessible by the CPU, a hard-wired '-1' may be used as input of the other side of the adder (bits 1 and 2 in control byte 3). By adding '-1' to the accu's content, the adder works as a standard down counter. With specific "READ LATCH" signals (control byte 2, bits 3, 4 and 5) and using the adder register as adder input, its content defines the step width of the counter.

In addition to its parallel byte connections, the adder registers have serial inputs and outputs. A serial clock shifts its contents. To hit the middle of serial data, the timer's prescaler has a half load feature, controlled with bit 1 in control byte 1.

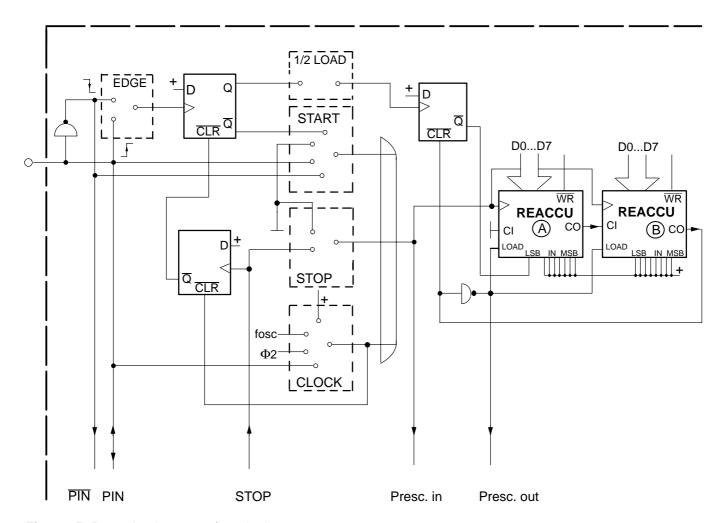

Fig. 2–14 shows a detailed diagram of the high part of the reloadable accumulator and its adder register. For examples of timer applications please refer to "Application Note CCU 3000/3001 Timers".

Fig. 2-14: Reloadable accumulator

Apart from the start values for the counter and adder registers, three control registers shift the timer into the preselected function.

Registers to control the timer:

2 bytes prescaler high and low byte (read/write)

(read: prescaler)

(write: prescaler and reload register)

2 bytes accu high and low byte (write)

(write: accu and reload register)

2 bytes adder register high and low byte

(read/write)

3 bytes control register 1 to 3 (write)

Fig. 2-15: Prescaler timer, start/stop logic

Fig. 2-16: Timer

The three control registers control the internal switches of the timer:

## **Control register 1**

## **Control register 2**

| bit 7    | SERIAL_2      | Second Serial Input<br>Level          | bit 7, 6    | PIN_out    | 00<br>01             | open<br>serial out                   |

|----------|---------------|---------------------------------------|-------------|------------|----------------------|--------------------------------------|

| bit 6, 5 | Clock         | 00 PIN<br>01 fosc.                    |             |            | 10<br>11             | PWM out carry accu D                 |

|          |               | 10 Φ2<br>11 disable clock             | bit 5, 4, 3 | Read_Latch | 000.<br>001.         | open                                 |

| bit 4    | Stop          | stop disabled     carry out accu      |             |            | 010.<br>011.         | carry accu C<br>carry accu D<br>PIN  |

| bit 3, 2 | Start         | 00 always active<br>01 edge<br>10 PIN |             |            | 100.<br>101.<br>110. | PIN prescaler output prescaler input |

| bit 1    | 1/2 load      | 11 PIN 0 disabled 1 active            | bit 2, 1    | accu clock | 00<br>01             | prescaler input<br>prescaler output  |

| bit 0    | Edge detector | 0 rising<br>1 falling                 | bit 0       | long       | 10<br>11<br>0        | PIN PIN open                         |

|          |               |                                       |             |            | 1                    | carry out accu C carry in accu D     |

# Control register 3

| bit 7, 6, 5<br>bit 4, 3 | INTER       | 000.<br>001.<br>010<br>011.<br>100.<br>00<br>01<br>10 | PIN<br>carry accu C<br>carry accu D<br>open<br>carry accu C |

|-------------------------|-------------|-------------------------------------------------------|-------------------------------------------------------------|

| bit 2                   | -11         | 0                                                     | ACCU C input = bus reg.                                     |

| bit 1                   | -12         | 1<br>0                                                | ACCU C<br>input = -1<br>ACCU D input<br>= bus reg.          |

| bit 0                   | Serial mode | 1<br>0<br>1                                           | ACCU D<br>input = -1<br>mode off<br>mode on                 |

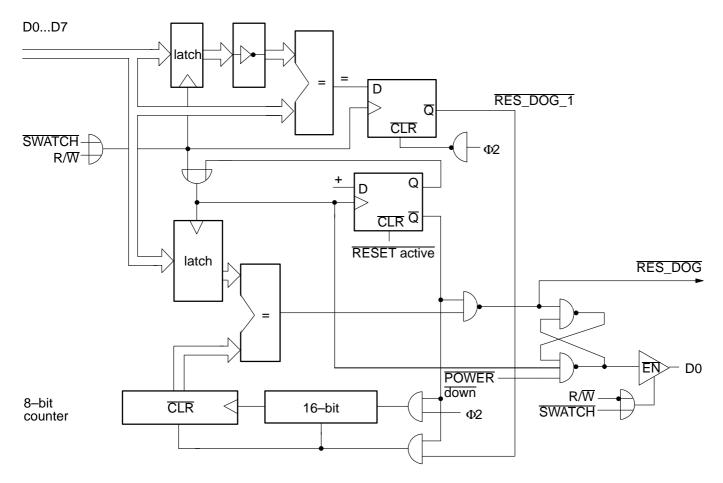

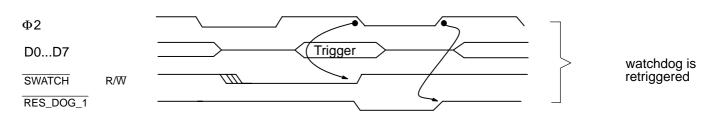

#### 2.14. Watchdog

- not active after Reset

- activated when written, cannot be stopped via software

- to retrigger, the watchdog period negated bit by bit must be rewritten within the preset space of time (first write event is also counted)

- triggers reset, the software can identify if Reset was generated by watchdog

- 16 ms to 4 s time-out for 4 MHz system clock

This counter circuit offers hardware support for software problems. It is disabled after reset and enabled with the first write of the desired time value into its register. The value to program is calculated by

$$n = T_{WD} * f_{system} / 65536 - 1$$

with n = watchdog counter value to be programmed for  $T_{WD}$  = the desired watchdog time and  $f_{system}$  = system frequency.

#### Remarks:

- a) To prevent the generation of a 'RESET' by the watchdog before it could be retriggered by the software, watchdog counter values less than 2 should not be programmed.

- b) The system clock as input of the watchdog counter is influenced by the system clock prescaler, determining the CPU speed (register addr. 200 H).

Software can't stop this counter but has to retrigger it by writing the inverted value (one's complement) of the preceding written pattern into its register, which makes unwanted retrigger loops of disturbed software unlikely. These writes have to occur within the time frame (8 ms to 2 s at 8 MHz system clock), defined with the first write.

If no write with the expected pattern occurs within the programmed time period, the watchdog circuit resets the CCU at the end of the time period. There will also be a watchdog reset if another pattern is written instead of the expected one. The software can detect if a reset was generated by the watchdog: Bit 0 of the watchdog register is '0' if the last reset was generated by the watchdog. This bit is reset only with an external reset, e.g. generated by power-on.

## Examples:

To set a cycle time of 1 second with 8 MHz system clock the value is 121. This value is calculated as follows:

system frequency: 8 MHz watchdog cycle time: 65536 / 8 MHz = 8.192 ms, counter value: 1 s / 8.192 ms = 122.07. The nearest integer value is 122. Because a 0 loaded into the counter divides by 1, already, the watchdog counter has to be programmed with 122-1 = 121. With the formula above

```

n = 121 = 1s * 8 MHz/65536 - 1

```

The software sequences in Assembler could look like this:

#### Definitions:

### Example 1:

During initialization the watchdog is filled with the desired time-value:

In the main loop of the program the watchdog has to be retriggered cyclically:

```

LDA watchdog_value

EOR #FFH ;invert bits

STA watchdog_address

STA watchdog_value ;memorize new

; watchdog pattern

```

#### Example 2:

If an interrupt function occurs cyclically, one value may be programmed in the interrupt service routine, while the other is written in the main loop. So both the continuity of executing the interrupt service and the main loop are checked:

During initialization the watchdog shadow variable is filled with the desired time-value:

```

LDA #WATCHDOG_TIME

STA watchdog_value ;memorize ; watchdog pattern

```

# Sequence in the interrupt function:

```

LDA watchdog_value

CMP #WATCHDOG_TIME

BEQ SKIP_IRQ_WD

;

STA watchdog_address

EOR #$FF

STA watchdog_value

SKIP_IRQ_WD

```

#### Sequence in the main loop:

```

LDA watchdog_value

CMP #WATCHDOG_TIME

BNE SKIP_WD;

STA watchdog_address

EOR #$FF

STA watchdog_value

SKIP_WD

```

#### Remark:

It is important to program the watchdog register with the new value before this value is memorized in the shadow variable, because this procedure could be interrupted by the interrupt, which will program the watchdog with the complementary value.

Fig. 2-17: Watchdog

Fig. 2-18: Timing watchdog

#### 2.15. IR-Input

The IR-interface consists of two parallel edge detectors which trigger the rising and falling edge. The respective state of the rising edge triggered flip-flop can be read from D0 (triggered positively), or D1 (triggered negatively). Any read event via the CPU deletes both flip-flops. D2 reflects the status of the IR pin, D3 to D7 are set to 0.

If the CPU is switched off, the IR-Interface is no longer available, as the IR pin is used as output for the interrupt controller. For use as an emulator this function has to be rebuilt externally. The I/O-address designed for the IR-INPUT is treated as an external address when the CPU is switched off, so that the software can remain untouched.

Fig. 2-19: IR input

#### 2.16. Mask Options

There are two mask options:

OSC option: if this option is set,  $X_1$  and  $X_2$  can be

used as clock input and output or as XTAL pins, (depending on control

word bit 5)

RES option: if this option is set, the reset sources

Power on and Clock Supervision are disabled with bit 0 of the test register 2FFH. Default = enabled).

In the production version none of the options is set, in the EMU version both are set.

| 3. Definit      | ions                                | 21AH         | IM-Bus 1 slave 3, IM-Bus address 04            |

|-----------------|-------------------------------------|--------------|------------------------------------------------|

|                 |                                     | 21CH         | Interrupt controller control byte              |

|                 |                                     | 21DH         | Interrupt controller return byte               |

| 3.1. Interi     | rupt Definitions                    | 21EH         | Interrupt controller priorities source 0 & 1   |

| lata uu sat     | Course Vester (levy high hyde)      | 21FH         | Interrupt controller priorities source 2 & 3   |

| Interrupt       | Source Vector (low, high byte)      | 220H         | Interrupt controller priorities source 4 & 5   |

| 0               | TIMER1 FFF6, FFF7                   | 221H         | Interrupt controller priorities source 6 & 7   |

| 1               | TIMER2 FFF4, FFF5                   |              |                                                |

| 2               | TIMER3 FFF2, FFF3                   | 222H         | Timer 1 control byte 1                         |

| 3               | IM-BUS1, Master FFF0, FFF1          | 223H         | Timer 1 control byte 2                         |

| 4               | IM-BUS1, Slave FFEE, FFEF           | 224H         | Timer 1 control byte 3                         |

| 5               | IM-BUS2, Master FFEC, FFED          | 225H         | Timer 1 prescaler low byte                     |

| 6               | IM-BUS2, Slave FFEA, FFEB           | 226H         | Timer 1 prescaler high byte                    |

| 7               | P87 FFE8, FFE9                      | 228H         | Timer 1 accu low byte                          |

| RESET           | FFFC, FFFD                          | 229H         | Timer 1 accu high byte                         |

|                 |                                     | 22AH         | Timer 1 adder low byte                         |

|                 |                                     | 22BH         | Timer 1 adder high byte                        |

| 3.2. Mem        | ory Mappings                        | 22CH         | Timer 2 control byte 1                         |

|                 |                                     | 22DH         | Timer 2 control byte 2                         |

| RAM             | 0000H to 01FFH Page 0, 1            | 22EH         | Timer 2 control byte 3                         |

|                 | 0300H to 063FH Page 3, 4, 5, 6      | 22FH         | Timer 2 prescaler low byte                     |

| ROM             | 8000H to FFFFH (CCU3001 only)       | 230H<br>232H | Timer 2 prescaler high byte                    |

|                 |                                     | 232H         | Timer 2 accu low byte                          |

| Control         | FFF9                                | 233H<br>234H | Timer 2 accu high byte Timer 2 adder low byte  |

| byte            |                                     | 234H<br>235H | Timer 2 adder low byte Timer 2 adder high byte |

| I/O             | 0200 to 02FF                        | 25511        | Timer 2 adder high byte                        |

| 1/0             | 0200 to 021 1                       | 236H         | Timer 3 control byte 1                         |

|                 |                                     | 237H         | Timer 3 control byte 2                         |

| 3.3. I/O D      | efinitions                          | 238H         | Timer 3 control byte 3                         |

| ۸ ما ما بره م م | Function                            | 239H         | Timer 3 prescaler low byte                     |

| Address         | Function                            | 23AH         | Timer 3 prescaler high byte                    |

| 200H            | Clock frequency                     | 23CH         | Timer 3 accu low byte                          |

| 20011<br>201H   | Control register                    | 23DH         | Timer 3 accu high byte                         |

| 20111<br>202H   | Watchdog                            | 23EH         | Timer 3 adder low byte                         |

| 202H            | Port 1 Data                         | 23FH         | Timer 3 adder high byte                        |

| 204H            | Direction Register Port 1           | 240H         | Port 6 Data                                    |

| 205H            | Port 2 Data                         | 241H         | Direction Register Port 6                      |

| 206H            | Direction Register Port 2           | 242H         | Port 7 Data                                    |

| 207H            | Port 3 Data                         | 243H         | Direction Register Port 7                      |

| 208H            | Direction Register Port 3           | 244H         | Port 8 Data                                    |

| 209H            | Port 4 Data                         | 245H         | Direction Register Port 8                      |

| 20AH            | Port 5 Mode Register                | 246H         | IM-Bus 2 control & status                      |

| 20BH            | Port 5 Direction Register           | 247H         | IM-Bus 2 transfer rate                         |

| 20CH            | Port 5 Data                         | 249H         | IM-Bus 2 master address                        |

| 20DH            | IR-Input                            | 24AH         | IM-Bus 2 master data low                       |

| 20FH            | Port 7 Mode Register                | 24BH         | IM-bus 2 master data high                      |

| 210H            | IM-Bus 1 control and status         | 24CH         | IM-bus 2 slave 1, IM address 02                |

| 211H            | IM-Bus 1 data transfer rate         | 24EH         | IM-bus 2 slave 2, IM address 03                |

| 213H            | IM-Bus 1 master address             | 250H         | IM-bus 2 slave 3, IM address 04                |

| 214H            | IM-Bus 1 master data low byte       | 2E0H         | External addresses, used for EMU boards        |

| 215H            | IM-Bus 1 master data high byte      | to 2E7H      |                                                |

| 216H            | IM-Bus 1 slave 1, IM address 02     | 2FEH         | Reserved, do not use                           |

| 218H            | IM-Bus 1 slave 2, IM-Bus address 03 | 2FFH         | Reserved for testing purposes                  |

|                 |                                     |              |                                                |

## 4. Specifications

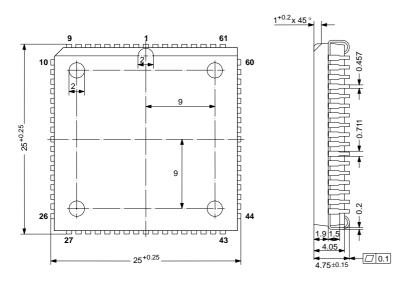

## 4.1. Outline Dimensions

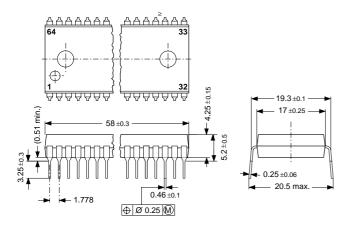

**Fig. 4–1:** 68-Pin Plastic Leaded Chip Carrier Package **(PLCC68)**Weight approximately 4.8 g Dimensions in mm

VSUP GND P67 Х2 P65 VStand-by RES P62 DAT IM1 ID\_IM1 68 67 66 65 64 63 62 61 2 1 DAT\_IM2 [10 P87/INT ID\_IM2 [11 P83 59 Clk\_IM2 12 58 P82 CCU 3000, CCU 3001 TIMER1 13 P81 TIMER2 14 P80 56 TIMER3 15 55 P77 IR [16 54 P76 P4 (R/W) [17 P75 53 P10 (D0) [18 P74 P11 (D1) [19 51 P73 P12 (D2) [20 P72 P13 (D3) [21 P71 49 P14 (D4) [22 P70 P15 (D5) 23 P55 P16 (D6) 24 46 P54 P17 (D7) [25 45 P53 P20 (A0) [26 P52 P21 (A1) P51 P22 (A2) P50 P23 (A3) P37 (A15) P24 (A4) P36 (A14) P25 (A5) P26 (A6) P27 (A7) P33 (A11) P31 (A9)

Fig. 4-2: Pinning of the CCU 3000, CCU 3001 in PLCC68 package

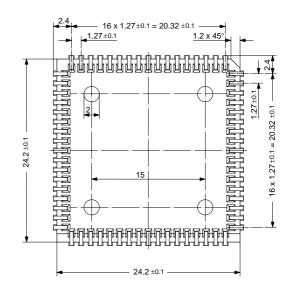

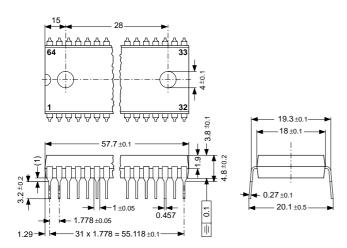

Fig. 4–3: 64-Pin Plastic Shrink Dual Inline Package (PSDIP64)<sup>1)</sup> Weight approximately 9.0 g Dimensions in mm

Fig. 4–4: 64-Pin Plastic Shrink Dual Inline Package (PSDIP64F)<sup>2)</sup> Weight approximately 9.0 g Dimensions in mm

1) PSDIP64 = Manufactured in Freiburg

2) PSDIP64F = Second Source

## 4.2. Pin Configuration

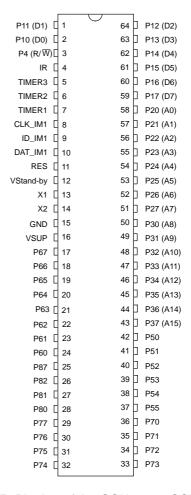

**Fig. 4–5:** Pinning of the CCU 3000, CCU 3001 in PSDIP64 and PSDIP64F package

## 4.3. Pin Connections and Short Descriptions

DA = IM bus data line of external devices

ID = IM bus ident line of external devices

CL = IM bus clock line of external devices

X = obligatory; connections depend on application

| Pin No.        |                | Con- I:                          | l:<br>Input  | Pin Name              | Short Description                 |  |

|----------------|----------------|----------------------------------|--------------|-----------------------|-----------------------------------|--|

| 68-pin<br>PLCC | 64–pin<br>SDIP | nection                          | O:<br>Output |                       |                                   |  |

| 1              | 16             | +5V                              | 1            | $V_{SUP}$             | Supply Voltage                    |  |

| 2              | 15             | GND                              | I            | GND                   | Ground                            |  |

| 3              | 14             | Crystal                          | I/O          | X2                    | Crystal connector 2               |  |

| 4              | 13             | Crystal                          | I            | X1                    | Crystal connector 1               |  |

| 5              | 12             | +3V to<br>+5V                    | I            | V <sub>Stand-by</sub> | Standby Supply Voltage            |  |

| 6              | 11             | Х                                | I/O          | RES                   | Reset input/Reset output          |  |

| 7              | 10             | DA                               | I/O          | DAT_IM1               | IM bus 1 data signal              |  |

| 8              | 9              | ID                               | 0            | ID_IM1                | IM bus 1 ident signal output      |  |

| 9              | 8              | CL                               | 0            | CLK_IM1               | IM bus 1 clock signal output      |  |

| 10             | _              | DA                               | I/O          | DAT_IM2               | IM bus 2 data signal              |  |

| 11             | _              | ID                               | 0            | ID_IM2                | IM bus 2 ident signal output      |  |

| 12             | _              | CL                               | 0            | CLK_IM2               | IM bus 2 clock signal output      |  |

| 13             | 7              | X                                | I/O          | TIMER1                | Timer 1 signal                    |  |

| 14             | 6              | Х                                | I/O          | TIMER2                | Timer 2 signal                    |  |

| 15             | 5              | X                                | I/O          | TIMER3                | Timer 3 signal                    |  |

| 16             | 4              | external<br>infrared<br>receiver | 1            | IR                    | Infrared signal input             |  |

| 17             | 3              | Х                                | I/O (O)      | P40 (R/W)             | Port 4 bit 0 (CPU read/write)     |  |

| 18             | 2              | Х                                | I/O<br>(I/O) | P10 (D0)              | Port 1 bit 0 (CPU data bus bit 0) |  |

| 19             | 1              | Х                                | I/O<br>(I/O) | P11 (D1)              | Port 1 bit 1 (CPU data bus bit 1) |  |

| 20             | 64             | Х                                | I/O<br>(I/O) | P12 (D2)              | Port 1 bit 2 (CPU data bus bit 2) |  |

| 21             | 63             | Х                                | I/O<br>(I/O) | P13 (D3)              | Port 1 bit 3 (CPU data bus bit 3) |  |

| 22             | 62             | Х                                | I/O<br>(I/O) | P14 (D4)              | Port 1 bit 4 (CPU data bus bit 4) |  |

| 23             | 61             | Х                                | I/O<br>(I/O) | P15 (D5)              | Port 1 bit 5 (CPU data bus bit 5) |  |

| Pin No.        |                | Con-    | l:<br>Input  | 1 111 11011110                 | Short Description                     |  |  |

|----------------|----------------|---------|--------------|--------------------------------|---------------------------------------|--|--|

| 68-pin<br>PLCC | 64-pin<br>SDIP | nection | O:<br>Output |                                |                                       |  |  |

| 24             | 60             | Х       | I/O<br>(I/O) | P16 (D6)                       | Port 1 bit 6 (CPU data bus bit 6)     |  |  |

| 25             | 59             | Х       | I/O<br>(I/O) | P17 (D7)                       | Port 1 bit 7 (CPU data bus bit 7)     |  |  |

| 26             | 58             | Х       | I/O (O)      | P20 (A0)                       | Port 2 bit 0 (CPU address bus bit 0)  |  |  |

| 27             | 57             | Х       | I/O (O)      | P21 (A1)                       | Port 2 bit 1 (CPU address bus bit 1)  |  |  |

| 28             | 56             | Х       | I/O (O)      | P22 (A2)                       | Port 2 bit 2 (CPU address bus bit 2)  |  |  |

| 29             | 55             | Х       | I/O (O)      | P23 (A3)                       | Port 2 bit 3 (CPU address bus bit 3)  |  |  |

| 30             | 54             | Х       | I/O (O)      | P24 (A4)                       | Port 2 bit 4 (CPU address bus bit 4)  |  |  |

| 31             | 53             | Х       | I/O (O)      | P25 (A5)                       | Port 2 bit 5 (CPU address bus bit 5)  |  |  |

| 32             | 52             | Х       | I/O (O)      | P26 (A6)                       | Port 2 bit 6 (CPU address bus bit 6)  |  |  |

| 33             | 51             | Х       | I/O (O)      | P27 (A7)                       | Port 2 bit 7 (CPU address bus bit 7)  |  |  |

| 34             | 50             | Х       | I/O (O)      | P30 (A8)                       | Port 3 bit 0 (CPU address bus bit 8)  |  |  |

| 35             | 49             | Х       | I/O (O)      | P31 (A9)                       | Port 3 bit 1 (CPU address bus bit 9)  |  |  |

| 36             | 48             | Х       | I/O (O)      | P32 (A10)                      | Port 3 bit 2 (CPU address bus bit 10) |  |  |

| 37             | 47             | Х       | I/O (O)      | P33 (A11)                      | Port 3 bit 3 (CPU address bus bit 11) |  |  |

| 38             | 46             | Х       | I/O (O)      | P34 (A12)                      | Port 3 bit 4 (CPU address bus bit 12) |  |  |

| 39             | 45             | Х       | I/O (O)      | P35 (A13)                      | Port 3 bit 5 (CPU address bus bit 13) |  |  |

| 40             | 44             | Х       | I/O (O)      | P36 (A14)                      | Port 3 bit 6 (CPU address bus bit 14) |  |  |

| 41             | 43             | Х       | I/O (O)      | P37 (A15)                      | Port 3 bit 7 (CPU address bus bit 15) |  |  |

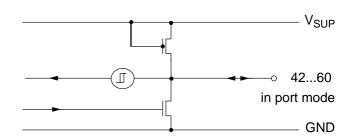

| 42             | 42             | Х       | I/O (O)      | P50 (RD Port 1)                | Port 5 bit 0 (CCU read Port 1)        |  |  |

| 43             | 41             | Х       | I/O (O)      | P51 (WR Port 1)                | Port 5 bit 1 (CCU write Port 1)       |  |  |

| 44             | 40             | Х       | I/O (O)      | P52 (RD Port 2)                | Port 5 bit 2 (CCU read Port 2)        |  |  |

| 45             | 39             | Х       | I/O (O)      | P53 (WR Port 2)                | Port 5 bit 3 (CCU write Port 2)       |  |  |

| 46             | 38             | Х       | I/O (O)      | P54 (RD Port 3)                | Port 5 bit 4 (CCU read Port 3)        |  |  |

| 47             | 37             | Х       | I/O (O)      | P55 (WR Port 3)                | Port 5 bit 5 (CCU write Port 3)       |  |  |

| 48             | 36             | х       | I/O (O)      | P70 (Memory Bank<br>Address 0) | Port 7 bit 0 (Memory Bank Address 0)  |  |  |

| 49             | 35             | Х       | I/O (O)      | P71 (Memory Bank<br>Address 1) | Port 7 bit 1 (Memory Bank Address 1)  |  |  |

| 50             | 34             | Х       | I/O (O)      | P72 (Memory Bank<br>Address 2) | Port 7 bit 2 (Memory Bank Address 2)  |  |  |

| 51             | 33             | Х       | I/O (O)      | P73 (Memory Bank<br>Address 3) | Port 7 bit 3 (Memory Bank Address 3)  |  |  |

| Pir            | n No.          | Con-    | l:<br>Input  | Pin Name                       | Short Description                    |

|----------------|----------------|---------|--------------|--------------------------------|--------------------------------------|

| 68-pin<br>PLCC | 64–pin<br>SDIP | nection | O:<br>Output |                                |                                      |

| 52             | 32             | Х       | I/O (O)      | P74 (Memory Bank<br>Address 4) | Port 7 bit 4 (Memory Bank Address 4) |

| 53             | 31             | Х       | I/O (O)      | P75 (Memory Bank<br>Address 5) | Port 7 bit 5 (Memory Bank Address 5) |

| 54             | 30             | х       | I/O (O)      | P76 (R/W)                      | Port 7 bit 6 (CPU read/write)        |

| 55             | 29             | Х       | I/O (O)      | P77 (Power-Down<br>Control)    | Port 7 bit 7 (Power-Down Control)    |

| 56             | 28             | Х       | I/O          | P80                            | Port 8 bit 0                         |

| 57             | 27             | Х       | I/O          | P81                            | Port 8 bit 1                         |

| 58             | 26             | Х       | I/O          | P82                            | Port 8 bit 2                         |

| 59             | _              | Х       | I/O          | P83                            | Port 8 bit 3                         |

| 60             | 25             | Х       | I/O /I       | P87/INT                        | Port 8 bit 7 /interrupt input        |

| 61             | 24             | Х       | I/O          | P60                            | Port 6 bit 0                         |

| 62             | 23             | X       | I/O          | P61                            | Port 6 bit 1                         |

| 63             | 22             | X       | I/O          | P62                            | Port 6 bit 2                         |

| 64             | 21             | X       | I/O          | P63                            | Port 6 bit 3                         |

| 65             | 20             | Х       | I/O          | P64                            | Port 6 bit 4                         |

| 66             | 19             | Х       | I/O          | P65                            | Port 6 bit 5                         |

| 67             | 18             | Х       | I/O          | P66                            | Port 6 bit 6                         |

| 68             | 17             | Х       | I/O          | P67                            | Port 6 bit 7                         |

### 4.4. Pin Descriptions

CCU 3000, CCU 3001 Pin Descriptions. Pin numbers refer to the 68–pin PLCC housing.

The functions of some pins are influenced by bit 4 of the CCU control register (addr. 201H, copied from FFF9H at reset: CCU control register bit 4 = '1' switches the CCU in *Port Mode*, CCU control register bit 4 = '0' switches the CCU in *Bus Mode*.

In addition, some port bit functions may be changed between *Normal Mode* and *Special Mode* by setting the specific bit in its port mode registers.

Pin 1: V<sub>sup</sub>: +5V power supply

Pin 2: GND: Digital ground

Pin 3: X2: Second Crystal connector

Pin 4: X1: First Crystal connector

Pin 5: V<sub>Stand-bv</sub>: +5V Stand-by Supply Voltage

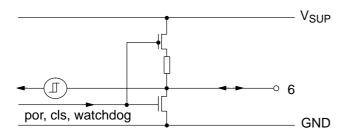

Pin 6: RES\: CCU Reset input / output (open drain)

Pin 7: DAT\_IM1: IM bus 1 data signal (I/O)

Pin 8: ID\_IM1: IM bus 1 ident signal output

Pin 9: CLK\_IM1: IM bus 1 clock signal output

Pin 10: DAT\_IM2: IM bus 2 data signal (I/O)

Pin 11: ID\_IM2: IM bus 2 ident signal output

Pin 12: CLK\_IM2: IM bus 2 clock signal output

Pin 13: TIMER1: Timer 1 signal (I/O)

Pin 14: TIMER2: Timer 2 signal (I/O)

Pin 15: TIMER3: Timer 3 signal (I/O)

Pin 16: IR: Infrared signal input

Pin 17: P40 or R/W\:

in Port Mode: Port 4 Bit 0

in Bus Mode: CPU read/not write output

Pin 18: P10 or data bit 0: in *Port Mode:* Port 1 Bit 0 in *Bus Mode*: CPU data bit 0

Pin 19: P11 or data bit 1: in *Port Mode:* Port 1 Bit 1 in *Bus Mode*: CPU data bit 1 Pin 20: P12 or data bit 2: in *Port Mode:* Port 1 Bit 2 in *Bus Mode*: CPU data bit 2

Pin 21: P13 or data bit 3: in *Port Mode:* Port 1 Bit 3 in *Bus Mode*: CPU data bit 3

Pin 22: P14 or data bit 4: in Port Mode: Port 1 Bit 4 in Bus Mode: CPU data bit 4

Pin 23: P15 or data bit 5: in *Port Mode:* Port 1 Bit 5 in *Bus Mode*: CPU data bit 5

Pin 24: P16 or data bit 6: in *Port Mode:* Port 1 Bit 6 in *Bus Mode*: CPU data bit 6

Pin 25: P17 or data bit 7: in *Port Mode:* Port 1 Bit 7 in *Bus Mode*: CPU data bit 7

Pin 26: P20 or address bit 0: in *Port Mode:* Port 2 Bit 0 in *Bus Mode*: CPU address bit 0

Pin 27 : P21 or address bit 1: in *Port Mode:* Port 2 Bit 1 in *Bus Mode*: CPU address bit 1

Pin 28: P22 or address bit 2: in *Port Mode:* Port 2 Bit 2 in *Bus Mode*: CPU address bit 2

Pin 29: P23 or address bit 3: in *Port Mode:* Port 2 Bit 3 in *Bus Mode*: CPU address bit 3

Pin 30 : P24 or address bit 4: in *Port Mode:* Port 2 Bit 4 in *Bus Mode*: CPU address bit 4

Pin 31 : P25 or address bit 5: in *Port Mode:* Port 2 Bit 5 in *Bus Mode*: CPU address bit 5

Pin 32 : P26 or address bit 6: in *Port Mode:* Port 2 Bit 6 in *Bus Mode*: CPU address bit 6

Pin 33: P27 or address bit 7: in *Port Mode*: Port 2 Bit 7 in *Bus Mode*: CPU address bit 7

Pin 34 : P30 or address bit 8: in *Port Mode:* Port 3 Bit 0 in *Bus Mode*: CPU address bit 8

Pin 35: P31 or address bit 9: in *Port Mode:* Port 3 Bit 1 in *Bus Mode*: CPU address bit 9

Pin 36: P32 or address bit 10: in *Port Mode:* Port 3 Bit 2

in Bus Mode: CPU address bit 10

Pin 37: P33 or address bit 11: in *Port Mode:* Port 3 Bit 3

in Bus Mode: CPU address bit 11

Pin 38: P34 or address bit 12: in *Port Mode:* Port 3 Bit 4

in Bus Mode: CPU address bit 12

Pin 39: P35 or address bit 13: in *Port Mode:* Port 3 Bit 5

in Bus Mode: CPU address bit 13

Pin 40: P36 or address bit 14: in *Port Mode:* Port 3 Bit 6

in Bus Mode: CPU address bit 14

Pin 41: P37 or address bit 15: in *Port Mode:* Port 3 Bit 7

in Bus Mode: CPU address bit 15

Pin 42: P50 or RDPort1\:

in Port Mode:

in *Normal Mode*: Port 5 Bit 0 (open drain output) in *Special Mode*: read port 1 (low active)

in Bus Mode:

in *Normal Mode*: Port 5 Bit 0 (open drain output) in *Special Mode*: read port 1 (low active)

Pin 43: P51 or WRPort1\:

in Port Mode:

in *Normal Mode*: Port 5 Bit 1 (open drain output) in *Special Mode*: write port 1 (low active)

in Bus Mode:

in *Normal Mode*: Port 5 Bit 1 (open drain output) in *Special Mode*: write port 1 (low active)

Pin 44: P52 or RDPort2\:

in Port Mode:

in *Normal Mode*: Port 5 Bit 2 (open drain output) in *Special Mode*: read port 2 (low active)

in Bus Mode:

in *Normal Mode*: Port 5 Bit 2 (open drain output) in *Special Mode*: read port 2 (low active)

Pin 45: P53 or WRPort2\:

in Port Mode:

in *Normal Mode*: Port 5 Bit 3 (open drain output) in *Special Mode*: write port 2 (low active)

in Bus Mode:

in *Normal Mode*: Port 5 Bit 3 (open drain output) in *Special Mode*: write port 2 (low active)

Pin 46: P54 or RDPort3\:

in Port Mode:

in Normal Mode: Port 5 Bit 4 (open drain output) in Special Mode: read port 3 (low active)

in Bus Mode:

in *Normal Mode*: Port 5 Bit 4 (open drain output) in *Special Mode*: read port 3 (low active)

Pin 47: P55 or WRPort3\:

in Port Mode:

in *Normal Mode*: Port 5 Bit 5 (open drain output) in *Special Mode*: write port 3 (low active)

in Bus Mode:

in *Normal Mode*: Port 5 Bit 5 (open drain output) in *Special Mode*: write port 3 (low active)

Pin 48: P70 or Memory Bank Address 0:

in Port Mode:

in Normal Mode: Port 7 Bit 0

in Special Mode: Memory Bank Address 0

in Bus Mode:

in Normal Mode: Port 7 Bit 0

in Special Mode: Memory Bank Address 0

Pin 49: P71 or Memory Bank Address 1:

in Port Mode:

in Normal Mode: Port 7 Bit 1

in Special Mode: Memory Bank Address 1

in Bus Mode:

in Normal Mode: Port 7 Bit 1

in Special Mode: Memory Bank Address 1

Pin 50: P72 or Memory Bank Address 2:

in Port Mode:

in Normal Mode: Port 7 Bit 2

in Special Mode: Memory Bank Address 2

in Bus Mode:

in Normal Mode: Port 7 Bit 2

in Special Mode: Memory Bank Address 2

Pin 51: P73 or Memory Bank Address 3:

in Port Mode:

in Normal Mode: Port 7 Bit 3

in Special Mode: Memory Bank Address 3

in Bus Mode:

in Normal Mode: Port 7 Bit 3

in Special Mode: Memory Bank Address 3

Pin 52: P74 or Memory Bank Address 4:

in Port Mode:

in Normal Mode: Port 7 Bit 4

in Special Mode: Memory Bank Address 4

in Bus Mode:

in Normal Mode: Port 7 Bit 4

in Special Mode: Memory Bank Address 4

Pin 53: P75 or Memory Bank Address 5:

in Port Mode:

in Normal Mode: Port 7 Bit 5

in Special Mode: Memory Bank Address 5

in Bus Mode:

in Normal Mode: Port 7 Bit 5

in Special Mode: Memory Bank Address 5

Pin 54: P76 or inverted CPU R/W\:

in Port Mode:

in Normal Mode: Port 7 Bit 6

in Special Mode: inverted CPU R/W\,

i.e.: low active at read

in Bus Mode:

in Normal Mode: Port 7 Bit 6

in Special Mode: inverted CPU R/W\,

i.e.: low active at read

Pin 55: P77 or Power-down Control:

in Port Mode:

in Normal Mode: Port 7 Bit 7

in Special Mode: Power-down Control External

Memory (high active)

in Bus Mode:

in Normal Mode: Port 7 Bit 7

in Special Mode: Power-down Control External

Memory (high active)

Pin 56: P80: Port 8 Bit 0

Pin 57: P81: Port 8 Bit 1

Pin 58: P82: Port 8 Bit 2

Pin 59: P83: Port 8 Bit 3

Pin 60: P87/INT:

Port 8 Bit 7 and interrupt input (interrupt controller source 7)

Pin 61: P60: Port 6 Bit 0

Pin 62: P61: Port 6 Bit 1

Pin 63: P62: Port 6 Bit 2

Pin 64: P63: Port 6 Bit 3

Pin 65: P64: Port 6 Bit 4

Pin 66: P65: Port 6 Bit 5

Pin 67: P66: Port 6 Bit 6

Pin 68: P67: Port 6 Bit 7

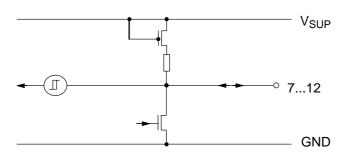

## 4.5. Pin Circuits

Fig. 4-6: X1, X2

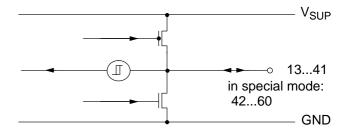

**Fig. 4–10:** P1, P2, P3, Timer (1, 2, 3), IR (Input only), in special mode: P5, P7, P8

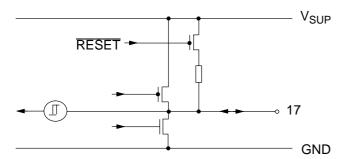

Fig. 4-7: Reset

Fig. 4-11: P5, P6, P7, P8 in port mode

Fig. 4-8: IM bus

Fig. 4-12: R/W, / P4, CCU 3001

Fig. 4-9: R/W, CCU 3000

#### 4.6. Electrical Characteristics

All voltages refer to ground.

# 4.6.1. Absolute Maximum Ratings

| Symbol           | Parameter                     | Pin                                | Min.   | Max.                    | Unit |

|------------------|-------------------------------|------------------------------------|--------|-------------------------|------|

| T <sub>A</sub>   | Ambient Operating Temperature | _                                  | 0      | 65                      | °C   |

| T <sub>S</sub>   | Storage Temperature           | _                                  | -40    | +125                    | °C   |

| V <sub>SUP</sub> | Supply Voltage                | 1                                  | -0.5   | 6                       | V    |

| VI               | Input Voltage                 | 4, 6, 16,<br>13 to 25,<br>42 to 68 | -0.3 V | V <sub>SUP</sub> +0.3 V | _    |

| P <sub>max</sub> | Maximum Power Dissipation     | _                                  | _      | 500                     | mW   |

The total sum of all the sink currents of all ports together must not exceed 80 mA  $I_{outlow}$  and 280 mA  $-I_{out}$  high at any time. Stresses beyond those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions/Characteristics" of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

# **4.6.2. Recommended Operating Conditions** at $T_A = 0$ °C to 65°C

| Symbol           | Parameter       | Pin  | Min. | Тур. | Max. | Unit |

|------------------|-----------------|------|------|------|------|------|

| V <sub>SUP</sub> | Supply Voltage  | 1    | 4.75 | _    | 5.25 | V    |

| f <sub>CLK</sub> | Clock Frequency | 3, 4 | 0.5  | _    | 8    | MHz  |

# **4.6.3. Recommended Crystal Characteristics** at $C_{XTAL1} = C_{XTAL2} = 22 \text{ pF}$ ; $C_{stray} \le 2 \text{ pF}$ ; $C_L \approx 13 \text{ pF}$

| Symbol                          | Parameter                                                | Min. | Тур. | Max.                     | Unit |

|---------------------------------|----------------------------------------------------------|------|------|--------------------------|------|

| T <sub>A</sub>                  | Ambient Operating Temperature                            | -20  | _    | +85                      | °C   |

| fp                              | Parallel Resonance Frequency<br>@ C <sub>L</sub> = 13 pF | _    | 4–8  | -                        | MHz  |

| R <sub>r</sub>                  | Series Resistance                                        | -    | _    | 40 [8MHz]<br>150 [4 MHz] | Ω    |

| C <sub>0</sub>                  | Shunt Capacitance                                        | _    | _    | 7.0                      | pF   |

| C <sub>1</sub>                  | Motional Capacitance                                     | _    | _    | 20                       | fF   |

| Р                               | Rated Drive Level                                        | _    | 0.02 | _                        | mW   |

| f <sub>p</sub> / f <sub>H</sub> | Spurious Frequency Attenuation                           | 20   | _    | _                        | dB   |

# **4.6.4. DC Characteristics** at $T_A$ = 0 °C to 65°C, $V_{SUP}$ = 5V, $f_{CLK}$ = 8 MHz

| Symbol                                      | Parameter                                        | Pin No.                          | Min.                      | Тур.  | Max.                      | Unit | Comment                                         |

|---------------------------------------------|--------------------------------------------------|----------------------------------|---------------------------|-------|---------------------------|------|-------------------------------------------------|

| I <sub>SUP</sub><br>CCU 3000,<br>CCU 3000-I | Supply Current<br>(no external load)             | 1                                | ı                         | 8/16  | 15/30                     | mA   | @ 4/8 MHz                                       |

| I <sub>SUP</sub><br>CCU 3001<br>CCU 3001-I  | Supply Current<br>(no external load)             | 1                                | -                         | 14/28 | 20/40                     | mA   | @ 4/8 MHz                                       |

| V <sub>ILH</sub>                            | Input Low to High Trigger Level                  | 4,6,<br>7–12,<br>13–25,<br>42–68 | 0.38*<br>V <sub>SUP</sub> | 2,05  | 0.56*<br>V <sub>SUP</sub> | V    | Schmitt-Trigger Inputs                          |

| V <sub>IHL</sub>                            | Input High to Low Trigger Level                  |                                  | 0.2*<br>V <sub>SUP</sub>  | 1.15  | 0.29*<br>V <sub>SUP</sub> | V    | Schmitt-Trigger Inputs                          |

| V <sub>IHYST</sub>                          | Input Hysteresis                                 | 4,6,<br>7–25,<br>42–68           | 0.1*<br>V <sub>SUP</sub>  | 0.9   | 0.27*<br>V <sub>SUP</sub> | V    | Schmitt-Trigger Inputs                          |

| V <sub>BOH</sub>                            | Bus Ports and Timer Output<br>High Voltage       | 13–15<br>17–41                   | 2.8                       | -     | _                         | V    |                                                 |

| V <sub>BOL</sub>                            | Bus Ports and Timer Output<br>Low Voltage        |                                  | -                         | _     | 0.4                       | V    |                                                 |

| Івон                                        | Bus Ports and Timer Output<br>High Current       | 13–151<br>7–41                   | _                         | -     | 2                         | mA   |                                                 |

| I <sub>BOL</sub>                            | Bus Ports and Timer Output<br>Low Current        |                                  | _                         | -     | 5                         | mA   |                                                 |

| I <sub>P5OL</sub>                           | P5 Output Low Current                            | 42–47                            | -                         | -     | 5                         | mA   |                                                 |

| I <sub>P6OL</sub>                           | P6 Output Low Current                            | 61–68                            | _                         | _     | 25                        | mA   |                                                 |

| I <sub>P7OL</sub>                           | P7 Output Low Current                            | 48–55                            | -                         | -     | 5                         | mA   |                                                 |

| I <sub>P8OL</sub>                           | P8 Output Low Current                            | 56–60                            | -                         | -     | 5                         | mA   |                                                 |

| I <sub>OHL</sub>                            | Output Leakage Current                           | 42–60                            | _                         | -     | 1                         | μА   |                                                 |

| I <sub>P5P7OH</sub>                         | Output High Current Special<br>Mode, P5 to P7    | 42–55                            | -                         | _     | 2                         | mA   |                                                 |

| V <sub>P5P7OH</sub>                         | Output High Voltage Special<br>Mode, P5 to P7    | 42–55                            | 2.8                       | -     | _                         | V    |                                                 |

| V <sub>OL</sub>                             | Output Low Voltage<br>at I <sub>OL</sub> = 5 mA  | 42–60                            | -                         | -     | 0.4                       | V    |                                                 |

| V <sub>OL</sub>                             | Output Low Voltage<br>at I <sub>OL</sub> = 25 mA | 61–68                            | -                         | -     | 0.55                      | V    |                                                 |

| V <sub>Stby</sub>                           | Stand-by Voltage RAM                             | 5                                | 3                         | -     | -                         | V    |                                                 |

| I <sub>Stby</sub>                           | Stand-by Current RAM                             | 5                                | -                         | -     | 1                         | μА   | @ V <sub>DD</sub> = 0 V, V <sub>Stby</sub> = 5V |

| V <sub>Pow on</sub>                         | Power-on Voltage                                 | 1                                | 4.2                       | -     | 4.75                      | V    |                                                 |

Bus Ports: P1, P2, P3, P4.

#### 4.6.5. Using external devices

To avoid collision on the data bus during direction changes, the CCU data bus out buffers (active during PHI2='1' only) are disabled before the address, the R/W and the  $\overline{R}$ /W line changes ( $t_{DHW} < t_{AH}$ ). This guarantees that no collision happens on the bus if the output drives of the external devices (ROM, RAM, Ports) are controlled with the R/ $\overline{W}$  or  $\overline{R}$ /W signal and a read cycle follows a write cycle.

Important: In a write cycle the data-out drivers of the CCU set up the data bus lines. Then they leave these lines so that no drivers are active on the data bus. A few ns later the R/W or the P5 select signal latch the data into the external device (Port out or Write into RAM). The same signal is used to enable the output drivers of exter-

nal devices for reading so that another few ns later they drive the bus. The DATA BUS is used as DATA MEMORY for a few ns. This is the only way to make sure that, independent from the loads on the CCU address, data and control lines collisions are avoided and a maximum of access time is available for the memory.

IF YOU WANT TO WRITE TO EXTERNAL DEVICES THE DATA BUS MUST BE IN THE TRISTATE MODE DURING WRITE OPERATIONS OF THE CCU. No pull-up or pull-down resistors are allowed.

Even in a good layout the capacitive load on the data bus is approx. 20 pF (2\* pin capacity and layout). Even in the worst case of a 1 M $\Omega$  leakage the time constant is approx. 20  $\mu$ s. The max. time between disabling the bus drivers and the rising edge of R/ $\overline{W}$  is 20 ns.

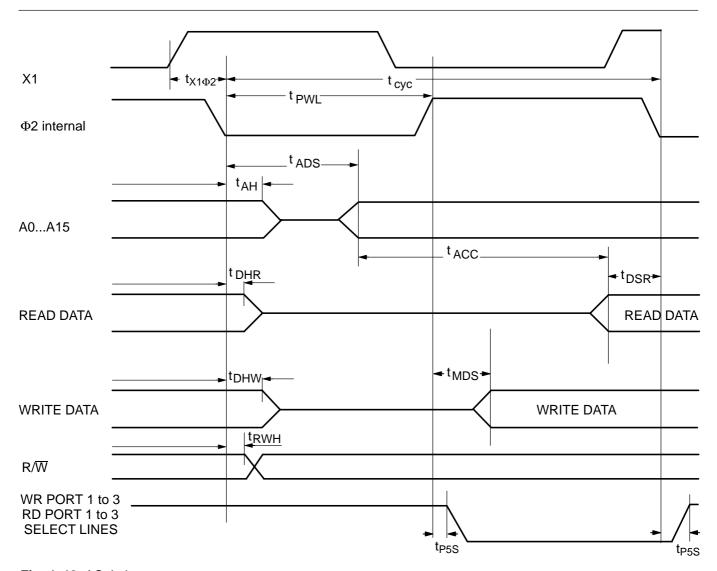

**4.6.6. AC Characteristics** at  $T_A = 0$  °C to 65°C,  $V_{SUP} = 5$  V,  $f_{CLK} = 8$  MHz, **CI = 0 pF External Loads:** add 0.75 ns/pF for controller output lines

| Symbol            | Parameter                               | Pin   | Min. | Max. | Unit |

|-------------------|-----------------------------------------|-------|------|------|------|

| t <sub>cyc</sub>  | Cycle Time (Processor)                  | 3     | 125  | 2000 | ns   |

| t <sub>PWL</sub>  | Pulse Width Low                         | 3     | 60   | 1000 | ns   |

| t <sub>AH</sub>   | Address Hold Time                       | 26–41 | 10   | 22   | ns   |

| t <sub>ADS</sub>  | Address Setup Time Read                 |       | 15   | 34   | ns   |

| t <sub>DSR</sub>  | Data Setup Time Read                    | 18–25 | 20   | -    | ns   |

| t <sub>MDS</sub>  | Write Data Delay                        |       | 10   | 29   | ns   |

| t <sub>DHW</sub>  | Write Data Hold Time                    |       | 9    | 16   | ns   |

| t <sub>DHR</sub>  | Read Data Hold Time                     |       | 10   | -    | ns   |

| t <sub>RWH</sub>  | Read/Write Hold Time                    | 17    | 10   | 24   | ns   |

| t <sub>WRH</sub>  | Read/Write Hold Time (P76 special mode) | 17    | 13   | 34   | ns   |

| t <sub>P5S</sub>  | Delay P1 to P3 Select Lines on P5       | 42–47 | 12   | 26   | ns   |

| t <sub>Χ1Φ2</sub> | Delay X1 to internalΦ2                  | 4     | 7    | 15   | ns   |

| t <sub>Φ2X2</sub> | Delay Φ2 internal to X2                 | 3     | 5    | 10   | ns   |

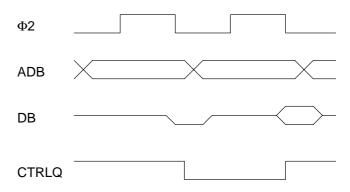

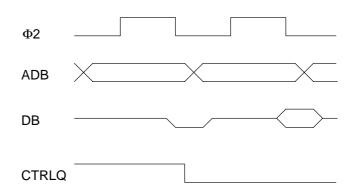

Fig. 4-13: AC timing

#### 4.6.7. IM Bus Waveforms

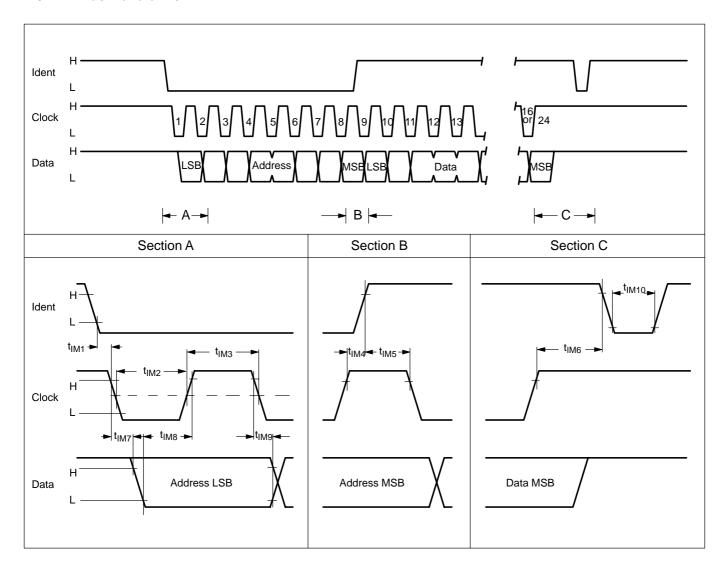

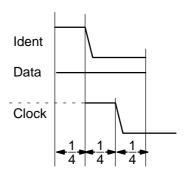

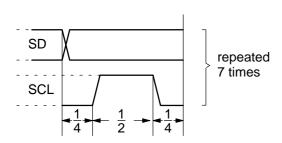

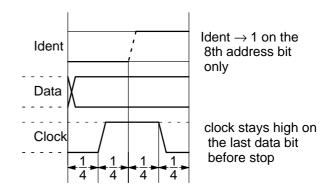

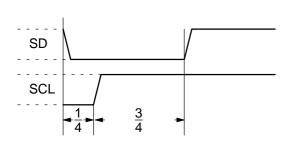

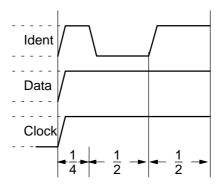

Fig. 4-14: IM bus waveforms

## 4.6.8. Description of the IM Bus

The INTERMETALL Bus (IM bus for short) was designed to control the DIGIT 2000 ICs by the CCU Central Control Unit. Via this bus the CCU can write data to the ICs or read data from them. This means that the CCU acts as a master, whereas all controlled ICs have purely slave status.

The IM bus consists of three lines for the signals Ident (ID), Clock (DL) and Data (D). The clock frequency range is 50 Hz to 1 MHz. Ident and clock are unidirectional from the CCU to the slave ICs, Data is bidirectional. Bidirectionality is achieved by using open-drain outputs. The 2.5 to 1 kOhm pull-up resistor common to all outputs must be connected externally.

The timing of a complete IM bus transaction is shown in Fig. 4–14. In the non-operative state the signals of all three bus lines are High. To start a transaction the CCU sets the ID signal to Low level, indicating an address transmission, and sets the CL signal to Low level as well

as to switch the first bit on the Data line. Then eight address bits are transmitted, beginning with the the LSB. Data takeover in the slave ICs occurs at the positive edge of the clock signal. At the end of the address byte the ID signal switches to High, initiating the address comparison in the slave circuits. In the addressed slave the IM bus interface switches over to Data read or write, because these functions are correlated to the address. Also controlled by the address the CCU now transmits eight or sixteen clock pulses, and accordingly one or two bytes of data are written into the addressed IC or read out from it, beginning with the LSB.

The completion of the bus transaction is signalled by a short Low state pulse of the ID signal. This initiates the storing of the transferred data.

For future software compatibility, the CCU must write a zero into all bits not currently used. When reading undefined or unused bits, the CCU must adopt "don't care" behavior.

## 4.6.9. Recommended Operating Conditions of IM Bus

| Symbol            | Parameter                                  | Pin No.         | Min. | Тур.                               | Max. | Unit |

|-------------------|--------------------------------------------|-----------------|------|------------------------------------|------|------|

| V <sub>IML</sub>  | IM bus Low Voltage                         | Data            | _    | _                                  | 0.8  | V    |

| V <sub>IMH</sub>  | IM bus High Voltage                        | 7, 10           | 2.4  | _                                  | _    | V    |

| R <sub>ext</sub>  | External Pull-Up Resistor                  |                 | 1    | -                                  | 2.5  | kΩ   |

| I <sub>IMOL</sub> | IM bus Output Low Current                  |                 | _    | -                                  | 5    | mA   |

| $f_{\PhiI}$       | Φl IM bus Clock Frequency                  | Clock           | 0.05 | -                                  | 1000 | kHz  |

| t <sub>IM1</sub>  | ΦI Clock Delay Time after IM bus Ident     | 9, 12           | > 0  | -                                  | _    | -    |