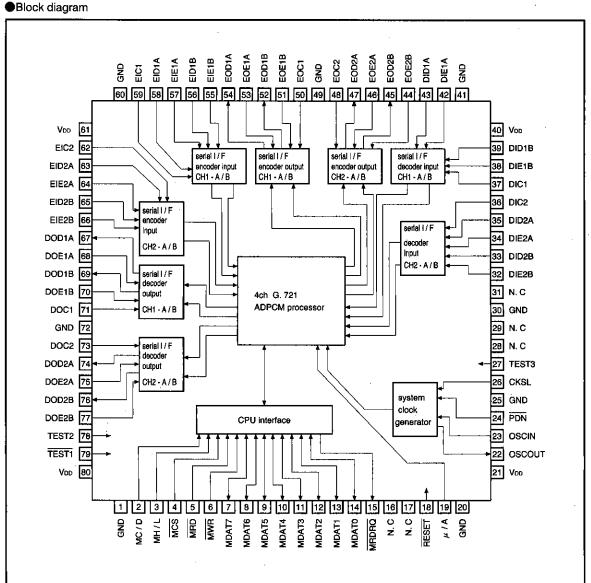

# 4-channel ADPCM transcoder for digital cordless telephone base stations **BU8710AKS**

This is an ADPCM transcoder which conforms to the G.721 standards listed in the 1988 edition of the CCITT recommendations. Simultaneous processing of four encoder and decoder channels is possible, enabling superb affinity with the quadruple TDMA which is a standard for PHS (personal handy phone) systems. In turn, this enables voice processing units for individual base stations in the public telephone network to be configured on single chips.

# ApplicationsPHS base stations

#### ●Features

- Can be connected to μ-law and A-law PCM codec through a serial interface. (Both long frames and short frames can be accommodated.)

- Various functions can be controlled through a CPU interface.

- 3) An internal power save mode can be controlled separately for individual channels. (Separate encoder and decoder control are possible.) In addition, external pin control enables power consumption to be reduced for the chip as a whole.

- An internal muting function can be controlled separately for individual channels. (Separate encoder and decoder control are possible.)

- An internal function silence detection is provided, which can be controlled separately for individual channels. (Applicable only to encoders.)

- An internal background noise generation function is provided, which can be controlled separately for individual channels. (Applicable only to decoders.)

- 7) The G.711 ( $\mu$ -law or A-law) output level can be attenuated freely on individual channels.

- An internal 64kbps data through mode is provided, which can be controlled separately for individual channels.

- 9) Internal 32kbps and 64kbps data loop back modes are provided, which can be controlled separately for individual channels.

- 10) An internal clock generator circuit is provided.

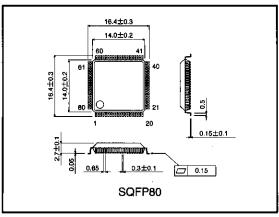

- 11) SQFP 80 pin package is used.

Celluar phones/PHS/Pagers

# ●Absolute maximum ratings (Ta=25℃)

| Parameter             | Symbol      | Limits              | Unit |

|-----------------------|-------------|---------------------|------|

| Power supply voltage  | <b>V</b> DD | 7.0                 | V    |

| Input voltage         | Vin         | Vss -0.3 ~ Vpp +0.3 | ٧    |

| Output voltage        | Vout        | Vss -0.3 ~ Vpp +0.3 | V    |

| Operating temperature | Topr        | <b>−25 ~ 75</b>     | ూ    |

| Storage temperature   | Tstg        | <b>−55 ~ 125</b>    | ొ    |

# ●Recommended operating range (Ta=25°C)

| Parameter                      | Symbol | Min. | Тур.   | Max. | Unit | Conditions |

|--------------------------------|--------|------|--------|------|------|------------|

| Power supply voltage           | Voo    | 3.6  | 5.0    | 5.5  | ٧    |            |

| Master clock input frequency 1 | fcLK1  | 12.2 | 12.288 | 12.4 | MHz  | CKSL="L"   |

| Master clock input frequency 2 | fclk2  | 19.0 | 19.2   | 19.4 | MHz  | CKSL="H"   |

| Master clock duty ratio        | foury  | 40   | 50     | 60   | %    |            |

O Not designed for radiation resistance.

# Pin descriptions

| Pin No. | Pin Name    | 1/0 | Format | Function                               | Description                                                                                                                |  |  |  |  |

|---------|-------------|-----|--------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 24      | PDN         | l   | CMOS   | Power save pin                         | When this pin goes LOW, the power save mode is entered, and line current consumption is minimized.                         |  |  |  |  |

| 23      | OSCIN       | 1   | CMOS   | Clock generator input                  | A crystal resonator is connected to this pin to                                                                            |  |  |  |  |

| 22      | OSCOUT      | 0   | CMOS   | Clock generator output                 | configure a generator circuit.                                                                                             |  |  |  |  |

| 26      | CKSL        | I   | CMOS   | Clock input frequency setting          | This is used to set the clock input frequency. At LOW, the frequency is 12.288 MHz, and at HIGH, the frequency is 19.2 MHz |  |  |  |  |

| 18      | RESET       | J   | CMOS   | System reset                           | When this pin goes LOW, internal circuits are initialized.                                                                 |  |  |  |  |

| 19      | μ/ <b>A</b> | 1   | CMOS   | Switches between μ - law, A - law      | This switches the G.711 format. At HIGH, the format is $\mu$ - law, and at LOW, A-law.                                     |  |  |  |  |

| 2       | MC / D      | 1   | CMOS   | Switches between CPU commands and data |                                                                                                                            |  |  |  |  |

| 3       | MH/L        | ı   | CMOS   | Switches between CPU MSB and LSB       |                                                                                                                            |  |  |  |  |

| 4       | MCS         | 1   | CMOS   | CPU Chip Select                        |                                                                                                                            |  |  |  |  |

| 5       | MRD         | I   | CMOS   | CPU Read Enable                        |                                                                                                                            |  |  |  |  |

| 6       | MWR         | 1   | CMOS   | CPU Write Enable                       |                                                                                                                            |  |  |  |  |

| 7       | MDAT7       |     |        |                                        |                                                                                                                            |  |  |  |  |

| 8       | MDAT6       |     |        |                                        | This is a CPU interface with                                                                                               |  |  |  |  |

| 9       | MDAT5       |     |        |                                        | 4-bit/8-bit parallel specifications. (See section (3), "Description of functions".)                                        |  |  |  |  |

| 10      | MDAT4       | 10  | CMOS   | CPU I/O data bus                       | , , , , , , , , , , , , , , , , , , , ,                                                                                    |  |  |  |  |

| 11      | MDAT3       |     | UNIUS  | OFO I/O data pus                       |                                                                                                                            |  |  |  |  |

| 12      | MDAT2       |     |        |                                        |                                                                                                                            |  |  |  |  |

| 13      | MDAT1       |     |        |                                        |                                                                                                                            |  |  |  |  |

| 14      | MDAT0       |     |        |                                        |                                                                                                                            |  |  |  |  |

| 15      | MRDRQ       | 0   | CMOS   | CPU data read request                  |                                                                                                                            |  |  |  |  |

# Pin descriptions

| Pin No. | Pin Name | 1/0 | Format     | Function                    | Description                                                                |

|---------|----------|-----|------------|-----------------------------|----------------------------------------------------------------------------|

| 58      | EID1A    | 1   | смоѕ       | CH1-A encoder input data    |                                                                            |

| 57      | EIE1A    | I   | CMOS       | CH1-A encoder input enable  |                                                                            |

| 56      | EID1B    | ı   | CMOS       | CH1-B encoder input data    | These are the dual-system encoder input interface for Channel 1, A and B.  |

| 55      | EIE1B    | ı   | смоѕ       | CH1-B encoder input enable  |                                                                            |

| 59      | EIC1     | 1   | смоѕ       | CH1 encoder input clock     |                                                                            |

| 63      | EID2A    | ı   | CMOS       | CH2-A encoder input data    |                                                                            |

| 64      | EIE2A    | ı   | CMOS       | CH2-A encoder input enable  |                                                                            |

| 65      | EID2B    | I.  | CMOS       | CH2-B encoder input data    | These are the dual-system encoder input interface for Channel 2, A and B.  |

| 66      | EIE2B    | Ī   | смоѕ       | CH2-B encoder input enable  |                                                                            |

| 62      | EIC2     | ı   | смоѕ       | CH2 encoder input clock     |                                                                            |

| 43      | DID1A    | ı   | CMOS       | CH1-A decoder input data    |                                                                            |

| 42      | DIE1A    | I   | смоѕ       | CH1-A decoder input enable  | <b>」</b>                                                                   |

| 39      | DID1B    | 1   | смоѕ       | CH1-B decoder input data    | These are the dual-system decoder input interface for Channel 1, A and B.  |

| 38      | DIE1B    | 1   | CMOS       | CH1-B decoder input enable  |                                                                            |

| 37      | DIC1     | 1   | CMOS       | CH1 decoder input clock     |                                                                            |

| 35      | DID2A    | ı   | CMOS       | CH2-A decoder input data    |                                                                            |

| 34      | DIE2A    | ı   | CMOS       | CH2-A decoder input enable  |                                                                            |

| 33      | DID2B    | ı   | CMOS       | CH2-B decoder Input data    | These are the dual-system decoder input interface for Channel 2, A and B.  |

| 32      | DIE2B    | ī   | смоѕ       | CH2-B decoder input enable  |                                                                            |

| 36      | DIC2     | ı   | смоѕ       | CH2 decoder input clock     |                                                                            |

| 54      | EOD1A    | 0   | CMOS<br>TS | CH1-A encoder output data   |                                                                            |

| 53      | EOE1A    | ı   | CMOS       | CH1-A encoder output enable |                                                                            |

| 52      | EOD1B    | 0   | CMOS<br>TS | CH1-B encoder output data   | These are the dual-system encoder output interface for Channel 1, A and B. |

| 51      | EOE1B    | ì   | CMOS       | CH1-B encoder output enable |                                                                            |

| 50      | EOC1     | I   | CMOS       | CH1 encoder output clock    |                                                                            |

| 47      | EOD2A    | 0   | CMOS<br>TS | CH2-A encoder output data   |                                                                            |

| 46      | EOE2A    | ı   | CMOS       | CH2-A encoder output enable | <u> </u>                                                                   |

| 45      | EOD2B    | О   | CMOS<br>TS | CH2-B encoder output data   | These are the dual-system encoder output interface for Channel 2, A and B  |

| 44      | EOE2B    | 1   | CMOS       | CH2-B encoder output enable |                                                                            |

| 48      | EOC2     | ı   | CMOS       | CH2 encoder output clock    |                                                                            |

| 67      | DOD1A    | 0   | CMOS<br>TS | CH1-A decoder output data   |                                                                            |

| 68      | - DOE1A  | 1   | смоѕ       | CH1-A decoder output enable | <u></u>                                                                    |

| 69      | DOD1B    | 0   | CMOS<br>TS | CH1-B decoder output data   | These are the dual-system decoder output interface for Channel 1, A and B  |

| 70      | DOE1B    | ı   | CMOS       | CH1-B decoder output enable |                                                                            |

| 71      | DOC1     | 1   | CMOS       | CH1 decoder output clock    |                                                                            |

TS ··· 3-state output

# Pin descriptions

| Pin No. | Pin Name | 1/0 | Format     | Function                    | Description                                                                |

|---------|----------|-----|------------|-----------------------------|----------------------------------------------------------------------------|

| 74      | DOD2A    | 0   | CMOS<br>TS | CH2-A decoder output data   |                                                                            |

| 75      | DOE2A    | 1.  | смоѕ       | CH2-A decoder output enable |                                                                            |

| 76      | DOD2B    | 0   | CMOS<br>TS | CH2-B decoder output data   | These are the dual-system decoder output interface for Channel 2, A and B. |

| 77      | DOE2B    | I   | CMOS       | CH2-B decoder output enable |                                                                            |

| 73      | DOC2     | Ī   | смоѕ       | CH2 decoder output clock    |                                                                            |

| 79      | TEST1    | I   | CMOS       | Test input 1                | This is normally set to HIGH.                                              |

| 78      | TEST2    | . 1 | CMOS       | Test input 2                |                                                                            |

| 27      | TEST3    | 1   | CMOS       | Test input 3                | These are normally set to LOW.                                             |

| 21      |          |     |            |                             |                                                                            |

| 40      | \ ,,.    |     |            | − Voo pin                   |                                                                            |

| 61      | Von      | _   | -          |                             |                                                                            |

| 80      | 1        |     |            |                             |                                                                            |

| 1       |          |     |            |                             |                                                                            |

| 20      |          |     |            |                             |                                                                            |

| 25      |          |     |            |                             |                                                                            |

| 30      | CND      |     |            | 0117                        |                                                                            |

| 41      | GND      | _   | _          | GND pin                     |                                                                            |

| 49      |          |     |            |                             |                                                                            |

| 60      |          |     |            |                             |                                                                            |

| 72      |          |     |            |                             |                                                                            |

TS ··· 3-state output

# Electrical characteristics

DC characteristics (Unless otherwise noted :  $Ta=25^{\circ}C$ ,  $V_{DD}=5.0V$ )

| Parameter              | Symbol | Min. | Тур. | Max. | Unit | Conditions                                         |

|------------------------|--------|------|------|------|------|----------------------------------------------------|

| Circuit current 1      | IDD1   | _    | 30.0 | 50.0 | mA   | fcuk =12.288MHz ; square waveform input from OSCIN |

| Circuit current 2      | lDD2   | _    | _    | 100  | μΑ   | PDN=LOW, all other input pins fixed at HIGH or LOW |

| "H" input voltage      | ViH    | 4.0  | _    | Voo  | V    |                                                    |

| "L" input voltage      | VIL    | Vss  | _    | 1.0  | V    |                                                    |

| "H" input current      | lan    | -10  | _    |      | μA   | V <sub>IH</sub> =V <sub>DD</sub>                   |

| "L" input current      | lı.    | _    |      | 10   | μА   | V <sub>IL</sub> =V <sub>SS</sub>                   |

| "H" Output voltage     | Vон    | 4.9  |      | _    | ٧    | IOH =0mA                                           |

| "L" Output voltage     | Vol    | _    | _    | 0.1  | ٧    | loL =0mA                                           |

| "H" Output current     | Іон    | _    | _    | -1.0 | mA   | V <sub>OH</sub> = V <sub>DD</sub> -0.4V            |

| "L" Output current     | lor    | 3.2  |      | _    | mA   | Vol. =0.4V                                         |

| Output leakage current | ILKG   |      | _    | 10   | μA   |                                                    |

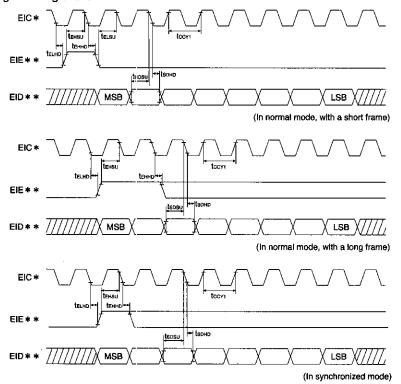

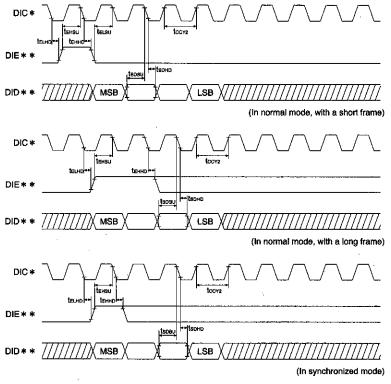

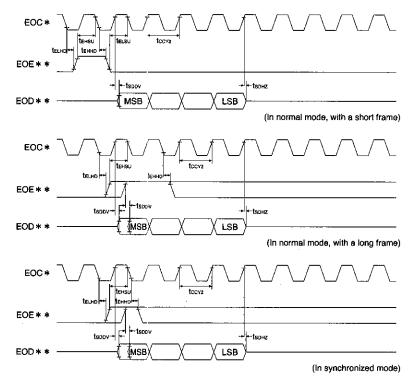

AC characteristics (Unless otherwise noted: Ta=25°C; V<sub>00</sub>=5.0V)

| Parameter                                      | Symbol | Min. | Тур. | Max.  | Unit | Conditions          |

|------------------------------------------------|--------|------|------|-------|------|---------------------|

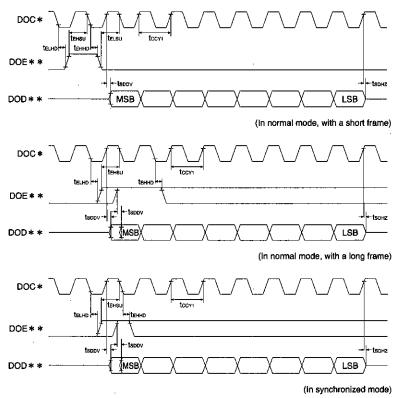

| Serial propagation clock cycle 1               | tccyı  | 125  | _    | 15625 | ns   | See Figures 2 and 5 |

| Serial propagation clock cycle 2               | toov2  | 125  | _    | 31250 | ns   | See Figures 3 and 4 |

| Setup time for enable input HIGH               | tensu  | 15   | -    | _     | ns   | See Figures 2 to 5  |

| Hold time for enable input HIGH                | tehhd  | 15   | _    | -     | ns   | See Figures 2 to 5  |

| Setup time for enable input LOW                | telsu  | 15   | _    |       | ns   | See Figures 2 to 5  |

| Hold time for enable input LOW                 | telho  | 30   | _    |       | ns   | See Figures 2 to 5  |

| Setup time for serial data input               | tsosu  | 15   | _    | _     | ns   | See Figures 2 and 3 |

| Hold time for serial data input                | tsphp  | 15   | _    | _     | ns   | See Figures 2 and 3 |

| Serial data output drive delay time            | tsdov  | _    |      | 60    | ns   | See Figures 4 and 5 |

| Serial data output release time                | tsonz  | _    | _    | 50    | ns   | See Figures 4 and 5 |

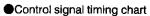

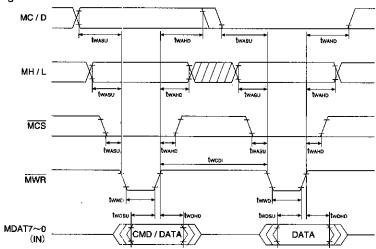

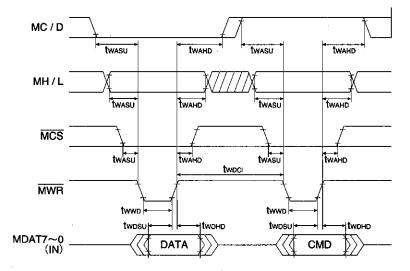

| Setup time for MWR vs. various control timings | twasu  | 15   |      | _     | ns   | See Figures 6 to 9  |

| Hold time for MWR vs. various control timings  | twand  | 15   | _    | _     | ns   | See Figures 6 to 9  |

| MWR pulse width                                | twwp   | 50   |      | -     | ns   | See Figures 6 to 9  |

| Setup time for MWR vs. write data              | twosu  | 15   | _    |       | ns   | See Figures 6 to 9  |

| Hold time for MWR vs. write data               | twoHD  | 15   | _    |       | ns   | See Figures 6 to 9  |

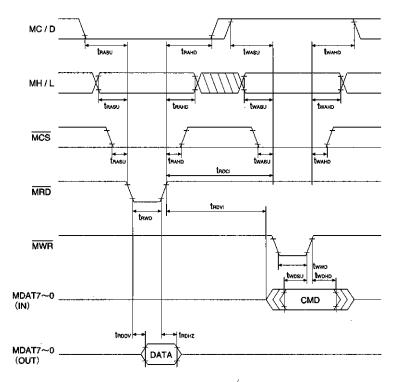

| Setup time for MRD vs. various control timings | trasu  | 15   | _    | _     | ns   | See Figures 7 and 9 |

| Hold time for MRD vs. various control timings  | trahd  | 15   | _    | _     | ns   | See Figures 7 and 9 |

| MRD pulse width                                | trwo   | 50   | -    | _     | ns   | See Figures 7 and 9 |

| MRD vs. read data drive time                   | troov  | _    | _    | 40    | ns   | See Figures 7 and 9 |

| MRD vs. read data release time                 | tronz  | -    | _    | 40    | ns   | See Figures 7 and 9 |

| Data write interval after command/data writing | twooi  | 100  | _    | _     | ns   | See Figure 6        |

| Command write interval after data writing      | twoci  | 900  | _    | _     | กร   | See Figure 8        |

| Data read interval after command writing       | tricoi | 100  | _    | _     | ns   | See Figure 7        |

| Command write interval after data reading      | troci  | 100  | _    | _     | ns   | See Figure 9        |

| Data read interval after data reading          | trooi  | 100  | -    | _     | ns   | See Figure 7        |

| Data read interval after written data release  | tovai  | 40   | _    | _     | ns   | See Figure 7        |

| Write data drive interval after data reading   | taovi  | 40   | _    |       | ns   | See Figure 9        |

<sup>\*</sup> The values for AC characteristics were tested at the timing shown below.

Fig. 1

The values for AC characteristics which apply to output pins were tested with a load capacitance of 50 pF connected.

# Input/output signal timing charts

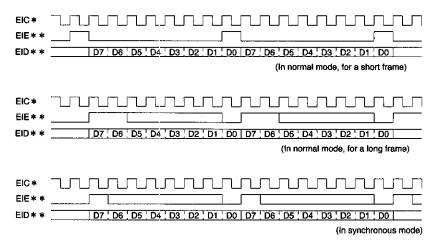

Fig. 2 Encoder input timings

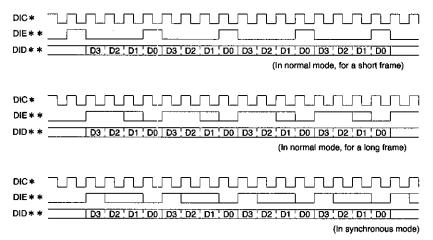

Fig. 3 Decoder input timings

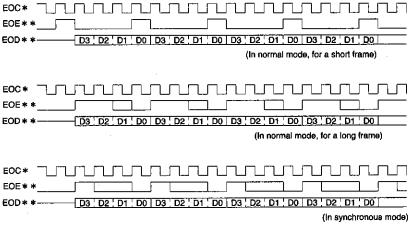

Fig. 4 Encoder output timings

108

ROHM

Fig. 5 Decoder output timings

Note: In Figures 2 to 5, when the 64kbps data through mode is set, the normal 4-bit output encoder output is equivalent to the timing of the decoder 8-bit output (corresponding to Figure 5), and the normal 4-bit input decoder input is equivalent to the timing of the encoder 8-bit input (corresponding to Figure 2).

# Correspondence between encoder and decoder input pins

| Channel | EIE** | EID** | EIC** | DIE** | DID** | DIC* |  |

|---------|-------|-------|-------|-------|-------|------|--|

| 1 - A   | EIE1A | EID1A | FICA  | DIE1A | DID1A | DIC1 |  |

| 1 - B   | EIE1B | EID1B | EIC1  | DIE1B | DID1B |      |  |

| 2 - A   | EIE2A | EID2A | EIC2  | DIE2A | DID2A | DIC2 |  |

| 2 - B   | EIE2B | EID2B | EICZ  | DIE2B | DID2B | DICZ |  |

#### Correspondence between encoder and decoder output pins

| Channel | EOE** | EOD** | EOC* | DOE** | DOD** | DOC* |  |

|---------|-------|-------|------|-------|-------|------|--|

| 1 - A   | EOE1A | EOD1A | F001 | DOE1A | DOD1A | DOC1 |  |

| 1 - B   | EOE1B | EOD1B | EOC1 | DOE1B | DOD1B |      |  |

| 2 - A   | EOE2A | EOD2A | EOC2 | DOE2A | DOD2A | DOC2 |  |

| 2 - B   | EOE2B | EOD2B | EUU2 | DOE2B | DOD2B | DOCZ |  |

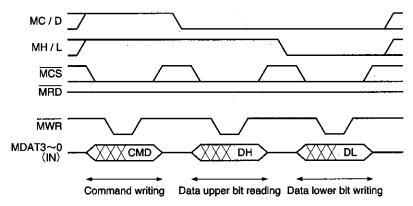

Fig. 6 Command/data writing → data writing timing

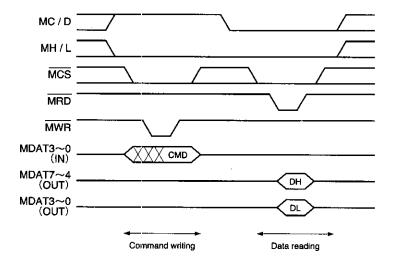

Fig. 7 Command writing → data read timing

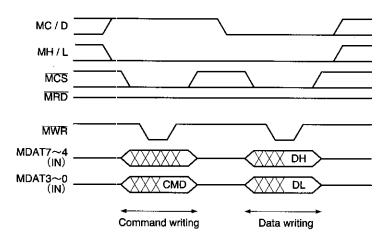

# ●Control signal timing chart

Fig. 8 Data writing → command writing timing

Fig. 9 Data read → command writing timing

#### Description of functions

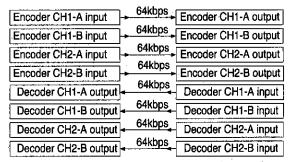

#### (1) 4-channel G.721 ADPCM processor

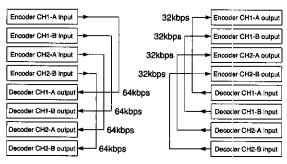

This is a 32kbps ADPCM processor which conforms to the G.721 standards listed in the 1988 edition of the CCITT recommendations, and is capable of 4-channel simultaneous processing. Various kinds of control can be carried out through a CPU interface. Calculations on the eight systems listed below can be processed simultaneously.

Channel 1-A, encoder

Channel 1-B, encoder

Channel 2-A, encoder

Channel 2-B, encoder

Channel 1-A, decoder

Channel 1-B, decoder

Channel 2-A, decoder

Channel 2-B, decoder

When Pin  $\mu$  / A is HIGH, calculation is carried out in the  $\mu$ -law mode, and when LOW, calculation is carried out in the A-law mode.

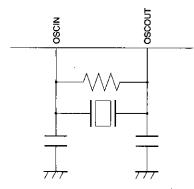

#### (2) Clock generator circuit

This LSI has an internal clock generator circuit which can be connected to a crystal resonator. Setting the PDN pin to LOW stops the clock generator circuit, enabling the line current to be suppressed to a minimum. When signals are input directly from an external generator circuit, the clock should be supplied to the OSCIN pin.

Fig. 10 Example of clock generator circuit

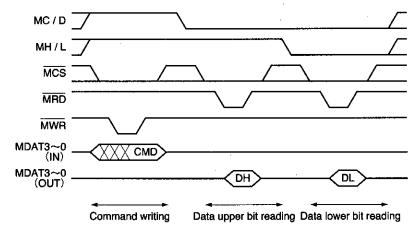

#### (3) CPU interface

The CPU interface data bus allows either 4-bit or an 8-bit parallel data transmission to be selected. When data is written to or read from the internal registers, the user can initiate control over various types of functions provided with this LSI.

The following section describes pins relating to the CPU interface.

- MC/D ··· Switches between commands and data from the CPU. When reading or writing data via the data bus, this switches between command and register data. When the MC/D pin is HIGH, commands can be written, and when LOW, register data can be read and written.

- MH/L · · · · Switches between the upper and lower bits of the data from the CPU. When using the 4-bit interface, this switches the upper and lower four bits of the data. When the MH/L pin is HIGH, commands are written, and the upper four bits of the register data can be read and written. When MH/L is LOW, the lower four bits of the register data can be read and written.

When using the 8-bit interface, MH/L is left at LOW.

- MCS · · · Selects the chip from the CPU. When reading and writing data, the MCS pin is set to the LOW state.

- MRD · · · Enables reading from the CPU. Data can be read from the data bus by setting MCS to LOW, MRD to LOW, and MWR to HIGH.

- MWR · · · Enables writing from the CPU. Data can be written from the data bus by setting MCS to LOW, MRD to HIGH, and MWR to LOW.

- MDAT7  $\sim$  0

- CPU 8-bit data bus. Because there is no internal pull-up or pull-down resistance, processing should be done externally. When using the 4-bit interface, use MDAT3 ~ 0 on the lower bit side.

- · MRDRQ

- Sends a request to the CPU to read data.

On channels where silence detection is enabled, if a silence state is detected, MRDRQ goes LOW.

# ●CPU interface truth table

| MC/D | MH/L                                     | MCS | MRD    | MWR                 | MDAT<br>7~0 | Operation                                                                                                   |

|------|------------------------------------------|-----|--------|---------------------|-------------|-------------------------------------------------------------------------------------------------------------|

| Н    | . н                                      | L   | Н      | L                   | , IN        | Writes commands; sets the 4-bit interface                                                                   |

| Н    | L                                        | L   | Н      | L                   | -IN         | Writes commands; sets the 8-bit interface                                                                   |

| L    | Н                                        | L   | Н      | L                   | 1N          | When using the 4-bit interface, writes the upper 4 bits. Inhibited when using the 8-bit interface.          |

| L    | L                                        | L   | Ĥ      | L                   | 1N          | When using the 4-bit interface, writes the lower 4 bits. When using the 8-bit interface, writes all 8 bits. |

| L    | Н                                        | L   | L      | Н                   | OUT         | When using the 4-bit interface, reads the upper 4 bits. Inhibited when using the 8-bit interface.           |

| L    | L                                        | L   | L      | Н                   | OUT         | When using the 4-bit interface, reads the lower 4 bits. When using the 8-bit interface, reads all 8 bits.   |

| Н    | Н                                        | L   | L      | L                   | Hi∙Z        | Normally inhibited. Sets the serial interface synchronous mode only when no CPU is being used.              |

| Co   | Combinations other than the above Hi - Z |     | Hi - Z | Doesn't do anything |             |                                                                                                             |

Fig. 11 Basic command writing/data reading timing when using the 4-bit interface

Fig. 12 Basic command/data writing timing when using the 4-bit interface

Fig. 13 Basic command writing/data reading timing when using the 8-bit interface

Fig. 14 Basic command/data writing timing when using the 8-bit interface

#### Internal register mapping

| No. | Command           | Register upper bits (DH) Register lower bits (DL) Initial v |            |            |            |            | Req        | jister lov | ver bits ( | DL)        | Initial | value |

|-----|-------------------|-------------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|---------|-------|

| CMD | Name              | IT / VV                                                     | D7         | D6         | D5         | D4         | D3         | D2         | D1         | D0         | D7···   | ···D0 |

| 0   | NOP               | W                                                           |            |            |            |            |            |            |            |            |         |       |

| 1   | RESET             | w                                                           | RES<br>E1A | RES<br>E1B | RES<br>E2A | RES<br>E2B | RES<br>D1A | RES<br>D1B | RES<br>D2A | RES<br>D2B | 0000    | 0000  |

| 2   | POWER DOWN        | R/W                                                         | PDN<br>E1A | PDN<br>E1B | PDN<br>E2A | PDN<br>E2B | PDN<br>D1A | PDN<br>D1B | PDN<br>D2A | PDN<br>D2B | 0000    | 0000  |

| 3   | MUTE              | R/W                                                         | MUT<br>E1A | MUT<br>E1B | MUT<br>E2A | MUT<br>E2B | MUT<br>D1A | MUT<br>D1B | MUT<br>D2A | MUT<br>D2B | 0000    | 0000  |

| 4   | BACK NOISE        | R/W                                                         |            |            |            |            | BNS<br>D1A | BNS<br>D1B | BNS<br>D2A | BNS<br>D2B |         | 0000  |

| 5   | NOISE<br>LEVEL    | w                                                           |            |            | _          |            |            | BN<br>LVL2 | BN<br>LVL1 | BN<br>LVL0 |         | -000  |

| 6   | VDET<br>ENABLE    | R/W                                                         | VDE<br>E1A | VDE<br>E1B | VDE<br>E2A | VDE<br>E2B |            |            |            |            | 0000    |       |

| 7   | VDET FLAG         | R                                                           | VDF<br>E1A | VDF<br>E1B | VDF<br>E2A | VDF<br>E2B | 7          |            |            |            | 0000    |       |

| .8  | VDET<br>L - LEVEL | w                                                           | VDLV<br>07 | VDLV<br>06 | VDLV<br>05 | VDLV<br>04 | VDLV<br>03 | VDLV<br>02 | VDLV<br>01 | VDLV<br>00 | 0000    | 0000  |

| 9   | VDET<br>U - LEVEL | w                                                           |            |            |            | VDLV<br>12 | VDLV<br>11 | VDLV<br>10 | VDLV<br>09 | VDLV<br>80 | 0       | 0000  |

| A   | VDET TIME         | w                                                           |            |            | VD<br>TIM5 | VD<br>TIM4 | VD<br>TIM3 | VD<br>TIM2 | VD<br>TIM1 | VD<br>TIM0 | 00      | 0000  |

| В   | OUT LEVEL         | R/W                                                         | OLV<br>1A1 | OLV<br>1A0 | OLV<br>1B1 | OLV<br>1B0 | OLV<br>2A1 | OLV<br>2A0 | OLV<br>2B1 | OLV<br>2B0 | 0000    | 0000  |

| С   | THRU MODE         | R/W                                                         | THR<br>E1A | THR<br>E1B | THR<br>E2A | THR<br>E2B | THR<br>D1A | THR<br>D1B | THR<br>D2A | THR<br>D2B | 0000    | 0000  |

| D   | LOOP BACK         | R/W                                                         |            |            |            |            | LPBK<br>1A | LPBK<br>18 | LPBK<br>2A | LPBK<br>2B |         | 0000  |

| E   | SERIAL<br>MODE    | R/W                                                         |            |            |            |            |            |            |            | SIF<br>MOD |         | 0     |

| F   | (don't use)       |                                                             |            |            |            |            |            | ·          |            |            | -       |       |

The table above shows the internal registers. Initial values Indicate the values for the various registers Immediately after a system reset (RESET = LOW). For details on the individual commands, please see the specific contents for that command on the following pages.

· Command No. : 0 (NOP)

No processing is carried out with this command.

· Command No. : 1 (RESET)

Writing "H" to the corresponding internal register initializes the individual encoder and decoder for the channel. The status at this point is the optional reset status noted in the 1988 edition of the CCITT recommendations for the G.721.

RESE1A · · Channel 1-A encoder initialized

RESE1B··Channel 1-B encoder initialized

RESE2A··Channel 2-A encoder initialized

RESE2B · · Channel 2-B encoder initialized

RESD1A · · Channel 1-A decoder initialized

RESD1B··Channel 1-B decoder initialized

RESD2A··Channel 2-A decoder initialized RESD2B··Channel 2-B decoder initialized

#### · Command No.: 2 (POWER DOWN)

Writing "H" to the corresponding internal register sets the power down mode for the individual encoder and decoder for the channel. At this point, the G.721 ADPCM processor simply stops calculation processing.

PDNE1A····Channel 1-A encoder in power down mode PDNE1B····Channel 1-B encoder in power down mode PDNE2A····Channel 2-A encoder in power down mode PDNE2B····Channel 2-B encoder in power down mode PDND1A····Channel 1-A decoder in power down mode PDND1B····Channel 1-B decoder in power down mode PDND2A····Channel 2-A decoder in power down mode PDND2B····Channel 2-B decoder in power down mode Command No.: 3 (MUTE)

Writing "H" to the corresponding internal register sets the mute mode for the individual encoder and decoder for the channel. In data through mode and data loop back mode, muting processing is not carried out.

MUTE1A····Muting on Channel 1-A encoder MUTE1B····Muting on Channel 1-B encoder MUTE2A····Muting on Channel 2-A encoder MUTE2B····Muting on Channel 2-B encoder MUTD1A····Muting on Channel 1-A decoder MUTD1B····Muting on Channel 1-B decoder MUTD2A····Muting on Channel 2-A decoder MUTD2B····Muting on Channel 2-B decoder

Command No.: 4 (BACK NOISE)

Writing "H" to the corresponding internal register generates background noise from the decoder output of each individual channel. The noise output level can be controlled to any level using registers BNLVL2 to 0 (command no.: 5). In data through mode and data loop back mode, background noise is not generated.

BNSD1A····Background noise generated for Channel 1-A decoder

BNSD1B····Background noise generated for Channel 1-B decoder

BNSD2A····Background noise generated for Channel 2-A decoder

BNSD2B····Background noise generated for Channel 2-B decoder

- Command No.: 5 (NOISE LEVEL)

This sets the output level for the background noise generated by the register BNSxxx (command no.: 4) setting. The noise output levels in the table below are the values calculated on a logic basis.

| BNLVL 2~0 | Noise output level (dBm0) |

|-----------|---------------------------|

| 111       | -34.6                     |

| 110       | -40.6                     |

| 101       | -46.5                     |

| 100       | -52.3                     |

| 011       | -57.9                     |

| 010       | -63.0                     |

| 001       | <del>-67.3</del>          |

| 000       | -69.0                     |

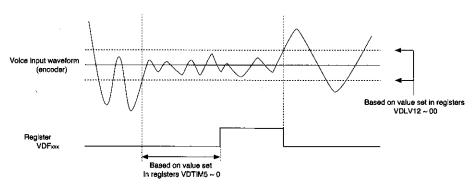

#### Command no.: 6 (VDET ENABLE)

Writing "H" to the corresponding internal register initiates silence detection for the encoder input of each individual channel. The standard level and time for the silence detection is supplied by registers VDLV12  $\sim$  00 (command nos. : 8 and 9) and registers VDTIM5  $\sim$  0 (command no. : A). The results of the silence detection can be checked by means of a flag using register VDFxxx (command no. : 7). In data through mode and data loop back mode, silence detection is not carried out.

VDEE1A····Silence detection enabled for Channel 1-A encoder

VDEE1B····Silence detection enabled for Channel 1-B encoder

VDEE2A····Silence detection enabled for Channel 2-A encoder

VDEE2B····Silence detection enabled for Channel 2-B encoder

If any of the encoders on channels for which silence detection is enabled is actually in the silence detection enabled state (in register VDFxxx, one or more bits are HIGH), the MRDRQ pin goes LOW. If silence detection is not in effect on any of the encoders on channels for which it is enabled (all bits of register VDFxxx are LOW), the MRDRQ pin is HIGH.

#### · Command No.: 7 (VDET FLAG)

For channels on which encoder silence detection is enabled by register VDFxxx (command no.: 6), a flag can be read out which indicates a silent status (HIGH). This flag can only be read and cannot be written.

VDFE1A····Silence detection flag for Channel 1-A encoder

VDFE1B····Silence detection flag for Channel 1-B encoder

VDFE2A····Silence detection flag for Channel 2-A encoder

VDFE2B····Silence detection flag for Channel 2-B encoder

- · Command No.: 8 (VDET L-LEVEL)

- · Command No.: 9 (VDET U-LEVEL)

When encoder silence detection is being carried out, these set the reference level on which judgments are based. This set value is supplied as a 13-bit linear absolute value.

VDLV12  $\sim$  00 · · · · Sets reference level on which encoder silence detection judgments are based.

· Command No. : A (VDET TIME)

When encoder silence detection is carried out, this sets the time interval for judgment. The set value issupplied in 6 bits.

VDTIM5  $\sim 0 \cdots$  Sets the time for judgment of encoder silence. The time is calculated using the equation below.

[Judgment time] =  $VDTIM \times 8ms$

(Example) If VDTIM = 110000 (binary), the judgment time will be  $48 \times 8ms = 384ms$

· Command No. : B (OUT LEVEL)

By writing the desired value to the corresponding internal register, the decoder output level for each individual channel can be attenuated to the desired level. In data through mode or data loop back mode, the output level cannot be controlled.

OLV1A1, OLV1A0····Output level control of Channel 1-A decoder

OLV1B1, OLV1B0····Output level control of Channel 1-B decoder

OLV2A1, OLV2A0····Output level control of Channel 2-A decoder

OLV2B1, OLV2B0····Output level control of Channel 2-B decoder

Two bits of control data are assigned to each channel, enabling adjustment in a total of four stages. The relationship between the set value and the output level is shown in the table below. The output levels noted here are recorded using the value prior to attenuation (0dB) as a reference.

| - |       |              |                                          |

|---|-------|--------------|------------------------------------------|

|   | QLVxx | Output level |                                          |

|   | 00    | 0dB          | Equivalent to value prior to attenuation |

|   | 01    | −6dB         | prior to attenuation                     |

|   | 10    | —12dB        | •                                        |

|   | 11    | -18dB        |                                          |

|   |       |              |                                          |

#### · Command No. : C (THRU MODE)

Writing "H" to the corresponding internal register sets the 64kbps data through mode for the individual encoders and decoders of the various channels.

THRE1A····64 kbps data through mode for Channel

1-A encoder

THRE1B · · · · 64 kbps data through mode for Channel

1-B encoder

THRE2A····64 kbps data through mode for Channel

THRE2B····64 kbps data through mode for Channel

2-B encoder

THRD1A····64 kbps data through mode for Channel

1-A decoder

THRD1B····64 kbps data through mode for Channel 1-B decoder

THRD2A · · · 64 kbps data through mode for Channel 2-A decoder

THRD2B····64 kbps data through mode for Channel 2-B decoder

Fig. 15 Interface relationships in 64 kbps through mode

#### · Command No. : D (LOOP BACK)

Writing "H" to the corresponding intermal register sets the 64 kbps data loop back mode for the encoder input → decoder output and the 32 kbps data loop back mode for the decoder input → encoder output.

LPBK1A····Loop back mode for Channel 1-A encoder/decoder

LPBK1B····Loop back mode for Channel 1-B encoder/decoder

LPBK2A····Loop back mode for Channel 2-A encoder/ decoder

LPBK2B····Loop back mode for Channel 2-B encoder/decoder

Fig. 16 Interface relationships in 32 kbps/64 kbps data loop back mode

※In the 64kbps through mode (command no.: C) and the 64kbps/32kbps data loop back mode (command no.: D), some functions cannot be used. Please refer to the table below.

| Function                    | Normal  | peration        | Data through mode<br>Loop back mode |         |

|-----------------------------|---------|-----------------|-------------------------------------|---------|

|                             | Encoder | Encoder Decoder |                                     | Decoder |

| Reset                       | 0       | 0               | 0                                   | 0       |

| Power down                  | 0       | 0               | 0                                   | 0       |

| Mute                        | 0       | 0               | ×                                   | X       |

| Background noise generation | ×       | 0               | ×                                   | ×       |

| Silence detection           | 0       | ×               | ×                                   | ×       |

| Output level control        | ×       | 0               | ×                                   | ×       |

#### · Command No. : E (SERIAL MODE)

This is used to select the timing for the input and output serial interfaces of the encoder and decoder. When register SIFMOD is LOW, the normal operation mode is effective (short frame or long frame), and when register SIFMOD is HIGH, the synchronous mode is effective. This setting is applied to all channels, and cannot be specified separately for individual channels.

SIFMOD····This switches the serial interface mode. If a CPU interface is not being used, the mode can be switched as shown in the truth table below, based on the logic level of the CPU interface pin.

|                  | MWR   | MRD                                  | MCS | MH/L | MC/D |  |  |  |

|------------------|-------|--------------------------------------|-----|------|------|--|--|--|

| Synchronous mode | L     | L                                    | L   | Н    | Н    |  |  |  |

| Normal mode      | above | Any combination other than the above |     |      |      |  |  |  |

#### (4) Serial interface

This is the serial interface which is used to input and output data to and from the 4-channel encoders and decoders. It accommodates all interfaces: the long frame in normal mode, the short frame in normal mode, and the synchronous mode.

≪Interfaces and signal names≫

| Interface       | Channel | Enable | Data  | Cłock |  |

|-----------------|---------|--------|-------|-------|--|

|                 | 1 - A   | EIE1A  | EID1A | EIC1  |  |

| <b>F</b> 414    | 1 - B   | EIE1B  | EID1B |       |  |

| Encoder input   | 2 - A   | EIE2A  | EID2A | FICO  |  |

|                 | 2-B     | EIE2B  | EID2B | EIC2  |  |

|                 | 1 - A   | DIE1A  | DID1A | DIC1  |  |

| Decoder input   | 1 - B   | DIE18  | DID1B | DIC1  |  |

| Decoder input   | 2 - A   | DIE2A  | DID2A | DIC2  |  |

|                 | 2 - B   | DIE2B  | DID2B |       |  |

|                 | 1 - A   | EOE1A  | EOD1A | EOC1  |  |

| Encoder output  | 1 - B   | EOE1B  | EQD1B |       |  |

| Elicodei output | 2 - A   | EOE2A  | EOD2A | EOC2  |  |

|                 | 2 - B   | EOE2B  | EOD2B |       |  |

|                 | 1 - A   | DOE1A  | DOD1A | DOC1  |  |

| Decoder output  | 1 - B   | DOE1B  | DOD1B |       |  |

| Decoder output  | 2 - A   | DOE2A  | DOD2A |       |  |

|                 | 2 - B   | DOE2B  | DOD2B |       |  |

The "Enable" and "Data" items are input and output individually for each channel. Clocks are input individually, with one clock being input for two channels. With serial interfaces, the following three types of timing are available.

≪Timings and their features≫

| Ti      | ming           | Enable                 | Data (in terms of Enable)                       |

|---------|----------------|------------------------|-------------------------------------------------|

| Normal  | Short<br>frame | 1-bit width            | Input/output at delay of 1 bit from rising edge |

| mode    | Long<br>frame  | 2-bit width<br>or more | Input/output synchronized to rising edge        |

| Synchro | nous mode      | 1-bit width<br>or more | Input/output synchronized to rising edge        |

Generally speaking, there are two types of timing, for normal mode and for synchronous mode. Normal mode timing is further subdivided into long frame and short frame timing.

· Normal mode

This is the mode in which either the long frame or short frame can be used.

Switching between the long and short frame is done automatically, based on the pulse width of the Enable signal.

· Synchronous mode

This is a special timing mode. In this mode, data is input and output in sequential order, immediately following the rising edge of the Enable signal, regardless of the pulse width of the Enable signal.

#### Timings for the various modes

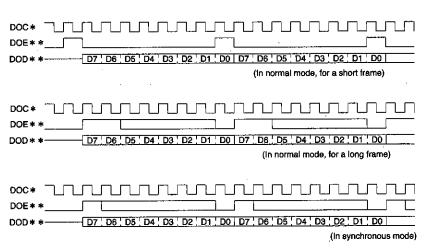

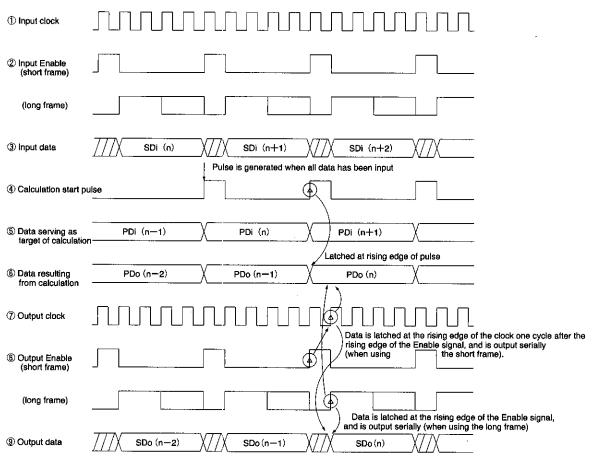

Figures 17 to 20 show the relations between the serial clock, Enable signal, and data for the various encoder and decoder input and output, in the normal mode and the synchronous mode.

Fig. 17 Encoder input (at EICx = 64 kHz)

Fig. 18 Decoder input (at DICx = 32 kHz)

Fig. 19 Encoder output (at EOCx = 32 kHz)

Fig. 20 Decoder output (at DOCx = 64 kHz)

- Relation between clock frequency and data word length Serial data is interfaced in two lengths, 8 bits and 4 bits. For 8-bit data, the transmission speed is 64kbps, and for 4-bit data, the speed is 32kbps.

- For 64 kbps transmission

The clock frequency is set within a range of 64kHz to 8MHz. This transmission speed is applicable in the following cases.

- For encoder input and decoder output when normal ADPCM calculation is being carried out.

- For encoder and decoder input and output in the data through mode.

- For encoder input and decoder output in the data loop back mode.

#### Output delays in relation to input

After data is input, it takes a certain amount of time for the data to undergo ADPCM calculation before being output. This section explains delays in data output in relation to data input.

First, we will look at the relationship between the timing at which serial data is input from and output to an external source, and internal operation.

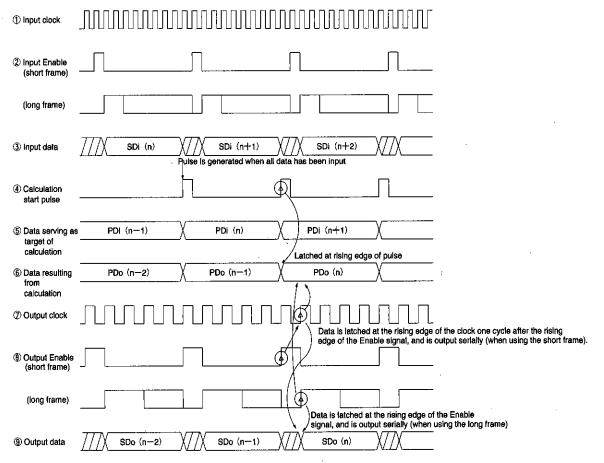

In Figures 21 to 24, the timings for items ① to ③ and ⑦ to ⑨ are indicated as seen from the pins, while items ④ to ⑥ show internal signal states. The items are explained below, in numeric order.

- (1) An 8-bit or 4-bit data row is input serially based on the input clock ①, Input Enable signal ②, and input data ③. Figures 21 to 24 show the states for the normal mode only. The timing for the synchronous mode is equivalent to that for the long frame in the normal mode.

- (2) Immediately after the 8-bit or 4-bit data has been input serially at step ①, the calculation start pulse ④ is generated. Also, at this point, the data which is the target of the calculation ⑤, which has been converted from serial to parallel data, is prepared as parallel 8-bit or 4-bit data.

#### For 32 kbps transmission

The clock frequency is set within a range of 32kHz to 8MHz. This transmission speed is applicable in the following cases.

- For decoder input and encoder output when normal ADPCM calculation is being carried out.

- For decoder input and encoder output in the data loop back mode.

- (3) The calculation is carried out on the target data. Calculation is completed before the next calculation start pulse ④ is received, and the resulting data ⑥ is updated by the calculation start pulse ④. In the data through and data loop back modes as well, the ADPCM calculation processing is omitted, but the timing at which the resulting data ⑥ is updated remains the same.

- (4) The data resulting from the calculation (a) is latched in order to be converted from parallel to serial data. With a short frame in the normal mode, this is done following one cycle after the rising edge of the Output Enable signal (a), at the rising edge of the output clock (b). With a short frame in the normal mode, and in the synchronous mode, this is done at the rising edge of the Output Enable signal. In addition, the 8-bit or 4-bit data is output serially based on the output clock, the Output Enable signal (a), and the Output Data signal (a).

[Supplementary information for Figures 21  $\sim$  24]

- SD (k) · · · · Serial input data targeted for calculation

- PDi (k) •••• Parallel input data targeted for calculation

- PDo (k) • • Parallel output data resulting from calculation

- SDo (k) · · · · Serial output data resulting from calculation

●Normal ADPCM calculation for the encoder Figure 21 shows the data delays that take place with normal ADPCM calculation for the encoder.

Fig. 21 Data delays for the encoder

As shown in Figure 21, if the input clock exceeds 64kHz and the output clock exceeds 32kHz, and the Input Enable and Output Enable are in the same phase, a delay equal to two data samplings will occur. Delays occurring under other conditions can also be determined based on Figure 21.

123

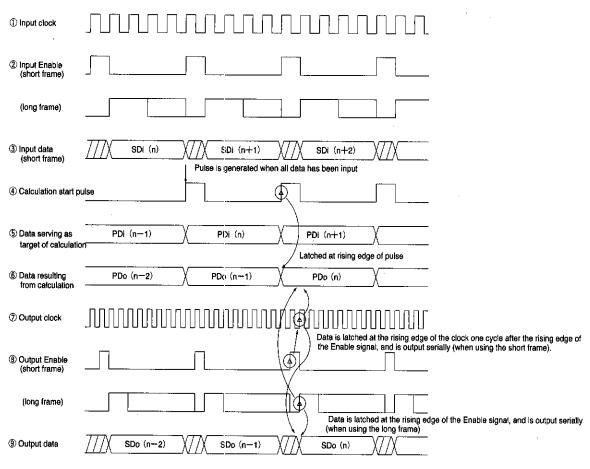

●Normal ADPCM calculation for the decoder Figure 22 shows the data delays that take place with normal ADPCM calculation for the decoder.

Fig. 22 Data celays for the decoder

As shown in Figure 22, if e input clock exceeds 32kHz and the output clock exceeds 64kHz, and the Input Enable and Output Enable are in the same phase, a delay equal to two data samplings will occur. Delays occurring under other conditions can also be determined based on Figure 22.

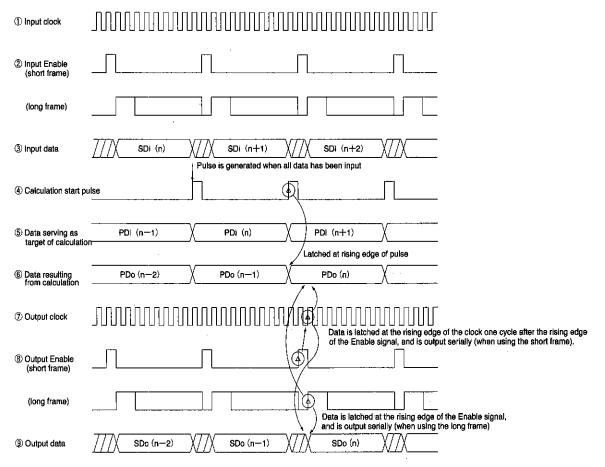

●Data through mode and loop back mode Figure 23 shows data delays in the 64kbps data through mode, for the encoder and decoder. The figure also shows data delays in the 64kbps data loop back mode, for encoder input and decoder output.

Fig. 23 Data delays for 64 kbps input and output

As shown in Figure 23, if the input / output clock exceeds 64 kHz and the Input Enable and Output Enable are in the same phase, a delay equal to two data samplings will occur. Delays occurring under other conditions can also be determined based on Figure 23.

Figure 24 shows data delays in the 32kbps data loop back mode, for the decoder input and encoder output.

Fig. 24 Data delays for 32 kbps input and output

As shown in Figure 24, if the input / output clock exceeds 32kHz and the Input Enable and Output Enable are in the same phase, a delay equal to two data samplings will occur. Delays occurring under other conditions can also be determined based on Figure 24.

#### (5) Silence detection method

Silence states can be judged if all of the conditions listed below have been met. The results of the silence detection are stored in register VDFxxx.

- (Condition 1) Must be in Silence Detection Enable state (register VDExxx = HIGH).

- (Condition 2) Must be within the specified reference level (set using registers VDLV12 to 00). The reference level is applied as an absolute value, so it will be within a range of VDLV to -VDLV.

- (Condition 3) Conditions 1 and 2 must be met continuously for more than a given period of time (set using registers VDTIM5 to 0).

Figure 25 shows silence detection conditions.

Fig. 25 Example of silence detection

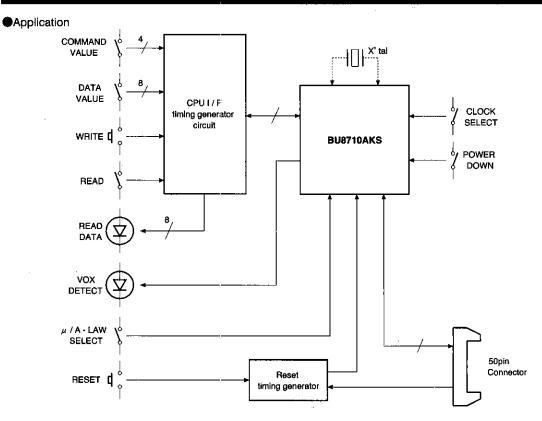

Fig. 26 Application diagram

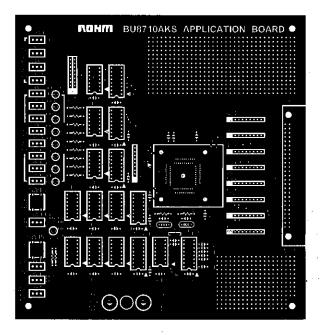

Board component layout

Fig. 27 Component layout

#### «Connector pin correspondence table»

| Connector                  |                    | BU8710AKS side                              |                              | Connector                  |        | BU8710AKS side                          |                          |

|----------------------------|--------------------|---------------------------------------------|------------------------------|----------------------------|--------|-----------------------------------------|--------------------------|

| Pin No.                    | 1/0                | Signal Name                                 | Pin No.                      | Pin No.                    | 1/0    | Signal Name                             | Pin No.                  |

| 1<br>3<br>5<br>7<br>9      |                    | EIC1<br>EIE1A<br>EIE1B<br>EIC2<br>EIE2A     | 59<br>57<br>55<br>62<br>64   | 2<br>4<br>6<br>8<br>10     |        | EID1A<br>EID1B<br>GND<br>EID2A<br>EID2B | 58<br>56<br><br>63<br>65 |

| 11<br>13<br>15<br>17<br>19 | -                  | EIE2B<br>EOC1<br>EOE1A<br>EOE1B<br>EOC2     | 66<br>50<br>53<br>51<br>48   | 12<br>14<br>16<br>18<br>20 | 10010  | GND<br>EOD1A<br>EOD1B<br>GND<br>EOD2A   | 54<br>52<br><br>47       |

| 21<br>23<br>25<br>27<br>29 | <br> -<br> -<br> - | EOE2A<br>EOE2B<br>DIC1<br>DIE1A<br>DIE1B    | 46<br>44<br>37<br>42<br>38   | 22<br>24<br>26<br>28<br>30 | 0      | EOD2B<br>GND<br>DID1A<br>DID1B<br>GND   | 45<br>43<br>39<br>       |

| 31<br>33<br>35<br>37<br>39 |                    | DIC2<br>DIE2A<br>DIE2B<br>DOC1<br>DOE1A     | 36<br>34<br>32<br>71<br>68   | 32<br>34<br>36<br>38<br>40 | 100    | DID2A<br>DID2B<br>GND<br>DOD1A<br>DOD1B | 35<br>33<br><br>67<br>69 |

| 41<br>43<br>45<br>47<br>49 | <br>               | DOE1B<br>DOC2<br>DOE2A<br>DOE2B<br>RESET(*) | 70<br>73<br>75<br>77<br>(18) | 42<br>44<br>46<br>48<br>50 | - 00 - | GND<br>DOD2A<br>DOD2B<br>GND<br>GND     | <br>74<br>76<br>         |

<sup>(\*) ···</sup> Logic reversed in relation to BU8710AKS and supplied (positive logic input)

Connector header used: FAP-50-07#1 by Yamaichi Electric

$\ll$ Items relating to switches and LEDs $\gg$

| Switch/LED |                    |                                                                                                                                  |  |  |  |

|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No. Name   |                    | Basic Function                                                                                                                   |  |  |  |

| SW1~4      | COMMAND VALUE      | Sets command number (4-bit).                                                                                                     |  |  |  |

| SW5~12     | DATA VALUE         | Sets data to be written (8-bit).                                                                                                 |  |  |  |

| SW13       | WRITE              | Writes data to internal register based on SW1 ~ 12 setting. Reads results that have been written and moritors them via LED1 ~ 8. |  |  |  |

| SW14       | READ               | Reads data from internal registers in real time, based on SW1 ~ 4 setting, and monitors data via LED1 ~ 8.                       |  |  |  |

| SW15       | RESET              | Initializes the LSI.                                                                                                             |  |  |  |

| SW16       | POWER DOWN         | Initiates the power save mode for the LSI.                                                                                       |  |  |  |

| SW17       | CLOCK SELECT       | Selects the master clock frequency supplied to the LSI. LOW → 12.288 MHz, HIGH→ 19.2 MHz.                                        |  |  |  |

| SW18       | μ / A - LAW SELECT | Switches the G.711 format. LOW→ A-law, HIGH→ μ-law.                                                                              |  |  |  |

| LED1∼8     | READ DATA          | If SW13 or SW14 is on, reads the data from the internal register and displays the results.                                       |  |  |  |

| LED9       | VOX DETECT         | Displays silence detection results for various channels. Lights when the LSI pin MRDRQ is LOW.                                   |  |  |  |

<sup>\*</sup> Setting any switch to the upward position turns it on (logic 1), and setting it to the downward position turns it off (logic 0).

#### Preparing peripheral circuits

①Processing a 50-pin connector

All of the pins in the serial interface (pin numbers 1 to 47, excluding the GND pin) are pulled up on the board, so only those pins which will actually be used should be connected to the desired signals.

If the reset pin (pin 49) is not being used, it should be processed to the GND pin.

②Processing the power supply

A power supply of 5 V should be supplied from POW-ER on the board.

#### Operation procedure

#### [Basic operation]

- ① Using SW17, set the master clock frequency.

- ② Using SW18, set the G.711 format.

- ③ Using SW16, turn off the power save mode.

- 4 Press the reset switch to initialize the LSI.

- \* At this point, normal voice transmission can be carried out through the serial interface.

## External dimensions (Units: mm)

#### [Writing data to internal registers]

- ① Using SW1 ~ SW4, set the command number.

- ② Using SW5  $\sim$  SW12, set the data to be written.

- ③ Press SW13 to write the data to the internal register.

- The data is read automatically immediately after it has been written, and is displayed by LED1 ~ LED8. Check to make sure the data has been written correctly.

#### [Reading data from internal registers]

- Using SW1 ~ SW4, set the command number.

- ② Turn on SW14 to read the data for the command number set using SW1 ~ SW4 in serial time. The results are displayed by LED1 ~ LED8.

- \* If the settings for SW1 ~ SW4 have been changed, the results displayed will change accordingly.

- Data can also be written while other data is being read.

#### Notes

- The contents described in this catalogue are correct as of March 1997.

- No unauthorized transmission or reproduction of this book, either in whole or in part, is permitted.

- The contents of this book are subject to change without notice. Always verify before use

that the contents are the latest specifications. If, by any chance, a defect should arise in

the equipment as a result of use without verification of the specifications, ROHM CO., LTD.,

can bear no responsibility whatsoever.

- Application circuit diagrams and circuit constants contained in this data book are shown as examples of standard use and operation. When designing for mass production, please pay careful attention to peripheral conditions.

- Any and all data, including, but not limited to application circuit diagrams, information, and various data, described in this catalogue are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO., LTD., disclaims any warranty that any use of such device shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes absolutely no liability in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices; other than for the buyer's right to use such devices

itself, resell or otherwise dispose of the same; no express or implied right or license to

practice or commercially exploit any intellectual property rights or other proprietary rights

owned or controlled by ROHM CO., LTD., is granted to any such buyer.

- The products in this manual are manufactured with silicon as the main material.

- The products in this manual are not of radiation resistant design.

The products listed in this catalogue are designed to be used with ordinary electronic equipment or devices (such as audio-visual equipment, office-automation equipment, communications devices, electrical appliances, and electronic toys). Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers, or other safety devices) please be sure to consult with our sales representatives in advance.

## Notes when exporting

- It is essential to obtain export permission when exporting any of the above products when it falls under the category of strategic material (or labor) as determined by foreign exchange or foreign trade control laws.

- Please be sure to consult with our sales representatives to ascertain whether any product is classified as a strategic material.