# 4-channel BTL driver for CD players BA6392FP

The BA6392FP is a 4-channel BTL driver for CD player motors and actuators. It has an internal primary filter, and can be directly connected (without attached components) to the servo PWM output of all drivers other than the spindle driver. The BA6392FP is pin compatible with the BA6297AFP.

### Applications

CD players, CD-ROM drives

#### Features

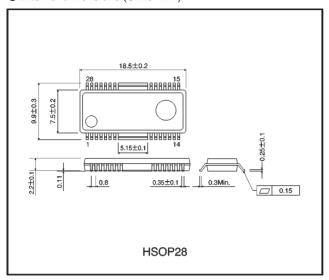

- HSOP 28-pin package allows for miniaturization of applications.

- 2) PWM input is filtered by the internal primary filter, eliminating the need for attached resistors and capacitors, thereby helping reduce the number of components. Resistor and capacitor time constants can also be changed with attached components.

- 3) Internal thermal shutdown circuit.

- 4) Internal mute circuit.

# ●Absolute maximum ratings (Ta = 25°C)

| Parameter             | Symbol | Limits             | Unit |

|-----------------------|--------|--------------------|------|

| Power supply voltage  | Vcc    | 18                 | V    |

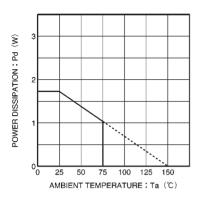

| Power dissipation     | Pd     | 1.7*1              | w    |

| Operating temperature | Topr   | <del>-30~+85</del> | °C   |

| Storage temperature   | Tstg   | <b>−55∼</b> +150   | C    |

<sup>\*1</sup> Reduced by 13.6 mW for each increase in Ta of 1°C over 25°C. When mounted on a 50  $\times$  50  $\times$  1.0 mm phenol paper PCB.

#### • Recommended operating conditions (Ta = 25°C)

| Parameter            | Symbol | Limits             | Unit |

|----------------------|--------|--------------------|------|

| Power supply voltage | Vcc    | 6~16 <sup>*2</sup> | V    |

<sup>\*2</sup> Set the power supply voltage according to power dissipation.

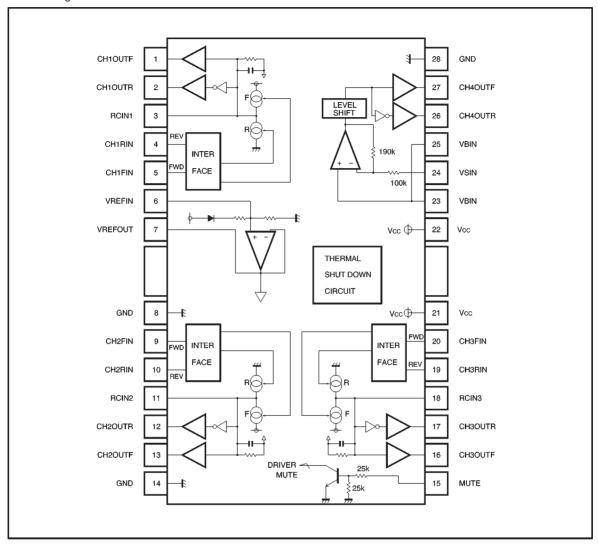

## Block diagram

# Pin descriptions

| Pin No. | Pin name | Function                                                 |  |  |  |

|---------|----------|----------------------------------------------------------|--|--|--|

| 1       | CH1OUT F | Driver channel 1 forward output                          |  |  |  |

| 2       | CH1OUT R | Driver channel 1 reverse output                          |  |  |  |

| 3       | RC IN1   | Connect to attached resistor/capacitor (1)               |  |  |  |

| 4       | CH1 RIN  | Driver channel 1 reverse input                           |  |  |  |

| 5       | CH1 FIN  | Driver channel 1 forward input                           |  |  |  |

| 6       | VREF IN  | Internal reference amplifier input                       |  |  |  |

| 7       | VREF OUT | Internal reference amplifier output                      |  |  |  |

| 8       | GND      | Ground for internal reference and internal power circuit |  |  |  |

| 9       | CH2 FIN  | Driver channel 2 forward input                           |  |  |  |

| 10      | CH2 RIN  | Driver channel 2 reverse input                           |  |  |  |

| 11      | RC IN2   | Connect to attached resistor/capacitor (2)               |  |  |  |

| 12      | CH2OUT R | Driver channel 2 reverse output                          |  |  |  |

| 13      | CH2OUT F | Driver channel 2 forward output                          |  |  |  |

| 14      | GND      | Ground                                                   |  |  |  |

| 15      | MUTE     | Driver mute control input                                |  |  |  |

| 16      | CH3OUT F | Driver channel 3 forward output                          |  |  |  |

| 17      | CH3OUT R | Driver channel 3 reverse output                          |  |  |  |

| 18      | RC IN3   | Connect to attached resistor/capacitor (3)               |  |  |  |

| 19      | CH3 RIN  | Driver channel 3 reverse input                           |  |  |  |

| 20      | CH3 FIN  | Driver channel 3 forward input                           |  |  |  |

| 21      | Vcc      | Power supply                                             |  |  |  |

| 22      | Vcc      | Power supply                                             |  |  |  |

| 23      | VBIN     | Driver channel 4 bias input*                             |  |  |  |

| 24      | VSIN     | Driver channel 4 input                                   |  |  |  |

| 25      | VBIN     | Driver channel 4 bias input*                             |  |  |  |

| 26      | CH4OUT R | Driver channel 4 reverse output                          |  |  |  |

| 27      | CH4OUT F | Driver channel 4 forward output                          |  |  |  |

| 28      | GND      | Ground                                                   |  |  |  |

<sup>\*</sup> Pin 23 and pin 25 are shorted internally.

●Electrical characteristics (unless otherwise noted, Ta = 25°C, Vcc = 8V, f = 1kHz, RL = 8Ω)

| Parameter                       | Symbol           | Min. | Тур. | Max. | Unit | Conditions                                    |

|---------------------------------|------------------|------|------|------|------|-----------------------------------------------|

| Quiescent current               | lα               | 8    | 13   | 18   | mA   | No load                                       |

| Bias pin voltage                | VBIAS            | 3.40 | 3.70 | 4.00 | V    |                                               |

| Bias pin voltage variance       | ΔVBIAS           | -30  | _    | 30   | mV   | 1 mA Source, sink                             |

| Mute-off voltage                | VMON             | 2.0  | _    | _    | V    |                                               |

| Mute-on voltage                 | VMOFF            | _    | _    | 0.5  | V    |                                               |

| ⟨Drivers (other than spindle⟩   |                  |      |      |      |      |                                               |

| Input high level voltage        | Viн              | 2.4  | _    | _    | V    |                                               |

| Input low level voltage         | VIL              | _    | _    | 0.5  | V    |                                               |

| Input high level current        | Іін              | 170  | 310  | 450  | μΑ   | V <sub>IN</sub> =5V                           |

| Input low level current         | lıL              | -10  | _    | 0    | μΑ   | V <sub>IN</sub> =0V                           |

| Output voltage, offset          | Voo              | -30  | _    | 30   | mV   | (same for spindle)                            |

| Output high level voltage       | Vонd             | 5.2  | 5.6  | _    | V    | Fin=5V, Rin=0V                                |

| Output low level voltage        | V <sub>OLD</sub> | _    | 1.3  | 1.6  | V    | Fin=0V, Rin=5V                                |

| Constant current                | Iconst           | 14   | 22   | 30   | μΑ   |                                               |

| Internal integral capacitance   | С                | _    | 24   | _    | pF   |                                               |

| Current pulse rise time 1       | Δtr              | _    | 0.08 | 1    | μS   | At startup                                    |

| Current pulse fall time 2       | ∆tf              | _    | 0.55 | 1    | μS   | At shutdown                                   |

| Current pulse time differential | ∆tr−f            | -160 | _    | 160  | μs   |                                               |

| Drive linearity                 | LIN              | 90   | 100  | 110  | %    | VIN=VREF±0.5, 1, 1.5V*1                       |

| Ripple rejection                | RR               | _    | 70   | _    | dB   | V <sub>IN</sub> =100mV <sub>rms</sub> , 100Hz |

| ⟨Spindle driver⟩                |                  |      |      |      |      |                                               |

| Input bias current              | lв               | _    | 10   | 300  | nA   |                                               |

| Synchronous input voltage       | Vicм             | 1.6  | _    | 6.4  | V    |                                               |

| Max. output voltage high        | Vонв             | 5.2  | 5.6  | _    | V    |                                               |

| Max. output voltage low         | Vold             | _    | 1.3  | 1.55 | ٧    |                                               |

| Voltage gain                    | Gvc              | 8.0  | 10.5 | 13.0 | dB   |                                               |

| Slew rate                       | SR               | _    | 2    | _    | V/μs |                                               |

| Ripple rejection                | RRs              | _    | 70   | _    | dB   | V <sub>IN</sub> =100mV <sub>rms</sub> , 100Hz |

O Not designed for radiation resistance.

<sup>\*1</sup> If Vo = V01 when V<sub>IN</sub> = VREF  $\pm 0.5$  V, Vo = Vo2 when V<sub>IN</sub> = VREF  $\pm 1.0$  V, and Vo = V3 when V<sub>IN</sub> = VREF  $\pm 1.5$  V, then L<sub>IN</sub> = (Vo3 - Vo2)/(Vo2 - Vo1)  $\times$  100%.

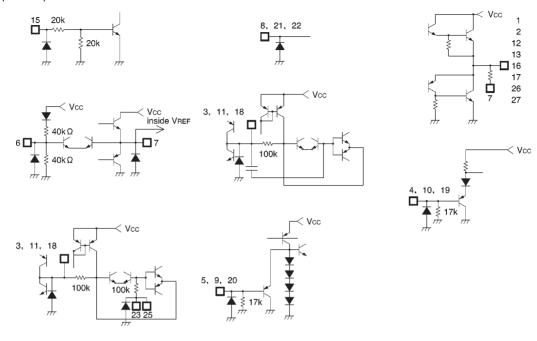

#### Input / output circuits

Fig. 1

# Circuit operation

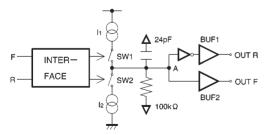

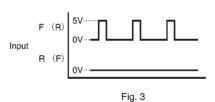

(1) Fig. 3 shows the inputs from the digital servo IC for CH1-CH3 drivers (all drivers except the spindle).

SW1 is on when the forward input signal (HIGH level, over 2.4V) is present. SW2 is on when the reverse input signal is present (Fig. 2)

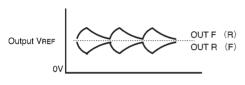

The constant current ( $I_1$ ) at this time enters the RC and generates an integral waveform based on the duty of the input waveform. The BTL is output from BUF1 and BUF2 (Fig. 4).

Fig. 2

To maintain the HIGH level with forward (or reverse) input, the DC voltage generated at point A is:

$$I_1 \times R = 2.5V \text{ (reverse : } -2.5V\text{)}$$

This is the voltage generated relative  $V_{\text{REF}}$ . The setting is such that a voltage differential of 5V is generated between output pins. The time constant is:

$$R \times C = 2.4 \mu sec$$

This can be increased by inserting a capacitor between point A (pins 3, 11 and 18) and  $V_{\text{REF}}$ . The constant current (Iconst) given in the electrical characteristics refers to  $I_1$  and  $I_2$  in Fig. 2.

| F | R | SW1 | SW2 |

|---|---|-----|-----|

| L | L | OFF | OFF |

| L | Н | OFF | ON  |

| Н | L | ON  | OFF |

| Н | Н | OFF | OFF |

H • • • 2.4V Max.

L··· 0.5V Min.

Fig. 4

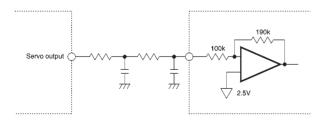

#### (2) CH4 driver (spindle driver)

Pins 23 and 25 are shorted inside the IC. Bias amplitudes are the primary type of inputs assumed. The level shift circuit converts the pre-stage amplifier output (centered on the bias level and impressed on pins 23 and 25) to positive and negative amplitudes centered on VREF. The level shift circuit's output is BTL-output from the buffer amplifier.

Because of the high input impedance, the IC is designed to accommodate a filter comprising attached resistors and capacitors.

#### (Example) For secondary filters

Fig. 5

#### Operation notes

- (1) The BA6392FP has an internal thermal shutdown circuit. Output current is muted when the chip temperature exceeds 180°C (typically).

- (2) The output current can also be muted by lowering the mute pin (pin 15) voltage below 0.5V.

- (3) All four driver output channels are muted during thermal shutdown, muting and a drop in bias pin voltage. No other components are muted.

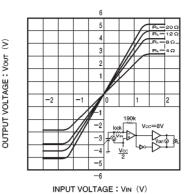

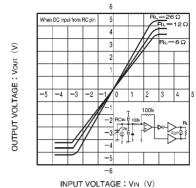

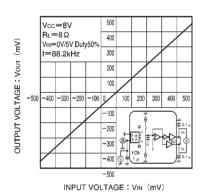

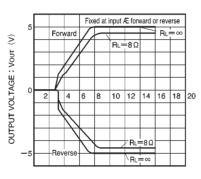

#### Electrical characteristics curves

Fig. 6 Thermal derating curve

Fig. 7 Spindle driver (CH4) I / O characteristics

(load variation)

Fig. 8 I / O characteristics of driver

stages CH1-CH3

Fig. 9 I / O characteristics with pulse input (drivers CH1-CH3)

POWER SUPPLY VOLTAGE: Vcc (V)

Fig. 10 Driver CH1-CH3 power supply voltage vs. output voltage

●External dimensions (Units: mm)