# HORIZONTAL APC/AFC LOOPS

Prepared by Linear Applications

The most popular method used in modern television receivers to synchronize the line frequency oscillator is the phase locked loop. Although in detail the circuits may vary considerably, the fundamental operation is the same. Any designer with a good understanding of phase locked loops in general and the required operating characteristics of television line frequency oscillators in particular, should be able to handle these circuits successfully.

For color television signal transmissions in the United States, the line frequency  $(f_H)$  is directly related to the color subcarrier frequency  $(f_{SC})$  such that:

$$f_H = \frac{2Xf_{SC}}{455}$$

Since  $f_{sc} = 3.579545$  MHz  $\pm 10$  Hz, then the line period is given by:

$H = 63.5555 \pm 0.0002 \mu s$

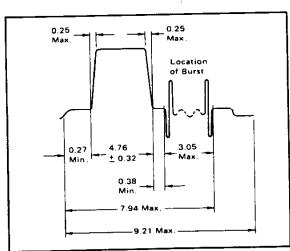

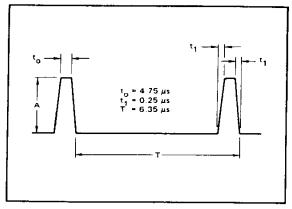

FIGURE 1 - Timing Detail of Line Sync Pulse (µs)

For satisfactory operating characteristics, the receiver must meet the following requirements:

# 1. Dynamic Phase Accuracy:

or repetitive phase accuracy. If the phase of a scan line is shifted with respect to the preceding line, a loss of detail can occur. For a given video frequency, a half cycle error from line to line will cause a complete loss of information at that frequency. At the system limit of 4.5 MHz, this corresponds to a 0.111  $\mu$ s timing error between adjacent lines or a repetitive phase accuracy of 0.62 degrees. Should thermal noise be present in the signal, the misstiming will be masked and much larger phase errors are tolerable. (See later discussions on noise performance.)

# 2. Static Phasing:

or-static phase error with the line oscillator at nominal frequency ( $f_H$ ). For monochrome receivers, this is determined by the tolerable shift of the picture information with respect to the raster and may be as much as 1.5  $\mu$ s. For color receivers, it is generally much less ( $< 0.5 \mu$ s) to permit gating the burst information on the back porch of the signal.

# 3. Static Phase Error (with detuning):

When the line oscillator is detuned from the nominal line frequency, the timing between the picture information and the receiver raster will change. For an inexpensive monochrome receiver, this error can be large (2 µs for  $\Delta_{

m f}$  = 300 Hz), particularly if the screen is overscanned and the picture escutcheon masks the sides of the raster. For a color receiver, the S.P.E is usually smaller. Figure 1 gives the tolerance of the burst envelope on the signal backporch and shows that the burst can occupy a 3 µs 'window' with respect to the leading edge of the sync pulse. The gating pulse for the burst channel is as narrow as possible to keep the chroma system noise bandwidth low and to prevent gating adjacent picture information or sync widgets. A gate pulse of 4 µs accurately centered when the line oscillator is at  $f_H$  will permit an S.P.E. of  $\pm 0.5~\mu s$ and yet maintain proper gating. Thus, for optimum performance, the S.P.E. over the detuning range of the line oscillator should be no more than  $\pm 0.5 \mu s$ .

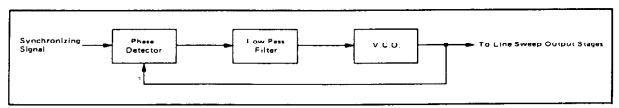

FIGURE 2 - APC/AFC Loop Theory

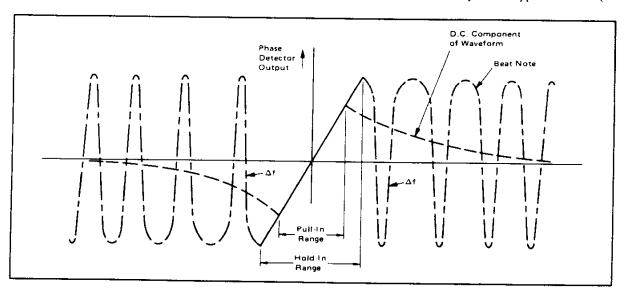

#### 4. Hold-In Range:

This is the total frequency deviation from fH over which an already synchronized oscillator will remain in synchronism, with no interruption of the synchronizing signal. This can typically be from 600 Hz to 800 Hz but is not usually designed for and occurs as the result of other design considerations.

#### 5. Pull-In Range:

This is the total frequency deviation of the line oscillator from fH over which the receiver will remain in synchronism, even following a momentary interruption of the synchronizing signal. Expressed another way, it is the limits of free-running oscillator frequency from which the oscillator will pull into synchronism on application of a synchronizing signal. The required pull-in range will depend on the frequency stability of the line oscillator and the permissible static phase error. It is usually >±180 Hz.

#### 6. Pull-In Time:

The time taken to synchronize from the limits of the pull-in range. Anything less than I second is considered instantaneous.

Four parameters are of primary interest; the phase detector sensitivity, the oscillator sensitivity, the loop gain, and the filter transfer characteristic.

# 1. Phase Detector Sensitivity $(\mu)$ :

The phase detector compares the incoming synchronizing signal with the line frequency oscillator signal and develops a control voltage that is proportional to the magnitude and polarity of the phase difference between the signals. If for a given phase difference at the phase detector of  $\delta \phi$  a control voltage  $\delta E$  is generated, then the phase detector sensitivity is defined as:

$$\mu = \frac{\delta E}{\delta \phi}$$

and is usually measured in volts/radian.

Since we are dealing with rectangular sync pulses and the signal from the oscillator is usually integrated to form a linear ramp, the phase detector output

$$E = \mu \phi$$

This is true over the stable operating region of the phase detector. (For further discussion of the stable and unstable operating regions, see Pull-In Range calculation on page 6.)

### Oscillator Sensitivity (β):

If a voltage  $\delta E$  at the control terminal of the oscillator produces a change of  $\delta_f$  in the free-running frequency of the oscillator, then the oscillator sensitivity  $(\beta)$  is defined

$$\beta = \frac{\delta f}{\delta E}$$

and the usual units are hertz/volt.

# 3. D.C. Loop Gain (f<sub>c</sub>):

When the oscillator has a tuning error of  $\Delta_f$  Hz, then the required correction voltage at the control terminal of the oscillator is  $\Delta f/\beta$ . If the system is capable of producing this correction voltage, the oscillator will remain in synchronism and the output voltage from the filter will be d.c. If the filter has a d.c. transmission of 100%, the phase detector output is  $\Delta_f/\beta$  and a static phase error of  $\phi$  will exist between the inputs of the phase detector to maintain this voltage.  $\therefore \mu \phi = \Delta_f / \beta$

or

$$\phi = \frac{\Delta_f}{\mu \beta}$$

The quantity  $\mu\beta$  is defined as the d.c. loop gain (f<sub>c</sub>) although its units are Hz/rad.

It is clear that the S.P.E. is directly proportional to the error in oscillator free-running frequency and is inversely proportional to the d.c. loop gain. The S.P.E. can be made as small as desired for a given tuning error by increasing the d.c. loop gain. However, note that the phase error  $\phi$ thus far defined is the static or long term phase error. To determine the dynamic phase error, i.e., the effect of impulse or thermal noise of the loop performance, we must evaluate the loop filter characteristics.

4. Filter Transfer Characteristic F<sub>(p)</sub>:

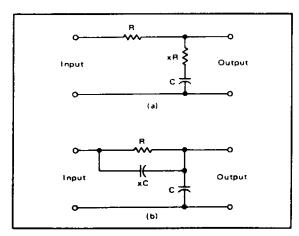

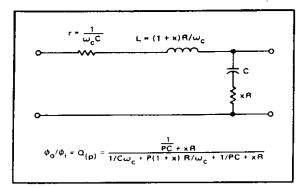

The low pass filter connected between the phase detector and the oscillator will have a significant effect on the loop performance. As this part of the system is the one most open to design adjustment, it should be fully understood. If single time-constant networks are used, it

FIGURE 3 - Typical Filter Networks

becomes impractical to achieve both small S.P.E.'s and small dynamic phase errors (low noise bandwidths) since the former requires a large value for  $f_{\rm C}$  and the latter a small value for  $f_{\rm C}$ . To avoid this compromise, more elaborate networks are used.

Both a) and b) are equivalent "proportional plus integral" networks. The output control voltage is proportional to the current through R plus the integral of the current in C. At any frequency, the ratio of the output voltage to the input voltage is:

$$F(p) = \frac{1 + pT_1}{1 + pT_2}$$

where  $T_1 = xRC$

$T_2 = (1 + x)RC$

:.

$$F_{(p)} = \frac{1 + pxRC}{1 + (1+x) pRC}$$

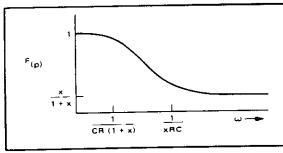

At d.c., the filter transmission F(p) = 1 and at high frequencies, the above expression reduces to  $\frac{x}{x}$

$$\therefore \frac{AC}{DC} \text{ gain ratio m} = \frac{x}{x+1}$$

The parameter m becomes important in the design of satisfactory loops.

FIGURE 4 - Filter Frequency Characteristics

# 5. Dynamic Phase Error or Noise Bandwidth:

Noise can be specified by its energy content and for a flat energy spectrum impulse noise and thermal noise are quite distinct. The relative phases of the frequency components of impulse noise are related and not random, although occurrence is a random variable. For thermal noise, the relative phases of the frequency components are completely random and incoherent and this type of noise is the most difficult to reject. Therefore, most of the following treatment is concerned with the rejection of thermal noise. However, methods to minimize the effects of impulse noise are also covered below in the selection of the filter components.

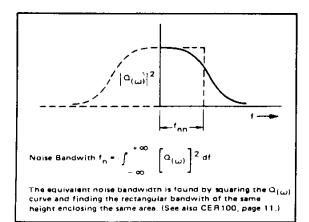

The presence of thermal noise in the signal will cause random variations in the output phase of the voltage controlled oscillator. An excellent way of determining the ability of the APC loop to reject thermal noise is to measure the noise bandwidth. This can be done by assuming a

noise free input phase which has sinusoidal variation with time and calculating the corresponding output phase. If this is repeated over a range of frequencies, the bandwidth for which the loop has significant variations in output phase can be determined, i.e., the noise bandwidth has been found.

For a loop that is initially phase locked, if the input phase changes to  $\phi_i$  with a corresponding output phase change of  $\phi_O$ , the resulting phase error of the system

$$\phi = \phi_i - \phi_O$$

and the phase detector

output voltage is  $\mu\phi$ . For a filter transfer function of F(p), the oscillator control voltage becomes

$$F_{(p)}\mu\phi$$

and the oscillator (with

sensitivity  $\beta$ ) will attempt to change frequency by

$$F_{(p)} 2\pi\mu\beta\phi$$

If frequency lock is to be maintained, the frequency shift of the oscillator must match the rate of change of the filter output phase

$$\therefore p\phi_{O} = F_{(p)} 2\pi \mu\beta\phi \qquad p = \frac{d}{dt}$$

$$2\pi \mu\beta = 2\pi f_c = \omega_c$$

or

$$p\phi + F_{(p)}\omega_c\phi = p\phi_i$$

3

This is the general D.E. for APC/AFC loops although its use for the asynchronous condition is subject to certain restrictions given later.

$$\therefore \phi_i = \phi_0 \left\{ 1 + \frac{P}{\omega_c F(p)} \right\}$$

... The phase transfer ratio

$$\frac{\phi_0}{\phi_i} = Q_{(p)} = \frac{F_{(p)}}{F_{(p)} + P/\omega_c}$$

(4)

Now for either of the filters shown in Figure 3,

$$F(p) = \frac{1 + pxRC}{1 + p(1+x)RC}$$

putting RC = T

P = j\omega

$$\therefore Q_{(\omega)} = \frac{1 + j\omega xT}{1 - \omega^2(1+x)T/\omega_c + j\omega(xT + 1/\omega_c)}$$

It is important to note the presence of  $\omega_c$  in the above expression. While the filter can modify the control voltage applied to the oscillator, the final output phase will depend on the loop gain  $f_c$ . The S.P.E. can be modified for a given detuning by changing  $f_c$  alone. The dynamic phase error can be modified by changing either  $f_c$  or F(p), or both

FIGURE 5

A plot of  $Q_{(\omega)}$  against input frequency (noise frequency) will show the ability of the loop to reject thermal noise in the synchronizing signal.

The integration is carried out from  $-\infty$  to  $+\infty$  since the abscissa does not represent the absolute frequency of the noise but the difference frequency between the noise and the oscillator frequency as detected by the phase detector. The phase detector output does not distinguish between frequencies above or below the oscillator frequency. A term commonly used for APC loops is the noise semibandwidth  $f_{nn}$ .

$$f_{nn} = \frac{f_n}{2} = \int_0^\infty |Q(\omega)|^2 df$$

$$\left[Q_{\omega}\right]^2 = \frac{1 + \omega^2 x^2 T^2}{\left[1 + \frac{\omega^2}{\omega_c} (1+x)T\right]^2 + \omega^2 \left[xT + 1/\omega_c\right]^2}$$

$$\therefore f_{nn} = \frac{\omega_c \left[ 1 + \frac{x^2 T \omega_c}{(1+x)} \right]}{4 \left( 1 + x T \omega_c \right)}$$

6. Other Synchronized Loop Characteristics:

It should be clear from  $\bigcirc$  above that if  $x \neq 0$  (1) for a given value of d.c. loop gain to produce satisfactory static phase performance, two parameters are available to produce satisfactory dynamic phase performance (x and T).

(1) If the filters of Figure 3 are simplified by pulling x = 0, then eq. (5) reduces to  $f_{nn} = \frac{\omega_c}{4}$ . Since  $\phi = \frac{\Delta\omega}{\omega_c}$ , then  $f_{nn} = \frac{\Delta\omega}{4}$ .

Thus with x = 0 and a given detuning error, the S.P.E. and  $f_{nn}$  cannot be chosen independently.

To obtain an idea of the best way to vary these parameters, assume that  $\phi_i$  and  $\phi_0$  are the voltage input and output of a low pass filter (Figure 6).

FIGURE 6 - Equivalent Voltage Transfer Filter

Step inputs to this filter can easily cause ringing. The output, following a step change in input phase (from signal source switching or a temporary spike of impulse noise) will assume a steady state following a transient.

Now,

$$Q_{(p)} = \frac{\phi_0}{\phi_i}$$

The steady state (particular solution) is  $\phi_i - \phi_0 = \phi$ . The transient (complementary function) is given by:

$$\frac{1}{Q_{(p)}} = 0$$

i.e.,  $(1+x) Tp^2 + (1+xT\omega_c) p + \omega_c = 0$

Solving for p, we have:

$$P = \frac{-(1+xT\omega_c) \pm \sqrt{(1+xT\omega_c)^2 - 4(1+x)T\omega_c}}{2(1+x)T}$$

(6)

The real part of 6 will give the natural undamped monant frequency of the loop.

$$\omega_{\rm n} = \frac{\sqrt{4(1+x)T\omega_{\rm c}}}{2(1+x)T} = \sqrt{\frac{\omega_{\rm c}}{(1+x)T}}$$

The quantity under the root sign in equation 6 will determine the response of the loop to a step input. For critical damping, this quantity will be zero.

$$(1+xT\omega_c)^2 = 4(1+x)T\omega_c$$

If we define a damping coefficient K =

$$\frac{(1+xT\omega_c)^2}{4(1+x)T\omega_c}$$

8

then, K = 1 and the loop is critically damped.

K > 1 and the loop is overdamped.

K < 1 and the loop is underdamped and a period of oscillatory ringing will occur.

The values of  $\omega_{ extsf{n}}$  and K will have a significant effect on the loop synchronous performance. If  $\omega_n$  is low K>1, the system may take an appreciable time to reach a stable state following a change of input phase. Therefore, there will be little transient disturbance from impulse noise because of the sluggish reaction of the loop. However, if the input phase changes as a result of airplane flutter, the loop may respond too slowly to produce satisfactory tracking of the input signal. Also, the pull-in from an asynchronous condition may be sloppy and slow. Conversely, if  $\omega_n$  is increased and K < I, the loop can respond very rapidly to incoming phase changes, but may be unstable with oscillatory ringing when impulse noise is encountered. Suitable design values will depend on the required characteristics and the interaction of the APC loop with other subsystems in the receiver and these will be discussed in detail later. In general, it can be assumed that x << 1 and  $x T \omega_{\rm c}$ >> 1 so that the formulae derived above can be simplified.

$$\phi = \frac{\Delta f}{f_c}$$

$$f_{nn} = \frac{1 + x^2 T \omega_c}{4xT}$$

$$\omega_n = \frac{\omega_c}{(1 + x)T}$$

$$K = \frac{x^2 T \omega_c}{4}$$

$$8$$

# 7. Asynchronous Performance of the Loop:

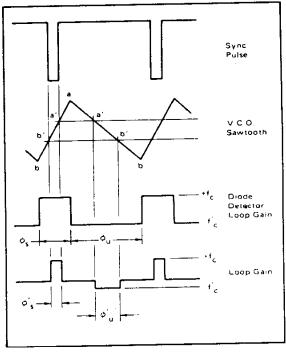

As the tuning difference ( $\Delta f$ ) between the oscillator free-running frequency and the incoming synchronizing signal increases, a larger static phase error is required at the inputs to the phase detector to maintain synchronism. Eventually, the phase detector output will stop increasing as the S.P.E. increases and the limit of hold-in will be reached (2). Should a further increase in  $\Delta f$  occur, the system becomes unstable and falls out of lock.

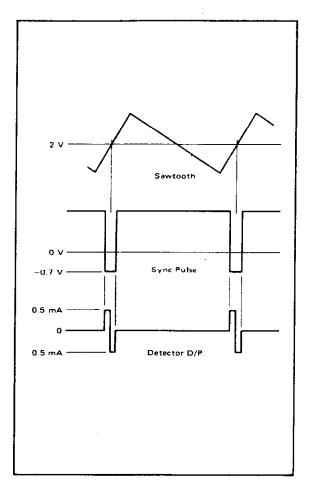

When the loop is out of synchronism, the phase detector will have two regions of operation (see Figure 7). If the sync pulse coincides with the steep slope of the integrated pulse from the V.C.O., this is the normal or stable operating region. The loop gain  $(f_{\rm C})$  is large and positive. When the sync pulse coincides with the more shallow slope of the sawtooth, operation is in the unstable region and the loop gain is much lower and negative.

(2) The Static Phase Error

$$\phi = \frac{\Delta f}{f_c}$$

and  $\phi$  max.  $= \frac{\phi_s}{2}$

( $\phi_s$  = width of stable operating region of the loop.)

$\therefore$  Maximum hold-in range  $\Delta f_{max} = \frac{f_c \phi_s}{2}$  —(10)

Notice, however, that the phase detector outputs always operate to reduce the period of the beat note produced by the frequency difference between the sync and sawtooth. Hence, the beat note is very asymmetrical and has an average d.c. output at the filter terminal. As  $\Delta f$  decreases, the average d.c. voltage will build up on the filter capacitor until pull-in is achieved.

FIGURE 7

If the maximum output from the phase detector is + E (obtained at points a and b on the sawtooth), then for the stable regions

$$f_{\rm c} = \frac{2 \beta E}{\phi_{\rm S}}$$

and for the unstable region  $\phi_{\mu}$

$$-f'_{c} = \frac{2 \beta E}{\phi_{\mu}}$$

$$\therefore f_c \phi_s = f'_c \phi_{\mu}$$

Two assumptions are implicit in the above: (1) the oscillator sensitivity  $(\beta)$  remains constant over the range of control voltages produced by the phase detector, and (2) the integrated fly-back pulse is a linear ramp. For a typical diode bridge phase detector, the width of the narrow slope of the sawtooth is the stable region. However, the above expressions will still hold even if this is not the case. Should the phase detector output limit at a and b on the slope, the areas under the loop gain curve are reduced

correspondingly with new stable and unstable regions  $\phi'_s$  and  $\phi'_\mu$  (this limitation could also be caused by the inability of the oscillator control to change the oscillator frequency close to the peak phase detector output voltages). For an integrated circuit phase detector, the MC1391, the phase detector output is limited to the sync-pulse width since it is a sync-gated system, i.e.,  $\phi_s = 4.75 \ \mu s$ .

When the loop is out of lock, a steady beat note output results from the phase detector. For a simple resistive filter (with no capacitors), the beat frequency would be constant and no pull-in would occur, but for the filters of interest the d.c. component of the waveform tends to reduce the mean tuning error. Thus at any time, the freerunning frequency of the oscillator in the absence of syncs will be greater than the off-set frequency obtained when the loop is closed. Notice, however, that as the detuning error increases, the waveform becomes more sinusoidal, reducing the d.c. component and the pull-in effect. Should the mean value of the d.c. component be found in terms of its frequency shifting capability, we can find the pull-in range and the pull-in time from any frequency within the pull-in range.

As shown in Appendix H, the maximum pull-in range  $\Delta_{f,max}$  is given by:

$$\Delta_{\text{f max}} = \frac{2 \phi_{\text{s}} f_{\text{c}} \sqrt{m}}{(3+m)}$$

if m << 1

The above expression, together with the formulae presented in 9, will completely specify the important characteristics of the conventional horizontal APC/AFC loop. The next section will cover the practical design use of these formulae, and detail instances of departure from the ideal case.

It should be apparent by now that the design of a satisfactory APC/AFC loop is not as straightforward as the simple block diagram of Figure 2 might have suggested. Five formulae are needed to define the characteristics of the loop and these formulae are not mutually independent. The designer has only three parameters that he can vary to fit all these formulae and meet his circuit needs. Further, his needs may change depending on the type and performance of circuits internal to the loop and, to complicate matters more, of circuits external to the loop. An obvious example of the former is the oscillator stability which will be a prime factor in determining the pull-in range required, and an example of the latter is the Static Phase Error permitted for correct burst gating in the chroma channel. If the burst is sync gated, then the S.P.E. requirement may not be as stringent although large oscillator drifts could result in high d.c. loop gain being needed that will also produce small S.P.E.'s.

Other factors that must be entered into the design concern the expected environment of the loop, both within the receiver and in the type and quality of the signals that will be received. Should the receiver manufacturer have a reputation for high performance in fringe reception areas, then he will be very concerned with thermal noise performance and the APC/AFC loop will tend to have small noise bandwidths. Alternatively, if the manufacturer is more concerned with urban reception, particularly near large airports, the loop will probably need to be high speed to track phase variations. More likely, the manufacturer will want the receiver to perform well everywhere and compromises must be made.

Within the receiver the characteristics of the loop will depend on the sync source and, for gated a.g.c. systems, the performance of the a.g.c. loop, especially when the horizontal oscillator is temporarily out of synchronism. Many loops use a dual diode arrangement for the phase detector and the sensitivity of this type of detector (see

FIGURE 8 - Detector Best Notes

Appendix) depends on the amplitude of the smaller of the two waveforms applied to it. The reference sawtooth waveform from the sweep circuit is usually chosen so that the phase detector sensitivity will not change with adverse signal conditions that affect the syncs. With a fixed oscillator sensitivity, the required d.c. loop gain can be obtained by changing the reference sawtooth waveform amplitude. For high loop gains and maximum flexibility, this means that the sync amplitude should be large –a requirement that can be difficult to meet in a 12 V. battery operated set. Alternatively, the effective amplitude of the sawtooth can be raised by using an active shaper network to increase the slope of the sawtooth.

A slow a.g.c. loop can seriously modify the apparent performance of the loop. If airplane flutter causes significant changes in the video detector output level and the sync separator is too slow to follow these changes, then the varying slice level will cause phase shifts at the input to the loop (see CER105). Also, when the line oscillator is out of lock, the gating pulse will activate the a.g.c. system during the video portion of the signal. This tends to make the a.g.c. loop increase the gain of the R.F. and I.F. amplifiers. Conversely, when the gate pulse and sync pulse coincide, the a.g.c. loop will attempt to reduce the R.F. and I.F. amplifier gains. The detector output that results from this process is modulated with a ripple corresponding to the frequency difference between the horizontal oscillator and the sync waveform. If the ripple amplitude is large then 'holes' will appear in the separated sync. The phase detector output beat note will be modified by these 'holes' and the mean d.c. voltage generated will be reduced causing a reduction in the oscillator pull-in range. This effect should be particularly noted when comparing a solid state receiver with an earlier tube or hybrid design. The introduction of I/C's into the receiver to perform the a.g.c. function (e.g., MC1345/44) has meant that coincidence of the sync and flyback pulse is necessary to gate the a.g.c. Since erroneous gating does not occur during the video portion of the signal, the detector level remains much more constant and wider pull-in ranges approximately the theoretical maximum (equation 11) are

A popular method of assessing the pull-in range is to offset the oscillator while syncs are applied to the loop. The 60 Hz component in the sync waveform is usually enough to cause a side-lock at multiples of the field frequency and the pull-in range is noted as the last side-lock on either side of 15.734 KHz from which the oscillator pulls into synchronism. Since the ripple at the detector increases as the oscillator approaches 15.734 KHz (the a.g.c. gate samples video for longer periods), the APC/AFC loop will get very little sync information and the beat note pull-in effect is correspondingly weak. Thus, for a tube design, the pull-in range obtained by the above method is close to the actual free-running frequency from which the oscillator can be locked. By measuring the picture offset on the CRT at the pull-in limits, the maximum stable phase error the system will tolerate is also found. However, with a solid state receiver using an improved a.g.c. system, a strong beat note (but no ripple at the detector) is generated when the APC/AFC loop is out of lock and the side-lock frequency limits at pull-in are significantly lower than the oscillator actual free-running frequencies at pull-in. Since the true pull-in range is not observed, the S.P.E. over the pull-in range obtained by the above method will be larger than a similar design with a poor a.g.c. system<sup>(3)</sup>.

Another characteristic of the APC/AFC loop that will depend in a large measure on the external circuitry is the required noise bandwidth. The effect of random noise in the sync waveform is to cause the position of individual picture elements to vary from instant to instant. The larger dynamic phase error that can be tolerated will depend on many subjective factors. For example: At the same time noise appears in the sync waveform, it will also be present in the video masking the true position of the picture elements. A moving picture or smaller screen size will also change the appearance of thermal noise.

In fact, when the video becomes unuseable at the picture tube because of the noise interference, then the signal to noise ratio at the detector can be considered the system limit. As far as the sync circuits are concerned, the received bandwidth can be reduced without seriously modifying the sync waveform. This will improve the signal to noise ratio for the sync signal with a corresponding reduction in the dynamic phase error under limiting conditions.

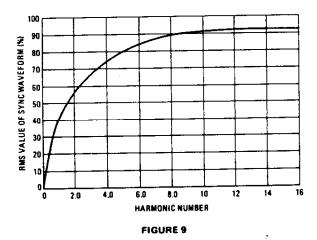

If we treat the syncs as a trapezoidal waveform, the contribution of each harmonic to the effective timing information can be calculated. This is shown in Figure 9 and it can be seen that 90% of the timing information is

<sup>(3)</sup> The reduction of the pull-in range vs. a.g.c. loop frequency response has been dealt with in the literature. However, the use of fast sync separators and the superior characteristics of I/C a.g.c. loops will probably make further investigation academic in nature.

FIGURE 10 (a)

contained in the first nine harmonics of 15.734 KHz a bandwidth of approximately 140 KHz. The bandwidth of many tube and hybrid designs has been as low as 100 KHz (determined primarily by the sync separator device) and this provides 87% of the available timing information with good thermal noise immunity. A typical solid state receiver has a bandwidth in excess of 1 MHz (determined by the circuits preceding the sync separator) and the noise bandwidth of the APC/AFC loop may have to be reduced, or further filtering in the sync channel before sync separation may be necessary to provide comparable thermal noise performance.

The approach to an APC/AFC design for a television receiver can take several different paths. For example: The design problem may simply be modification of a circuit to remove an undesirable characteristic caused by a faulty design, production spreads or a new operating environment. Cost reduction may be the objective, or adaptation of an existing circuit to a new chassis design.

Should any of the above conditions be encountered, the best starting point is to fully evaluate the fundamental characteristics of the present circuit. This naturally includes measurements of the oscillator and phase detector sensitivities. Those are usually quite simple to make and may require just disconnecting the phase detector output from the voltage (or current) controlled device in the oscillator circuit. Sometimes the loading of the oscillator circuit on the phase detector may have to be duplicated (particularly with solid state circuits) or the effect of loading allowed for. Since linear operation of practical circuits is rarely encountered, the characteristics should be measured over the expected operating range of each block.

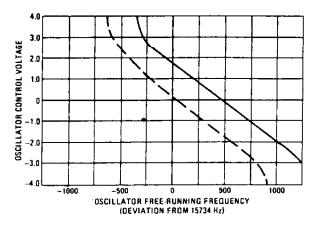

Figure 10(a) and (b) shows the measured sensitivity curves of a solid state monochrome receiver. In this particular case, asymmetrical pull-in was the problem and the cause is the change in oscillator sensitivity producing a fall in d.c. loop gain as the oscillator free-running frequency is lowered. Relocation of the d.c. operating point of the oscillator at 15.734 KHz is the solution (the dotted line on Figure 10).

Notice that the product of the two slopes will give

FIGURE 10 (b)

the circuit d.c. loop gain. This will define the Static Phase Error as the oscillator drifts. For this particular circuit, a drift of ± 180 Hz would produce an S.P.E. of  $\pm 1~\mu s$ . Clearly, if this design were to be adapted to a color receiver, the loop gain would have to be raised. Obviously, the amount of loop gain increase required will depend on the drift characteristics of the loop. Before any efforts are made to change the loop gain, the oscillator frequency variation with temperature and supply voltage should be measured and the effects of aging estimated. The lower operating ambient temperature of a solid state set means that the temperature/frequency drift can be held to less than ±190 Hz, including the turn-on warm-up drift. Wherever possible, if increased loop gain is still needed, the most stable circuit block should be changed or increased drift will result.

When further cost reduction will seriously impair the circuit performance, or the circuit already cannot meet the full performance capability of the simple APC/AFC loop, other circuits or a complete new design may have to be investigated.

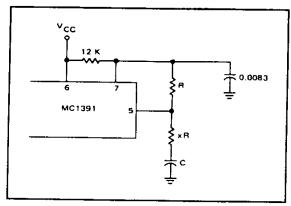

One excellent solution to the problem of low cost combined with full performance can be provided by an integrated circuit, either in combination with other circuit functions or simply as an APC/AFC block. Several I/C's performing this function are available and one circuit, the MC1391P, will be used to demonstrate the use and universality of the preceding theoretical analysis. The MC1391P is well suited for this purpose as its parameters are stable and well documented. Although it is an I/C, it is very flexible with an external filter and externally adjustable loop gain allowing any performance characteristic, within the limits of the simple APC/AFC loop, to be obtained. (See Figure 11 and Appendix)

The operating characteristics of the MC1391 are easily calculated (Ref. 5), or they can be measured. The oscillator sensitivity is best expressed in amps per radian as this is a current controlled device, and can be measured by disconnecting the phase detector output (pin 5) and noting the current through the filter resistor R into the oscillator timing pin (pin 7). This current can be positive

Since the available voltage swing at pin 5 before saturation occurs is 5.8 V, then:

$$R = \frac{5.8}{0.053 \times 10^{-3}} \cong 110 \text{ K}\Omega$$

$$\therefore$$

Put R = 100 K $\Omega$ ;  $\therefore$  xR = 4.2 K  $\simeq$  3.9 K $\Omega$

With these practical values, x = 0.039 and m = 0.038

$$C = T/R = 0.15 \,\mu\text{F}$$

The maximum possible pull-in range is given by equation (14):

$$\Delta f = \pm \frac{2 \times 0.46 \times 6000 \sqrt{-0.038}}{3 + 0.038}$$

$$= \pm 354 \text{ Hz}$$

From equation (5):

$$f_{nn} = \frac{1 + (0.039)^2 \times 0.015 \times 37699}{4 \times 0.039 \times 0.015}$$

= 795 Hz

The response time to recover from a step input is given by:

$$t = \frac{\log_{10} 0.1}{a}$$

where  $a = \frac{1 + xT_{wc}}{2(1 + x)T}$

i.e.,  $t = 3\mu s$  = 739.6

This example effectively shows the compromises involved in the design of an APC loop. In aiming for a fast responsive loop with a quick recovery time to give optimum tracking of incoming phase variations (airplane flutter, etc.), we have obtained a loop with a noise bandwidth about twice what it should be. The stability of the sync when the incoming signal is heavily contaminated with thermal noise may be considered unsatisfactory; a continual jitter or "rubber banding" will be evident on the CRT. Also, because of the high a-c gain and very low damping of the loop, impulse noise will cause 'tearing' as the loop attempts to follow the transient changes produced by the impulse noise.

To improve the design with respect to the noise performance, several things can be done—the problem is to decide which changes will have the least effect on the other loop characteristics.

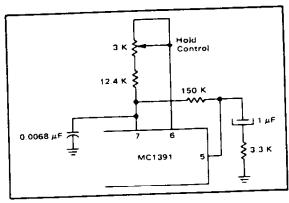

If the AC/DC gain ratio is reduced by changing x, the pull-in range will be reduced also. A safer course is to decrease the natural resonant frequency of the loop by modifying T, and a suitable design is shown in Figure 15.

FIGURE 15

The d.c. loop gain has been increased slightly to:

$$f_c = \frac{1.61 \times 10^{-4} \times 13.9 \times 10^3 \times 15734}{5}$$

= 7040 Hz/rad.

To limit the hold-in range to ±1 KHz,

$$\frac{R = 150 \text{ K}\Omega}{x = 0.022} \qquad \frac{xR = 3.3 \text{ K}\Omega}{m = 0.0215}$$

$$T = RC = 1X10^{-6} \times 150 \times 10^3 = 0.15$$

The lower loop time constant reduces the natural resonant frequency to 85 Hz and the damping coefficient K=0.8.

$$f_{nn} = 1 + \frac{(0.022)^2 \ 0.15 \times 2\pi \times 7040}{4 \times 0.022 \times 0.15} = \frac{319 \ Hz}{}$$

The pull-in range is slightly lower at  $\pm 315$  Hz, and the recovery time from a step transient is  $4.8~\mu s$ .

# REFERENCE AND FURTHER READING:

- 1. GARDNER, F. M.

- "Phaselock Techniques"

John Wiley and Sons, New York, 1966.

- 2. GRUEN, W. J.

- "Theory of AFC Synchronization"

Proceeding of the L.R.E. pp 1043-1048, Aug. 1953.

- 3. HEROTA, NABEYAMA, MIYAZAKI

- "Design and Analysis of the Pull-In Range of Horizontal AFC in Television Systems"

- 4. RICHMAN, D.

- "Color Carrier Reference Phase Synchronization Accuracy in the N.T.S.C. Color Television"

Proceedings of the I.R.E. pp 106 133, Jan. 1954.

- 5. WILCOX, M.

- "A TV Horizontal I/C"

manufacturer, it avoids the use of a large inductor that may be subject to pick-up from toroidal yokes, for example. However, unless an expensive multiturn pot is used, the entire operating range of the oscillator is covered in a 320° rotation of the hold control. If the control capability is ±750 KHz, then each degree of rotation will change the oscillator frequency by 4.7 Hz. When an L-C oscillator is used, the t.p.i. of the inductor core can be used to limit the frequency change for a single 360° rotation of the hold control, thus making a relatively insensitive setting.

Notice that the warm-up drift is not included in the above figure. This is the drift that occurs during the first few minutes after turn on as the I/C package temperature stabilizes to the 25°C ambient. It is not included since the hold control is usually adjusted after this period and unless it exceeds the pull-in range of an 'instant on' receiver, it cancels out and is not noticed.

The *minimum* loop gain is now defined by the permissible phase error over this frequency duration. Use equation (1):

$$\frac{0.5 \times 2\pi}{63.5} = \frac{190}{f_c}$$

$$\therefore$$

f<sub>c</sub> = 3840 Hz/rad.

The drift characteristic has also defined the minimum pull-in range that can be tolerated and usually, if other dynamic performance characteristics are to be satisfactory, the value of loop gain given above is insufficient to guarantee pull-in over  $\pm 190$  Hz. Also, the oscillator sensitivity and the phase detector sensitivity are subject to component tolerance and manufacturing tolerance and the loop gain must be in excess of 3800 Hz/rad to ensure that the S.P.E. will be maintained below 0.5  $\mu$ s. It is a safe assumption that at least 50% more loop gain than the minimum will be needed.

$$\therefore$$

f<sub>c</sub> =  $\mu\beta$  = 6000 Hz/rad.

Now the frequency deviation can be as much as ±300 Hz for acceptable phase performance.

The phase detector sensitivity of the MC1391 is nominally:

$$\mu = 1.6 \times 10^{-4} \text{ A/rad}$$

.

(assuming a sync pulse deviation of 4.7  $\mu$ s, i.e.,  $\phi_s = 4.7 \times 0.095 = 0.46$  rads.)

Therefore, the required oscillator sensitivity  $\beta = 37.3 \times 10^6 \text{ Hz/A}$ .

FIGURE 12 - MC1391 Filter Circuit

To obtain this sensitivity, the timing resistor at pin 7 must be  $12 \text{ K}\Omega$  when the free-running frequency is 15.734 HKz, which will give a timing capacitor value of:

$$C = \frac{10-4}{12 \times 10^{-6}} = 0.0083 \,\mu\text{F}$$

The next part of the design procedure, the filter network, can appear somewhat arbitrary in nature as this is the area in which a designer can emphasize one performance characteristic but only at the expense of others.

Before making a first-cut try at the design, it should be noted that the resistor R between pins 5 and 7 can have a significant effect on the loop other than its function as part of the filter.

Earlier it was stated that the stable operating region of the phase detector in the MC1391 is confined to the width of the sync pulse. With the value of loop gain chosen previously, this means that the hold-in range of the oscillator can be as much as:

$$\frac{\pm 2.35 \times 2\pi \times 6000}{63.5} \simeq \pm 1400 \text{ Hz}$$

and obviously if higher loop gains are needed for the synchronous performance, it will become possible for the oscillator free-running frequency to deviate even more from 15.734 HKz at the hold-in limits. The full hold-in range can be realized, of course, only if the loop remains linear over the stable operating region. Should the value of R be large, then the available voltage swing at pin 5 will not permit the full phase detector current to be applied to pin 7, i.e., the phase detector will saturate. Reducing the hold-in frequency limit can be desirable and making the value of R fairly large to do this is a useful technique. (For a discrete circuit actively shaping the reference sawtooth to increase its slope or using limiting diode clamps on the oscillator control pin will have the same effect.)

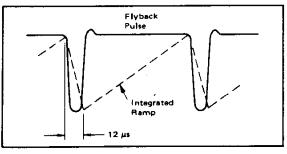

When a step input phase change is applied to the loop, the response should be as rapid as possible to reach the new equilibrium. Two characteristics of the loop will define how far it can respond, the natural resonant frequency

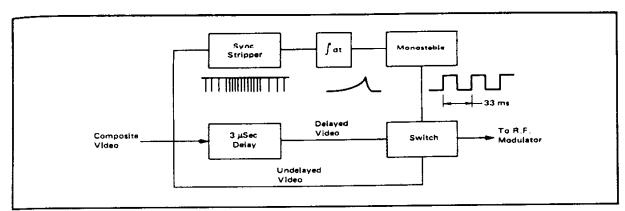

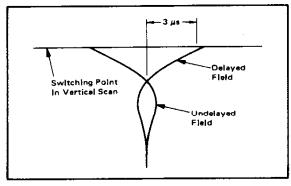

FIGURE 13 - Jitter Generator

and the amount of overshoot permitted when the correct phase has been reached. Both of these characteristics can be ideally demonstrated by using a Jitter Generator. This generator is inserted into the video channel of the r.f. modulator used to supply a signal to the receiver and it introduces (typically) a 3  $\mu$ s delay during one field and then switches back to an undelayed signal on the next field.

This switching between delayed signal and undelayed signal will cause a vertical line in the video to trace the transient response of the loop on the CRT of the receiver. A typical response is shown in Figure 14.

An ideal response would be one that approached equilibrium as fast as possible without overshooting or 'hunting.' This indicates that the damping should be critical and the natural resonant frequency high, but this will result in a system with high a-c loop gain corresponding to large noise bandwidths. The effect of a fast recovery with lower natural resonant frequencies and acceptable noise bandwidths can be obtained by allowing some overshoot to occur. Usually the recovery from the transient should be complete within 1/3 to 1/2 of the field scan period. If a single overshoot is permitted, this will tend to limit the natural resonant frequency to a maximum of 363 Hz or 250 Hz, respectively (more than one overshoot during the recovery time indicates high natural resonant frequencies and large noise bandwidths with the chance of ringing to occur on impulse noise).

FIGURE 14 - Typical Transient Display on a CRT

Choosing a high natural resonant frequency of 250 Hz means that x should be selected to minimize the noise bandwidth.

From equation (5):

$$\frac{d}{dx}(f_{nn}) = -\frac{1}{4 x^2 T} + \frac{W_c}{4} = 0 \text{ for a minimum.}$$

i.e.,

$$x = \sqrt{\frac{1}{W_c T}}$$

From equation (8), this produces a value of 0.25 for K.

$W_c = 2\pi x 6000 = 37699 \text{ rads/sec. volt}$

and

$$W_0 = 2\pi x 250 = 1571 \text{ rads/sec}$$

If x is small, then  $W_n \simeq \sqrt{\frac{W_c}{T}}$

$$T = \frac{37699}{(1571)^2} = 0.0153$$

$$\therefore x = \frac{1}{\sqrt{37699 \times 0.0153}} = \frac{0.0417}{}$$

$$\therefore m = \frac{x}{x+1} = \underline{0.04}$$

If we decide to limit the hold-in range to  $\pm 1$  KHz then the linear operating region of the phase detector  $\phi$  must be limited to:

$$\phi = \frac{2000}{f_c} = 0.33 \text{ radians}$$

The phase detector average current change =  $\mu\phi_S$  =

$$1.61 \times 10^{-4} \times 0.33 = 0.053 \text{ mA}$$

or negative corresponding to the direction of the oscillator frequency offset. Note, however, that the oscillator sensitivity is dependent on the impedance at pin 7 and can be increased by raising the value of the timing resistor (with a concomitant reduction in the capacitor value to keep the same time constant). This is the method by which the circuit loop gain can be changed to suit the design aims.

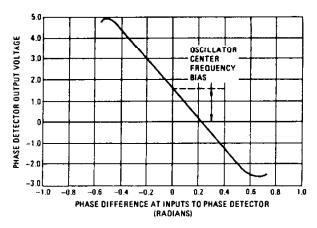

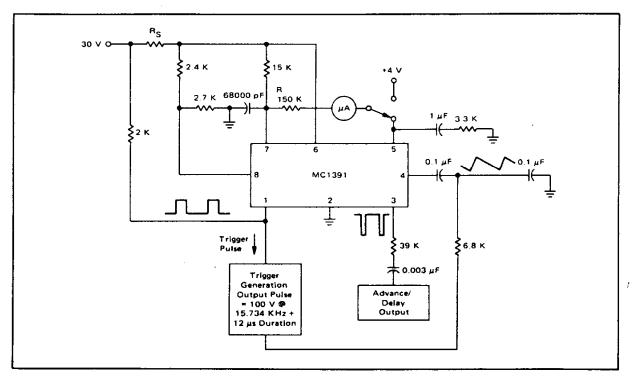

Since the oscillator characteristic around the centre frequency of 15.734 KHz is very linear, the phase detector sensitivity can be determined simply by producing a known phase error between the sync and flyback pulses and noting the resulting oscillator free-running frequency to produce this error when the phase detector is disconnected. The measured oscillator characteristic will then indicate the phase detector offset current for this phase error. In a more general case, the oscillator characteristic may not be linear (see Figure 10a) and the above method would not give a direct evaluation of the phase detector characteristic and a more complicated method must be resorted to. A typical set-up is shown in Figure 11 where a generator is used to provide the flyback pulse and is also phase-locked to a second generator which provides the sync pulse. By using the advance/delay pulse output from the second generator, the inputs to the phase detector can be varied by known phase differences and the detector output current measured. This method has the additional advantage that any loading by the oscillator on the phase detector is retained for a true operating characteristic. The phase detector characteristic of the MC1391 is also very linear with the end points occurring at the edges of the sync pulse as this is a sync gated detector. Notice that the

operating range of the diode detector in Figure 10 is nearly  $\pm 6~\mu s$ -or the flyback pulse width. For that loop, the stable operating region is determined partially by the oscillator characteristic rather than wholly by the phase detector as it is with the MC1391.

Once the phase detector characteristic is known, it is an easy matter to select the oscillator impedance for the oscillator sensitivity required to produce sufficient circuit d.c. loop gain. How much loop gain is sufficient will depend on several factors.

Primarily, there must be enough gain to maintain the Static Phase Error within defined limits, ideally  $\pm 0.5 \,\mu s$ for a flyback pulse gated chroma channel. Because the oscillator section of the MC1391 is designed for a nominal zero temperature coefficient, the free-running frequency can drift in either direction from 15.734 KHz. Over a 30°C operating temperature range, the drift can be as much as +25 Hz. The external frequency determining elements will add another ±75 Hz drift if the hold control is typically 10% of the total timing resistance (polystyrene and polyster capacitor ±100 p.pm/°C. Cermet Pot 150 ppm/OC and NC5 resistor). Apart from temperature drift of the oscillator an S.P.E. can be caused by the permissible transmitter tolerance for f<sub>H</sub>, and sometimes CCTV applications must be considered, adding another 20 to 30 Hz. Finally, operator error must be included, that is the possibility of an incorrectly set hold control either by the factory or by the serviceman/customer.

The advantage of an R-C oscillator, from the I/C designer's viewpoint, is that both timing and oscillator control can be achieved with a single pin-out. For the set

FIGURE 11 - Test Set-up for Measuring Oscillator and Phase Detector Characteristics

# APPENDIX A

$$f_{H} = 15.734 \text{ KHz}$$

$$T = 63.5 \, \mu sec.$$

$1 \mu s$  at  $f_H = 5.699$  degrees = 0.0989 radians

# APPENDIX B

# Loop Recovery Time From a Step Transient.

The D.E. of the loop can be written:

$$p^2 + \frac{(1+xTw_c)p}{(1+x)T} + \frac{W_c}{(1+x)T} = 0$$

$$p^2 + 2ap + c = 0$$

i.e., The envelope decay =  $K_e^{-at}$

The envelope decay =  $K_e^{-at}$

where K is proportional to the initial step amplitude.

$$\therefore a = \frac{1 + xTw_c}{2(1 + x)T}$$

Therefore, the time to decay to 10% of the initial offset is given by:

$$e^{-at} = 0.1$$

$$\therefore t = \frac{\log_n 0.1}{-a}$$

$$=\frac{\frac{2.303}{(1+xTw_c)}/(1+x)T}$$

# APPENDIX C

# Spectrum of the Horizontal Sync Waveform.

For a trapezoidal waveform of amplitude A, period T and duration  $t_0$  with rise and fall times of  $t_1$  then:

$$A_{rms} = \sqrt[A]{\frac{3t_0 + 2t_1}{3T}}$$

$A_{avg} = A \frac{(t_0 + t_1)}{T}$

= A x 0.278

Amplitude of the nth harmonic:

$$A_{n} = 2A_{avg} \left\{ \frac{\sin \pi n t_{1}/T}{\pi n t_{1}/T} \bullet \frac{\sin \pi n \left(\frac{t_{1}+t_{0}}{T}\right)}{\pi n \left(\frac{t_{1}+t_{0}}{T}\right)} \right\}$$

$$= A \cdot 0.1575 \times \frac{\sin(0.0124n)\sin(0.247n)}{3.06 \times 10^{-3} \times n^{2}}$$

Calculating the contribution of each harmonic to the total effective value generates the curve shown in Figure 9.

FIGURE C-1

# APPENDIX D

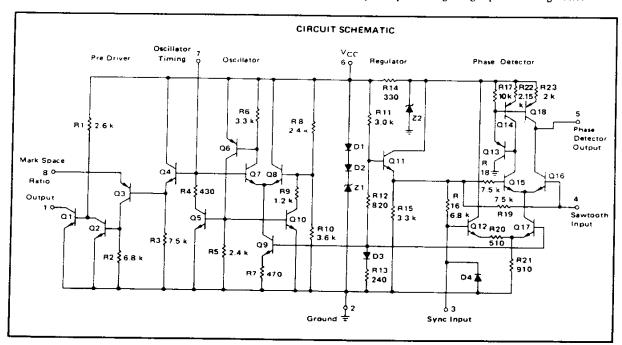

# Circuit Diagram of the MC1391.

The output pulse width is adjusted by the resistive divider at pin 8. For stable operation, the impedance at

pin 8 should be close to 1 K $\Omega$ . To advance the static phasing, a small resistor (<100  $\Omega$ ) can be placed between the flyback pulse integrating capacitor and ground.

FIGURE D-1

# APPENDIX E

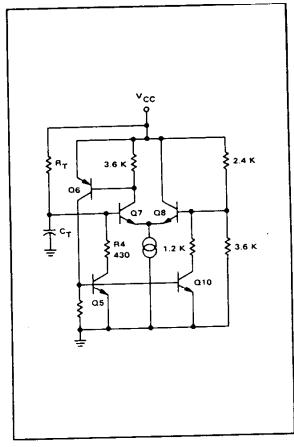

# The MC1391 Oscillator Circuit.

If it is assumed that Q7 is initially off, then the capacitor connected from pin 7 to ground will be charged by an external resistor (RT) connected to pin 6. As soon as pin 7 voltage exceeds 5 V, the potential at Qg base, Q7 will conduct allowing Q6 to supply base current to Q5 and Q10. Transistor Q10 sets the base of Q8 at approximately 2 V. Q5 then discharges  $C_{\Upsilon}$  through  $R_4$  until pin 7 reaches 2 V and Q7 turns off again and the cycle repeats.

The frequency of oscillation is given by:

$$I_{o} = \frac{1}{\iota_{c} \iota_{n} \left( 1 + \frac{R_{2}^{2}}{R_{1}R_{2} + R_{1}R_{3} + R_{2}R_{3}} \right) + \iota_{d} \iota_{n} \left( 1 + \frac{R_{1}R_{2}}{R_{1}R_{3} + R_{2}R_{3}} \right)}$$

and for  $f_0 = 15.734 \text{ KHz}$

$$t_c \Omega 10^{-4}$$

if  $R >> R4$

t<sub>c</sub> = charge time constant = R<sub>T</sub>C<sub>T</sub>

$t_d$  = discharge time constant =  $R_4C_T$

For small frequency deviations, the oscillator sensitivity:

$$\beta = \frac{15.734 \times R_T}{5 \text{ V}} \qquad \text{Hz/A}$$

The sensitivity can be adjusted by changing the external resistor RT.

FIGURE E-1

### APPENDIX F

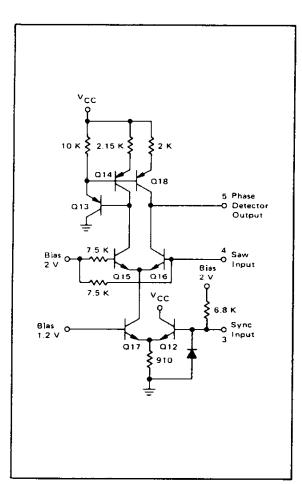

# Phase Detector Operation of the MC1391P.

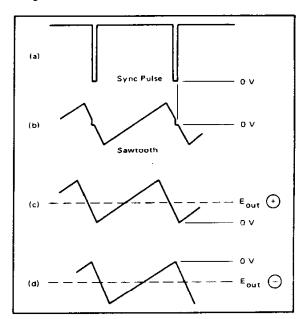

The phase detector consists of the comparator Q<sub>15</sub> and Q16 and the gated current source Q17. Negative going sync pulses (1 V to 5 V (p-p)) at pin 3 turn off  $Q_{12}$  allowing  $Q_{17}$  to conduct. The current division between Q15 and Q16 during the sync pulse period will be determined by the phase relationship between the syncs and the sawtooth at pin 4 which is derived from the horizontal flyback pulse. If the steep slope of the sawtooth is symmetrical about the sync pulse (Figure F2), then Q15 and Q16 will each conduct for half the sync pulse period. When the sawtooth is just less than 2 V, Q<sub>15</sub> conducts all the Q<sub>17</sub> current, and this current is turned around by Q<sub>18</sub> to flow out of pin 5. When the sawtooth is above 2 V, Q16 conducts and current flows into pin 5; thus the net current at balance is zero. When a phase offset occurs, there will be an average current flow either in or out of pin 5 to speed up or slow down the oscillator. Note that if the sawtooth amplitude is greater than about 1 V (p-p), the change in voltage at pin 4 to completely switch the comparator is small compared to the amplitude of the

saw. Switching can be considered instantaneous and the detector sensitivity is independent of either the sawtooth amplitude or the sync pulse amplitude.

The average phase detector current goes from zero to full output in half the sync pulse width:

$$\therefore \mu = \frac{(l_{peak} \times duty \ cycle)}{(conduction \ period)}$$

$$= \frac{0.5 \times 10^{-3} \times \frac{4.7}{63.5}}{0.5 \times 4.7 \times 0.098} \text{ A/rad}.$$

If the sawtooth is reasonably linear, then the phase detector output current

$$\pm 1 = \mp \mu \phi$$

where  $\phi$  is the phase difference between the oscillator and the sync pulse.

FIGURE F-1

FIGURE F-2

## APPENDIX G

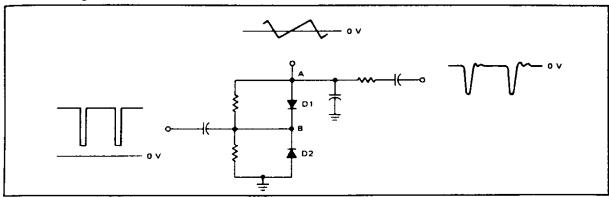

# **Dual Diode Bridge Phase Detectors**

FIGURE G-1 - Diode Bridge

In the simple dual diode bridge phase detector, the negative going sync pulse tips are clamped to ground by D<sub>2</sub> and the waveform at B is shown in Figure G2(a). The output voltage from the bridge due to the sync waveform is very small because the diode D<sub>1</sub> is back biassed between the sync pulses (when B is very positive) and the impedance at A, determined largely by the integrating capacitor for the flyback pulse, is small compared to the diode load resistors. Therefore, when an a.c. coupled sawtooth is applied to A and the phase is such that the steep slope of the waveform is symmetrical about the sync pulse, the waveform at A is as shown in Figure G2(b). The bridge output is nominally zero. If the oscillator beings to lead the sync pulses, the sawtooth is clamped later on its steep portion as shown in G2(c) and a net +ve voltage is obtained. This voltage is filtered and applied to the control device to slow the oscillator down. Similarly for a lagging oscillator, a net -ve voltage is developed to speed the oscillator up (Figure G2(d)). Notice that the output voltage obtained is a maximum at each end of the sawtooth steep slope, i.e., the stable operating range is over the flyback pulse width. If the flyback pulse width is  $\phi_S$  radians and the peak-topeak sawtooth amplitude is E volts, then:

$$\mu = \frac{E}{\phi_s}$$

volts/radian

and the phase detector output voltage for a phase shift between oscillator and sync pulse of  $\pm \phi$  is:

$$\pm E_{out} = \pm \mu \phi$$

Obviously, the phase detector sensitivity can be increased by increasing the reference sawtooth amplitudes (but not to the point where the sawtooth can start the diode  $D_1$  into conduction—the saw amplitude must be less than the sync pulse amplitude). Alternatively increasing the slope (reducing  $\phi_s$ ) has the same effect. The simple diode detector is very dependent on the sawtooth shape and amplitude. If the sync amplitude is large, then the bridge is

relatively independent of amplitude modulation of the syncs, but if these are heavily differentiated amplitude modulation will also cause phase modulation when the bridge is unbalanced.

FIGURE G-2

FIGURE G-3

#### APPENDIX H

Derivation of the Approximate Expression Given in Equation (10) for the Maximum Pull-In Range.

The general D.E. for the loop is:

$$\dot{p}\phi + F_{(p)}\omega_c\phi = p\phi_i$$

which can be rewritten:

$$\frac{d\phi}{dt} + F_{(p)}\omega_c\phi = \Delta\omega$$

Now

$$F_{(p)} = \frac{1+pxT}{1+p(1+x)T} = \frac{1-m+pT}{1+m+pT}$$

since

$$x = \frac{m}{m-1}$$

$$F_{(p)} = m + \left\{ \frac{1 - 2m + m^2}{1 - m + pT} \right\}$$

Substituting this in equation (11) gives:

$$\frac{d\phi}{dt} + mw_c\phi + \left\{ \frac{1 - 2m + m^2}{1 - m + pT} \right\} \quad \omega_c\phi = \Delta\omega$$

If we write

$$W_1 = \Delta\omega - \left\{ \frac{1 - 2m + m^2}{1 - m + pT} \right\} \omega_C \phi$$

then  $W_I$  is the effective instantaneous impressed frequency difference, produced by the detuning error of the oscillator  $(\Delta\omega)$  and the frequency drift generated by the correction voltage across the filter capacitor. As pull-in progresses the right-hand term will cause  $\omega_I$  to be reduced, and the mean value of  $W_I$

$$\overline{W_1} = \Delta \omega - \left\{ \frac{1 - 2m + m^2}{1 - m + pT} \right\} \qquad \omega_c \phi$$

Since the capacitor bias is generated by applying the mean phase detector output  $m\omega_c\overline{\phi}$  to the filter

$$\overline{W}_1 \approx \Delta \omega - \left\{ \frac{1-2m+m^2}{1-m+pT} \right\} \omega_c \overline{\phi}$$

Now

$$\frac{d\phi}{dt} + m\omega_c\phi = W_1$$

If it is assumed that the average bias across the filter capacitor will not change significantly during a cycle of the beat-note (i.e., the filter time constant is long compared to the beat-note frequency), we can find this average bias by integrating the loop D.E. over a cycle of the beat-note.

Integrating (12) over the beat note period TBN:

$$\int_{1}^{t+T_{BN}} \frac{d\phi}{dt} dt + \int_{t}^{t+T_{BN}} m\omega_{c}\phi = \int_{t}^{t+T_{BN}} W_{I}$$

$$-2\pi + \int_{1}^{t+T_{BN}} m\omega_{c}\phi = -\overline{W}_{I}T_{BN}$$

The integral in the above equation is the area under a cycle of phase detector output and this integral, divided by the beat note period will give the mean d.c. component of the output:

i.e.,

$$-\overline{m\omega_c\phi} = -\overline{W_I} + \overline{W_{BN}}$$

.: The mean d.c. component

$$\overline{\omega_c \phi} = \frac{1}{m} \left\{ \overline{w}_1 - \overline{w}_{BN} \right\}$$

When the phase detector generates a cycle of the beat note in the time  $T_{BN}$ , it will have operated in two regions—the stable region for a time  $t_s$  and the unstable region for a time  $t_u$  such that:

$$\frac{1}{T_{BN}} = \frac{1}{t_{S} + t_{U}}$$

Solving equation (13) in the region  $\phi_s$ :

$$\int_{0}^{t_{s}} m\omega_{c} dt = \int_{-\phi_{s}/2}^{+\phi_{s}/2} \frac{d\phi}{\frac{W_{l}}{m\omega_{c}} - \phi}$$

$$\therefore m\omega_{c}t_{s} = \begin{bmatrix} \log_{e} \left( \frac{w_{1}}{m\omega_{c}} - \phi \right) \end{bmatrix} - \frac{\phi_{s/2}}{\phi_{s/2}}$$

$$\therefore t_{s} = \frac{1}{m\omega_{c}} \log_{e} \left\{ 1 + \frac{2}{\frac{2W_{1}}{m\omega_{c}\phi_{c}}} - 1 \right\}$$

Similarly during  $\phi_{u}$ :

$$\frac{m\omega_c\phi_s t_u}{\phi u} = \log_e \left\{ 1 + \frac{2}{\frac{2W_1}{m\omega_s\phi_s} - 1} \right\}$$

$$\therefore W_{BN} = \frac{2\pi}{T_{BN}} = \frac{m\omega_c\phi_s}{\log_e \left\{1 + \frac{2}{2W_I} - 1\right\}} \phi_{s+\phi_u} = 2\pi$$

Substituting this expression into E<sub>y</sub> (12) gives

$$\omega_{c}\overline{\phi} = \frac{1}{m} \left\{ \overline{W_{I}} - \frac{m\omega_{c}\phi_{s}}{\log_{e} \left[1 + \left(\frac{2W_{I}}{m\omega_{c}\phi_{s}} - 1\right)\right]} \right\}$$

Now:

$$\overline{W}_{I} = \Delta \omega - \left\{ \frac{1 - 2m + m^{2}}{1 - m + pT} \right\} \quad \overline{\omega}_{C} \phi$$

$$\therefore \omega_{C} \phi = \left[ \frac{1 - m + pT}{1 - 2m + m^{2}} \right] \quad \Delta \omega - \overline{W}_{I}$$

$$= \frac{\Delta \omega}{(1 - m)} - \frac{\overline{W}_{I}}{(1 - m)} - \frac{T}{(1 - m)^{2}} \frac{d}{dt} \quad \overline{W}_{I}$$

using partial fractions and noting T = RC = const.

Substituting equation (14) in the above:

$$\begin{split} \overline{W}_{l} - \frac{m\omega_{c}\phi_{s}}{\log_{e}} & = \frac{m\Delta\omega}{(l-m)} \\ & \left\{ 1 + \left( \frac{\frac{2}{2W_{l}}}{m\omega_{c}\phi_{s}} - 1 \right) \right\} & = \frac{m\Delta\omega}{(l-m)} \\ - \frac{m\overline{W}_{l}}{(l-m)} - \frac{m}{(l-m)^{2}} - T \frac{d}{dt} \overline{W}_{l} \end{split}$$

Putting  $K = \frac{2 \overline{W}_I}{\omega_c \phi_s}$  representing the average frequency difference

and  $K_0 = \frac{2 \Delta \omega}{\omega_c \phi_s}$  representing the initial frequency difference

and multiplying the equation by  $\frac{(1-m)^2}{m \omega_c \phi_s}$

$$(1-m) K - \frac{2(1-m)}{\log_e \left(\frac{K+1}{K-1}\right)} = K_o - mK - \frac{m}{1-m} T \frac{dk}{dt}$$

or

$$\left(\frac{1-m}{mT}\right) dt = \frac{dK}{K_o - K + \frac{2(1-m)}{\log_e \left(\frac{K+1}{K-1}\right)}}$$

If the mean average frequency (K) decreases with time then the initial frequency difference (K<sub>0</sub>) is within the

pull-in range. Putting  $T_F$  for the limit time to pull-in from  $\overline{W}_I = \Delta \omega$  to  $\overline{W}_I = \frac{m\omega_c \phi_s}{2}$

$$\frac{\left(\frac{1-m}{mT}\right)}{\frac{K_o}{m}} \quad T_F = \int_{-\frac{K_o}{m}}^{1} \frac{\frac{dK}{K_o - K + \frac{2(1-m)}{K-1}}}{\log_e\left(\frac{K+1}{K-1}\right)}$$

In the limit, if Tr is real:

$$K_{0} - K + \frac{2(1-m)}{\log_{e} \left(\frac{K+1}{K-1}\right)} > 0$$

$$W = \left\{ \left(\frac{2(1-m)}{K-1}\right) \right\}$$

or

$$K_0 = \left\{ K - \frac{2(1-m)}{\log_e \frac{K+1}{K-1}} \right\}$$

limit

For a maximum,

$$\frac{d}{dk} (K_0) = 0 = 4(1-m) - (K-1)(K+1) \left\{ \log_e \left( \frac{K+1}{K-1} \right) \right\}^2$$

$$\log_e (K+1) - \log_e (K-1) = 2 \left\{ \frac{1}{K} + \frac{1}{3K^3} + \frac{1}{5K^5} + \cdots \right\}$$

$$\therefore 4(1-m) \approx (K+1)(K-1) \cdot 4 \left( \frac{1}{K^2} \right) \quad \text{if } (K) > 1$$

i.e.,

$$K = \frac{1}{\sqrt{m}}$$

$$= \frac{1}{\sqrt{m}} - \frac{2(1-m)}{\log\left(\frac{1}{\sqrt{m}} + 1\right) - \log\left(\frac{1}{\sqrt{m}} - 1\right)}$$

$$= \frac{1}{\sqrt{m}} - \frac{2(1-m)3}{2\sqrt{m}(3+m)} \quad \text{if } m << 1$$

$$= \frac{4\sqrt{m}}{(3+m)}$$

$$\therefore \Delta\omega_{\text{max}} = \frac{\phi_{\text{s}}\omega_{\text{c}}}{2} \frac{4\sqrt{m}}{(3+m)},$$

i.e., Maximum pull-in range

$$\Delta f_{\text{max}} = \frac{2\phi_s f_c \sqrt{m}}{(3+m)}$$