### 4 x 30W QUAD BRIDGE CAR RADIO AMPLIFIER

- HIGH OUTPUT POWER CAPABILITY:

- 4 x 35W/4 $\Omega$  MAX.

- $4 \times 30W/4\Omega$  EIAJ

- $4 \times 22W/4\Omega$  @ 14.4V, 1KHz, 10%

- 4 x 18.5W/4Ω @ 13.2V, 1KHz, 10%

- CLIPPING DETECTOR

- LOW DISTORTION

- LOW OUTPUT NOISE

- ST-BY FUNCTION

- MUTE FUNCTION

- AUTOMUTE AT MIN. SUPPLY VOLTAGE DE-TECTION

- DIAGNOSTICS FACILITY FOR:

- CLIPPING

- OUT TO GND SHORT

- OUT TO V<sub>S</sub> SHORT

- THERMAL SHUTDOWN

- LOW EXTERNAL COMPONENT COUNT:

- INTERNALLY FIXED GAIN (32dB)

- NO EXTERNAL COMPENSATION

- NO BOOTSTRAP CAPACITORS

### **PROTECTIONS:**

OUTPUT SHORT CIRCUIT TO GND, TO V<sub>S</sub>, ACROSS THE LOAD

- VERY INDUCTIVE LOADS

- OVERRATING CHIP TEMPERATURE WITH SOFT THERMAL LIMITER

- LOAD DUMP VOLTAGE

- FORTUITOUS OPEN GND

- REVERSED BATTERY

- ESD PROTECTION

### **DESCRIPTION**

The TDA7383 is a new technology class AB Audio Power Amplifier in Flexiwatt 25 package designed for high end car radio applications.

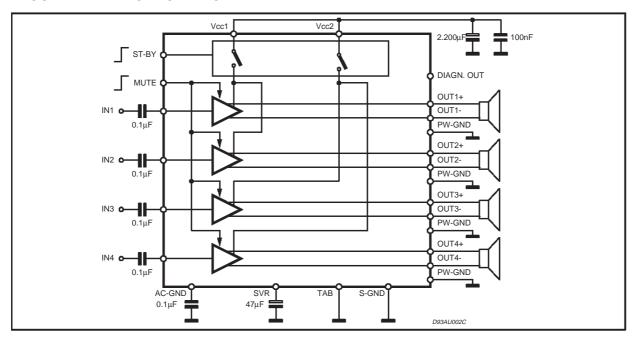

### **BLOCK AND APPLICATION DIAGRAM**

September 1998 1/12

### **DESCRIPTION** (continued)

Thanks to the fully complementary PNP/NPN output configuration the TDA7383 allows a rail to rail output voltage swing with no need of bootstrap capacitors. The extremely reduced components count allows very compact sets.

The on-board clipping detector simplifies gain compression operations. The fault diagnostics makes it possible to detect mistakes during Car-Radio assembly and wiring in the car.

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol               | Parameter                                                                               | Value       | Unit   |  |

|----------------------|-----------------------------------------------------------------------------------------|-------------|--------|--|

| $V_{CC}$             | Operating Supply Voltage                                                                | 18          | V      |  |

| V <sub>CC</sub> (DC) | DC Supply Voltage                                                                       | 28          | V      |  |

| V <sub>CC (pk)</sub> | Peak Supply Voltage (t = 50ms)                                                          | 50          | V      |  |

| lo                   | Output Peak Current: Repetitive (Duty Cycle 10% at f = 10Hz) Non Repetitive (t = 100µs) | 4.5<br>5.5  | A<br>A |  |

| P <sub>tot</sub>     | Power dissipation, (T <sub>case</sub> = 70°C)                                           | 80          | W      |  |

| Tj                   | Junction Temperature                                                                    | 150         | °C     |  |

| T <sub>stg</sub>     | Storage Temperature                                                                     | - 55 to 150 | °C     |  |

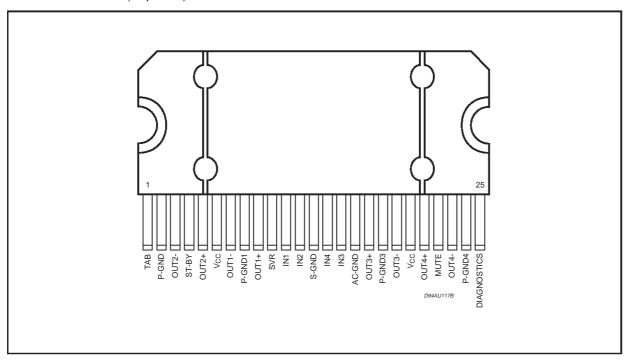

### PIN CONNECTION (Top view)

### **THERMAL DATA**

| Symbol                 | Parameter                                | Value | Unit |

|------------------------|------------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction to Case Max. | 1     | °C/W |

2/12

## **ELECTRICAL CHARACTERISTICS** (V<sub>S</sub> = 14.4V; f = 1KHz; R<sub>L</sub> = $4\Omega$ ; T<sub>amb</sub> = $25^{\circ}$ C; Refer to the Test and application circuit (fig.1), unless otherwise specified.)

| Symbol              | Parameter                                         | Test Condition                                                                                      | Min.           | Тур.           | Max. | Unit        |

|---------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------|----------------|------|-------------|

| I <sub>q1</sub>     | Quiescent Current                                 |                                                                                                     |                | 180            | 300  | mA          |

| Vos                 | Output Offset Voltage                             |                                                                                                     |                |                | 200  | mV          |

| $G_v$               | Voltage Gain                                      |                                                                                                     | 31             | 32             | 33   | dB          |

| Po                  | Output Power                                      | THD = 10%<br>THD = 1%                                                                               | 20<br>16.5     | 22<br>18       |      | W<br>W      |

|                     |                                                   | THD = 10%; V <sub>S</sub> = 14V<br>THD = 5%; V <sub>S</sub> = 14V<br>THD = 1%; V <sub>S</sub> = 14V | 19<br>17<br>16 | 21<br>19<br>17 |      | W<br>W<br>W |

|                     |                                                   | THD = 10%; V <sub>S</sub> = 13.2V<br>THD = 1%; V <sub>S</sub> = 13.2V                               | 17<br>14       | 18.5<br>15     |      | W<br>W      |

| P <sub>o EIAJ</sub> | EIAJ Ouput Power (*)                              | VS = 13.7V                                                                                          | 27.5           | 30             |      | W           |

| P <sub>o max.</sub> | Max. Output Power (*)                             | V <sub>S</sub> = 14.4V                                                                              | 33             | 35             |      | W           |

| THD                 | Distortion                                        | $P_0 = 4W$                                                                                          |                | 0.05           | 0.3  | %           |

| e <sub>No</sub>     | Output Noise                                      | "A" Weighted<br>Bw = 20Hz to 20KHz                                                                  |                | 75<br>100      | 150  | μV<br>μV    |

| SVR                 | Supply Voltage Rejection                          | f = 100Hz                                                                                           | 50             | 65             |      | dB          |

| f <sub>cl</sub>     | Low Cut-Off Frequency                             |                                                                                                     |                | 20             |      | Hz          |

| f <sub>ch</sub>     | High Cut-Off Frequency                            |                                                                                                     | 75             |                |      | KHz         |

| $R_i$               | Input Impedance                                   |                                                                                                     | 70             | 100            |      | ΚΩ          |

| $C_{T}$             | Cross Talk                                        | f = 1KHz                                                                                            | 50             | 70             |      | dB          |

| I <sub>SB</sub>     | St-By Current Consumption                         | St-By = LOW                                                                                         |                |                | 100  | μΑ          |

| $V_{SB out}$        | St-By OUT Threshold Voltage                       | (Amp: ON)                                                                                           | 3.5            |                |      | V           |

| $V_{SBIN}$          | St-By IN Threshold Voltage                        | (Amp: OFF)                                                                                          |                |                | 1.5  | V           |

| $A_M$               | Mute Attenuation                                  | V <sub>O</sub> = 1Vrms                                                                              | 80             | 90             |      | dB          |

| V <sub>M out</sub>  | Mute OUT Threshold Voltage                        | (Amp: Play)                                                                                         | 3.5            |                |      | V           |

| $V_{M in}$          | Mute IN Threshold Voltage                         | (Amp: Mute)                                                                                         |                |                | 1.5  | V           |

| I <sub>m (L)</sub>  | Muting Pin Current                                | V <sub>MUTE</sub> = 1.5V<br>(Source Current)                                                        | 5              | 10             | 16   | μА          |

| I <sub>CDOFF</sub>  | Clipping Detector "OFF" Output<br>Average Current | THD = 1% (**)                                                                                       |                | 100            |      | μΑ          |

| I <sub>CDON</sub>   | Clipping Detector "ON" Output<br>Average Current  | THD = 10% (**)                                                                                      | 100            | 240            | 350  | μΑ          |

<sup>(\*)</sup> Saturated square wave output. (\*\*) Diagnostics output pulled-up to 5V with 10K $\Omega$  series resistor.

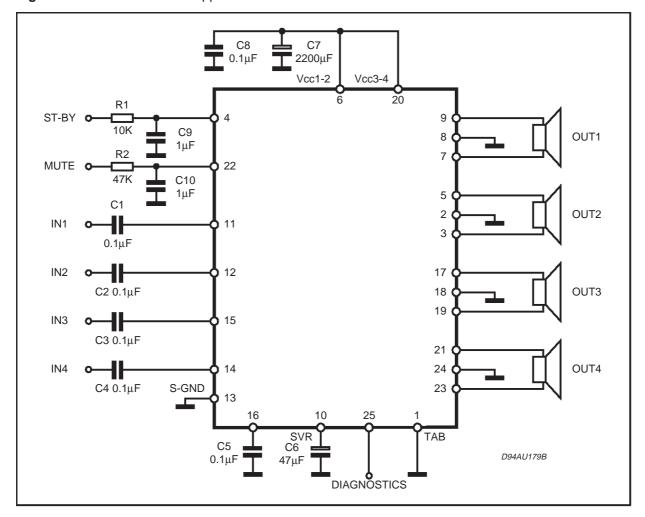

Figure 1: Standard Test and Application Circuit

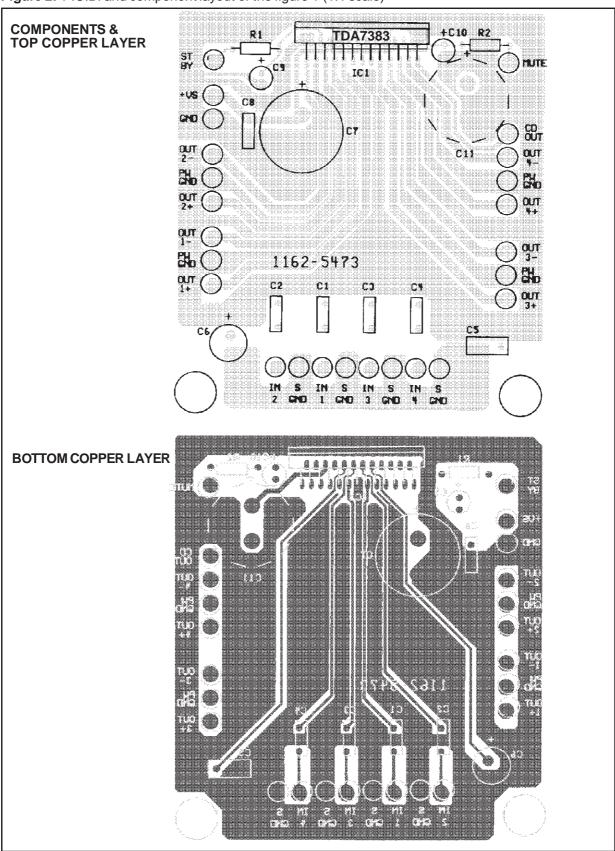

Figure 2: P.C.B. and component layout of the figure 1 (1:1 scale)

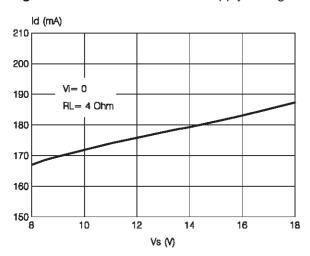

Figure 3: Quiescent Current vs. Supply Voltage

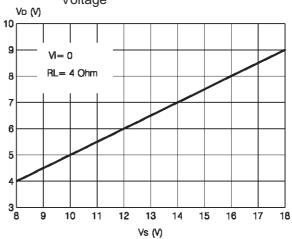

Figure 4: Quiescent Output Voltage vs. Supply Voltage

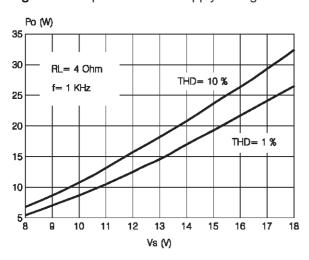

Figure 5: Output Power vs. Supply Voltage

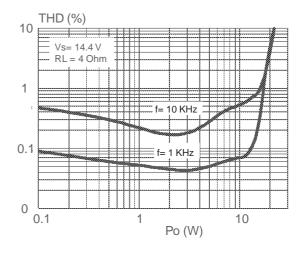

Figure 6: Distortion vs. Output Power

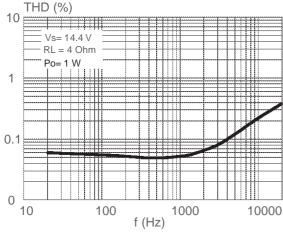

Figure 7: Distortion vs. Frequency.

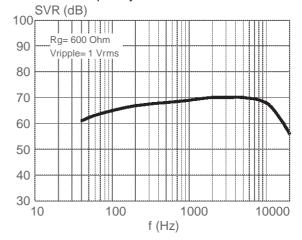

**Figure 8:** Supply Voltage Rejection vs. Frequency

6/12

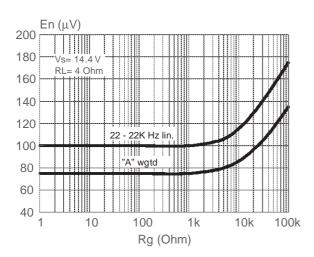

Figure 9: Output Noise vs. Source Resistance

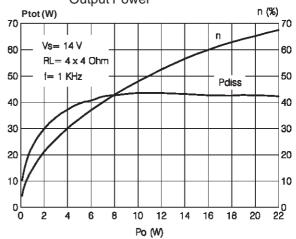

**Figure 10:** Power Dissipation & Efficiency vs. Output Power

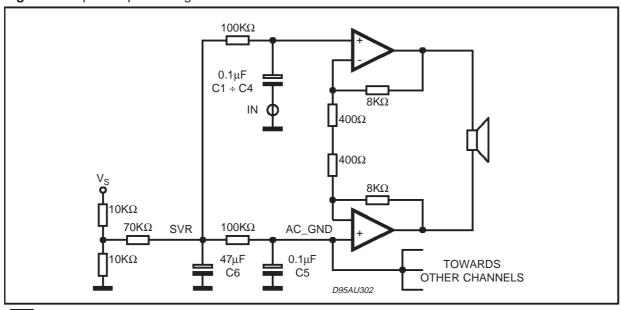

### **APPLICATION HINTS** (ref. to the circuit of fig. 1) BIASING AND SVR

As shown by fig. 11, all the TDA7383's main sections, such as INPUTS, OUTPUTS AND AC-GND (pin 16) are internally biased at half Supply Voltage level (Vs/2), which is derived from the Supply Voltage Rejection (SVR) block. In this way no current flows through the internal feedback network.

The AC-GND is common to all the 4 amplifiers and represents the connection point of all the inverting inputs.

Both individual inputs and AC-GND are connected to Vs/2 (SVR) by means of  $100 \mathrm{K}\Omega$  resistors.

To ensure proper operation and high supply voltage rejection, it is of fundamental importance to provide a good impedance matching between INPUTS and AC-GROUND terminations. This implies that  $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ ,  $C_5$  CAPACITORS HAVE TO CARRY THE SAME NOMINAL VALUE AND THEIR TOLERANCE SHOULD NEVER EXCEED  $\pm 10$  %.

Besides its contribution to the ripple rejection, the SVR capacitor governs the turn ON/OFF time sequence and, consequently, plays an essential role in the pop optimization during ON/OFF transients. To conveniently serve both needs, ITS MINIMUM RECOMMENDED VALUE IS 10µF.

Figure 11: Input/Output Biasing.

7/12

### **INPUT STAGE**

The TDA7383's inputs are ground-compatible and can stand very high input signals ( $\pm$  8Vpk) without any performances degradation.

If the standard value for the input capacitors (0.1  $\mu\text{F})$  is adopted, the low frequency cut-off will amount to 16 Hz.

### STAND-BY AND MUTING

STAND-BY and MUTING facilities are both CMOS-COMPATIBLE. If unused, a straight connection to Vs of their respective pins would be admissible. Conventional low-power transistors can be employed to drive muting and stand-by pins in absence of true CMOS ports or microprocessors.

R-C cells have always to be used in order to smooth down the transitions for preventing any audible transient noises.

Since a DC current of about 10 uA normally flows out of pin 22, the maximum allowable muting-series resistance ( $R_2$ ) is 70K $\Omega$ , which is sufficiently high to permit a muting capacitor reasonably small (about  $1\mu F$ ).

If R<sub>2</sub> is higher than recommended, the involved risk will be that the voltage at pin 22 may rise to above the 1.5 V threshold voltage and the device will consequently fail to turn OFF when the mute line is brought down.

About the stand-by, the time constant to be assigned in order to obtain a virtually pop-free transition has to be slower than 2.5V/ms.

### **DIAGNOSTICS FACILITY**

The TDA7383 is equipped with a diagnostics circuitry able to detect the following events:

- CLIPPING in the output stage

- OVERHEATING (THERMAL SHUT-DOWN proximity)

- OUTPUT MISCONNECTIONS (OUT-GND & OUT-Vs shorts)

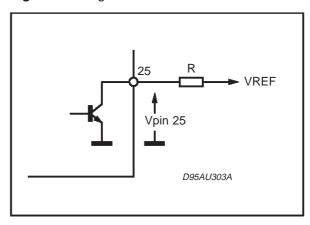

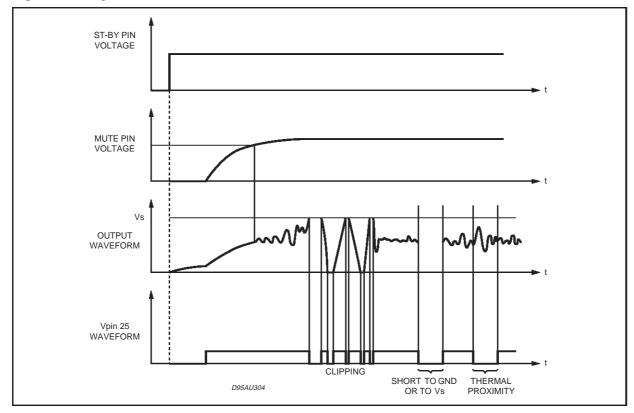

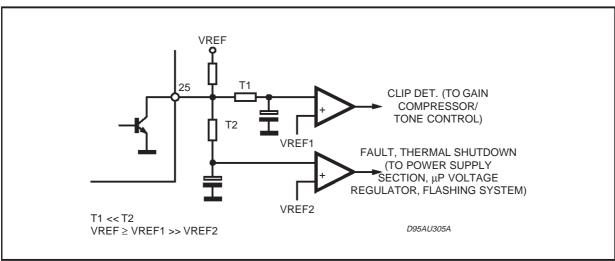

Diagnostics information is available across an open collector output located at pin 25 (fig. 12) through a current sinking whenever at least one of the above events is recognized.

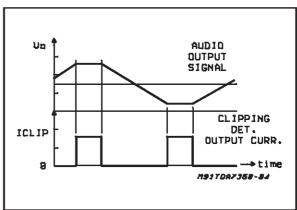

Among them, the **CLIPPING DETECTOR** acts in a way to output a signal as soon as one or more power transistors start being saturated.

As a result, the clipping-related signal at pin 25 takes the form of pulses, which are perfectly syncronized with each single clipping event in the music program and reflect the same duration time (fig. 13). Applications making use of this facility usually operate a filtering/integration of the pulses train through passive R-C networks and realize a volume (or tone bass) stepping down in associa-

tion with microprocessor-driven audioprocessors.

The maximum load that pin 25 can sustain is  $1 \mathrm{K}\Omega$ .

Due to its operating principles, the clipping detector has to be viewed mainly as a power-depend-

Figure 12: Diagnostics circuit.

Figure 13: Clipping Detection Waveforms.

ent feature rather than frequency-dependent. This means that clipping state will be immediately signaled out whenever a fixed power level is reached, regardless of the audio frequency.

In other words, this feature offers the means to counteract the extremely sound-damaging effects of clipping, caused by a sudden increase of odd order harmonics and appearance of serious intermodulation phenomena.

Another possible kind of distortion control could be the setting of a maximum allowable THD limit (e.g. 0.5 %) over the entire audio frequency range. Besides offering no practical advantages, this procedure cannot be much accurate, as the non-clipping distortion is likely to vary over frequency.

In case of **OVERHEATING**, pin 25 will signal out the junction temperature proximity to the thermal shut-down threshold. This will typically start about 2°C before the thermal shut-down threshold is

5

Figure 14: Diagnostics Waveforms.

reached.

As various kind of diagnostics information is available at pin 25 (CLIPPING, SHORTS AND OVER-HEATING), it may be necessary to operate some distinctions on order to treat each event separately. This could be achieved by taking into account the intrinsically different timing of the diagnostics output under each circumstance.

In fact, clipping will produce pulses normally much shorter than those present under faulty conditions. An example of circuit able to distinguish between the two occurrences is shown by fig. 15.

### STABILITY AND LAYOUT CONSIDERATIONS

If properly layouted and hooked to standard carradio speakers, the TDA7383 will be intrinsically stable with no need of external compensations

Figure 15.

5

such as output R-C cells. Due to the high number of channels involved, this translates into a very remarkable components saving if compared to similar devices on the market.

To simplify pc-board layout designs, each amplifier stage has its own power ground externally accessible (pins 2,8,18,24) and one supply voltage pin for each couple of them.

Even more important, this makes it possible to achieve the highest possible degree of separation among the channels, with remarkable benefits in terms of cross-talk and distortion features.

About the layout grounding, it is particularly im-

portant to connect the AC-GND capacitor ( $C_5$ ) to the signal GND, as close as possible to the audio inputs ground: this will guarantee high rejection of any common mode spurious signals.

The SVR capacitor ( $C_6$ ) has also to be connected to the signal GND.

Supply filtering elements  $(C_7, C_8)$  have naturally to be connected to the power-ground and located as close as possible to the Vs pins.

Pin 1, which is mechanically attached to the device's tab, needs to be tied to the cleanest power ground point in the pc-board, which is generally near the supply filtering capacitors.

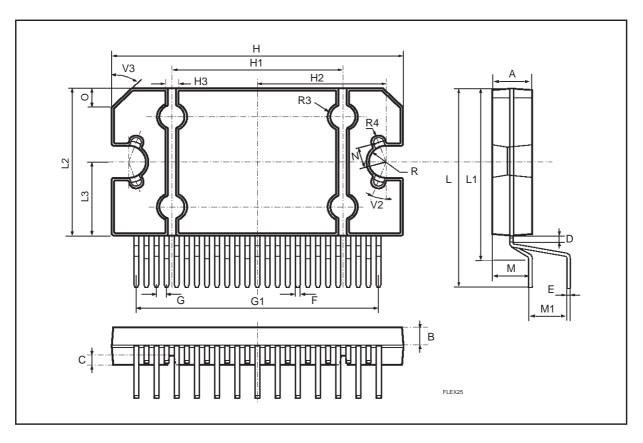

|      | mm    |       |       | inch  |       |       |

|------|-------|-------|-------|-------|-------|-------|

| DIM. | MIN.  | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| Α    | 4.45  |       | 4.65  | 0.175 |       | 0.183 |

| В    | 1.80  | 1.90  | 2.00  | 0.070 | 0.074 | 0.079 |

| С    |       | 1.40  |       |       | 0.055 |       |

| D    | 0.75  | 0.90  | 1.05  | 0.029 | 0.035 | 0.041 |

| Е    | 0.37  | 0.39  | 0.42  | 0.014 | 0.015 | 0.016 |

| F    |       |       | 0.57  |       |       | 0.022 |

| G    | 0.80  | 1.00  | 1.20  | 0.031 | 0.040 | 0.047 |

| G1   | 23.75 | 24.00 | 24.25 | 0.935 | 0.945 | 0.955 |

| Н    | 28.90 | 29.23 | 29.30 | 1.138 | 1.150 | 1.153 |

| H1   |       | 17.00 |       |       | 0.669 |       |

| H2   |       | 12.80 |       |       | 0.503 |       |

| H3   |       | 0.80  |       |       | 0.031 |       |

| L    | 21.57 | 21.97 | 22.37 | 0.849 | 0.865 | 0.880 |

| L1   | 18.57 | 18.97 | 19.37 | 0.731 | 0.786 | 0.762 |

| L2   | 15.50 | 15.70 | 15.90 | 0.610 | 0.618 | 0.626 |

| L3   | 7.70  | 7.85  | 7.95  | 0.303 | 0.309 | 0.313 |

| М    | 3.70  | 4.00  | 4.30  | 0.145 | 0.157 | 0.169 |

| M1   | 3.60  | 4.00  | 4.40  | 0.142 | 0.157 | 0.173 |

| N    |       | 2.20  |       |       | 0.086 |       |

| 0    |       | 2     |       |       | 0.079 |       |

| R    |       | 1.70  |       |       | 0.067 |       |

| R4   |       | 0.50  |       |       | 0.019 |       |

| V2   | 20°   |       |       |       |       |       |

| V3   | 45°   |       |       |       |       |       |

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics © 1998 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com

5