## 2 x 37W DUAL/QUAD POWER AMPLIFIER FOR CAR RADIO

- HIGH OUTPUT POWER CAPABILITY

- $2 \times 43W/4\Omega$  MAX

- $2 \times 37W/4\Omega$  EIAJ

- $2 \times 26W/4\Omega$  @14.4V, 1KHz, 10%

- $4 \times 7W/4\Omega$  @ 14.4V, 1KHz, 10%

- $4 \times 12W/2\Omega$  @14.4V, 1KHz, 10%

- MINIMUM EXTERNAL COMPONENTS COUNT:

- NO BOOTSTRAP CAPACITORS

- NO BOUCHEROT CELLS

- INTERNALLY FIXED GAIN (26dB BTL)

- ST-BY FUNCTION (CMOS COMPATIBLE)

- NO AUDIBLE POP DURING ST-BY OPERA-TIONS

- DIAGNOSTIC FACILITIES

- CLIP DETECTOR

- OUT TO GND SHORT

- OUT TO Vs SHORT

- SOFT SHORT AT TURN-ON

- THERMAL SHUTDOWN PROXIMITY

### **Protections:**

- OUPUT AC/DC SHORT CIRCUIT

- TO GND

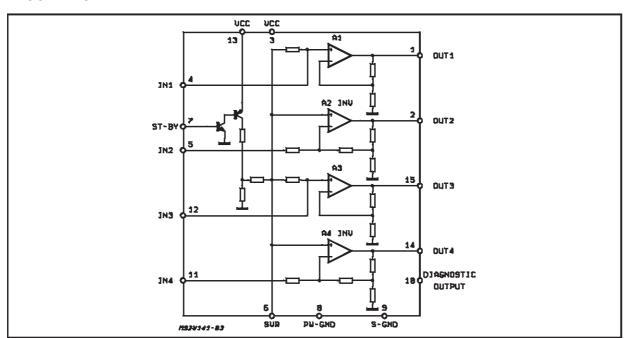

### **BLOCK DIAGRAM**

- TO Vs

- ACROSS THE LOAD

- SOFT SHORT AT TURN-ON

- OVERRATING CHIP TEMPERATURE WITH SOFT THERMAL LIMITER

- LOAD DUMP VOLTAGE SURGE

- VERY INDUCTIVE LOADS

- FORTUITOUS OPEN GND

- REVERSED BATTERY

- ESD

October 1998 1/14

### **DESCRIPTION**

The TDA7375A is a new technology class AB car radio amplifier able to work either in DUAL BRIDGE or QUAD SINGLE ENDED configuration. The exclusive fully complementary structure of the output stage and the internally fixed gain guaran-

tee the highest power performances with extremely reduced component count. The on board clip detector simplifies gain compression operation. The fault diagnostic makes it possible to detect mistakes during car radio set assembly and wiring in the car.

### **GENERAL STRUCTURE**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                    | Value      | Unit |  |

|-----------------------------------|----------------------------------------------|------------|------|--|

| $V_{op}$                          | Operating Supply Voltage                     | 18         | V    |  |

| Vs                                | DC Supply Voltage                            | 28         | V    |  |

| $V_{peak}$                        | Peak Supply Voltage (for t = 50ms)           | 40         | V    |  |

| Ιο                                | Output Peak Current (not repitive t = 100μs) | 4.5        | А    |  |

| Ιο                                | Output Peak Current (repetitive f > 10Hz)    | 3.5        | А    |  |

| P <sub>tot</sub>                  | Power Dissipation T <sub>case</sub> = 85°C   | 36         | W    |  |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and Junction Temperature             | -40 to 150 | °C   |  |

#### THERMAL DATA

| Symbol                 | Description                      | Value | Unit |      |

|------------------------|----------------------------------|-------|------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case | Max   | 1.8  | °C/W |

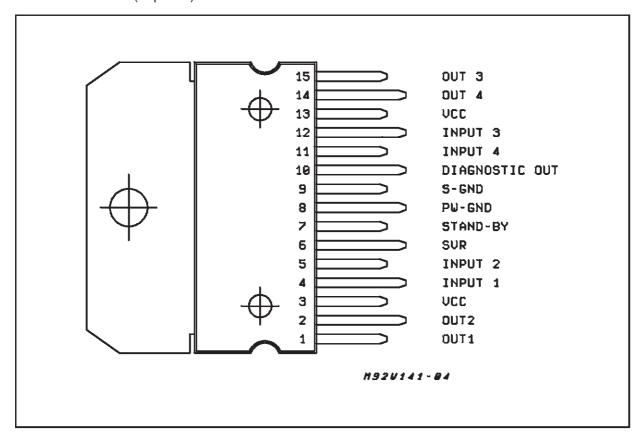

### PIN CONNECTION (Top view)

57

# **ELECTRICAL CHARACTERISTICS** (Refer to the test circuit, $V_S$ = 14.4V; $R_L$ = 4 $\Omega$ ; f = 1KHz; $T_{amb}$ = 25°C, unless otherwise specified

| Symbol                      | Parameter                                   | Test Condition                                                                         | Min.      | Тур.          | Max.     | Unit        |

|-----------------------------|---------------------------------------------|----------------------------------------------------------------------------------------|-----------|---------------|----------|-------------|

| Vs                          | Supply Voltage Range                        |                                                                                        | 8         |               | 18       | V           |

| $I_d$                       | Total Quiescent Drain Current               | R <sub>L</sub> = ∞                                                                     |           |               | 150      | mA          |

| Vos                         | Output Offset Voltage                       |                                                                                        |           |               | 150      | mV          |

| P <sub>O</sub> Output Power |                                             | $THD = 10\%; R_L = 4\Omega$ Bridge Single Ended Single Ended, $R_L = 2\Omega$          | 23<br>6.5 | 26<br>7<br>12 |          | W<br>W<br>W |

| P <sub>O max</sub>          | Max. Output Power (***)                     | VS = 14.4V, Bridge                                                                     | 37        | 43            |          | W           |

| P <sub>O EIAJ</sub>         | EIAJ Output Power (***)                     | V <sub>S</sub> = 13.7V, Bridge                                                         | 33        | 37            |          | W           |

| THD                         | Distortion                                  | $R_L = 4\Omega$<br>Single Ended, $P_O = 0.1$ to 4W<br>Bridge, $P_O = 0.1$ to 10W       |           | 0.02<br>0.03  | 0.3      | %<br>%      |

| CT                          | Cross Talk                                  | f = 1KHz Single Ended<br>f = 10KHz Single Ended                                        |           | 70<br>60      |          | dB<br>dB    |

|                             |                                             | f = 1KHz Bridge<br>f = 10KHz Bridge                                                    | 55        | 60            |          | dB<br>dB    |

| R <sub>IN</sub>             | Input Impedance                             | Single Ended 20<br>Bridge 10                                                           |           | 30<br>15      |          | KΩ<br>KΩ    |

| Gv                          | Voltage Gain                                | Single Ended<br>Bridge                                                                 | 19<br>25  | 20<br>26      | 21<br>27 | dB<br>dB    |

| G <sub>V</sub>              | Voltage Gain Match                          |                                                                                        |           |               | 0.5      | dB          |

| E <sub>IN</sub>             | Input Noise Voltage                         | R <sub>g</sub> = 0; "A" weighted, S.E.<br>Non Inverting Channels<br>Inverting Channels |           | 2<br>5        |          | μV<br>μV    |

|                             |                                             | Bridge<br>Rg = 0; 22Hz to 22KHz                                                        |           | 3.5           |          | μV          |

| SVR                         | Supply Voltage Rejection                    | $R_g = 0; f = 300Hz$                                                                   | 50        |               |          | dB          |

| $A_SB$                      | Stand-by Attenuation                        | P <sub>O</sub> = 1W                                                                    | 80        | 90            |          | dB          |

| $I_{SB}$                    | ST-BY Current Consumption                   | $V_{ST-BY} = 0$ to 1.5V                                                                |           |               | 100      | μΑ          |

| $V_{SB}$                    | ST-BY In Threshold Voltage                  |                                                                                        |           |               | 1.5      | V           |

| $V_{SB}$                    | ST-BY Out Threshold Voltage                 |                                                                                        | 3.5       |               |          | V           |

| I <sub>pin7</sub>           | ST-BY Pin Current                           | Play Mode V <sub>pin7</sub> = 5V                                                       |           |               | 50       | μΑ          |

|                             |                                             | Max Driving Current Under Fault (*)                                                    |           |               | 5        | mA          |

| I <sub>cd off</sub>         | Clipping Detector<br>Output Average Current | d = 1% (**)                                                                            |           | 90            |          | μΑ          |

| I <sub>cd on</sub>          | Clipping Detector<br>Output Average Current | d = 5% (**)                                                                            |           | 160           |          | μΑ          |

| V <sub>sat pin10</sub>      | Voltage Saturation on pin 10                | Sink Current at Pin 10 = 1mA                                                           |           |               | 0.7      | V           |

<sup>(\*)</sup> See built-in S/C protection description (\*\*) Pin 10 Pulled-up to 5V with 10K $\Omega$ ; R<sub>L</sub> = 4 $\Omega$  (\*\*\*) Saturated square wave output.

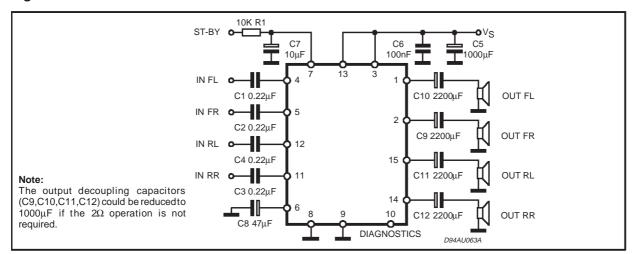

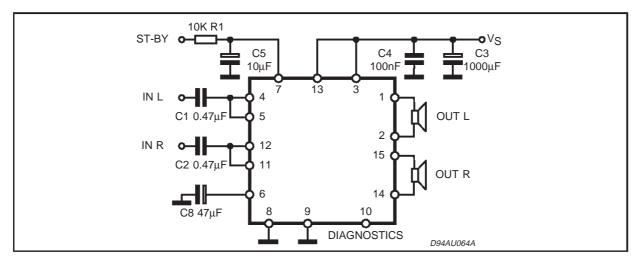

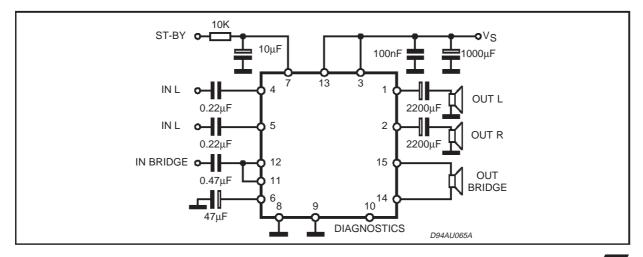

### STANDARD TEST AND APPLICATION CIRCUIT

Figure 1: Quad Stereo

Figure 2: Double Bridge

Figure 3: Stereo/Bridge

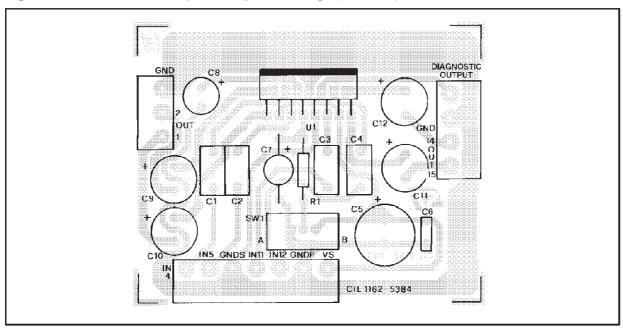

Figure 4: P.C. Board and Component Layout of the fig.1 (1:1 scale).

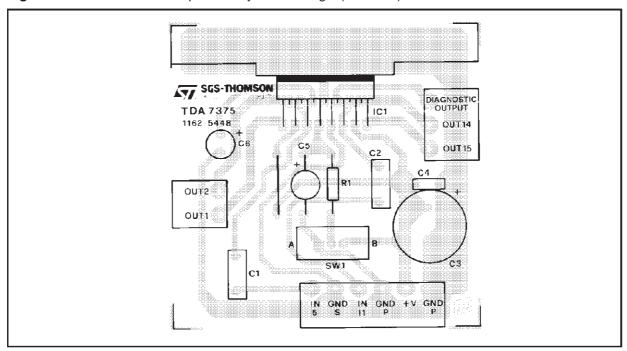

Figure 5: P.C. Board and Component Layout of the fig.2 (1:1 scale).

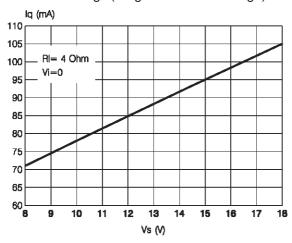

**Figure 6:** Quiescent Drain Current vs. Supply Voltage (Single Ended and Bridge).

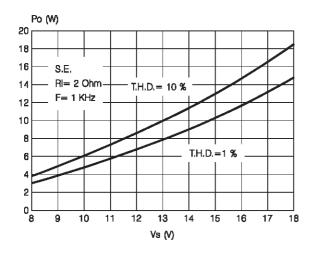

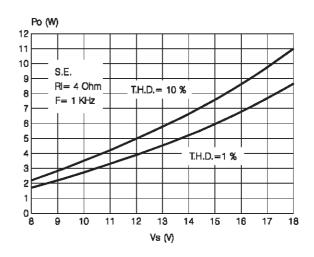

Figure 8: Output Power vs. Supply Voltage

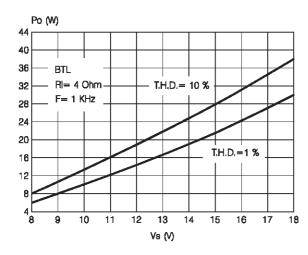

Figure 10: Output Power vs. Supply Voltage

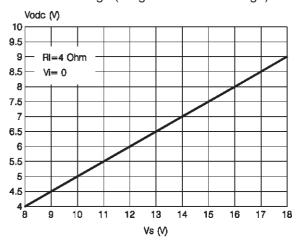

**Figure 7:** Quiescent Output Voltage vs. Supply Voltage (Single Ended and Bridge).

Figure 9: Output Power vs. Supply Voltage

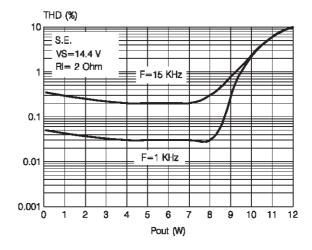

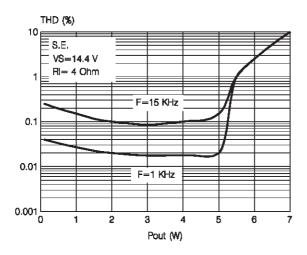

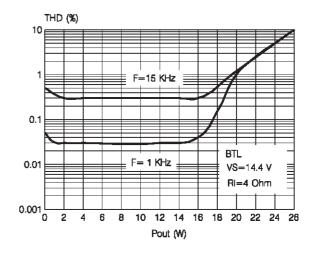

Figure 11: Distortion vs. Output Power

Figure 12: Distortion vs. Output Power

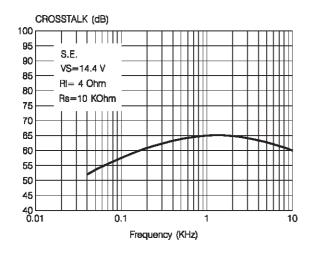

Figure 14: Cross-talk vs. Frequency

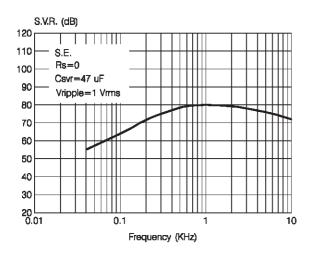

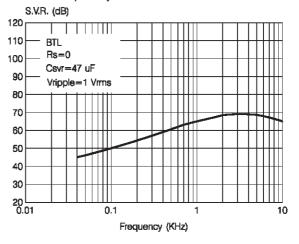

Figure 16: Supply Voltage Rejection vs. Frequency

Figure 13: Distortion vs. Output Power

**Figure 15:** Supply Voltage Rejection vs. Frequency

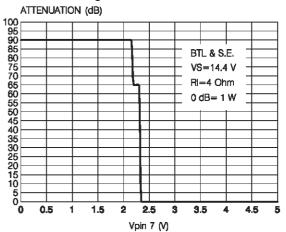

**Figure 17:** Stand-by Attenuation vs. Threshold Voltage

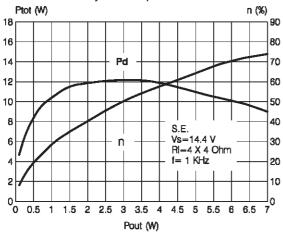

Figure 18: Total Power Dissipation and Efficiency vs. Output Power

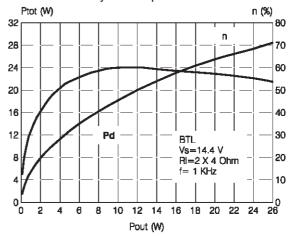

Figure 19: Total Power Dissipation and Efficiency vs. Output Power.

### **High Application Flexibility**

The availability of 4 independent channels makes it possible to accomplish several kinds of applications ranging from 4 speakers stereo (F/R) to 2 speakers bridge solutions.

In case of working in single ended conditions the polarity of the speakers driven by the inverting amplifier must be reversed respect to those driven by non inverting channels.

This is to avoid phase inconveniences causing sound alterations especially during the reproduction of low frequencies.

### **Easy Single Ended to Bridge Transition**

The change from single ended to bridge configurations is made simply by means of a short circuit across the inputs, that is no need of further external components.

# Gain Internally Fixed to 20dB in Single Ended, 26dB in Bridge

Advantages of this design choice are in terms of:

- components and space saving

- output noise, supply voltage rejection and distortion optimization.

## Silent Turn On/Off and Muting/Stand-by Function

The stand-by can be easily activated by means of a CMOS level applied to pin 7 through a RC filter. Under stand-by condition the device is turned off completely (supply current =  $1\mu$ A typ.; output attenuation = 80dB min.).

Every ON/OFF operation is virtually pop free.

Furthemore, at turn-on the device stays in muting condition for a time determined by the value assigned to the SVR capacitor.

While in muting the device outputs becomes insensitive to any kinds of signal that may be present at the input terminals. In other words every transient coming from previous stages produces no unplesant acoustic effect to the speakers.

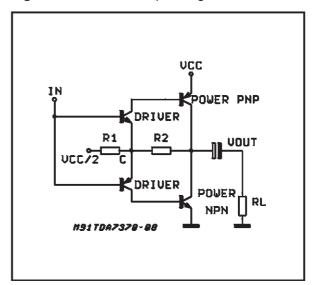

### **OUTPUT STAGE**

The fully complementary output stage was made possible by the development of a new component: the ST exclusive power ICV PNP.

A novel design based upon the connection shown in fig. 20 has then allowed the full exploitation of its possibilities.

The clear advantages this new approach has over classical output stages are as follows:

#### Rail-to-Rail Output Voltage Swing With No

### **Need of Bootstrap Capacitors.**

The output swing is limited only by the VCEsat of the output transistors, which are in the range of  $0.3\Omega$  (R<sub>sat</sub>) each.

Classical solutions adopting composite PNP-NPN for the upper output stage have higher saturation loss on the top side of the waveform. This unbalanced saturation causes a significant power reduction. The only way to recover power consists of the addition of expensive bootstrap capacitors.

# Absolute Stability Without Any External Compensation.

Referring to the circuit of fig. 20 the gain  $V_{Out}/V_{In}$  is greater than unity, approximately 1+ R2/R1. The DC output (Vcc/2) is fixed by an auxiliary amplifier common to all the channels. By controlling the amount of this local feedback it is possible to force the loop gain (A\* $\beta$ ) to less than unity at frequency for which the phase shift is 180°. This means that the output buffer is intrinsically stable and not prone to oscillation.

Most remarkably, the above feature has been achieved in spite of the very low closed loop gain of the amplifier.

In contrast, with the classical PNP-NPN stage, the solution adopted for reducing the gain at high frequencies makes use of external RC networks, namely the Boucherot cells.

Figure 20: The New Output Stage

#### **BUILT-IN SHORT CIRCUIT PROTECTION**

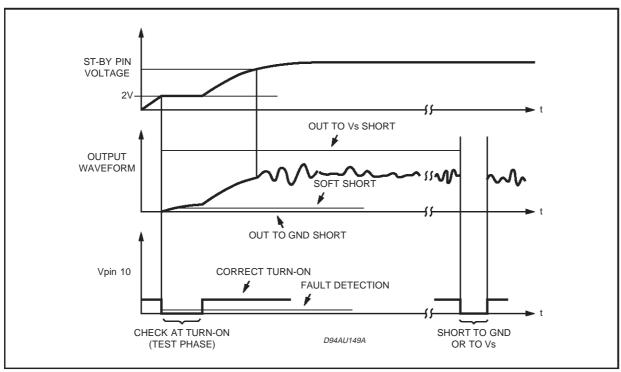

Reliable and safe operation, in presence of all kinds of short circuit involving the outputs is assured by BUILT-IN protectors. Additionally to the AC/DC short circuit to GND, to V<sub>S</sub>, across the speaker, a SOFT SHORT condition is signalled out during the TURN-ON PHASE so assuring cor-

rect operation for the device itself and for the loudspeaker.

This particular kind of protection acts in such a way to avoid the device is turned on (by ST-BY) when a resistive path (less than 16 ohms) is present between the output and GND. As the involved circuitry is normally disabled when a current higher than 5mA is flowing into the ST-BY pin, it is important, in order not to disable it, to have the external current source driving the ST-BY pin limited to 5mA.

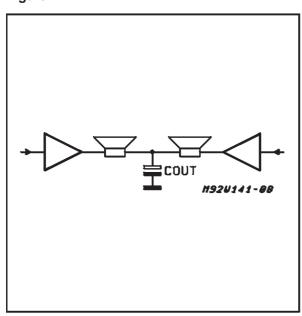

This extrafunction becomes particularly attractive when, in the single ended configuration, one capacitor is shared between two outputs (see fig. 21).

Figure 21.

Supposing that the output capacitor Cout for any reason is shorted, the loudspeaker will not be damaged being this soft short circuit condition revealed.

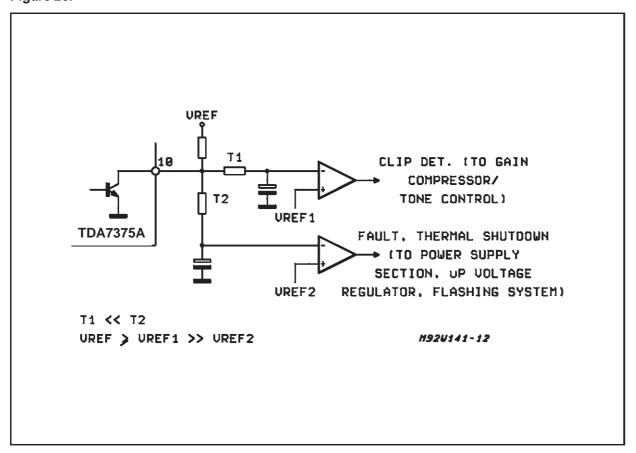

### **Diagnostic Facilities**

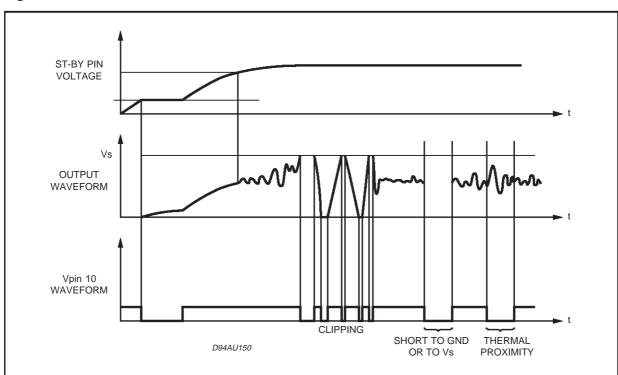

The TDA7375 is equipped with a diagnostic circuitry able to detect the following events:

- Clipping in the output signal

- Thermal shutdown

- Output fault:

- short to GND

- short to Vs

- soft short at turn on

The information is available across an open collector output (pin 10) through a current sinking when the event is detected

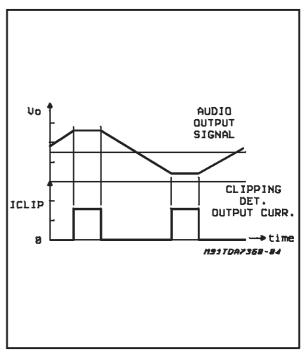

Figure 22: Clipping Detection Waveforms

A current sinking at pin 10 is provided when a certain distortion level is reached at each output. This function allows gain compression facility whenever the amplifier is overdriven.

### **Thermal Shutdown**

In this case the output 10 will signal the proximity of the junction temperature to the shutdown threshold. Typically current sinking at pin 10 will start ~10°C before the shutdown threshold is reached.

### HANDLING OF THE DIAGNOSTIC INFORMA-

Figure 23: Output Fault Waveforms (see fig. 24)

Figure 24: Fault Waveforms

### **TION**

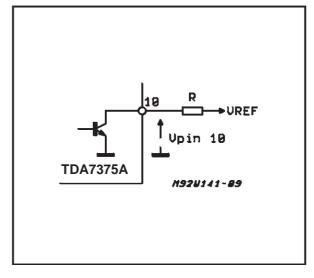

As different kinds of information is available at the same pin (clipping detection, output fault, thermal proximity), this signal must be handled properly in order to discriminate the event.

Figure 25: Waveforms

This could be done taking into account the different timing of the diagnostic output against different events.

Normally the clip detector signalling produces a low level at out 10 that is shorter referred to every

57

kind of fault detection; based on this assumption an interface circuitry to differentiate the information is represented in the following schematic.

Figure 26.

57

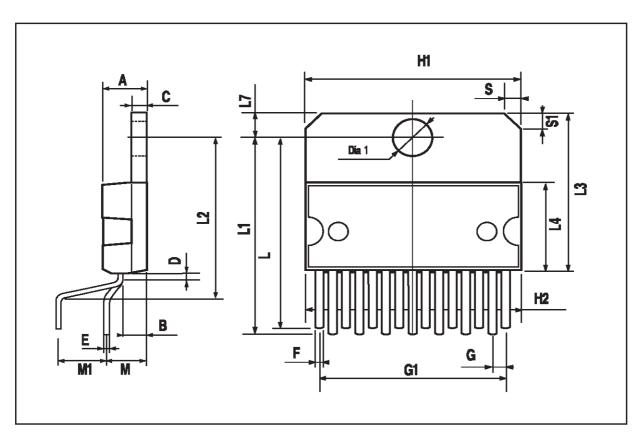

| DIM.   | mm    |       |       | inch  |       |       |  |

|--------|-------|-------|-------|-------|-------|-------|--|

| Dilvi. | MIN.  | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |  |

| Α      |       |       | 5     |       |       | 0.197 |  |

| В      |       |       | 2.65  |       |       | 0.104 |  |

| С      |       |       | 1.6   |       |       | 0.063 |  |

| D      |       | 1     |       |       | 0.039 |       |  |

| Е      | 0.49  |       | 0.55  | 0.019 |       | 0.022 |  |

| F      | 0.66  |       | 0.75  | 0.026 |       | 0.030 |  |

| G      | 1.02  | 1.27  | 1.52  | 0.040 | 0.050 | 0.060 |  |

| G1     | 17.53 | 17.78 | 18.03 | 0.690 | 0.700 | 0.710 |  |

| H1     | 19.6  |       |       | 0.772 |       |       |  |

| H2     |       |       | 20.2  |       |       | 0.795 |  |

| L      | 21.9  | 22.2  | 22.5  | 0.862 | 0.874 | 0.886 |  |

| L1     | 21.7  | 22.1  | 22.5  | 0.854 | 0.870 | 0.886 |  |

| L2     | 17.65 |       | 18.1  | 0.695 |       | 0.713 |  |

| L3     | 17.25 | 17.5  | 17.75 | 0.679 | 0.689 | 0.699 |  |

| L4     | 10.3  | 10.7  | 10.9  | 0.406 | 0.421 | 0.429 |  |

| L7     | 2.65  |       | 2.9   | 0.104 |       | 0.114 |  |

| М      | 4.25  | 4.55  | 4.85  | 0.167 | 0.179 | 0.191 |  |

| M1     | 4.63  | 5.08  | 5.53  | 0.182 | 0.200 | 0.218 |  |

| S      | 1.9   |       | 2.6   | 0.075 |       | 0.102 |  |

| S1     | 1.9   |       | 2.6   | 0.075 |       | 0.102 |  |

| Dia1   | 3.65  |       | 3.85  | 0.144 |       | 0.152 |  |

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics © 1998 STMicroelectronics - Printed in Italy - All Rights Reserved MULTIWATT® is a Registered Trademark of the STMicroelectronics

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com