## STV0196B

## QPSK/BPSK DEMODULATOR AND FEC IC

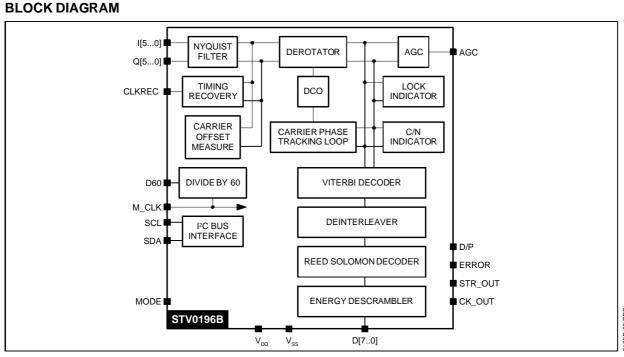

#### FRONT-END INTERFACE

- I AND Q 6 BITS DIGITAL INPUTS AT 2Fs

- QPSK DEMODULATION (Two Modes : A and B)

- INPUT SYMBOL FREQUENCY (Fs) UP TO 30MSYMBOLS/S

- DIGITAL NYQUIST ROOT FILTER:

ROLL-OFF VALUE OF 0.35 IN MODE A

- DIGITAL CARRIER LOOP:

- ON-CHIP DEROTATOR AND TRACKING LOOP

- CARRIER OFFSET INDICATOR

- LOCK DETECTOR

- C/N INDICATOR FOR DISH POSITIONING

- DIGITAL TIMING RECOVERY :

- INTERNAL TIMING ERROR EVALUATION AND FILTER

- OUTPUT CONTROL SIGNAL FOR A 2FS EXTERNAL VCO OR VCXO

- DIGITAL AGC:

- INTERNAL SIGNAL POWER ESTIMATION AND FILTER

- OUTPUT CONTROL SIGNAL FOR AGC (1 BIT PULSE DENSITY MODULATION)

#### FORWARD ERROR CORRECTION

- INNER DECODER:

- VITERBI SOFT DECODER FOR CONVOLU-TIONAL CODES, CONSTRAINT LENGTH M = 7, RATE 1/2

- PUNCTURED CODES 1/2, 2/3, 3/4, 5/6 AND 7/8 IN MODE A

- AUTOMATIC OR MANUAL RATE AND PHASE RECOGNITION

- DEINTERLEAVER:

- WORD SYNCHRO EXTRACTION

- CONVOLUTIVE DEINTERLEAVER

- OUTER DECODER:

- IN MODE A: REED-SOLOMON DECODER FOR 16 PARITY BYTES; CORRECTION OF UP TO 8 BYTE ERRORS

- BLOCK LENGTHS: 204 IN MODE A

- ENERGY DISPERSAL DESCRAMBLER

#### CONTROL

■ I<sup>2</sup>C SERIAL BUS

#### **DESCRIPTION**

Designed for the fast growing direct broadcast satellite (DBS) digital TV receiver market, the SGS-THOMSON STV0196B Digital Satellite Receiver Front-end integrates all the functions needed to demodulate incoming digital satellite TV signals from the tuner: Nyquist filters, QPSK/BPSK demodulator, signal power estimator, automatic gain control, Viterbi decoder, deinterleaver, Reed-Solomon decoder and energy dispersal descrambler. This high level of integration greatly reduces the package count and cost of a set top box. The demodulator blocks are suitable for a wide range of symbol rates while the advanced error correction functions guarantee a low error rate even with small receiver antennas or low power transmitters.

The STV0196B has multistandard capability.

It is fully compliant with the recently defined Digital Video Broadcasting (DVB) standard (already adopted by satellite TV operators in the USA, Europe and Asia) and also compatible with the main consumer digital satellite TV standards in use.

September 1996 1/23

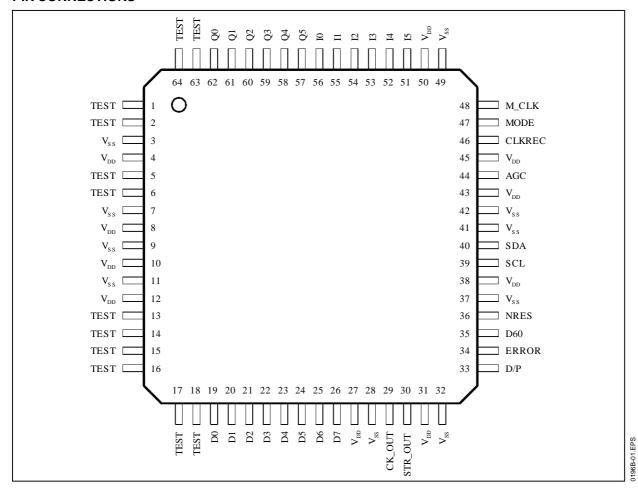

#### **PIN CONNECTIONS**

#### **PIN LIST**

| Pin Number                        | Pin Name | Туре | Pin Description                                                              |

|-----------------------------------|----------|------|------------------------------------------------------------------------------|

| SIGNAL INPUTS                     |          |      |                                                                              |

| 51, 52, 53, 54, 55, 56            | I [50]   | I    | In Phase Component, at twice the symbol frequency (2Fs).                     |

| 57, 58, 59, 60, 61, 62            | Q [50]   | I    | In Quadrature Component, at twice the symbol frequency (2Fs).                |

| 48                                | M_CLK    | ı    | Master Clock Input, 2Fs. Sampling Clock of the External A to D Converters.   |

| FRONT END CONTRO                  | LS       |      |                                                                              |

| 46                                | CLKREC   | 0    | 1 Bit Control Signal for the External CLK VCO. It must be Low-pass Filtered. |

| 44                                | AGC      | 0    | 1 Bit Control Signal for the External AGC. It must be Low-pass Filtered.     |

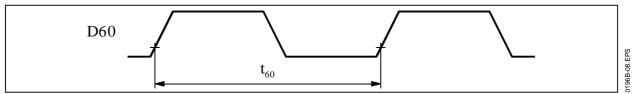

| 35                                | D60      | 0    | M_CLK Divided by 60                                                          |

| SIGNAL OUTPUTS                    |          |      |                                                                              |

| 26, 25, 24, 23,<br>22, 21, 20, 19 | D [70]   | 0    | Output Data                                                                  |

| 29                                | CK_OUT   | 0    | Output Byte Clock                                                            |

| 30                                | STR_OUT  | 0    | Output Synchronization Byte Signal                                           |

| 33                                | D/P      | 0    | Data/Parity Signal                                                           |

| 34                                | ERROR    | 0    | Output Error Signal. Set in Case of uncorrected Block.                       |

| I <sup>2</sup> C MICRO INTERFAC   | E        |      |                                                                              |

| 39                                | SCL      | I    | Serial Clock                                                                 |

| 40                                | SDA      | I/O  | Serial Data Bus                                                              |

| OTHER                             |          |      |                                                                              |

0 = Mode A, 1 = Mode B

**Ground References**

3.3V Supply

Negative Reset

Reserved for Manufacturing Test. It must remain unconnected

# 36

47

1, 2, 5, 6, 13, 14, 15, 16, 17, 18, 63, 64

3, 7, 9, 11, 28, 32,

37, 41, 42, 49 4, 8, 10, 12, 27, 31, 38, 43, 45, 50 MODE

**TEST**

$V_{SS}$

$V_{DD}$

**NRES**

0

1

#### **FUNCTIONAL DESCRIPTION**

## I - I<sup>2</sup>C BUS SPECIFICATION

This is the standard I<sup>2</sup>C protocol.

The device address is "1101000"; the first byte is therefore Hex D0 for a write operation and Hex D1 for a read operation.

#### I.1 - Write Operation

The first byte is the device address plus the direction bit (R/W = 0).

The second byte contains the internal address of the first register to be accessed.

The next byte is written in the internal register.

The following (if any) bytes are written in successive internal registers.

The transfer lasts until stop conditions are encountered.

The STV0196B acknowledges every byte transfer.

## I.2 - Read Operation

The address of the first register to read is programmed in a write operation without data, and terminated by stop condition.

Then another start is followed by the device address and R/W = 1; all successive bytes are now data read at successive positions starting from the initial address.

The STV0196B acknowledges every byte transfer.

#### Example:

Write registers 0 to 3 with AA,BB,CC,DD

| Start | Device Address,<br>Write D0 | ACK | Internal<br>Address | ACK | Data<br>AA | ACK | Data<br>BB | ACK | Data<br>CC | ACK | Stop |  |

|-------|-----------------------------|-----|---------------------|-----|------------|-----|------------|-----|------------|-----|------|--|

|-------|-----------------------------|-----|---------------------|-----|------------|-----|------------|-----|------------|-----|------|--|

#### Read registers 2 and 3

| Start | Device Address,<br>Write D0 |     |                | ACK |    | Register Address 01 |                 |     | Stop |

|-------|-----------------------------|-----|----------------|-----|----|---------------------|-----------------|-----|------|

| Start | Device Address,<br>Read D1  | ACK | Data Rea<br>BB |     | ad | ACK                 | Data Read<br>CC | ACK | Stop |

#### 1.3 - Identification Register

This read only register gives the release number of the circuit in order to ensure software compatibility. The read value is Hex 83 for STV0196B and Hex 81 for STV0196.

Internal Address: Hex 0B

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

|---|---|---|---|---|---|---|---|

Notes: - Unspecified register addresses must not be used.

- All the unused bits in the registers must be programmed to 0.

## I.4 - Register Map

#### REGISTER HEX 00

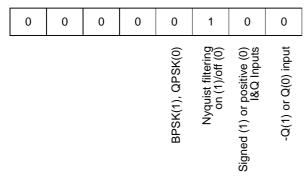

INPUT CONFIGURATION REGISTER (R/W)

Reset Value: Hex 04 0 -Q(1) or Q(0) input

1 Signed (1) or positive (0) I & Q inputs

2 Nyquist filtering on (1) / off (0)

3 BPSK (1), QPSK(0)

4 To be set to 0.

5 To be set to 0.

6 To be set to 0.

7 To be set to 0.

#### REGISTERS HEX 01 TO HEX 05

VITERBI, PUNCTURE RATE THRESHOLDS (R/W)

Reset Value: Hex 20

|            |   |     |     |     |     |     |     |     | rate             |

|------------|---|-----|-----|-----|-----|-----|-----|-----|------------------|

| Hex01 VTH0 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | 1/2              |

| Hex02 VTH1 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | 2/3              |

| Hex03 VTH2 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | 3/4              |

| Hex04 VTH3 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | 5/6              |

| Hex05 VTH4 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | 7/8<br>or<br>6/7 |

#### **REGISTER HEX 06**

VSEARCH (VITERBI) (R/W)

Reset Value: Hex 19

| 0<br><u>1</u> | H[10]  | Sync counter hysteresis value                                        |

|---------------|--------|----------------------------------------------------------------------|

| 2             | T[10]  | Sync search time out                                                 |

| 4<br>5        | SN[10] | VITERBI error rate averaging period. C/N indicator averaging period. |

| 6             | F      | VITERBI operating status freeze (1)                                  |

(0) automatic, (1) manual

#### REGISTER HEX 07

A/M

VERROR REGISTER (Read only)

#### REGISTER HEX 08

VSTATUS REGISTER (Read only)

O 1 PR[2..0] Current puncture rate identification 2

3 LK (1) synchro found, (0) searching puncture rate 4 PRF (1) puncture rate found, (0) searching puncture rate

5 unused set to (0) 6 unused set to (0)

7 CF (1) carrier found, (0) searching carrier

#### REGISTER HEX 09

PUNCTURE RATE ENABLE (R/W)

Reset Value: Hex 10 (mode A)

0 E0 (1) Puncture 1/2 enabled, (0) disabled 1 E1 (1) Puncture 2/3 enabled, (0) disabled 2 E2 (1) Puncture 3/4 enabled, (0) disabled 3 E3 (1) Puncture 5/6 enabled, (0) disabled 4 E4 (1) Puncture 7/8 (mode A), 6/7 (mode B) (0) disabled

5 6 unused

7

#### REGISTER HEX 0A

RS REGISTER (R/W)

Reset Value: Hex B8

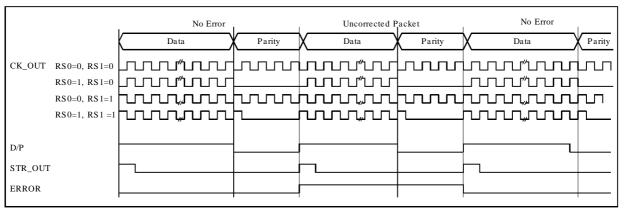

0 RS0 (1) output clock stopped during parity, (0) continuous

1 RS1 Output clock polarity

2 RS2 (1) all synchro words are Hex47, (0) synchro inversion disabled

3 RS3 Write error bit

4 RS4 Descrambler on (1), off (0)

5 RS5 Reed-Solomon on (1), off (0)

6 RS6 Normal operation (0), Reed-Solomon correction bytes to output (1)

7 RS7 De-interleaver on (1), off (0)

## I.4 - Register Map (continued)

REGISTER HEX 0B

IDENTIFICATION REGISTER (Read only)

Reset Value: Hex83 for STV0196B,

Hex 81 for STV0196

#### REGISTER HEX 0C

TIMING LOOP: TIME CONSTANT (R/W)

Reset Value: Hex 45

0 1 beta\_tmg coefficient 2 3 4 5 alpha\_tmg coefficient 6

Istr external VCO/VCXO slope polarity (0)

positive, (1) negative

#### REGISTER HEX 0D

TIMING FREQUENCY REGISTER (R/W) Signed value ranging from 80 to 7F.

#### REGISTER HEX 0E

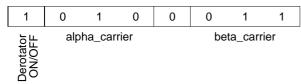

CARRIER LOOP REGISTER (R/W)

Reset Value: Hex A3

0

1 beta\_carrier coefficient

2

3 unused

4

5 alpha\_carrier coefficient

6

7 Deratator on (1), off (0)

## REGISTER HEX OF

DEROTATOR FREQUENCY REGISTER (R/W)

Signed value ranging from 80 to 7F.

#### **REGISTER HEX 10**

CARRIER OFFSET EVALUATOR (Read only)

Signed value ranging from 80 to 7F.

#### **REGISTER HEX 11**

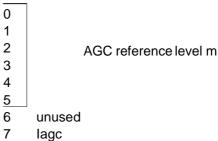

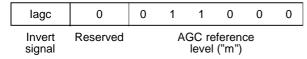

AGC CONTROL REGISTER (R/W)

Reset Value: 18 Hex.

#### **REGISTER HEX 12**

AGC INTEGRATOR (R/W)

Signed value ranging from 80 to 7F.

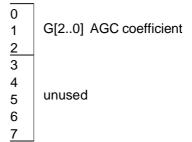

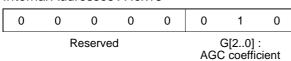

# REGISTER HEX 13 AGC COEFFICIENT

### **REGISTER HEX 14**

C/N INDICATOR (Read only)

Value ranging from 00 to FF.

#### **II - ADC INTERFACE**

#### II.1 - M\_CLK Master Clock Input

This is the highest frequency clock of the chip, at twice the symbol frequency; all other clocks are derived from it.

This clock should be output from an external VCO or VCXO, controlled by CLKREC output.

M\_CLK divided by 60 is available to the system (output D60).

## II.2 - I and Q Signal Inputs

Those signals are coded on 6 bits, either in 2's complement or as positive values: the choice is programmable via the Input Configuration register.

The  $\pi/2$  ambiguity inherent in QPSK is solved in the Error Correction part.

A programmable bit in a mode register allows to multiply by -1 the data on Q input, in order to accommodate QPSK modulation with another convention of rotation sense; (this is equivalent to a permutation of I and Q inputs, or a spectral symmetry).

#### **III - NYQUIST ROOT FILTER**

The I and Q components are filtered by a digital Nyquist root filter with the following features:

- Input: separate I and Q streams, two samples per symbol.

- Excess bandwidth: 0.35 in Mode A.

- The filters may be bypassed; in this case, the input flow is connected to the carrier and clock recovery section.

#### **Input Configuration Register**

(the written value of each bit is the reset value)

Internal Address: Hex00

#### **IV - TIMING RECOVERY**

The timing loop comprises an external VCO or VCXO, running at twice the symbol frequency, controlled by the output CLKREC; this signal is a pulse density modulated output, at the symbol frequency, and represents the filtered timing error.

The loop is parametrised by two coefficients: alpha\_tmg and beta\_tmg; the 12 bit filter output is converted into a pulse density modulation signal which should be filtered by an analog low pass filter before commanding the VCO.

#### IV.1 - Timing Loop Registers

Time Constant Register

Internal Address: Hex0C

Reset Value: Hex45

| Istr   | 1      | 0      | 0       | 0 | 1      | 0         | 1  |

|--------|--------|--------|---------|---|--------|-----------|----|

| Invert | alpha_ | _tmg ( | 1 to 6) | b | eta_tm | g (0 to 9 | 9) |

The bit "Istr" allows to change the polarity of the output signal, in order to accommodate both possibilities of external VCO:

| Istr | Loop Control                                               |

|------|------------------------------------------------------------|

| 0    | VCO frequency raises when output average voltage raises    |

| 1    | VCO frequency decreases when output average voltage raises |

Timing Frequency Register

Internal Address: Hex0D

| Signed number |  |  |  |  |  |  |  |  |  |  |

|---------------|--|--|--|--|--|--|--|--|--|--|

|               |  |  |  |  |  |  |  |  |  |  |

The value of this register, when the system is locked, is an image of the frequency offset; it should be as close as possible to 0 in order to have a symmetric capture range; reading it allows optimal trimming of the timing VCO range.

## IV.2 - Loop Equations

The external VCO is controlled by the output CLKREC followed by a low pass filter.

The full analog swing of the output originates a relative frequency shift of  $2\Delta f$ , depending on the characteristics of the external VCO (typically a fraction of percent).

The frequency range is therefore  $f = f_0$  ( $1 \pm \Delta f$ ). Neglecting the analog low pass filter on the pulse modulated output, this loop may be considered as a second order loop.

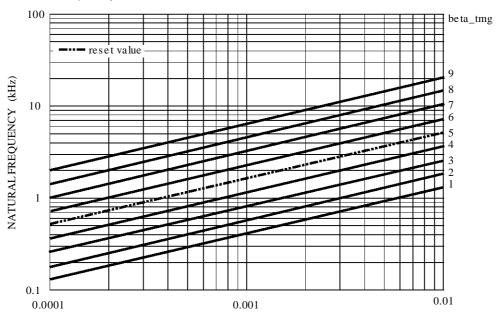

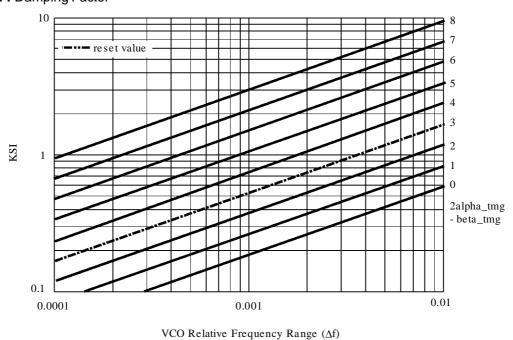

The natural frequency and the damping factor may be calculated by the following formulas:

$$f_n \,=\, \frac{\omega_n}{2\pi} \,=\, \frac{F_s}{2\pi} \,\sqrt{\,\beta\,\,K_0\,\,K_d}$$

where  $\beta$  is programmed by the timing register  $\beta = 2^{\text{beta\_tmg}}.$

> :  $K_0 = \frac{\Delta f}{2^{26}}$ . K<sub>0</sub> is the constant of the VCO

$K_d$  is the phase detector; its value depends on :  $K_d = 0.977 \text{m}^2$  (in Mode A), the roll-off value and on the power of the signal. or  $K_d = 0.564 \text{m}^2$  (in Mode B).

where m is the programmed reference level (see AGC part), reset value : m = 24

$F_s$  is the symbol frequency,  $\Delta f$  is the half range of the VCO

$$\begin{array}{ll} Therefore \ \ f_n = 19.2 \ 10^{-6} \cdot m \cdot F_s \cdot \sqrt{\Delta f \ 2^{beta\_tmg}} \ (Mode \ A) \\ or \qquad \qquad f_n = 14.6 \ 10^{-6} \cdot m \cdot F_s \cdot \sqrt{\Delta f \ 2^{beta\_tmg}} \ (Mode \ B) \end{array}$$

$$\begin{split} &\text{The damping factor is}: \xi = \frac{\alpha}{2} \, \sqrt{\frac{K_0 K_d}{\beta}} \text{ with } \alpha = 2^{\, \text{alpha\_tmg} \, + \, 12} \\ &\text{or } \xi = \frac{0.247 \cdot m \cdot \sqrt{\Delta f} \cdot 2^{\, \text{alpha\_tmg}}}{\sqrt{2^{\, \text{beta\_tmg}}}} \text{ (Mode A) } \text{ or } \xi = \frac{0.188 \cdot m \cdot \sqrt{\Delta f} \cdot 2^{\, \text{alpha\_tmg}}}{\sqrt{2^{\, \text{beta\_tmg}}}} \text{ (Mode B)}. \end{split}$$

beta\_tmg can only take value from 0 to 9; if beta\_tmg = 0, the loop becomes a first order one. alpha\_tmg can take any value from 1 to 6; if both alpha\_tmg and beta\_tmg are null, the loop is open; the duty cycle of the CLKREC output is controlled by writting the timing frequency register.

The next curve shows the natural frequency for a symbol frequency of 20Mbd, in Mode A, with nominal reference level m = 24 as a function of the VCO relative frequency half range  $\Delta f$ , for different values of the register value beta\_tmg.

The following chart gives the value of the damping factor as a function of the VCO relative range, for different combinations of alpha\_tmg and beta\_tmg, noticing that the damping factor only depends on the value of or (2 . alpha\_tmg - beta\_tmg).

Figure 1: Natural Frequency for Fs = 20MBauds

VCO Relative Frequency Range (Δf)

Figure 2: Damping Factor

Example:

the VCO is trimmed from 39.9MHz to 40.1MHz when the VCO control output CLKREC goes from duty cycle 0 to 100%. The peak-to-peak relative range is therefore 0.5% and  $\Delta f = 0.0025$ ; the reset values of the parameters (alpha\_tmg = 4, beta\_tmg = 5) leads to a natural frequency of 2.6kHz, with a damping factor of 0.84.

### V - CARRIER RECOVERY; DEROTATOR

The input of the circuit is a pair of demodulated signals; however, there may subsist some phase error not corrected by the front end loop.

Furthermore, the demodulation may be done at constant frequency; the tuner is trimmed in order to make the useful signal bandwidth centered on this demodulation frequency; in that case, a carrier offset frequencymay subsist; it is fixed by the mean of the on-chip derotator which acts as a fine tuning carrier loop.

The derotator frequency range is limited to an interval corresponding to  $\pm F_s/16$ .

#### V.1 - Loop Parameters

Like the timing loop, the carrier loop is a second order system where two parameters  $\alpha$  and  $\beta$  may be programmed respectively with alpha\_car and beta\_car.

## **Carrier Loop Parameter Registers**

Internal Address: Hex0E

#### **Derotator Frequency Register**

Internal Address: Hex0F

| Signed number |  |  |  |  |  |  |  |  |  |  |

|---------------|--|--|--|--|--|--|--|--|--|--|

|               |  |  |  |  |  |  |  |  |  |  |

This 8 bit R/W register may be written at any time to force the central frequency of the derotator to start the carrier research, or read, when the loop is locked,in order to know the current carrier offset (one LSB correspond to  $F_s/2048$ ).

#### V.2 - Loop Equations

The natural pulsation is:

$$\omega_n = 10^{-3} \cdot f_s \cdot \sqrt{m \cdot 2^{beta\_car}}$$

and the damping factor is:

$$\xi = 0.128 \cdot 2^{alpha\_car} \cdot \sqrt{\frac{m}{2^{beta\_car}}}.$$

where m is the reference value (see AGC registers).

The next table gives for the nominal amplitude m = 24 the natural period (in symbols), and the damping factor for the possible values of alpha\_car.

As an example, the corresponding natural frequency is given assuming a symbol frequency of 20MBauds.

The shaded area correspond to the reset values.

| beta_car<br>(reg. value)         | 0  | 1              | 2     | 3    | 4    | 5    | 6    | 7    |  |  |

|----------------------------------|----|----------------|-------|------|------|------|------|------|--|--|

| $T_n = 2\pi/\omega_n$ (symb per) | NA | 907            | 642   | 454  | 321  | 227  | 160  | 113  |  |  |

| $f_n$ (kHz) for $F = 20$ Mbd     | -  | 22             | 31    | 44   | 62   | 88   | 125  | 177  |  |  |

| alpha_car<br>(reg. value)        |    | Damping Factor |       |      |      |      |      |      |  |  |

| 0                                | NA | NA             | NA    | NA   | NA   | NA   | NA   | NA   |  |  |

| 1                                | NA | 0.89           | 0.63  | 0.44 | 0.31 | 0.22 | 0.16 | 0.11 |  |  |

| 2                                | NA | 1.77           | 1.25  | 0.89 | 0.63 | 0.44 | 0.31 | 0.22 |  |  |

| 3                                | NA | 3.54           | 2.51  | 1.77 | 1.25 | 0.89 | 0.63 | 0.44 |  |  |

| 4                                | NA | 7.09           | 5.01  | 3.54 | 2.51 | 1.77 | 1.25 | 0.89 |  |  |

| 5                                | NA | 14.18          | 10.03 | 7.09 | 5.01 | 3.54 | 2.51 | 1.77 |  |  |

#### VI - CARRIER OFFSET EVALUATOR

An 8 bit register may be read at any time; it gives a signed value proportionnal to the carrier frequency offset according to the expression:

$$\Delta f = 1.8 \cdot 10^{-6} \cdot m^2 \cdot N \cdot F_s \text{ (in mode A)}$$

where  $F_s$  is the symbol frequency, m the symbol module (AGC reference), N the read value.

The maximum value for N is reached in nominal conditions for a carrier offset of 16% of  $F_s$ ; if greater, N remains saturated, giving a reliable sign indication over more than  $\pm 50\%$   $F_s$  range.

#### **Carrier Offset Register**

Internal Address: Hex10

| Signed number |  |  |  |  |  |  |  |  |  |  |

|---------------|--|--|--|--|--|--|--|--|--|--|

|               |  |  |  |  |  |  |  |  |  |  |

#### VI.1 - Lock Indicator

This 1 bit Carrier Found flag may be read (see Viterbi Status register) at any time; it indicates that a QPSK signal is found, and that the carrier loop is closed; This flag allows to detect false lock that can happen if the loop bandwidth is small regarding the frequency offset.

#### VII - CARRIER TO NOISE INDICATOR

Internal Address: Hex14. Read only register.

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|----|----|----|----|----|----|----|----|

This register can be used to estimate the carrier to noise level (Eb/No) in a range from 4 to 16dB. The register value depends on both the AGC reference level "m" (see paragraph VIII) and the control bits "SN[1..0]" (see paragraph IX). For more details about how to use this register, please refer to the Annexe 1.

# FUNCTIONAL DESCRIPTION (continued) VIII - AGC CONTROL

amplifier before the A to D converter.

### The modulus of the input is compared to a programmable threshold; the difference is scaled by the AGC coefficient, then integrated; the result is converted into a pulse density modulation signal to drive the AGC output; it may be filtered by a simple analogue filter to control the gain command of any

The 8 integrator MSB's may be read or written at any time by the micro; when written, the LSB's are reset. The integrator value is the level of the AGC output, after low pass filtering; it gives an image of the input signal power, whatever this signal is, and can be used to point the antenna.

The coefficient may be reset by programmation; in that case, the AGC reduces to a programmable voltage synthesiser.

The AGC reference level "m" value impacts the value of the following functions:

- carrier to noise indicator (see paragraph VII)

- the carrier loop (see paragraph V.2)

- the timing loop (paragraph IV.2)

- carrier offset evaluator (paragraph VI)

## **Control Registers**

Internal Addresses: Hex11

Internal Addresses: Hex12

Internal Addresses: Hex13

The 8 bit signed value in the integrator is the image of the AGC output; reading this value gives an image of the RF signal power.

A constant error on the modulus leads to a ramp at the output of the integrator with value :

AGC Int =

$$2^{AGC\_Coeff-16}$$

. error

As a consequence, for the reset conditions, a constant signal of null value (error = 24) should cause the output AGC duty cycle to go from 100% to 0% in  $2^{22}$  symbol periods, or 8.7ms at 20MBauds.

If lagc is set, the sign of the integrator is inverted.

#### IX-VITERBI DECODER AND SYNCHRONIZATION

The convolutives codes are generated by the polynoms  $Gx = 171_{oct}$  and  $Gy = 133_{oct}$ .

The Viterbi decoder computes for each symbol the metrics of the four possible paths, proportional to the square of the Euclidian distance between the received I and Q and the theoretical symbol value. The puncture rate and phase are estimated on the error rate basis.

Five rates are allowed and may be enabled/disabled through register programming :

1/2, 2/3, 3/4,5/6, 7/8.

In Mode B, 7/8 is replaced by 6/7.

For each enabled rate, the current error rate is compared to a programmable threshold; if it is greater, anotherphase (or another rate) is tried until the good rate is obtained.

A programmable hysteresis is added to avoid to loose the phase during short term perturbation.

The rate may also be imposed by the external software, and the phase is incremented only on micro request; the error rate may be read at any time in order to use other algorithm than implemented.

The decoder is accessed via a set of 9 registers:

### Threshold Registers (VTH0 to VTH4)

Internal Address: Hex1 (VTH0) to 5 (VTH4)

Reset Value: Hex20

|      |   |     |     |     |     |     |     |     | Threshold<br>Value |

|------|---|-----|-----|-----|-----|-----|-----|-----|--------------------|

| VTH0 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | rate 1/2           |

| VTH1 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | rate 2/3           |

| VTH2 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | rate 3/4           |

| VTH3 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | rate 5/6           |

| VTH4 | 0 | Th6 | Th5 | Th4 | Th3 | Th2 | Th1 | Th0 | rate 7/8<br>or 6/7 |

For each register, bits 6 to 0 represent an error rate threshold: the average number of errors happening during 256 bit periods; the maximum programmable value is 127/256 (higher error rates are of no practical use).

#### **Puncture Rate Enable register**

Internal Address : Hex09 Reset Value : Hex10 (Mode A)

|   | 14.40 |   | . 0 ( |    |    |    |    |

|---|-------|---|-------|----|----|----|----|

| 0 | 0     | 0 | E4    | E3 | E2 | E1 | E0 |

E4: enable Punctured Rate 7/8 (Mode A) or 6/7 (Mode B)

E3: enable Punctured Rate 5/6 E2: enable Punctured Rate 3/4 E1: enable Punctured Rate 2/3

E0: enable Basic Rate 1/2

#### IX - VITERBI DECODER AND SYNCHRONIZATION (continued)

#### Other Registers VSEARCH

Internal Address: Hex06

| A/M | F | SN [10] | TO [10] | H [10] |

|-----|---|---------|---------|--------|

|-----|---|---------|---------|--------|

A/M : Automatic/manual

F : Freeze

SN [1..0]: Averaging period. It gives the number of bits required to calculate the rate error:

| SN [10] | Number of bits |

|---------|----------------|

| 00      | 1.024          |

| 01      | 4.096          |

| 10      | 16.384         |

| 11      | 65.536         |

Reset Value: SN=01 (4096 bits)

The SN[1..0] bits also inpacts the C/N indicator (see paragraph VII).

TO [1..0]: Time out value. It programs the maximum duration of the synchro word research in automatic mode; if no sync is found within this duration, the phase is incremented.

| TO [10] | Time out<br>(in 1024 bit periods) |

|---------|-----------------------------------|

| 00      | 16                                |

| 01      | 32                                |

| 10      | 64                                |

| 11      | 128                               |

Reset Value: TO=10 (64K bit periods).

H [1..0] : Hysteresis value. It programs the maximum value of the Sync counter. The unit is the block duration (204 bytes in Mode A).

| <u> </u> | ,                                          |

|----------|--------------------------------------------|

| H [10]   | Sync Counter max value (in blocks periods) |

| 00       | forbidden value                            |

| 01       | 32                                         |

| 10       | 64                                         |

| 11       | 128                                        |

Reset Value: H=01 (32 blocks).

In Mode A, the sync word is 47hex and it is complemented to B8hex for every 8th block.

An Up/Down Sync counter counts whenever a sync word is recognized with the good timing, and counts down for each missing sync word; this counter is bounded by a programmable maximum value; when this value is reached, the LK bit ("locked") is set in VSTATUS register; when the event counter counts down until 0, this flag is reset. VSEARCH bit 7 (A/M) and bit 6 (F) programs the automatic/manual (or computer aided) search mode:

if A/M =0 and F=0 : automatic mode; successive enabled punctured rates are tried with all possible phases, until the system is locked and the block synchro found; this is the default (reset) mode.

- if A/M=0 and F=1, the current puncture rate is frozen, if no sync is found, the phase is incremented, but not the rate number; this mode allows to shorten the recovery time in case of noisy conditions: the puncture rate is not supposed to change in a given channel.

In a typical computer aided implementation, the research begins in automatic mode; the micro reads the error rate or the PRF flag in order to detect the capture of a signal; then it switches F to 1, until a new channel is requested by the remote control.

- if AM=1: manual mode; in this case, only one puncture rate should be validated, the system is forced to this rate, on the current phase, ignoring the time-out register and the error rate; in this mode, each 0 to 1 transition of the bit F leads to a phase incrementation, allowing full control of the operation by an external micro by choosing the lowest error rate:

Reset Value: A/M=0, and F=0; automaticsearch mode

#### **VERROR** (Read only register)

Internal Address: Hex07

| <br>       |  |

|------------|--|

| ERROR RATE |  |

PR [2..0]

At any time, the last value of the error rate may be read in this register (unlike VTH, the possible range is 0 to 255/256).

### VSTATUS (Read only register)

CF 0 0 PRF LK

Internal Address: Hex08

| CF |        |        |         |        |       | covery)<br>QPSK |

|----|--------|--------|---------|--------|-------|-----------------|

|    | signal | is pre | esent a | at the | input | of the          |

Viterbi decoder.

PRF : Puncture Rate Found

PRF indicates the state of the puncture rate research: 0 for searching, 1 when found; this bit is irrelevant in manual mode.

LK : Locked/searchingthe sync word

LK indicates the state of the sync word research: 0 for searching, 1 when found.

PR [2..0]: Current Puncture Rate

It hold the current puncture rate indice with the correspondance:

| Punctured Rate                            | Regiter Value PR[20] |

|-------------------------------------------|----------------------|

| Basic 1/2                                 | 100                  |

| Punctured 2/3                             | 000                  |

| Punctured 3/4                             | 001                  |

| Punctured 5/6                             | 010                  |

| Punctured 7/8 (Mode A)<br>or 6/7 (Mode B) | 011                  |

#### X - CONVOLUTIONAL DE-INTERLEAVER

This is a 204 x 12 convolutional interleaver in Mode A; the periodicity of 204 bytes for sync byte is preserved.

The de-interleaver may be skipped (see RS register).

### XI - REED-SOLOMON DECODER **AND DESCRAMBLER**

The input blocks are 204 byte long with 16 parity bytes in Mode A; the synchro byte is the first byte of the block. Up to 8 byte errors may be fixed.

Code Generator polynom:

$$g(x) = (x - \omega^0) (x - \omega^1) (...) (x - \omega^{15})$$

over the Galois Field generated by:

$$X^{8} + X^{4} + X^{3} + X^{2} + 1 = 0$$

Energy dispersal descrambler:

Output energy dispersal descrambler generator:

$$X^{15} + X^{14} + 1$$

The polynom is initialised every eight blocks with the sequence 100101010000000. The synchro words are unscrambled.

#### Control register: RS register

Internal Address: Hex0A

The reset value is written in each register cell

| RS7 | RS6 | RS5 | RS4 | RS3 | RS2 | RS1 | RS0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 1   | 0   | 1   | 1   | 1   | 0   | 0   | 0   |

RS7: De-interleaver Enable

If 1, the input flow is deinterleaved. If 0, the flow is not affected.

RS6: If 0, Output data are corrected bytes (normal operating mode).

If 1, Output data are Reed-Solomon correction bytes (error count mode) (see Note 1).

RS5: Reed-Solomon Enable

If 1, the input code is corrected.

If 0, no correction happens; all the data are

fed to the descrambler.

The error signal remains inactive.

RS4: Descrambler Enable

If 1, the output flow from Reed-Solomon

decoder is descrambled.

If 0, the descrambler is desactived.

RS3: Write Error Bit

If RS3=1, and uncorrectible error happens, the MSB of the first byte following the sync byte is forced to 1after descrambling.

RS2: Super Synchro Suppression

If RS2=1, all synchro bytes are Hex47 in

If RS2=0, the synchro is complemented every 8th packet. It allows, when scrambler is off, to provide RS coded signals for use in low-cost SMATV interface.

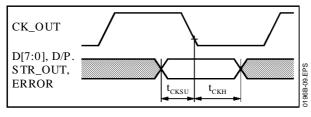

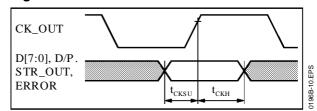

RS1: Output Clock Polarity

If RS1=0, data and control signals change during high to low transition of CK\_OUT. If RS1=1, they change during the low to high transition.

**Output Clock Configuration**

If RS0=0, CK\_OUT is continuous.

If RS0=1, CK\_OUT remains low during the

parity bits.

When RS6 = 1, the output data are the correction bytes

applied to data incoming the Reed-Solomon block. The number of bits at 1 in these output data represent therefore the number of errors remaining at the output of VITERBI decoder

All null output data mean no error left after VITERBI

Remark: Output datas are meaningless when error flag (Pin 34) is

set to high level.

## Figure 3

3196B-05.EPS

## **ABSOLUTE MAXIMUM RATINGS**

Maximum limits indicate where permanent device damages occur, continuous operation at these limits is not intended and should be limited to those conditions specified in section "DC Electrical Specifications".

| Symbol           | Parameter                     | Value                         | Unit |

|------------------|-------------------------------|-------------------------------|------|

| $V_{DD}$         | Power Supply (1)              | -0.3 to 4                     | V    |

| VI               | Voltage on Input pins (2)     | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Vo               | Voltage on Output pins        | -0.3 to V <sub>DD</sub> +0.3  | V    |

| T <sub>stg</sub> | Storage Temperature           | -40 to +150                   | °C   |

| Toper            | Operating Ambient Temperature | -10 to +85                    | °C   |

| P <sub>D</sub>   | Power Dissipation             | 1.5                           | W    |

Notes: 1. All V<sub>DD</sub> to be tied together

2. SCL, SDA, NRES Pins can be tied to 5V ± 10% with an impedance ≥ 2kΩ (remark in these conditions the input leakage current becomes higher than 10μA).

## DC ELECTRICAL CHARACTERISTICS (V<sub>DD</sub> = 3.3V, T<sub>amb</sub> = 25°C unless otherwise specified)

| Symbol                             | Parameter                                                                  | Test conditions                                                                 | Min.        | Тур.       | Max.        | Unit          |

|------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------|------------|-------------|---------------|

| $V_{DD}$                           | Operating Voltage                                                          | 0°C ≤ T <sub>oper</sub> ≤ 70°C<br>0°C < T <sub>oper</sub> < 85°C, M_CLK ≤ 55MHz | 3.0<br>3.15 | 3.3<br>3.3 | 3.6<br>3.45 | V             |

| I <sub>DD</sub>                    | Average Power Supply Current                                               | C <sub>LOAD</sub> = 20pF on all outputs,<br>M_CLK = 60MHz                       |             | 300        | 480         | mA            |

| V <sub>IL</sub><br>V <sub>IH</sub> | Input Logic Low Voltage except M_CLK Input Logic High Voltage except M_CLK | M_CLK = 60MHz                                                                   | -0.3<br>2.0 |            | 0.8<br>3.6  | V             |

| V <sub>IL</sub><br>V <sub>IH</sub> | Input Logic Low Voltage for M_CLK Input Logic High Voltage for M_CLK       | M_CLK = 60MHz                                                                   | -0.3<br>2.2 |            | 0.8<br>3.6  | V             |

| I <sub>LK</sub>                    | Input Leakage Current                                                      | $V_{IN} = 0V$ and $V_{DD}$                                                      |             |            | 10          | μА            |

| C <sub>IN</sub>                    | Input Capacitance                                                          |                                                                                 |             | 3.5        |             | pF            |

| V <sub>OL</sub><br>V <sub>OH</sub> | Output Logic Low Voltage<br>Output Logic High Voltage                      | $C_{LOAD}$ = 20pF, $I_{LOAD}$ = 2mA, $M\_CLK$ = 60MHz                           | 2.4         |            | 0.5         | <b>&gt;</b> > |

Note: This product doesn't withstand the MIL 883C Norm at 2kV, but only at 1.5kV (all VDD tied together).

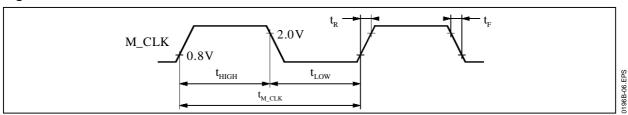

## **TIMING CHARACTERISTICS**

| Symbol             | Parameter                                                  | Min.                  | Тур. | Max.               | Unit     |

|--------------------|------------------------------------------------------------|-----------------------|------|--------------------|----------|

| PRIMARY            | CLOCK (see Figure 4)                                       | •                     |      |                    |          |

| t <sub>M_CLK</sub> |                                                            | 16.6<br>18.2          |      |                    | ns<br>ns |

| thigh              | Clock High Time                                            | 6                     |      |                    | ns       |

| t <sub>LOW</sub>   | Clock Low Time                                             | 6                     |      |                    | ns       |

| t <sub>R</sub>     | Clock Rising Edge                                          |                       |      | 4                  | ns       |

| t <sub>F</sub>     | Clock Falling Edge                                         |                       |      | 4                  | ns       |

| I[5:0],Q[5:        | )] INPUT SPECIFICATIONS (see Figure 5)                     |                       |      |                    |          |

| t <sub>SU</sub>    | I,Q stable before M_CLK                                    | 4                     |      |                    | ns       |

| t <sub>H</sub>     | I,Q stable after M_CLK                                     | 4                     |      |                    | ns       |

| D60 OUT            | PUT CHARACTERISTICS (see Figure 6)                         |                       |      |                    |          |

| t <sub>60</sub>    | D60 period                                                 | (Tm_clk * 60)<br>- 10 |      | (Tm_clk*60)<br>+10 | ns       |

| D[7:0],D/P         | ,CK_OUT,STR_OUT,ERROR OUTPUT CHARACTERISTICS               |                       |      |                    |          |

| Bit RS1 =          | = 1 in register RS ( adr = 0x0A) (see Figure 7)            |                       |      |                    |          |

| tcksu              | D[7:0],D/P,STR_OUT,ERROR stable before CK_OUT Falling Edge | 32                    |      |                    | ns       |

| tckh               |                                                            |                       |      | ns                 |          |

| Bit RS1 =          | 0 in register RS ( adr = 0x0A) (see Figure 8)              |                       |      |                    |          |

| t <sub>CKSU</sub>  | D[7:0],D/P,STR_OUT,ERROR stable before CK_OUT Rising Edge  | 32                    |      |                    | ns       |

| t <sub>CKH</sub>   | D[7:0],D/P,STR_OUT,ERROR stable after CK_OUT Rising Edge   | 32                    |      |                    | ns       |

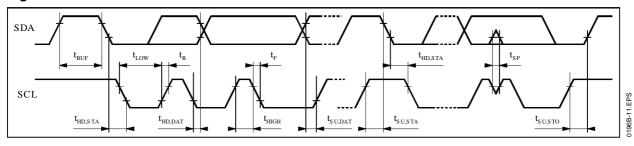

## I<sup>2</sup>C BUS CHARACTERISTICS (see Figure 9)

| Symbol                                | Parameter                                                                                    | Test Conditions                                                                 | Min.                       | Тур. | Max.       | Unit     |

|---------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------|------|------------|----------|

| V <sub>IL</sub><br>V <sub>IH</sub>    | Input Logic Low Voltage Input Logic High Voltage                                             | See Note 1                                                                      | -0.3<br>2.0                |      | 0.8<br>5.5 | V        |

| V <sub>OL</sub><br>V <sub>OH</sub>    | Output Logic Low Voltage<br>Output Logic High Voltage                                        | C <sub>LOAD</sub> = 20pF, I <sub>LOAD</sub> = 2mA,<br>M_CLK = 60MHz, see Note 1 | 2.4                        |      | 0.5<br>5.5 | V        |

| $I_{LK}$                              | Input Leakage Current                                                                        | $V_{IN} = 0V$ to $V_{DD}$ , see Note 2                                          | -10                        |      | 10         | μΑ       |

| Cin                                   | Input Capacitance                                                                            |                                                                                 |                            | 3.5  |            | pF       |

| I <sub>OL</sub>                       | Output Sink Current                                                                          | $V_{OL} = 0.5V$                                                                 |                            | 10   |            | mA       |

| tsp                                   | Pulse Width of Spikes which must be suppressed by the Input filter                           |                                                                                 | 0                          |      | 50         | ns       |

| f <sub>SCL</sub>                      | SCL Clock Frequency                                                                          |                                                                                 | 0                          |      | 400        | kHz      |

| t <sub>BUF</sub>                      | Bus Free Time between a STOP and START Condition                                             |                                                                                 | 1.3                        |      |            | μs       |

| t <sub>HD,STA</sub>                   | Hold Time (repeated) START Condition. After this period, the first clock pulse is generated. |                                                                                 | 0.6                        |      |            | μs       |

| t <sub>LOW</sub><br>t <sub>HIGH</sub> | Low Period of the SCL Clock<br>High Period of the SCL Clock                                  |                                                                                 | 1.3<br>0.6                 |      |            | μs<br>μs |

| t <sub>SU,STA</sub>                   | Set-up Time for a repeated START Condition                                                   |                                                                                 | 0.6                        |      |            | μs       |

| t <sub>SU,STO</sub>                   | Set-up Time for STOP Condition                                                               |                                                                                 | 0.6                        |      |            | μs       |

| t <sub>HD,DAT</sub>                   | Data Hold Time                                                                               | See Note 3                                                                      | 0                          |      | 0.9        | μs       |

| t <sub>SU,DAT</sub>                   | Data Set-up Time                                                                             | See Note 4                                                                      | 100                        |      |            | ns       |

| t <sub>R</sub> , t <sub>F</sub>       | Rise and Fall Time of both SDA and SCL signals                                               | See Note 5                                                                      | 20 +<br>0.1 C <sub>B</sub> |      | 300        | ns       |

| Св                                    | Capacitive Load for each Bus Line                                                            |                                                                                 |                            |      | 400        | pF       |

An impedance higher than  $2k\Omega$  is required when SDA and SCL are tied to a 5V  $\pm$  10% voltage line. Notes: 1.

Leakage current exceeds  $\pm$  10µA when SDA and SCL are tied to a 5V  $\pm$  10% line.

A device must internally provide a hold time of at least 300ns for the SDA signal (refered to the V<sub>IH Min.</sub> of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

The maximum tHD,DAT has only to be met if the device does not stretch the low period  $(t_{LOW})$  of the SCL signal. A fast-mode  $l^2C$  bus device can be used in a standard-mode  $l^2C$  bus system, but the requirement  $t_{SU,DAT} \ge 250$ ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line  $t_{R,Max} + t_{SU,DAT} = 1000 + 250 = 1250$ ns (according to the standard-mode  $l^2C$  bus specification) before the SCL line is released.

$C_B$  = total capacitance of one bus line in pF.

0196B-03.BTBL

## Figure 4

## Figure 5

## Figure 6

## Figure 7

## Figure 8

## Figure 9

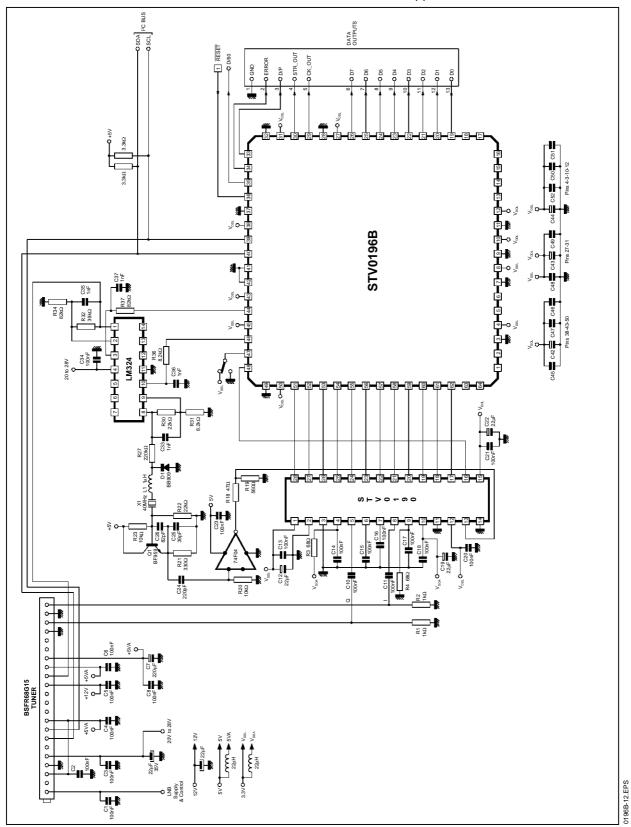

## APPLICATION DIAGRAM: STV0196B/STV0190 Fixed 20 MBauds Application

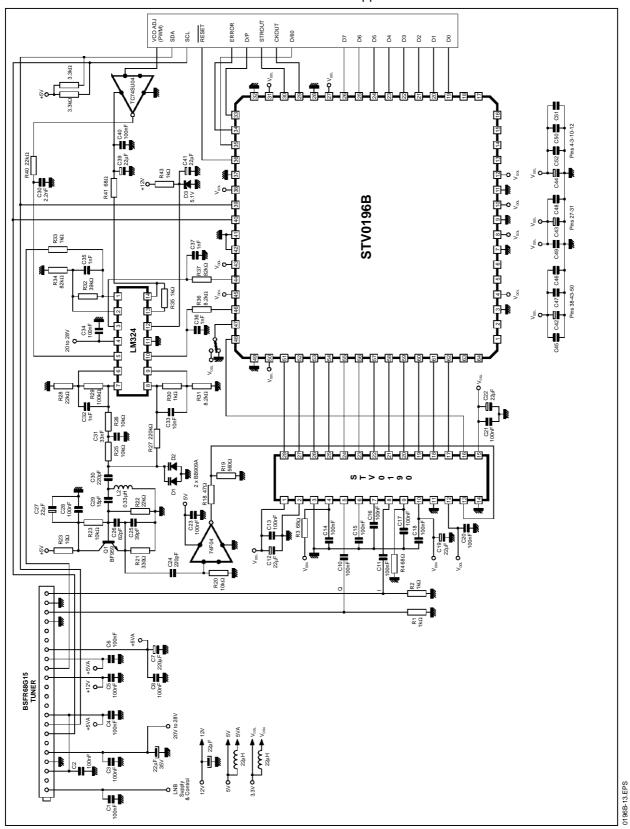

## APPLICATION DIAGRAM: STV0196B/STV0190Multirate Application

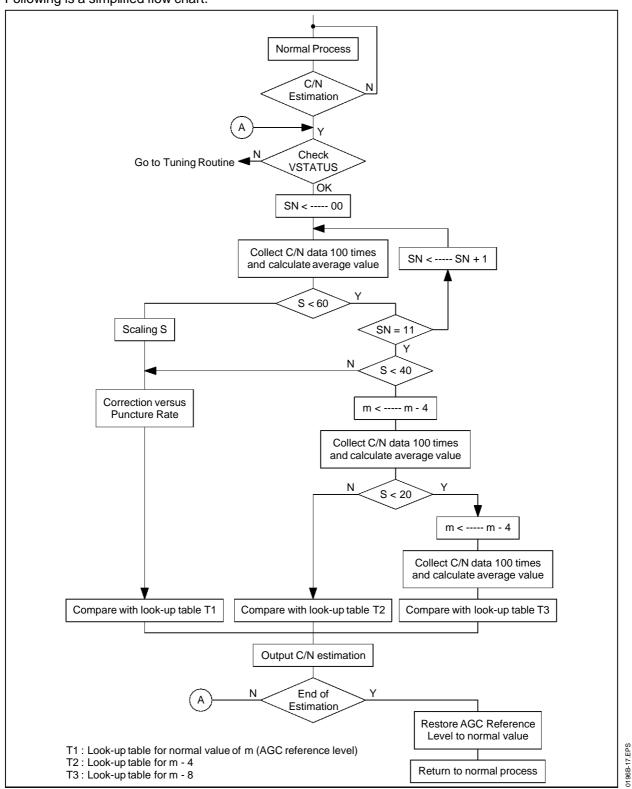

#### **ANNEXE 1: C/N ESTIMATION**

The C/N indicator register permanently reports a value S which depends on the C/N level at the input of the STV0196B.

The C/N indicator offers a programmable sensitivity which allows a reliable C/N estimation over a wide Eb/No range (4dB to 16dB typically); this is particularly useful to optimize the dish positioning.

Remark: In this note, we have assumed that:

$$\frac{C}{N} = \frac{E_b}{N_o} \cdot 2 \text{ (PR)}, \text{ PR : Puncture Rate}$$

The sensitivity of the C/N indicator is dependant on the SN bits of the register VSEARCH (Hex06) and on the AGC function reference level "m".

## A - SUGGESTED PROCEDURE TO RELIABLY ESTIMATE THE ACTUAL C/N

As no simple mathematical low ensumes a good matching between the C/N indicator and the actual C/N, the method relies on a comparaison of the value S (reported by the C/N indicator) with a reference look-up table which has been realized under well controlled conditions.

Basically there are 3 steps in the C/N estimation software.

- To collect C/N indication (under adapted conditions).

- Indication scaling and correction versus the puncture rate

- 3. Comparaison with the look-up table

#### A.1 - To collect C/N Indication

The purpose of this first step is to collect the C/N indicator with the appropriate sensitivity (SN bits and AGC reference level m).

#### Basically:

- The value reported by the C/N indicator is proportional to the Number of bits (at the output of the VITERBI decoder) selected by the SN bits.

- The AGC reference level is only changed to appreciate the high Eb/No ratios. This second parameter has to be used with some care.

**Procedure**: Before to make an estimation, the VSTATUS register (internal address Hex 08) must be checked to make sure that:

- a carrier is actually present (bit 7)

- puncture rate is found (bit 4)

- puncture rate is known (bits 0-1-2)

Remark: Optionally, it is possible to make an estimation without informations about the puncture rate (useful when the dish is still very far from optimum position), in such case the puncture rate is forced.

The C/N indicator register has no overflow detection, so it is necessary to start the measure with the lowest sensitivity (SN=00) and to gradually increase it (using SN bits). Due to the noise, the result S of the measure may have a lot of dispersion, consequently it is recommended to measure S several times (typically 100 times) and to calculate the average value.

Remark: The required duration  $t_W$  between two readings of the register must be higher than:

$$t_{W (Min.)} = \frac{BC}{BR}$$

BR = 2 (Fs) x (PR)

with BC: Bit Count (selected by SN bits)

Fs: Symbol Rate PR: Puncture Rate

When the current average value of the measure S is lower than 63, the measure is done again with a higher sensitivity. With this care the new C/N measure S does not overflow the counter (the counting time is multiplied by 4 at each step). In practice some margin is given to this threshold: a higher sensitivity is selected when the average value of S is lower than 60.

When the maximum SN value is reached (SN = 11  $\Leftrightarrow$  to 65 536 bits at the output of the VITERBI decoder), the sensitivity can be further increased by lowering the AGC reference level (parameter  $\mathbf{m}$ , internal address Hex11, bit 0 to bit 5).

Remark: There is the need to change the AGC reference level only in case of high C/N conditions, then to change the reference level has no important influence on the bit error rate (BER). In other words, a completete C/N estimation can be run during the operation of the receiver.

When the highest possible sensitivity is found the result S (average value) is ready for further process.

#### ANNEXE 1 : C/n ESTIMATION (continued)

#### A.2 - Scaling and Correction versus Puncture Rate

#### Scaling

This simple operation is recommended to easily compare data which have been recorded under different sensitivity conditions. To do so, the result S of the C/N indication is multiplied by a coefficient so that the scaled value would correspond to a measure done with the highest counting period (SN = 11).

Remark: Scaling is not done for results which have been recorded after changing the AGC reference level.

Scaling operation: Scaled\_value =  $(S) \times (factor)$  factor = 64 when C/N estimation is done with SN = 00 factor = 16 when C/N estimation is done with SN = 01 factor = 4 when C/N estimation is done with SN = 10 factor = 1 when C/N estimation is done with SN = 11

#### Correction versus puncture rate

This correction is not required when a reference look-up table have been memorized for each possible puncture rate. When required, the correction is done with respect to the puncture rate PRref of the reference look-up table:

$$Scorrected = (S) \cdot \frac{PRcurrent}{PRref}$$

PR current: the puncture currently identified with the bits 0,1,2 of VSTATUS register.

#### A.3 - Comparing with the look-up table

In the application the read value Srs (scaled and corrected) will seldom exactly match a value of the look-up table; consequently there will be the need for some interpolation.

To make it simple, a linear interpolation is preferred, with such a solution a good precision can be achieved when the look-up table is built with a small step for the C/N (or Eb/No).

#### Interpolation

Generally Ssr will be between two values of the reference look-up table :  $V_{(Min.)} \leq Ssr \leq V_{(Max.)}$ , with  $V_{(Min.)}$  corresponding  $C/N_{(Min.)}$  and  $V_{(Max.)}$  corresponding to  $C/N_{(Min.)}$  (with typically  $(C/N_{(Max.)})$  -  $(C/N_{(Min.)})$  = 0.5dB).

The calculated C/N corresponding to Ssr is:

$$C/N = C/N_{(Max.)} - \left( \ C/N_{(Max.)} - C/N_{(Min.)} \ \right) \cdot \frac{V_{(Min.)} - Ssr}{V_{(Min.)} - V_{(Max.)}}$$

in above calculation C/N (or Eb/No) are given in algebraic value (not in dB).

## **ANNEXE 1:** C/n ESTIMATION (continued)

## **B-FLOW CHART**

Following is a simplified flow chart.

## ANNEXE 1 : C/n ESTIMATION (continued)

## **C-RESULTS**

The results reported in the following table are typical values. When evaluating another application some differences may be especially noticed when Eb/No is higher than 10dB, in these conditions the characteristics of the tuner and the A/D converter may influence the results.

**Conditions :** Puncture rate : 2/3, 20MBauds signal, DVB encoding (RS : 188/204),  $C/N = \frac{Eb}{No} 2 \cdot (PR)$

| Eb/No (dB) | Measurement Conditions |              | S   | S Scaled |  |

|------------|------------------------|--------------|-----|----------|--|

| ED/NO (GB) | SN bits (hex)          | AGC, m (dec) | 3   | 5 Scaled |  |

| 4          | 1                      | 20           | 152 | 2.432    |  |

| 4.5        |                        |              | 137 | 2.192    |  |

| 5          |                        |              | 121 | 1.936    |  |

| 5.5        |                        |              | 105 | 1.664    |  |

| 6          |                        |              | 92  | 1.474    |  |

| 6.5        |                        |              | 78  | 1.248    |  |

| 7          |                        |              | 64  | 1.024    |  |

| 7.5        | 2                      | 20           | 205 | 820      |  |

| 8          |                        |              | 168 | 672      |  |

| 8.5        |                        |              | 131 | 524      |  |

| 9          |                        |              | 98  | 392      |  |

| 9.5        |                        |              | 73  | 292      |  |

| 10         | 3                      | 20           | 212 | 212      |  |

| 10.5       |                        |              | 146 | 146      |  |

| 11         |                        |              | 95  | 95       |  |

| 11.5       |                        |              | 61  | 61       |  |

| 12         | 3                      | 16           | 122 |          |  |

| 12.5       |                        |              | 84  |          |  |

| 13         |                        |              | 55  |          |  |

| 13.5       |                        |              | 35  |          |  |

| 14         |                        |              | 22  |          |  |

| 14.5       |                        |              | 13  |          |  |

| 15         | 3                      | 12           | 128 |          |  |

| 15.5       |                        |              | 95  |          |  |

| 16         |                        |              | 70  |          |  |

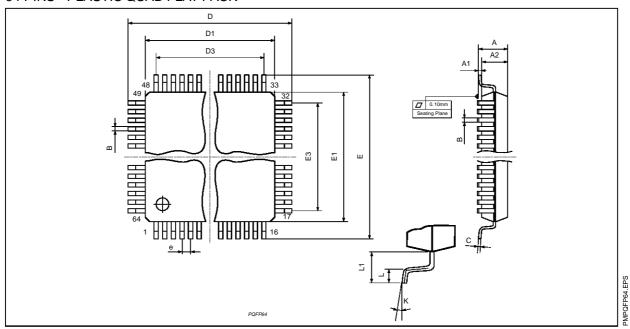

#### PACKAGE MECHANICAL DATA

64 PINS - PLASTIC QUAD FLAT PACK

| Dimensions | Millimeters |       |           | Inches      |        |        |

|------------|-------------|-------|-----------|-------------|--------|--------|

| Dimensions | Min.        | Тур.  | Max.      | Min.        | Тур.   | Max.   |

| А          |             |       | 3.40      |             |        | 0.134  |

| A1         | 0.25        |       |           | 0.010       |        |        |

| A2         | 2.55        | 2.80  | 3.05      | 0.100       | 0.110  | 0.120  |

| В          | 0.30        |       | 0.45      | 0.0118      |        | 0.0177 |

| С          | 0.13        |       | 0.23      | 0.005       |        | 0.009  |

| D          | 16.95       | 17.20 | 17.45     | 0.667       | 0.677  | 0.687  |

| D1         | 13.90       | 14.00 | 14.10     | 0.547       | 0.551  | 0.555  |

| D3         |             | 12.00 |           |             | 0.472  |        |

| е          |             | 0.80  |           |             | 0.0315 |        |

| E          | 16.95       | 17.20 | 17.45     | 0.667       | 0.677  | 0.687  |

| E1         | 13.90       | 14.00 | 14.10     | 0.547       | 0.551  | 0.555  |

| E3         |             | 12.00 |           |             | 0.472  |        |

| К          |             |       | 0° (Min.) | , 7° (Max.) |        |        |

| L          | 0.65        | 0.80  | 0.95      | 0.026       | 0.0315 | 0.0374 |

| L1         |             | 1.60  |           |             | 0.063  |        |

PQFP64.TBL

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

#### © 1996 SGS-THOMSON Microelectronics - All Rights Reserved

Purchase of I<sup>2</sup>C Components of SGS-THOMSON Microelectronics, conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in a I<sup>2</sup>C system, is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

## SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.