## **STV0118**

## PAL/NTSC HIGH PERFORMANCE DIGITAL ENCODER

#### PRELIMINARY DATA

- NTSC-M, PAL-B, D, G, H, I, N, M, PLUS NTSC-4.43 ENCODING (OPTIONAL PEDES-TAL IN ALL STANDARDS)

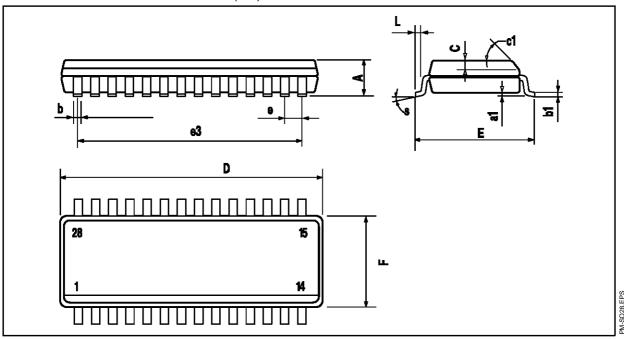

- SMALL AND ECONOMICAL SO28 PACKAGE

- LINE SKIP/INSERT CAPABILITY SUPPRES-SING THE NEED FOR AN EXTERNAL VCXO, THUS REDUCING APPLICATION COST

- 4 SIMULTANEOUS ANALOG OUTPUTS: RGB+ CVBS, or S-VHS (Y/C) + CVBS1 + CVBS2

- 54MHz INPUT MULTIPLEX INTERFACE FOR DOUBLE ENCODING APPLICATIONS

(TO BE ABLE TO ENCODE OR NOT THE OSD CONTENT OF THE VIDEO INPUT STREAM)

- CROSS-COLOR REDUCTION BY SPECIFIC TRAP FILTERING ON LUMA WITHIN CVBS FLOW

- CLOSED CAPTIONING, CGMS ENCODING AND TELETEXT ENCODING

- ITU-R/CCIR601 ENCODING WITH EASILY PROGRAMMABLE COLOR SUB-CARRIER FREQUENCIES

- DIGITAL FRAME SYNC INPUT/OUTPUT (ODDEV/VSYNC), PROGRAMMABLE PO-LARITY AND RELATIVE POSITION

- DIGITAL HORIZONTAL SYNC INPUT/OUPUT (HSYNC), PROGRAMMABLE POLARITY AND RELATIVE POSITION

- DIGITAL LINE OR FRAME SYNC EXTRACTION FROM ITU-R/CCIR656 / D1 DATA

- MASTER OPERATION MODE, PLUS 6 SLAVE MODES

- INTERLACED/NON-INTERLACED OPERA-TION MODES

- FULL OR PARTIAL VERTICAL BLANKING

- LUMA FILTERING WITH 2X OVERSAMPLING & SINY/Y CORRECTION

- CHROMINANCE FILTERING WITH 4X OVER-SAMPLING TO EITHER 1.1MHz, 1.3MHz, 1.6MHz or 1.9MHz

- WIDE CHROMINANCE BANDWIDTH FOR RGB ENCODING (2.45MHz)

- 24-BIT DIRECT DIGITAL FREQUENCY SYN-THESIZER FOR COLOR SUBCARRIER

- PROGRAMMABLE RESET OF COLOR SUB-CARRIER PHASE (4 MODES)

- EASY CONTROL VIA FAST I<sup>2</sup>C BUS

- TWO I<sup>2</sup>C ADDRESSES

- AUTOTEST OPERATION MODE (ON-CHIP COLOR BAR PATTERN 100/0/75/0)

- CMOS TECHNOLOGY WITH 3.3V POWER SUPPLY

- APPLICATIONS: SATELLITE, CABLE & TERRESTRIAL DIGITAL TV DECODERS, MULTIME-DIATERMINALS, DVD PLAYERS

**ORDER CODE:** STV0118

May 1997 1/42

## STV0118

| CONTE                      | INTS                                                    | Page           |

|----------------------------|---------------------------------------------------------|----------------|

| I                          | GENERAL DESCRIPTION                                     | 3              |

| II                         | PIN INFORMATION                                         | 3              |

| II.1                       | PIN CONNECTIONS                                         | 3              |

| II.2                       | PIN DESCRIPTION.                                        | 4              |

| III                        | BLOCK DIAGRAM                                           | 5              |

| IV                         | FUNCTIONAL DESCRIPTION                                  |                |

|                            |                                                         | 6              |

| IV.1                       | DATA INPUT FORMAT                                       | 6              |

| IV.2<br>IV.3               | VIDEO TIMING                                            | 6<br>10        |

| IV.3<br>IV.4               | RESET PROCEDURE                                         | 10             |

|                            |                                                         |                |

| IV.5                       | SLAVE MODES                                             | 12             |

| IV.5.1<br>IV.5.2<br>IV.5.3 | Synchronization onto a Line Sync Signal                 | 12<br>13<br>14 |

| IV.6                       | INPUT DEMULTIPLEXER                                     | 15             |

| IV.7                       | SUB-CARRIER GENERATION                                  | 15             |

| IV.8                       | BURST INSERTION.                                        | 16             |

| IV.9                       | LUMINANCE ENCODING.                                     | 16             |

| IV.10                      | CHROMINANCE ENCODING                                    | 17             |

| IV.11                      | COMPOSITE VIDEO SIGNAL GENERATION                       | 17             |

| IV.12                      | RGB ENCODING                                            | 18             |

| IV.13                      | CLOSED CAPTIONING                                       | 18             |

| IV.14                      | CGMS ENCODING                                           | 19             |

| IV.15                      | TELETEXT ENCODING                                       | 19             |

| IV.15.1                    | Signals Exchanged                                       | 19             |

| IV.15.2                    | Transmission Protocol.                                  | 19             |

| IV.15.3<br>IV.15.4         | Programming                                             | 20<br>20       |

| IV.16                      | I <sup>2</sup> C BUS                                    | 21             |

| IV.17                      | DUAL ENCODING APPLICATION WITH 54MBIT/S YCRCB INTERFACE | 22             |

| IV.18                      | LINE SKIP / LINE INSERT CAPABILITY                      | 24             |

| IV.19                      | CVBS, S-VHS AND RGB ANALOG OUTPUTS                      | 24             |

| ٧                          | CHARACTERISTICS                                         | 25             |

| V.1                        | ABSOLUTE MAXIMUM RATINGS                                | 25             |

| V.1<br>V.2                 | THERMAL DATA                                            | 25<br>25       |

| V.2<br>V.3                 | DC ELECTRICAL CHARACTERISTICS.                          | 25<br>25       |

| V.4                        | AC ELECTRICAL CHARARCTERISTICS.                         | 26             |

|                            |                                                         |                |

| VI                         | REGISTERS                                               | 27             |

| VI.1                       | REGISTER MAPPING                                        | 27             |

| VI.2                       | REGISTER CONTENTS AND DESCRIPTION                       | 28             |

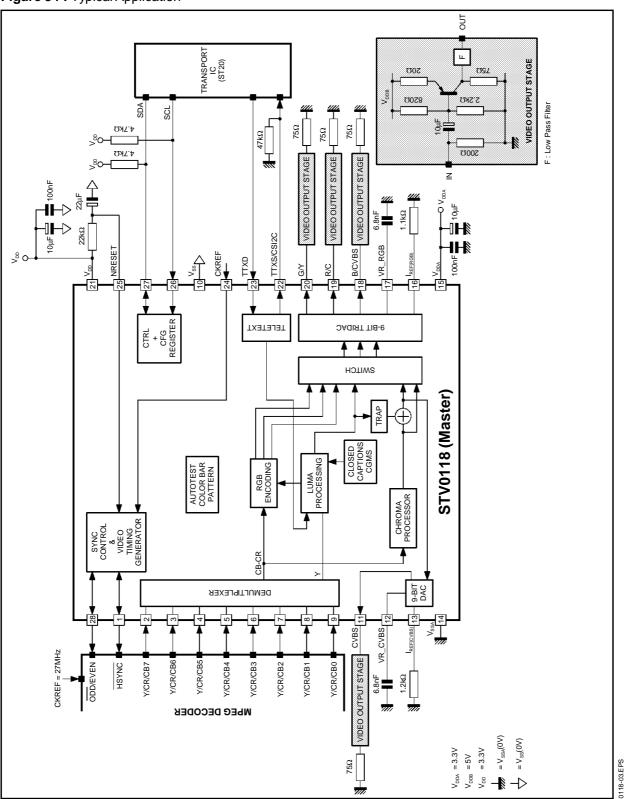

| VII                        | APPLICATION                                             | 41             |

| VIII                       | PACKAGE MECHANICAL DATA                                 | 42             |

#### I - GENERAL DESCRIPTION

The STV0118 is a high performance PAL/NTSC digital encoder in a low cost pakage. It converts a 4:2:2 digital video stream into a standard analog baseband PAL/NTSC signal and into RGB analog components. The STV0118 can handle interlaced mode (with 525/625 line standards) and non-interlaced mode. It can perform Closed-Captions, CGMS or Teletext encoding.

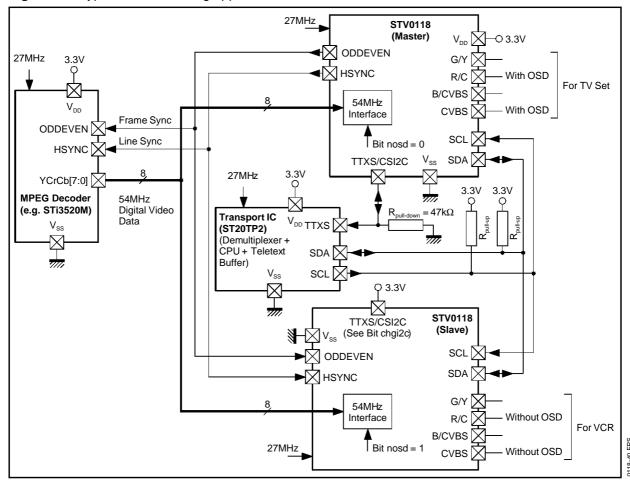

Four analog output pins are available, on which it is possible to output either S-VHS(Y/C) + CVBS1 + CVBS2 or RGB + CVBS. Moreover, it is possible to use two STV0118 in parallel to interface with SGS-THOMSON's MPEG decoder ICs that are able to deliver a 54Mbit/s "double" YCrCb stream (e.g. the STi3520M). This allows for example to encode OSD in one of the streams only.

#### **II - PIN INFORMATION**

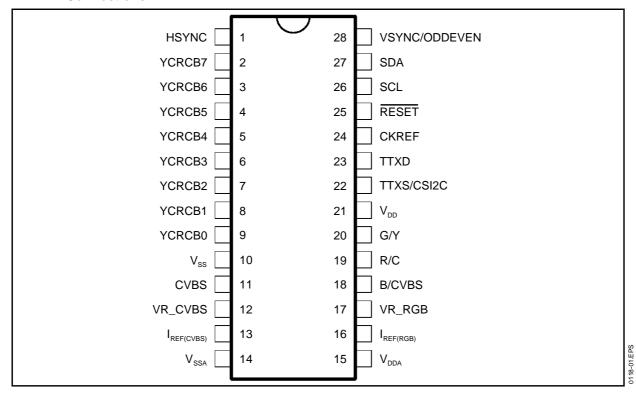

#### **II.1 - Pin Connections**

3/42

# II - PIN INFORMATION (continued)

## II.2 - Pin Description

| Pin                                  | Name                                                                         | Туре                                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                    | HSYNC                                                                        | I/O                                           | Line Synchronization Signal: - Input in ODDEV+HSYNC or VSYNC + HSYNC or VSYNC slave modes - Output in all other modes (master/slave) - Synchronous to rising edge of CKREF - Default polarity: negative pulse                                                                                                                                                                                                                                                                                               |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | YCrCb7<br>YCrCb6<br>YCrCb5<br>YCrCb4<br>YCrCb3<br>YCrCb2<br>YCrCb1<br>YCrCb0 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Input: time multiplexed 4:2:2 luminance and chrominance data as defined in ITU-R Rec601-2 and Rec656 (except for TTL input levels). This bus interfaces with MPEG video decoder output port and typically carries a stream of Cb,Y,Cr,Y digital video at CKREF frequency, clocked on the rising edge (by default) of CKREF. A 54-Mbit/s 'double' Cb, Y, Cr, Y input multiplex is supported for double encoding application (rising and falling edge of CKREF are operating). Output: for test purpose only. |

| 10                                   | Vss                                                                          | Supply                                        | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11                                   | CVBS                                                                         | Output                                        | Analog Composite Video Output (current-driven). CVBS must be connected to analog ground over a load resistor (R <sub>LOAD</sub> ). Following the load resistor, a simple analog low pass filter is recommended CVBS amplitude is proportional to I <sub>REF(CVBS)</sub> (V <sub>OUT(N)</sub> = N x R <sub>LOAD</sub> x I <sub>REF(CVBS)</sub> /96) with N = [0-511] V <sub>OUT(Max.)</sub> = 1V <sub>PP</sub> and I <sub>OUT(Max.)</sub> = 5mÅ                                                              |

| 12                                   | VR_CVBS                                                                      | I/O                                           | Internal Reference Voltage for the 9-bit DAC CVBS. VR_CVBS must be connected to analog ground over a capacitor (6.8nF typ.), VR_CVBS = 1.9V                                                                                                                                                                                                                                                                                                                                                                 |

| 13                                   | I <sub>REF(CVBS)</sub>                                                       | I/O                                           | Reference current source for the 9-bit DAC CVBS.  - $I_{REF(CVBS)}$ must be biased to analog ground over a reference resistor $R_{REF(CVBS)}$ - $R_{REF(CVBS)(Min.)} = 5.95 \times R_{LOAD}/V_{OUT(Max.)}$ with $V_{OUT(Max.)} = 1V_{PP}$ and $I_{OUT(Max.)} = 5mA$ ( $I_{REF(CVBS)} = V_{REF(CVBS)}/R_{REF(CVBS)}$ ), $V_{REF(CVBS)(Typ.)} = 1.12V$ .                                                                                                                                                      |

| 14                                   | $V_{SSA}$                                                                    | Supply                                        | Analog ground for DACs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15                                   | $V_{DDA}$                                                                    | Supply                                        | Analog positive power supply for DACs (+3.3V nom.)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16                                   | IREF(RGB)                                                                    | I/O                                           | Reference current source for Tri-DAC R/Y,G/C,B/CVBS.<br>- $I_{REF(RGB)}$ must be connected to analog ground over a reference resistor $I_{REF(RGB)}$ - $I_{REF(RGB)(Mn.)}$ = 5.95 x $I_{LOAD}/I_{OUT(Max.)}$ , with $I_{OUT(Max.)}$ = 1 $I_{OUT(Max.)}$ = 5mA ( $I_{REF(RGB)}$ = $I_{REF(RGB)}/I_{REF(RGB)}$ ), $I_{REF(RGB)}/I_{IVp.}$ = 1.12V.                                                                                                                                                            |

| 17                                   | VR_RGB                                                                       | I/O                                           | Internal reference voltage for the 9bit Tri-DAC R/Y,G/C,B/CVBS. VR_RGB must be biased to analog ground over a typical 6.8nF capacitor, VR_RGB = 1.9V.                                                                                                                                                                                                                                                                                                                                                       |

| 18                                   | B/CVBS                                                                       | 0                                             | Analog 'Blue' or CVBS output (current-driven). This output must be connected to analog ground over a load resistor ( $R_{LOAD}$ ). Following the load resistor, a simple analog low pass filter is recommended. $V_{OUT(Max.)} = 1V_{PP}$ and $I_{OUT(Max.)} = 5mA$ ( $V_{OUT(N)} = N \times R_{LOAD} \times I_{REF(RGB)}/96$ ) with $N = [0-511]$ .                                                                                                                                                        |

| 19                                   | R/C                                                                          | 0                                             | Analog 'Red' or S-VHS Chrominance output (current-driven). This output must be connected to analog ground over a load resistor ( $R_{LOAD}$ ). Following the load resistor, a simple analog low pass filter is recommended. $V_{OUT(Max.)} = 1V_{PP}$ and $I_{OUT(Max.)} = 5mA$ ( $V_{OUT(N)} = N \times R_{LOAD} \times I_{REF(RGB)}/96$ ) with $N = [0-511]$ .                                                                                                                                            |

| 20                                   | G/Y                                                                          | 0                                             | Analog 'Green' or S-VHS Luminance output (current-driven). This output must be connected to analog ground over a load resistor (R <sub>LOAD</sub> ). Following the load resistor, a simple analog low pass filter is recommended. $V_{\text{OUT}(Max.)} = 1V_{PP} \text{ and } I_{\text{OUT}(Max.)} = 5\text{mA } (V_{\text{OUT}(N)} = N \text{ x } R_{\text{LOAD}} \text{ x } I_{\text{REF}(RGB)}/96)$ with N = [0-511].                                                                                   |

| 21                                   | $V_{DD}$                                                                     | Supply                                        | Digital positive supply voltage (+3.3V nom.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 22                                   | TTXS/CSI2C                                                                   | I/O                                           | Output : positive sync pulse for control of Teletext buffer in external demultiplexer or Transport IC.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 23                                   | TTXD                                                                         | I/O                                           | Teletext data stream from external demultiplexer or Transport IC synchronous to rising edge of CKREF signal average rate of 6.9375Mbit/s. Output in test mode only.                                                                                                                                                                                                                                                                                                                                         |

#### II - PIN INFORMATION (continued)

#### II.2 - Pin Description (continued)

| Pin | Name              | Туре | Function                                                                                                                                                                                                                                                                                         |

|-----|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24  | CKREF             | I    | Master clock reference signal. Its rising edge is the default reference for set-up and hold times of all inputs, and for propagation delay of all outputs (except for SDA output). CKREF nominal frequency is 27MHz (CCIR601): input pad with pull down (50kΩ Typ.)                              |

| 25  | RESET             | I    | Hardware reset, active LOW. It has priority over software reset. NRESET imposes default states (see Register Contents). Minimum Low level required duration is 5 CKREF periods : input pad with pull down (50kΩ Typ.)                                                                            |

| 26  | SCL               | I    | $\mbox{I}^2\mbox{C}$ bus clock line (internal 5-bit majority logic with CKREF for reference) : input pad with pull down (50k $\Omega$ Typ.)                                                                                                                                                      |

| 27  | SDA               | I/O  | I <sup>2</sup> C bus serial data line.<br>Input: internal 5-bit majority logic with CKREF for reference<br>Output: open drain                                                                                                                                                                    |

| 28  | VSYNC/<br>ODDEVEN | I/O  | Frame sync signal : - input in slave modes, except when sync is extracted from YCrCb data - output in master mode and when sync is extracted from YCrCb data - synchronous to rising edge of CKREF - ODDEVEN default polarity : odd (not-top) field : LOW level even (bottom) field : HIGH level |

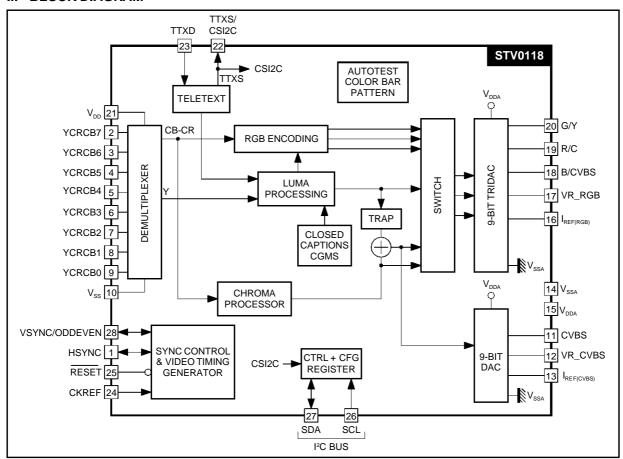

#### **III - BLOCK DIAGRAM**

#### **IV - FUNCTIONAL DESCRIPTION**

The STV0118 can operate either in master mode, where it supplies all sync signals, or in 6 slave modes, where it locks onto incoming sync signals.

The main functions are controlled by a micro-controller via an I<sup>2</sup>C 2-wire bus. Refer to the "User's Register Description" for an exhaustive list of the control possibilities available.

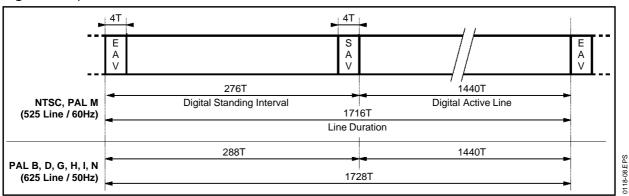

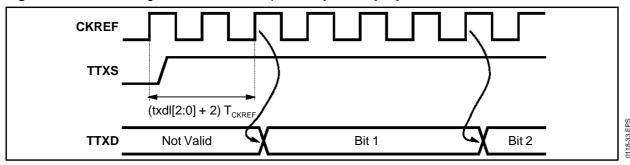

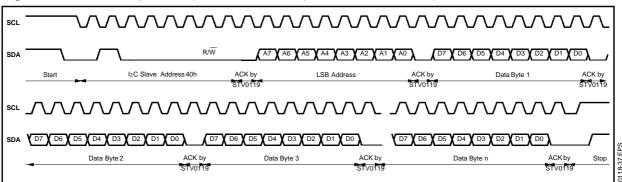

#### IV.1 - Data Input Format

The digital input is a time-multiplexed ITU-R656 /D1-type [Cb, Y, Cr, Y] 8-bit stream. Note that "ITU-R" was formerly known as "CCIR". Input samples are latched in on the rising edge (by default) of the clock signal CKREF, whose nominal frequency is 27MHz. Figure 1 illustrates the expected data input format. Alternatively, a 54-Mbit/s stream can be fed to the STV0118, refer to Section IV.17 ("dual encoding") for details.

The STV0118 is able to encode interlaced and non-interlaced video. One bit is sufficient to automatically direct the STV0118 to process non-interlaced video. Update is performed internally on the first frame sync active edge following the programing of this bit. The non-interlaced mode is a 624/2 = 312 line mode or a 524/2 = 262 line mode, where all fields are identical.

An 'autotest' mode is available by setting 3 bits (sync[2:0]) within the configurations register0. In this mode, a color bar pattern is produced, independently from video input, in the adequate standard. As this mode sets the STV0118 in master mode, VSYNC/ODDEV and HSYNC pins are then in output mode.

#### **IV.2 - Video Timing**

The STV0118 outputs interlaced or non-interlaced video in PAL-B, D, G, H, I, PAL-N, PAL-M or NTSC-M standards and 'NTSC- 4.43' is also possible.

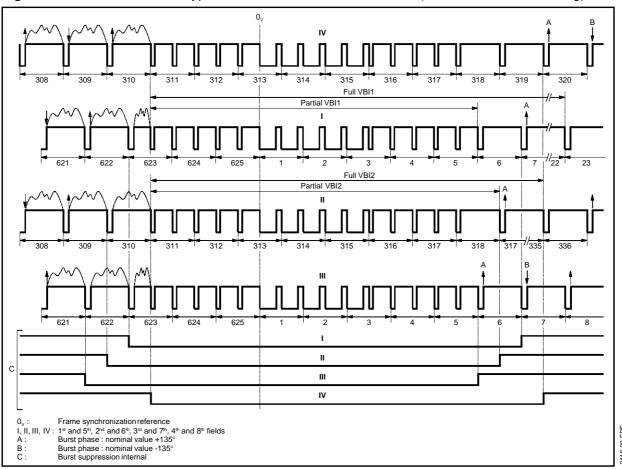

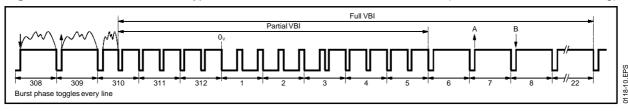

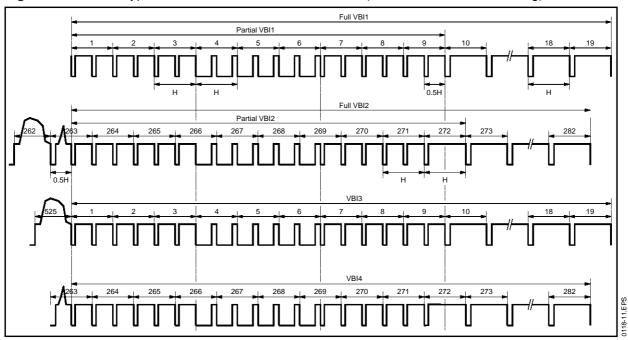

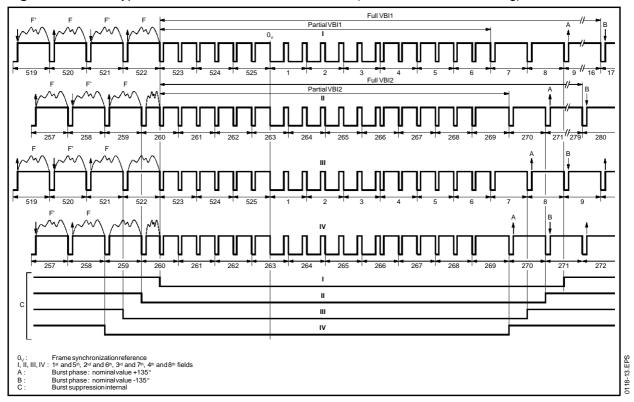

The 4-frame (for PAL) or 2 frame (for NTSC) burst sequences are internally generated, subcarrier generation being performed numerically with CKREF as reference. Rise and fall times of synchronization tips and burst enveloppe are internally controlled according to the relevant ITU-R and SMPTE recommendations.

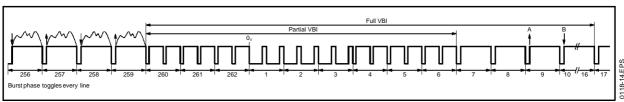

Figures 2 to 7 depict typical VBI waveforms.

It is possible to allow encoding of incoming YCrCb data on those lines of the VBI that do not bear line sync pulses or pre/post-equalisation pulses (see Figures 2 to 7). This mode of operation is refered to as "partial blanking" and is the default set-up. It

allows to keep in the encoded waveform any VBI data present in digitized form in the incoming YCrCb stream (e.g. WSS data, VPS, supplementary Closed-Captions line or StarSight data, etc.). Alternatively, the complete VBI may be blanked (no incoming YCrCb data encoded on these lines, "full blanking").

The complete VBI comprises of the following lines:

- for 525/60 systems (SMPTE line numbering convention): lines 1 to 19 and second half of line 263 to line 282.

- for 625/50 systems (CCIR line numbering convention): second half of line 623 to line 22 and lines 311 to 335.

The 'partial' VBI consists of:

- for 525/60 systems (SMPTE line numbering convention): lines 1 to 9 and second half of line 263 to line 272.

- for 625/50 systems (CCIR line numbering convention): second half of line 623 to line 5 and lines 311 to 318.

Full or partial blanking is controlled by configuration bit 'blkli in configuration register1'.

#### Note that:

- line 282 in 525/60/SMPTE systems is either fully blanked or fully active.

- line 23 in 625/60/CCIR systems is always fully active.

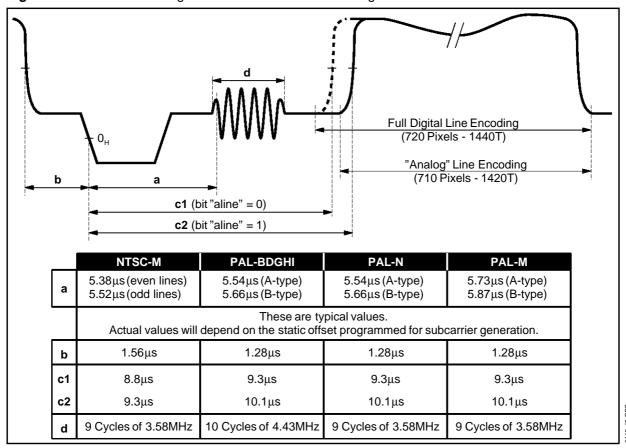

In an ITU-R656-compliant digital TV line, the active portion of the digital line is the portion included between the SAV (Start of Active Video) and EAV (End of Active Video) words. However, this digital active line starts somewhat earlier and may end slightly later than the active line usually defined by analog standards. The STV0118 allows two approaches:

- It is possible to encode the full digital line (720 pixels/1440 clock cycles). In this case, the output waveform will reflect the full YCrCb stream included between SAV and EAV.

- Alternatively, it is possible to drop some YCrCb samples at the extremities of the digital line so that the encoded analog line fits within the 'analog' ITU-R/SMPTE specifications.

Selection between these two modes of operation is performed with bit 'aline' in configuration register 4.

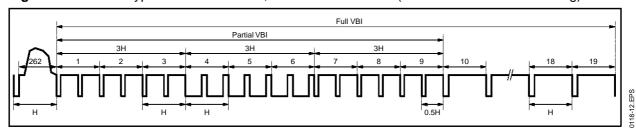

In all cases, the transitions between horizontal blanking and active video are shaped to avoid too steep edges within the active video. Figure 8 gives timings concerning the horizontal blanking interval and the active video interval.

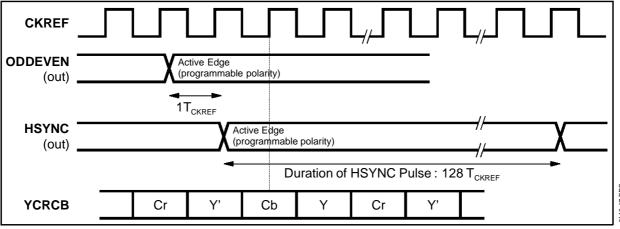

Figure 1: Input Data Format

Figure 2: PAL-BDGHI, PAL-N Typical VBI Waveform, Interlaced Mode (CCIR-625 Line Numbering)

Figure 3: PAL-BDGHI, PAL-N Typical VBI Waveform, Non-interlaced Mode ("CCIR-like" Line Numbering)

Figure 4: NTSC-M Typical VBI Waveforms, Interlaced Mode (SMPTE-525 Line Numbering)

Figure 5: NTSC-M Typical VBI Waveforms, Non-interlaced Mode ("SMPTE-like" Line Numbering)

Figure 6: PAL-M Typical VBI Waveforms, Interlaced Mode (CCIR-525 Line Numbering)

Figure 7: PAL-M Typical VBI Waveforms, Non-interlaced Mode ("CCIR-like" Line Numbering)

Figure 8: Horizontal Blanking Interval and Active Video Timings

#### **IV.3 - Reset Procedure**

Ahardware reset is performed by grounding the pin NRESET. The master clock must be running and pin NRESET kept low for a minimum of 5 clock cycles. This sets the STV0118 in HSYNC+ODDEV (line-locked) slave mode, for NTSC-M, interlaced ITU-R601 encoding. Closed-captioning and Teletext encoding are all disabled.

Then the configuration can be customized by writing into the appropriate registers. A few registers

are never reset, their contents is unknown until the first loading (refer to the Register Contents and Description).

It is also possible to perform a software reset by setting bit'softreset' in Reg 6. The IC's response in that case is similar to its response after a hardware reset, except that Configuration Registers (Reg 0 to 6) and a few other registers (see description of bit 'softreset') are not altered.

#### IV.4 - Master Mode

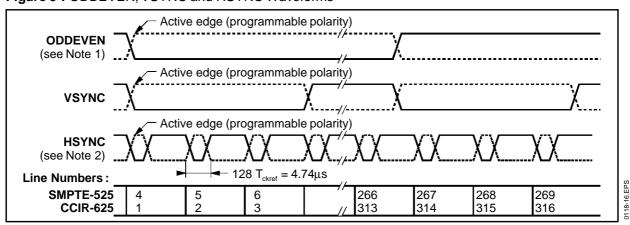

In this mode, the STV0118 supplies HSYNC and ODDEV sync signals (with independentlyprogrammable polarities) to drive other blocks. Refer to Figure 9 and 10 for timings and waveforms.

The STV0118 starts encoding and counting clock

cycles as soon as the master mode has been loaded into the control register (Reg.0).

Configuration bits "Syncout\_ad[1:0]" (Reg4) allow to shift the relative position of the sync signals by up to 3 clock cycles to cope with any YCrCb phasing.

Figure 9: ODDEVEN, VSYNC and HSYNC Waveforms

Notes: 1. When ODDEVEN is a sync input, only one edge ("the active edge") of the incoming ODDEVEN is taken into account for synchronization. The "non-active" edge (2nd edge on this drawing) is not critical and its position may differ by H/2 from the location shown.

2. The HSYNC pulse width indicated is valid when the STV0118 supplies HSYNC. In those slave modes where it receives HSYNC, only the edge defined as active is relevant, and the width of the HSYNC pulse it receives is not critical.

Figure 10: Master Mode Sync Signals

**Note:** 1. This figure is valid for bits "syncout\_ad[10]" = default.

#### IV.5 - Slave Modes

Six slave modes are available: ODDEV+HSYNC based (line-based sync), VSYNC+HSYNC based (another type of line-based sync), ODDEV-only based (frame-based sync), VSYNC-only based (another type of frame-based sync), or sync-indata based (line locked or frame locked).

ODDEV refers to an odd/even (also known as not-top/bottom) field flag, HSYNC is a line sync signal, VSYNC is a vertical sync signal. Their waveforms are depicted in Figure 9. The polarities of HSYNC and VSYNC/ODDEV are independently programmable in all slave modes.

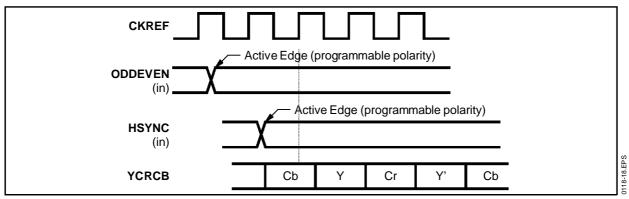

# IV.5.1 - Synchronization onto a Line Sync Signal IV.5.1.1 - HSYNC+ODDEV Based Synchronization

Synchronization is performed on a line-by-line basis by locking onto incoming ODDEV and HSYNC signals. Refer to Figure 11 for waveforms and timings. The polarities of the active edges of HSYNC and ODDEV are programmable and independent.

The first active edge of ODDEV initializes the internal line counter but encoding of the first line does not start until an HSYNC active edge is detected (at the earliest, HSYNC may transition at the same time as ODDEV). At that point, the internal sample counter is initialized and encoding of the first line starts. Then, encoding of each subsequent line is individually triggered by HSYNC active edges. The phase relationship between HSYNC and the incoming YCrCB data is normally such that the first clock rising edge following the HSYNC active edge samples "Cb" (i.e. a 'blue' chroma sample within the YCrCb stream). It is however possible to internally delay the incoming sync signals (HSYNC+ODDEV) by up to 3 clock cycles to cope with different data/sync phasings, using configuration bits "Syncin ad" (Reg. 4).

The STV0118 is thus fully slaved to the HSYNC signal, which means that lines may contain more or less samples than typical 525/625 system requirement.

If the digital line is shorter than its nominal value: the sample counter is re-initialized when the 'early' HSYNC arrives and all internal synchronization signals are re-initialized.

If the digital line is longer than its nominal value: the sample counter is stopped when it reaches its nominal end-of-line value and waits for the 'late' HSYNC before reinitializing.

The field counter is incremented on each ODDEV transition. The line counter is reset on the HSYNC following each active edge of ODDEV.

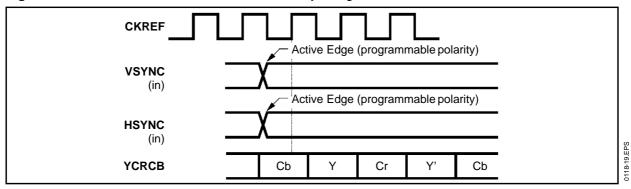

#### IV.5.1.2- HSYNC+VSYNC Based Synchronization

Synchronization is performed on a line-by-line basis by locking onto incoming VSYNC and HSYNC signals. Refer to Figure 12 for waveforms and timings. The polarities of HSYNC and VSYNC are programmable and independent.

The incoming VSYNC signal is immediately transformed into a waveform identical to the odd/even waveform of an ODDEV signal, therefore the behavior of the core is identical to that described above for ODDEV+HSYNC based synchronization. Again, the phase relationship between HSYNC and the incoming YCrCb data is normally such that the first clock rising edge following the HSYNC active edge samples "Cb" (i.e. a 'blue' chroma sample within the YCrCb stream). It is however possible to internally delay the incoming sync signals (HSYNC+VSYNC) by up to 3 clock cycles to cope with different data/sync phasings, using configuration bits "Syncin\_ad" (Reg. 4).

The field counter is incremented on each active edge of VSYNC.

Figure 11: HSYNC + ODDEVEN Based Slave Mode Sync Signals

Note: 1. This figure is valid for bits "syncin\_ad[1:0]" = default.

12/42

Figure 12: HSYNC + VSYNC Based Slave Mode Sync Signals

This figure is valid for bits "syncin\_ad[1:0]" = default.

The active edges of HSYNC and VSYNC should normally be simultaneous. It is permissible that HSYNC transitions before VSYNC, but VSYNC must not transition before HSYNC.

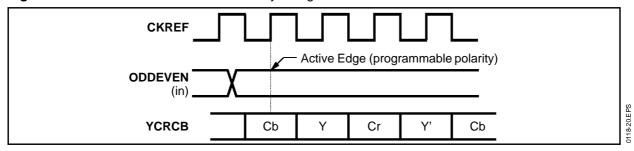

Figure 13: ODDEVEN Based Slave Mode Sync Signals

Note: 1. This figure is valid for bits "syncin\_ad[1:0]" = default.

#### IV.5.2 - Synchronization onto a Frame Sync Signal IV.5.2.1 - ODDEV-only Based Synchronization

Synchronization is performed on a frame-by-frame basis by locking onto an incoming ODDEV signal. A line sync signal is derived internally and is also output as HSYNC. Refer to Figure 13 for waveforms and timings. The phase relationship between ODDEV and the incoming YCrCB data is normally such that the first clock rising edge following the ODDEV active edge samples "Cb" (i.e. a 'blue' chroma sample within the YCrCb stream). It is however possible to internally delay the incoming ODDEV signal by up to 3 clock cycles to cope with different data/sync phasings, using configuration bits "Syncin\_ad" (Reg. 4).

The first active edge of ODDEV triggers generation of the analog sync signals and encoding of the incoming video data. Frames being supposed to be of constant duration, the next ODDEV active transition is expected at a precise time after the last ODDEV detected.

So, once an active ODDEV edge has been detected, checks that the following ODDEV are present at the expected instants are performed.

Encoding and analog sync generation carry on unless three successive fails of these checks occur.

In that case, three behaviors are possible, according to the configuration programmed (Reg. 1-2):

- if 'free-run' is enabled, the STV0118 carries on outputting the digital line sync HSYNC and generating analog video just as though the expected ODDEV edge had been present. However, it will re-synchronize onto the next ODDEV active edge detected, whatever its location.

- if 'free-run' is disabled but bit 'sync\_ok' is set in configuration register1, the STV0118 sets the active portion of the TV line to black level but carries on outputting the analog sync tips (on Ys and CVBS) and the digital line sync signal HSYNC.

- if 'free-run' is disabled and the bit 'sync\_ok' is not set, all analog video is at black level and neither analog sync tips nor digital line sync are output.

Note that this mode is a frame-based sync mode, as opposed to a field-based sync mode, that is, only one type of edge (rising or falling, according to bit 'polv'in Reg 0) is of interest to the STV0118, the other one is ignored.

#### IV.5.2.2 - VSYNC only Based Synchronization

Synchronization is performed on a frame-by-frame basis by locking onto an incoming VSYNC signal. An auxiliary line sync signal HSYNC must also be fed to the STV0118, which uses it to reconstruct from VSYNC and HSYNC information an internal odd/even waveform identical to that of an ODD-EVEN signal. Therefore the behavior of the core is identical to that described above for ODDEVEN only basedsynchronization(except that nothing is output on HSYNC pin since it is an input port in that mode). Note that HSYNC is an input but has no other use than allowing the STV0118 to decide whether an incoming VSYNC pulse flags an odd or an even field. In other words, the STV0118 does not lock onto HSYNC in this mode since this is NOT a line-locked mode.

The phase relationship between VSYNC and the incoming YCrCb data is normally such that the first clock rising edge following the VSYNC active edge samples "Cb" (i.e. a 'blue' chroma sample within the YCrCb stream). It is however possible to internally delay the incoming sync signals (VSYNC+HSYNC) by up to 3 clock cycles to cope with different data/sync phasings, using configuration bits "Syncin\_ad" (Reg. 4).

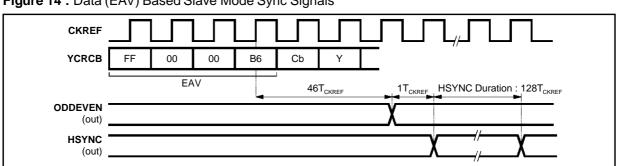

#### IV.5.3 - Synchronization onto Data-embedded Sync Words

# IV.5.3.1 - 'End-of-frame' Word Based Synchronization

Synchronization is performed by extracting the 1-to-0 transitions of the 'F' flag (end-of-frame) from the 'EAV' (End-of-Active Video) sequence embedded within ITU-R656 / D1 compliant digital video streams. Both a frame sync signal and a line sync signal are derived and are made available externally as ODDEVEN and HSYNC (see Figure 14). The first successful detection of the 'F' flag triggers generation of the analog sync signals and encoding of the incoming video data. Frames being supposed to be of constant duration, the next EAV word containing the 'F' flag is expected at a precise

time after the latest detection.

So, once an active 'F' flag has been detected, checks that the following flags are present within the incoming video stream at the expected times are performed.

Encoding and analog sync generation carry on unless three successive fails of these checks occur.

In that case, three behaviors are possible, according to the configuration programmed:

- if 'free-run' is enabled, the STV0118 carries on generating the digital frame and line syncs (ODD-EVEN and HSYNC) and generating analog video just as though the expected 'F' flag had been present. However, it will re-synchronize onto the next 'F' flag detected within the incoming CCIR656/D1 video stream.

- if 'free-run' is disabled but the bit 'sync\_ok' is set in the configuration registers, the STV0118 sets the active portion of the TV line to black level but carries on outputtingthe analog synctips (on Ys and CVBS) and the digital frame and line syncsignals ODDEVEN and HSYNC.

- if 'free-run' is disabled and the bit 'sync\_ok' is not set, all analog video is at black level and neither analog synctips nor digital frame/line sync are output.

The SAV and EAV words are Hamming-decoded. After detection of two successive errors, a bit is set in the status register to inform the micro-controller of the poor transmission quality.

# IV.5.3.2 - 'End-of-line' Word Based Synchronization

Synchronization is performed by extracting the 'F' and 'H' flags from the 'SAV' (Start of Active Video) and 'EAV' (End of Active Video) words embedded within ITU-R656/D1 compliant digital video streams. Aline sync signal and a frame sync signal are derived internally from these flags and are output on the HSYNC and ODDEVEN/VSYNC pins in output mode. These signals are also exploited by the core of the circuit which treats them like it treats incoming ODDEVEN and HSYNC signals in HSYNC+ODDEV based synchronization (see Section IV.5.1.1).

Figure 14: Data (EAV) Based Slave Mode Sync Signals

#### IV.6 - Input Demultiplexer

The incoming 27Mbit/s YCrCb data is demultiplexed into a 'blue-difference' chroma information stream, a 'red-difference' chroma information stream and a luma information stream. Incoming data bits are treated as blue, red or luma samples according to their relative position with respect to the sync signals in use and to the content of configuration bits "Syncin\_ad" (slave modes) or "Syncout\_ad" (master mode).

The ITU-R601 recommendation defines the black luma level as Y = 16dec and the maximum white luma level as Y = 235dec. Similarly it defines 225 quantization levels for the color difference components (Cr, Cb), centered around 128.

Accordingly, incoming YCrCB samples can be saturated in the input multiplexer with the following rules:

- for Cr or Cb samples :

- Cr, Cb > 240  $\Rightarrow$  Cr, Cb saturated at 240 Cr, Cb < 16  $\Rightarrow$  Cr, Cb saturated at 16

- for Y samples:

- $Y > 235 \Rightarrow Y$  saturated at 235

$Y < 16 \Rightarrow Y$  saturated at 16

This avoids having to heavily saturate the composite video codes before digital-to-analog conversion in case erroneous or unrealistic YCrCb samples are input to the encoder (there may otherwise be overflow errors in the codes driving the DACs), and therefore avoids genera-ting a distorded output waveform.

However, in some applications, it may be desirable to let 'extreme' YCrCb codes pass through the demultiplexer. This is also possible, provided that bit "maxdyn" is set in configuation register 6.

In this case, only codes 00hex and FFhex are overridden: if such codes are found in the active video samples, they are forced to 01hex and FEhex.

In any case, the YCrCb codes are not overridden for EAV/SAV decoding

The demultiplexer is also able to handle 54Mbit/s

YCrCb streams for dual encoding applications. Refer to Section IV.17, "Dual Encoding Application - 54Mbit/s YCrCB interface".

#### IV.7 - Sub-carrier Generation

A Direct Digital Frequency Synthesizer (DDFS) using a 24-bit phase accumulator, generates the required color sub-carrier frequency. This oscillator feeds a quadrature modulator which modulates the baseband chrominance components.

The sub-carrier frequency is obtained from the following equation:

Fsc = (24-bit Increment Word / 2<sup>24</sup>) x CKREF

Hard-wired Increment Word values are available for each standard (except for 'NTSC-4.43') and can be automatically selected. Alternatively (according to bit 'selrst' in Reg. 2.), the frequency can be fully customized by programming other values into a dedicated Increment Word Register (Reg. 10-11-12). This allows for instance to encode "NTSC-4.43" or "PAL-M-4.43".

This is done with the following procedure:

- Program the required increment in Registers 10 to 12

- Set bit 'selrst' to '1' in Configuration Register 2

- Perform a software reset (Reg. 6).

Caution: this sets back all bits from Reg. 7 onwards to their default value, when they can be

**Warning:** if a standard change occurs after the software reset, the increment value is automatically re-initialized with the hardwired or loaded value according to bit selrst.

The reset phase of the color sub-carrier can also be software-controlled (Reg. 13-14).

The sub-carrier phase can be periodically reset to its nominal value to compensate for any drift introduced by the finite accuracy of the calculations. Sub-carrier phase adjustment can be performed every line, every eight field, every four field, or every two field (Register 2 bits valrst[1:0]).

#### **IV.8 - Burst Insertion**

The color reference burst is inserted so as to always start with a positive zero crossing of the subcarrier sine wave. The first and last half-cycles have a reduced amplitude so that the burst envelope starts and ends smoothly.

The burst contains 9 or 10 sine cycles of 4.43361875MHzor3.579545MHzaccording to the standard programmed in the Control Register (Reg. 0, bits std[1:0]), as follows:

- NTSC-M 9 cycles of 3.579542MHz - PAL-BDGHI 10 cycles of 4.43361875MHz - PAL-M 9 cycles of 3.57561149MHz - PAL-N 9 cycles of 3.5820558MHz

It is possible to turn the burst off (no burst insertion) by setting configuration bit 'bursten' to 0 (register 2).

Notes: - Two strategies exist for burst insertion: one is to merely gate and shape the subcarrier for burst insertion, the other is more elaborated and is to always start the burst with a positive-going zero crossing. In the first case the phase of the subcarrier when the burst starts is not controlled, with the consequence that some of its first and last cycles are more heavily distorded. The second solution guarantees smooth start and end of burst with a maximum of undistorded burst cycles and can only be beneficial to chroma decoders, it is the solution implemented in the STV0118.

- While the first option gave constant burst start time but uncontrolled initial burst phase, the second solution guarantees start on a positive-going zero crossing with the consequence that two burst start locations are visible over successive lines, according to the line parity. This is normal and explained below.

- In NTSC, the relation between subcarrier frequency and line length creates a 1800 subcarrier phase difference (with respect to the horizontal sync) from one line to the next according to the line parity. So if the burst always starts with the same phase (positive-going zero crossing), this means the burst will be inserted at time X or at time X+T<sub>NTSC</sub>/2 after the horizontal sync tip according to the line parity, where T<sub>NTSC</sub> is the duration of one cycle of the NTSC burst.

- With PAL, a similar rationale holds, and again there will be two possible burst start locations. The subcarrier phase difference (with respect to the horizontal sync) from one line to the next in that case is either 0 or 1800 with the following series: A-A-B-B-A-A-..-etc. where A denotes 'A-type' bursts and B denotes 'B-type' bursts, A-type and B-type being 180° out of phase with respect to the horizontal sync. So 2 locations are possible, one for A-type, the other for B-type (see Figure 8).

- This assumes a periodic reset of the subcarrier is automatically performed (see bits valrst[1:0] in Reg 2). Otherwise, over several frames, the start of burst will drift within an interval of one a subcarrier's cycle. THIS IS NORMAL and means the burst is correctly locked to the colors encoded. The equivalent effect with a gated burst approach would be the following: the start location would be fixed but the phase with which the burst starts (with respect to the horizontal sync) would be drifting.

#### IV.9 - Luminance Encoding

The demultiplexed Y samples are band-limited and interpolated at CKREF clock rate. The resulting luminance signal is properly scaled before insertion of any Closed-captions, CGMS or Teletext data and synchronization pulses.

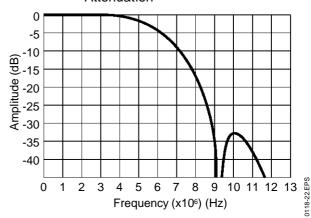

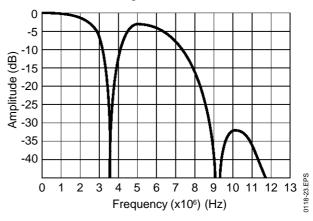

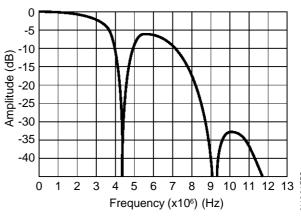

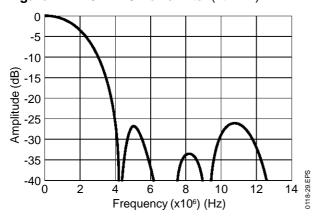

The interpolation filter compensates for the  $\sin(x)/x$  attenuation inherent to D/A conversion and greatly simplifies the output stage filter (refer to Figures 15 to 17 for characteristic curves).

**Figure 15:** Luma Filtering Including DAC Attenuation

**Figure 16:** Luma Filtering with 3.58MHz Trap, Including DAC Attenuation

**Figure 17:** Luma Filtering with 4.43MHz Trap, Including DAC Attenuation

In addition, the luminance that is added to the chrominance to create the composite CVBS signal can be trap-filtered at 3.58MHz (NTSC) or 4.43MHz (PAL). This allows to cope with application oriented towards low-end TV sets which are subject to cross-color if the digital source has a wide luminance bandwidth (e.g. some DVD sources). Note that the trap filter does not affect the S-VHS luminance output nor the RGB outputs.

A 7.5 IRE pedestal can be programmed if needed with all standards (see Reg1, bit setup). This allows in particular to encode Argentinian and non-Argentinian PAL-N, or Japanese NTSC (NTSC with no set-up).

A programmable delay can be inserted on the luminance path to compensate any chroma/luma delay introduced by off-chip filtering (chroma and luma transitions being coincident at the DAC output with default delay) (Reg3, bits del[2:0]).

#### IV.10 - Chrominance Encoding

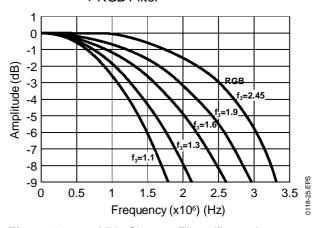

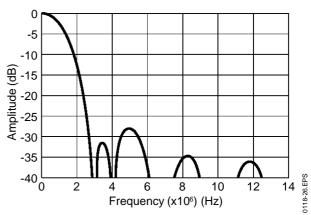

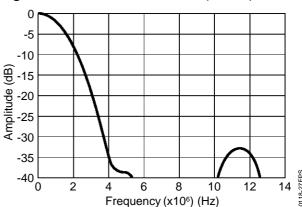

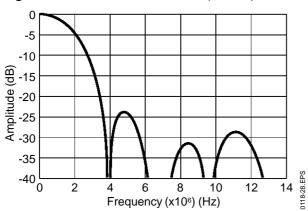

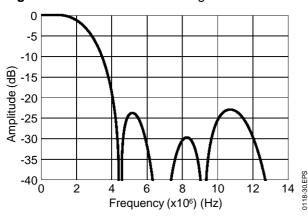

U and V chroma components are computed from demultiplexed Cb, Cr samples. Before modulating the subcarrier, these are band-limited and interpolated at CKREF clock rate. This processing eases the filtering following D/A conversion and allows a more accurate encoding. A set of 4 different filters is available for chroma filtering to fit a wide variety of applications in the different standards and include filters recommended by ITU-R Rec624-4 and SMPTE170-M. The available 3dB bandwidths are 1.1, 1.3, 1.6 or 1.9MHz, refer to Figures 18 to 22 for the various frequency responses (Reg1, bits flt[1:0]).

The narrower bandwidths are useful against crossluminance artefacts, the wider bandwidths allow to keep higher chroma contents and then an improved image quality.

#### IV.11 - Composite Video Signal Generation

The composite video signal is created by adding the luminance (after optional trap filtering, Reg 3 bits entrap and trap\_pal) and the chrominance components. A saturation function is included in the adder to avoid overflow errors should extreme luminance levels be modulated with highly saturated colors (this does not correspond to natural colors but may be generated by computers or graphic engines).

A 'color killing' function is available (Reg 1, bit coki) whereby the composite signal contains no chrominance, i.e. replicates the trap-filtered luminance.

Note that this function does not suppress the chrominance on the S-VHS outputs (nevertheless suppressing the S-VHS chrominance is possible using bit "bkg\_c" in Reg 5).

Figure 18: Various Chroma Filters Available + RGB Filter

Figure 19: 1.1MHz Chroma Filter (flt = 00)

Figure 20: 1.3MHz Chroma Filter (flt = 01)

Figure 21: 1.6MHz Chroma Filter (flt = 10)

Figure 22: 1.9MHz Chroma Filter (flt = 11)

#### IV.12 - RGB Encoding

After demultiplexing, the Cr and Cb samples feed a 4 times interpolation filter. The resulting baseband chroma signal has a 2.45MHz bandwidth (Figure 23) and is combined with the filtered luma component to generate R, G, B samples at 27MHz.

Figure 23: RGB Chroma Filtering

#### IV.13 - Closed Captioning

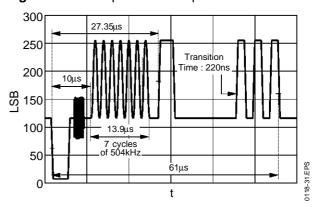

Closed-captions (or data from an Extended Data Service as defined by the Closed-Captions specification) can be encoded by the circuit. The closed caption data is delivered to the circuit through the I<sup>2</sup>C interface. Two dedicated pairs of bytes (two bytes per field), each pair preceded by a clock run-in and a start bit can be encoded and inserted on the luminance path on a selected TV line. The Clock Run-In and Start code are generated by the STV0118.

Closed-caption data registers are double-buffered so that loading can be performed anytime, even during line 21/284 or any other selected line.

User register 39 (resp. 41) contains the first byte to send (LSB first) after the start bit on the appropriate TV line in field 1 (resp. field 2), and user register 40 (resp. 42) contains the second byte to send. The TV line number where data is to be encoded is programmble (Reg. 37, 38). Lines that may be selected include those used by the StarSight data broadcast system. Closed-captions data has priority over CGMS programmed for the same line.

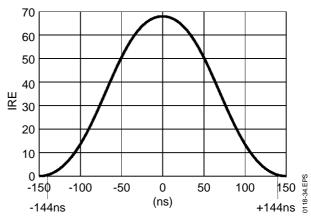

The internal Clock Run-In generator is based on a Direct Digital Frequency Synthesizer. The nominal instantaneous data rate is 503.5kbit/s(i.e. 32 times the NTSC line rate). Data LOW corresponds nominally to 0 IRE, data HIGH corresponds to 50 IRE at the DAC outputs. Refer to Figure 24.

When closed-captioning is on (bits cc1/cc2 in Reg.1), the CPU should load the relevant registers (reg. 39 and 40, or 41 and 42) once every frame at most (although there is in fact some margin due to the double-buffering). Two bits are set in the status register in case of attempts to load the closed-caption data registers too frequently, these can be used to regulate loading rate.

Figure 24: Example Closed-caption Waveform

18/42

The closed caption encoder considers that closed caption data has been loaded and is valid on completion of the write operation into register 40 for field 1, into register 42 for field 2. If closed caption encoding has been enabled and no new data bytes have been written into the closed caption data registers when the closed caption window starts on the appropriate TV line, then the circuit outputs two US-ASCII NULL characters with odd parity after the start bit.

#### IV.14 - CGMS Encoding

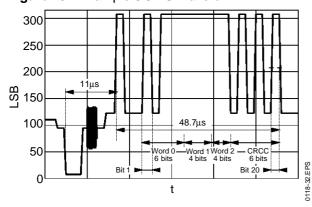

CGMS (Copy Generation Management System - also known as VBID and described by standard CPX-1204 of EIAJ) data can be encoded by the circuit. Three bytes (20 significant bits) are delivered to the chip via the I2C interface. Two reference bits ('1' then '0') are encoded first, followed by 20 bits of CGMS data (including a Cyclic Redundancy Check sequence, not computed by the device and supplied to it as part of the 20 data bits). The reference bits are generated locally by the STV0118. Refer to Figure 25 for a typical CGMS waveform.

When CGMS encoding is enabled, the CGMS (see bit encgms in Reg 3) waveform is continously present once in each field, on lines 20 and 283 (SMPTE-525 line numbering).

The CGMS data register is double-buffered, which means that it can be loaded anytime (even during line 20/283) without any risk of corrupting CGMS data that could be in the process of being encoded. The CGMS encoder considers that new CGMS data has been loaded and is valid on completion of the write operation into register 33

Figure 25: Example CGMS Waveform

#### IV.15 - Teletext Encoding

The STV0118 is able to encode Teletext according to the "CCIR/ITU-R Broadcast Teletext System B" specification, also known as "World System Teletext".

In DVB applications, Teletext data is embedded within DVB streams as MPEG data packets. It is the responsibility of a "Transport Layer Processing" IC (or demultiplexer), like SGS-Thomson's ST20-based "TP2", to sort out incoming data packets and inparticular to store Teletextpacket in a buffer, which then passes them to the STV0118 on request.

#### IV.15.1 - Signals Exchanged

The STV0118 and the Teletext buffer exchange 2 signals: TTXS (Teletext Synchronization) going from the STV0118 to the Teletext Buffer and TTXD (Teletext Data) going from the Teletext Buffer to the STV0118.

The TTXS signal is a request signal generated on selected lines. In response to this signal, the Teletext buffer is expected to send 360 Teletext bits to the STV0118 for insertion of a Teletext line into the analog video signal.

The duration of the TTXS window is 1402 reference clock periods (51.926 $\mu$ s), which corresponds to the duration of 360 Teletext bits (see Transmission Protocol below).

Following the TTXS rising edge the encoder expects data from the Teletext buffer after a programmable number (2 to 9) of 27MHz master clock periods. Data is transmitted synchronously with the master clock at an average rate of 6.9375Mbit/s according to the protocol described below. It consists, in order of transmission, of 16 Clock Run-In bits, 8 Framing Code bits and the 336 bits (42 bytes) that represent one Teletext packet.

#### IV.15.2 - Transmission Protocol

In order to transmit the Teletext data bits at an average rate of 6.9375Mbit/s, which is about 1/3.89 times the master clock frequency, the following scheme is adopted:

The 360-bit packet is regarded as nine 37-bit sequences plus one 27-bit sequence. In every sequence, each Teletext data bit is transmitted as a succession of 4 identical samples at 27 Msample/s, except for the 10th, 19th, 28th and 37th bits of the sequence which are transmitted as a succession of 3 identical samples. This protocol is compatible with SGS-Thomson's ST-20 based Tranport Layer IC ("TP2").

Figure 26: "TTXS Rising" to "First Valid Sample" Delay for txdl[2:0] = 0

# IV.15.3 - Programming IV.15.3.1 - 'TTXS Rising' to 'First Valid Sample' Delay Programming

The encoder expects the Teletext buffer to clock out the first Teletext data sample on the (2+N)th rising edge of the master clock following the rising edge of TTXS (Figure 26 depicts this graphically for N=0). 'N' is programmable from 0 to 7 (i.e. overall delay is programmable from TWO to NINE 27MHz cycles) via 3 dedicated bits located in the Configuration Register4: "txdl[2:0]".

#### IV.15.3.2 - Teletext Line Selection

Five dedicated registers allow to program Teletext encoding in various areas of the Vertical Blanking Interval (VBI) of each field. A total of 4 such areas (i.e. blocks of contiguous Teletext lines) can independently be defined within the two VBIs of one frame (e.g. 2 blocks in each VBI, or 3 blocks in field1 VBI and one in field2 VBI, etc.). Further, under certain circumstances, it is possible to define up to 4 areas in each VBI.

Programming is performed using 4 "Teletext Block Definition" registers (TTXBD1, TTXBD2, TTXBD3,TTXBD4) and a "Teletext Block Mapping" register (TTXBM). Refer to the description of user registers 34 to 38 for details.

#### IV.15.4 - Teletext Pulse Shape

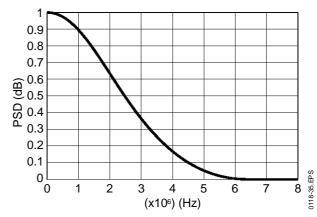

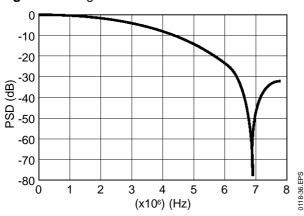

The shape and amplitude of a single Teletext pulse are depicted in Figure 27, its relative power spectral density is given in Figures 28 and 29 and is substantially zero at frequencies above 5MHz, as re-

quired by the World System Teletext specification.

Figure 27: Shape and Amplitude of a Single Teletext Symbol

Figure 28: Linear PSD Scale

Figure 29: Logarithmic PSD Scale

#### IV.16 - I<sup>2</sup>C Bus

An external micro-controller controls the STV0118 via an  $I^2C$  bus by writing into or reading from internal registers. The  $I^2C$  interface supports the "fast  $I^2C$  protocol" (up to 400kHz- and potentially more).

The default I<sup>2</sup>C addresses of the STV0118 are:

- in write mode: "01000000" (40 hex)

- in read mode: "01000001" (41 hex)

After a hardware reset, it is these addresses that the STV0118 recognizes.

It is possible to modify the default I<sup>2</sup>C address by tiing the TTXS/CSI2C pin to logic '1' and validating the change by writing into a dedicated bit in Register 6.

In that case, the STV0118 has a new I<sup>2</sup>C address:

- in write mode: "01000010" (42 hex)

- in read mode: "01000011"(43 hex)

Once the I<sup>2</sup>C address has been changed, it cannot be modifed anymore until the next hardware reset.

Note that these I<sup>2</sup>C addresses are the same as those used by the STV0117/STV0117A/STV0119 (others SGS-THOMSON PAL/NTSC Digital Encoder).

It is expected that I<sup>2</sup>C address changes will normally be needed for dual encoding applications. The exact procedure to change the I<sup>2</sup>C addresses is detailed below, in the section that deals with dual encoding applications.

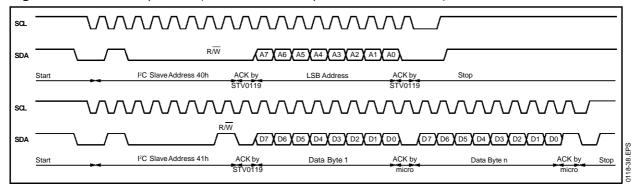

Write and read operations are described in Figures 30 and 31.

Figure 30 : I<sup>2</sup>C Write Operation (default address at power-on, CSI2C ≠ '1')

Figure 31 : 1<sup>2</sup>C Read Operation (default address at power-on, CSI2C ≠ '1')

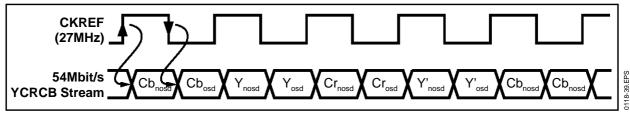

#### IV.17 - Dual Encoding Application with 54Mbit/s YCrCb Interface

The STV0118 is able to interface with SGS-THOMSON's MPEG decoders capable of supplying a 54-Mbit/s YCrCB multiplex, like the STi3520M. This multiplex embeds two 27Mbit/s YCrCb video streams, one with OSD contents and the other without OSD content (see Figure 32). Note that the frequency of the reference clock supplied to the encoder is still 27MHz, only both edges are used in the interface.

The MPEG decoder being usually slaved to the encoder, if two encoders are to be used in parallel, one of them must be master and the other must be slave. Figure 33 shows a typical dual encoding application (although other applications where two STV0118's are slave are possible).

It is also necessary to be able to control independently the encoders. One solution is to have two separate I<sup>2</sup>C busses (one for each encoder) running from the microcontroller (this is possible on SGS-THOMSON's ST20, which features two I<sup>2</sup>C busses), another solution is to change the I<sup>2</sup>C chip address of one of the STV0118.

This can be done with the following procedure:

- If no Teletext is required, tie pin TTXS/ CSI2C of

the 1st encoder to '0'.

- If Teletext encoding is needed, connect the TTXS/CSI2C pin of the first encoder to both the TTXS input pin of the Teletext Buffer / Transport IC (e.g. SGS-Thomson's TP2) and a pull-down resistor (needed for power-on configuration).

- Connect TTXS/CSI2C of the second encoder to logic '1'.

- Before performing any Teletext-related programming, set to '1' bit "chgi2c" in configuration register 6.

On hardware reset, both encoders have the same default  $I^2C$  address (40-41hex). When bit "chgi2c" toggles to '1', the  $I^2C$  address of the first encoder (with TTXS/CSI2C pulled low) keeps unchanged at 40-41hex, whilst the  $I^2C$  address of the second encoder (with TTXS/CSI2C = '1') switches to 42-43hex and can no more be changed until the next hardware reset.

After I<sup>2</sup>C address change, the second encoder must be programmed to choose the YCRCb incoming data stream on the falling edge of CKREF (see bit 'nosd' in configuration register 3).

Figure 32: 54Mbit/s Dual YCRCB Stream

Figure 33: Typical Dual Encoding Application

#### IV.18 - Line Skip / Line Insert Capability

This patented feature of the STV0118 offers the possibility to cut the cost of the application by suppressing the need for a VCXO.

Ideally, the master clock used on the application board and fed to the MPEG decoding IC would have exactly same frequency as the clock that was used when the MPEG data was encoded. Obviously this is not realistic; up to now a solution commonly chosen is to dynamically adjust the clock on the board as close to the 'ideal' clock as possible with the help of time stamps embedded within the MPEG stream. Such a kind of tracking often involves the use of a VCXO: when the MPEG data bufferfills up to more than some threshold the clock frequency is increased, when it empties down to some other threshold the clock frequency is lowered.

The STV0118 offers an alternative, cost-saving solution: by programming the two bits jump and dec\_ninc in configuration Reg6, the STV0118 is able to reduce or increase the length of some frames in a way that will not introduce visible artefacts (even if comb-filtering is used). These bits should be set according to the level of the MPEG data buffer. Refer to Section VI.2 Register 6, Register 9 and Registers 21-22-23 for complete bit description.

Operation with the STV0118 as sync master is as follows:

- If the MPEG data buffers fills up too much: set bit "jump" to '1' and bit "dec\_ninc" to '1'. The STV0118 will reduce the length of the current frame (Bit "jump" will then automatically be reset to '0').

- If the MPEG data buffers empties too much: set bit "jump" to '1' and bit "dec\_ninc" to '0'. The STV0118 will increase the length of the current frame (Bit "jump" will then automatically be reset to '0').

These operations can be repeated until the MPEG data buffer is inside its fixed limits.

It is also possible to use the line skip/repeat capability in non-interlaced mode.

This functionality of the STV0118 is also available in slave mode, in this case the sync signals supplied to the STV0118 must be in accordance with the modified frame lengthes programmed.

#### IV.19 - CVBS, S-VHS and RGB Analog Outputs

Four out of six video signals (composite CVBS, S-VHS (Y/C) and RGB) can be directed to 4 analog output pins through 9-bit D/A converters operating at the reference clock frequency.

The available combinations (see bit 'rgb\_nyc' in Reg5) are:

S-VHS (Y/C) + CVBS + CVBS1 or : R, G, B + CVBS1.

A single external analog power supply pair is used for all DACs, but two independent pairs of current and voltage references are needed. Each current reference pin is normally connected externally to a resistor tied to the analogue ground, whilst each voltage reference pin is normally connected to a capacitance tied to the analogue ground.

The internal current sources are independent from the positive supply, thanks to a bangap, and the consumption of the DACs is constant whatever the codes converted.

Any unused DAC may be independently disabled by software, in which case its output is at 'neutral' level (blanking for luma and composite outputs, no color for chroma output, black for RGB outputs). For applications where a single CVBS output is required, the RGB/CVBS+S-VHS Triple DAC should be disabled and Pins IREF(RGB), VR\_RGB tied to analog power supply.

#### **V-CHARACTERISTICS**

#### V.1 - Absolute Maximum Ratings

| Symbol            | Parameter                      | Value                       | Unit |

|-------------------|--------------------------------|-----------------------------|------|

| $V_{DDx}$         | DC Supply Voltage              | -0.3, 4.0                   | V    |

| V <sub>IN</sub>   | Digital Input Voltage          | -0.3, V <sub>DD</sub> + 0.3 | V    |

| V <sub>OUT</sub>  | Digital Output Voltage         | -0.3, V <sub>DD</sub> + 0.3 | V    |

| I <sub>REF</sub>  | Analog Input Reference Current | 2                           | mA   |

| T <sub>oper</sub> | Operating Temperature          | 0, +70                      | °C   |

| T <sub>stg</sub>  | Storage Temperature            | -40, +150                   | °C   |

| P <sub>tot</sub>  | Total Power Dissipation        | 500                         | mW   |

#### V.2 - Thermal Data

| Symbol               | Parameter                                                                 | Value | Unit |

|----------------------|---------------------------------------------------------------------------|-------|------|

| R <sub>th(j-a)</sub> | DC Junction-Ambient Thermal Resistance Typ. with sample soldered on a PCB | 76    | °C/W |

#### V.3 - DC Electrical Characteristics

$T_{amb} = 25$ °C/70°C,  $V_{DDA} = V_{DD} = 3.3$ V, unless otherwise specified

| Symbol            | Parameter                                                         | Test Conditions                                                                                        | Min.       | Тур.     | Max.                   | Unit     |

|-------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------|----------|------------------------|----------|

| SUPPLY            |                                                                   |                                                                                                        |            |          |                        |          |

| $V_{DDA}$         | Analog Positive Supply Voltage                                    |                                                                                                        | 3.0        | 3.3      | 3.6                    | V        |

| $V_{DD}$          | Digital Supply Voltage                                            |                                                                                                        | 3.0        | 3.3      | 3.6                    | V        |

| I <sub>DDA</sub>  | Analog Current Consumption                                        | $RI_{REF}=1.2k\Omega$ , $R_{L}=200\Omega$ ,                                                            | 20         |          | 50                     | mΑ       |

| I <sub>DD</sub>   | Digital Current Consumption                                       | C <sub>L</sub> = 50pF, CKREF = 27MHz,<br>V <sub>DD</sub> = 3.6V autotest mode,<br>static input signals | 20         | 35       | 50                     | mA       |

| DIGITAL IN        | IPUTS                                                             |                                                                                                        |            |          |                        |          |

| V <sub>IL</sub>   | Input Voltage                                                     | Low level (any other pins)                                                                             |            |          | 0.8                    | V        |

| V <sub>IH</sub>   | Input Voltage<br>SCL and SDA<br>Except SCL and SDA                | High level (any other pins)                                                                            | 2.0<br>2.0 |          | 4.5<br>V <sub>DD</sub> | V        |

| lι                | Input Leakage Current Input Pins (see note 2) Bi-directional Pins | $V_{\text{IL}}$ min or $V_{\text{IH}}$ max                                                             | -10<br>-10 |          | 80<br>10               | μΑ<br>μΑ |

| C <sub>IN</sub>   | Input Capacitance<br>Input Pins<br>Bi-directional Pins            |                                                                                                        |            | 0.1<br>5 |                        | pF<br>pF |

| SDA OUTF          | PUT                                                               | •                                                                                                      |            | •        |                        |          |

| VL                | Output Voltage                                                    | Low level, I <sub>O</sub> = 2mA                                                                        |            |          | 0.4                    | V        |

| DIGITAL O         | UTPUT                                                             |                                                                                                        |            |          |                        |          |

| V <sub>OH</sub>   | Output Voltage                                                    | High level (I <sub>OH</sub> = -4mA)                                                                    | 2          |          |                        | V        |

| V <sub>OL</sub>   | Output Voltage                                                    | Low level (I <sub>OL</sub> = 4mA)                                                                      |            |          | 0.6                    | V        |

| D/A CONV          | ERTER                                                             |                                                                                                        |            | •        |                        |          |

| RI <sub>REF</sub> | Resistance for reference Current<br>Source for 3 D/A Converters   | $I_{REF} = V_{REF}/RI_{REF}$ , $V_{REF} = 1.12V$ typ.                                                  |            | 1.2      |                        | kΩ       |

| Vo                | Output Voltage Dyn                                                | $RI_{REF} = 1.2k\Omega$ , $R_L = 200\Omega$ (Max. code - Min. Code)                                    | 0.95       |          | 1.10                   | $V_{PP}$ |

|                   | DAC to DAC V <sub>O</sub> max code (tri-DAC only)                 | $RI_{REF} = 1.2k\Omega$ , $R_L = 200\Omega$                                                            |            |          | 3                      | %        |

| ILE               | LF Integral Non-linearity                                         | $RI_{REF} = 1.2k\Omega$ , $R_L = 200\Omega$                                                            |            | ± 1      |                        | LSB      |

| DLE               | LF Differential Non-linearity                                     | $RI_{REF} = 1.2k\Omega$ , $R_L = 200\Omega$                                                            |            | ± 0.5    |                        | LSB      |

Notes: 1. This product withstands 1.4kV (The MIL883C Norm requires 2.0kV).

<sup>2.</sup> The high value for input Pins is due to internal pull-down resistance.

This product withstands 150V (The EIAJ Norm requires 200V).

## V - CHARACTERISTICS (continued)

#### V.4 - AC Electrical Characteristics

$T_{amb} = 25$ °C/70°C,  $V_{DDA} = V_{DD} = 3.3$ V, unless otherwise specified

| Symbol                       | Parameter              | Test Conditions                                           | Min. | Тур. | Max. | Unit |

|------------------------------|------------------------|-----------------------------------------------------------|------|------|------|------|

| DIGITAL INPUT (Y             | CRCB[7:0], HSYNC, VSYN | C/ODDEVEN)                                                | •    |      | •    |      |

| tsu                          | Input Data Set-up Time | CKREF rising edge, CKREF = 27MHz                          | 6    |      |      | ns   |

| tho                          | Input Data Hold Time   | CKREF rising edge, CKREF = 27MHz                          | 3    |      |      | ns   |

| ACTIVE PERIOD F              | FOR NRESET             |                                                           |      |      |      |      |

| tRSTL                        | Input Low Time         |                                                           | 200  |      |      | ns   |

| REFERENCE CLC                | OCK : CKREF            |                                                           |      |      |      |      |

| 1/tC_REF                     | Clock Frequency        |                                                           |      | 27   |      | MHz  |

| tD_REF                       | Clock Duty Cycle       |                                                           | 35*  |      | 65*  | %    |

| tR_REF                       | Clock Rise Time        |                                                           |      |      | 5    | ns   |

| tF_REF                       | Clock Fall Time        |                                                           |      |      | 5    | ns   |

| I <sup>2</sup> C CLOCK : SCL |                        | •                                                         |      |      |      |      |

| tC_SCL                       | Clock Cycle Time       | Rpull_up = 4.7kΩ                                          |      |      | 2    | MHz  |

| tD_SCL                       | Clock Duty Cycle       |                                                           |      | 50   |      | %    |

| tL_SCL                       | LOW Level Cycle        | Rpull_up = $4.7k\Omega$                                   | 250  |      |      | ns   |

| DIGITAL OUTPUT               | S                      |                                                           |      |      |      |      |

| td_HSYNC                     | Delay Time             | CKREF rising edge<br>CKREF = 27MHz, C <sub>L</sub> = 50pF |      |      | 10   | ns   |

| td_ODDEVEN                   | Delay Time             | CKREF rising edge<br>CKREF = 27MHz, C <sub>L</sub> = 50pF |      |      | 10   | ns   |

$<sup>\</sup>ensuremath{^{*}}$  In case of double encoding these values must be compatible with the ycrcb transmitter.

## **VI - REGISTERS**

# VI.1 - Register Mapping

| configuration0   | R/W | 00 | std1           | std0           | sync2           | sync1           | sync0     | polh      | polv      | freerun   |

|------------------|-----|----|----------------|----------------|-----------------|-----------------|-----------|-----------|-----------|-----------|

| configuration1   | R/W | 01 | blkli          | flt1           | fltO            | sync_ok         | coki      | setup     | cc2       | cc1       |

| configuration2   | R/W | 02 | nintrl         | enrst          | bursten         | XXX             | selrst    | rstosc    | valrst1   | valrst0   |

| configuration3   | R/W | 03 | entrap         | trap_pal       | encgms          | nosd            | del2      | del1      | del0      | xxx       |

| configuration4   | R/W | 04 | syncin<br>_ad1 | syncin<br>_ad0 | syncout<br>_ad1 | syncout<br>_ad0 | aline     | txdl2     | txdl1     | txdl0     |

| configuration5   | R/W | 05 | rgb_nyc        | bkcvbs1        | reserved        | reserved        | bk_ys     | bk_c      | bk_cvbs   | dacinv    |

| configuration6   | R/W | 06 | softreset      | jump           | dec_ninc        | free_jump       | XXX       | XXX       | chgi2c    | maxdyn    |

| reserved         | xxx | 07 | XXX            | XXX            | XXX             | XXX             | XXX       | XXX       | XXX       | XXX       |

| reserved         | xxx | 08 | XXX            | XXX            | XXX             | XXX             | XXX       | XXX       | XXX       | XXX       |

| status           | R   | 09 | hok            | atfr           | b2_free         | b1_free         | fieldct2  | fieldct1  | fieldct0  | jumping   |

| increment_dfs    | R/W | 10 | d23            | d22            | d21             | d20             | d19       | d18       | d17       | d16       |

| increment_dfs    | R/W | 11 | d15            | d14            | d13             | d12             | d11       | d10       | d9        | d8        |

| increment_dfs    | R/W | 12 | d7             | d6             | d5              | d4              | d3        | d2        | d1        | d0        |

| phase_dfs        | R/W | 13 | -              | -              | -               | -               | -         | -         | o23       | 022       |

| phase_dfs        | R/W | 14 | o21            | o20            | o19             | o18             | o17       | o16       | o15       | o14       |

| reserved         | xxx | 15 | xxx            | xxx            | xxx             | xxx             | xxx       | xxx       | xxx       | xxx       |

| reserved         | xxx | 16 | xxx            | xxx            | xxx             | XXX             | xxx       | xxx       | S         | xxx       |

| chipid           | R   | 17 | 0              | 1              | 1               | 1               | 0         | 1         | 1         | 1         |

| revid            | R   | 18 | 0              | 0              | 0               | 0               | 0         | 0         | 0         | 1         |

| reserved         | R/W | 19 | xxx            | xxx            | xxx             | xxx             | xxx       | xxx       | xxx       | xxx       |

| reserved         | R/W | 20 | xxx            | xxx            | xxx             | xxx             | xxx       | xxx       | xxx       | xxx       |

| line_reg         | R/W | 21 | Itarg8         | ltarg7         | ltarg6          | ltarg5          | ltarg4    | Itarg3    | ltarg2    | Itarg1    |

| line_reg         | R/W | 22 | ltarg0         | Iref8          | lref7           | Iref6           | Iref5     | Iref4     | Iref3     | lref2     |

| line_reg         | R/W | 23 | Iref1          | lref0          | -               | -               | -         | -         | -         | -         |