## 2Mbit CEPT & PRIMARY RATE CONTROLLER DEVICE

**PRELIMINARY DATA**

- ONE CHIP SOLUTION FROM PCM BUS TO TRANSFORMER (CEPT STANDARD)

- ISDN PRIMARY ACCESS CONTROLLER (COMPATIBLE WITH ETSI, OPTION 1 AND 2)

- HDB3/BIN ENCODER AND DECODER ON CHIP

- MULTIFRAME STRUCTURE HANDLING

- **■** BUILT IN CRC4

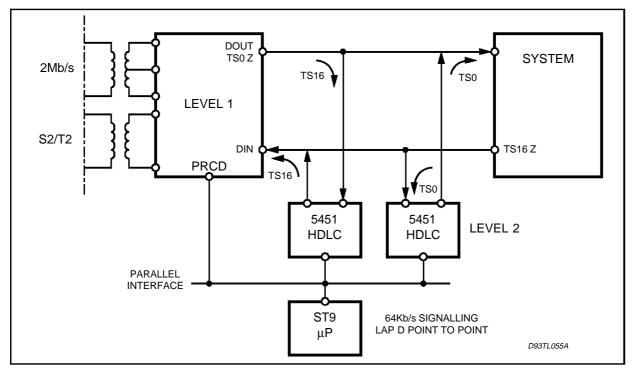

- EASY LINK TO ST5451/MK50H25/MK5027 LINK CONTROLLERS.

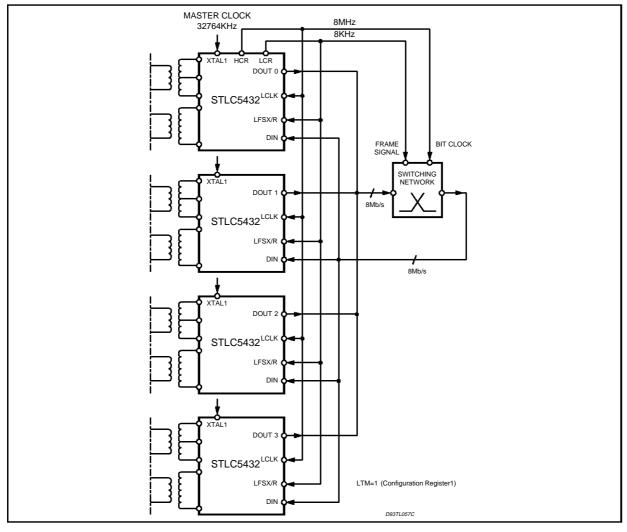

- DATA RATE: 2048, 4096 AND 8192 Kb/s FOR MULTIPLEXED APPLICATIONS

- FOUR LOOPBACK MODES FOR TESTING

- PSEUDO RANDOM SEQUENCE GENER-ATOR AND ANALYZER FOR ON-LINE, OFF-LINE AND AUTOTEST

- CLOCK RECOVERY CIRCUITRY ON CHIP

- 64 BYTE ELASTIC MEMORY FOR TIME COMPENSATION AND AUTOMATIC FRAME AND SUPERFRAME ALIGNMENT

- 32 ON CHIP REGISTERS FOR CONFIGURA-TIONS, TESTING, ALARMS, FAULT AND ER-ROR RATE CONTROL.

- AUTO ADAPTATIVE DETECTION THRESH-OLD

- AUTOMATIC EQUALIZER OPTION

- 5V POWER SUPPLY

- AMI OR HDB3 CODE SELECTION

- PARALLEL OR SERIAL MICROPROCESSOR INTERFACE OPTION

- BOTH μp AND STAND ALONE MODE AVAIL-ABLE

#### DESCRIPTION

STLC5432, CMOS device, interfaces the multiplex system to the physical CEPT Transmission link at 2048Kb/s. Furthermore, thanks to its flexibility, it is the optimum solution also for the ISDN application as PRIMARY RATE CONTROLLER. The receive circuit performances exceed CCITT recommendation and the line driver outputs meet the G.703 specifications.

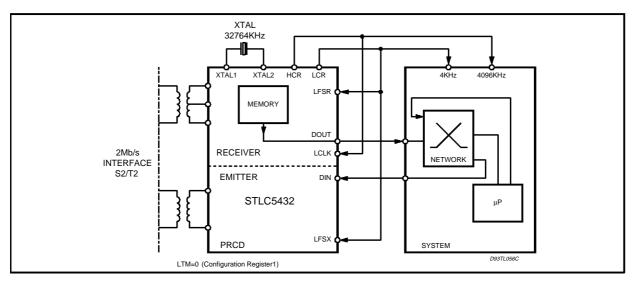

STLC5432 is the real single chip solution that allows the best system flexibility and easy design. STLC5432 can work either in 2048 or 4096 or 8192 Kbit/s systems programming the CR4 register (when parallel micro interface selected).

#### **PIN CONNECTION** (Top view)

July 1996 1/46

#### **PIN DESCRIPTION**

| Name                   | Pin            | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCCD1<br>VCCD2<br>VCCA | 18<br>17<br>34 |        | Positive power supply inputs for the digital ( $V_{CCD1}$ ) and analog ( $V_{CCA}$ ) sections and for microprocessor interface signals ( $V_{CCD2}$ ). They must be +5 Volts and must be directly connected together.                                                                                                                                                                                                                                                            |

| GNDD<br>GNDA           | 1<br>44        |        | Negative power supply pins which must be connected together close to the device. All digital and analog signals are referred to these pins, which are normally at the system ground.                                                                                                                                                                                                                                                                                             |

| LI1<br>LI2             | 40<br>42       | l<br>I | Receive HDB3 signal differential inputs from the line transformer.                                                                                                                                                                                                                                                                                                                                                                                                               |

| VT                     | 41             | 0      | Positive power supply output for fixing reference voltage to the receive transformer. Typical value is 2.375V                                                                                                                                                                                                                                                                                                                                                                    |

| L01<br>L02             | 36<br>37       | 0      | Transmit HDB3 signal differential outputs to the line transformer. When used with an appropriate transformer, the line signal conforms to the output specifications in CCITT with a nominal pulse amplitude of 3 volts for a $120\Omega$ load on line side.                                                                                                                                                                                                                      |

| XTAL1                  | 15             | I      | The master clock input which requires either a parallel resonance crystal to be tied between this pin and XTAL2, or a clock input from a stable source. This clock does not need to be synchronized to the system clock. Crystal specifications = 32764 kHz $\pm$ 50 ppm parallel resonant; RS $\leq$ 20 $\Omega$ loaded with 33pF to GND each side.                                                                                                                             |

| XTAL2                  | 16             | 0      | The output of the crystal oscillator, which should be connected to one end of the crystal if used.                                                                                                                                                                                                                                                                                                                                                                               |

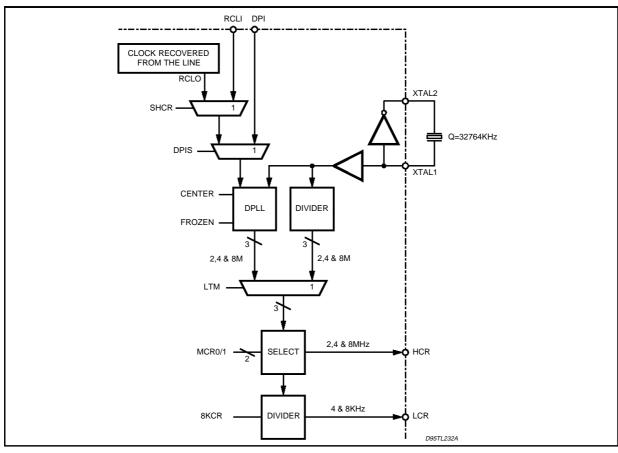

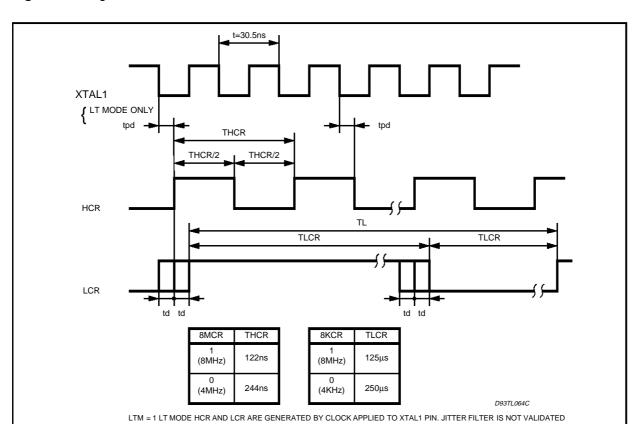

| HCR                    | 19             | 0      | High clock received, bit clock. When the device has recovered the clock from the HDB3 signal, HCR signal is synchronized to the remote circuit. The HCR frequency is either 8192kHz if 8MCR bit of CR1 Register is put to 1 or 4096 kHz if 8MCR is set to 0.                                                                                                                                                                                                                     |

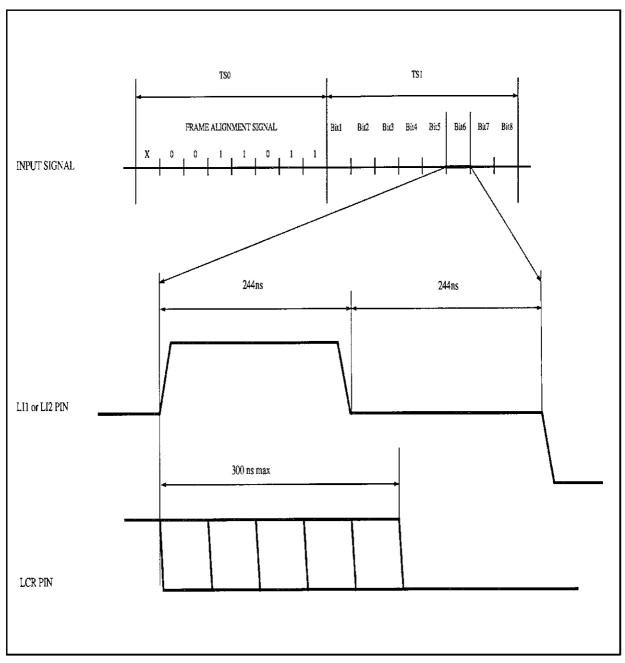

| LCR                    | 20             | 0      | Low clock received, frame clock. When the device has recovered the clock from the HDB3 signal, LCR signal is synchronized to the remote entity.  The LCR frequency is 8 kHz if 8KCR bit is set to 1, or 4 kHz if 8KCR bit is set to 0. When the remote clock is not recovered, HCR and LCR frequency are synchronized to master clock (16384 kHz).  HCR and LCR can be used by the system in Terminal Mode. These two clocks can be used by the transmit function of the device. |

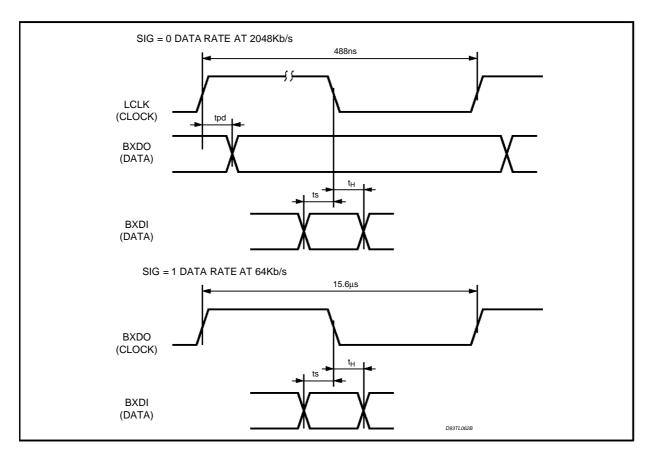

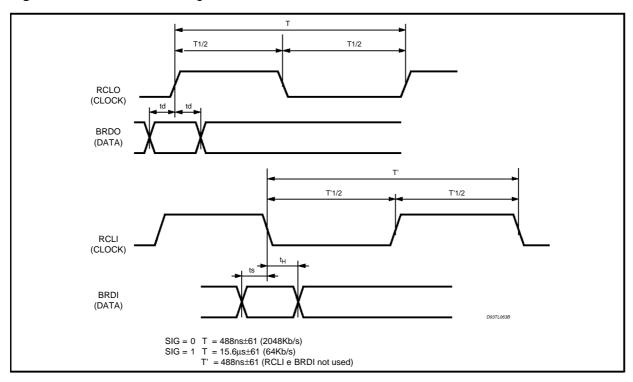

| BRDO<br>RCLO           | 12<br>14       | 0      | Binary Receive Data Output, 2048 kbit/s or 64kbit/s. Receive Clock output, 2048 kHz or 64kHz. After decoding, Binary Data and clock associated are provided for different applications.                                                                                                                                                                                                                                                                                          |

| BRDI<br>RCLI           | 10<br>9        |        | Binary Receive Data Input. 2048 kbit/s.<br>Receive Clock Input 2048 kHz.                                                                                                                                                                                                                                                                                                                                                                                                         |

| BXDO                   | 22             | 0      | Binary Transmit Data Output, 2048 kbit/s or output clock at 64kHz. Before encoding Binary Data is provided to different applications (Optical Interface for instance). Local clock is associated to this data.                                                                                                                                                                                                                                                                   |

| BXDI                   | 33             | I      | This binary signal can replace BXD internal signal to be encoded if SELEX bit (CR1 Register) is set to 1.                                                                                                                                                                                                                                                                                                                                                                        |

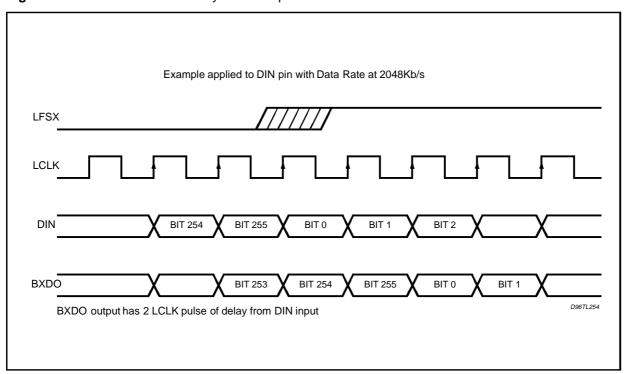

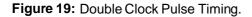

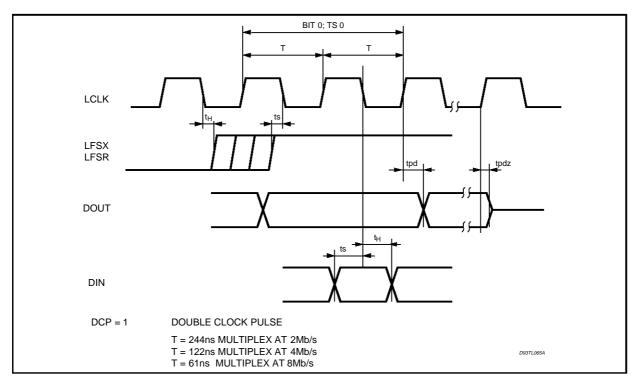

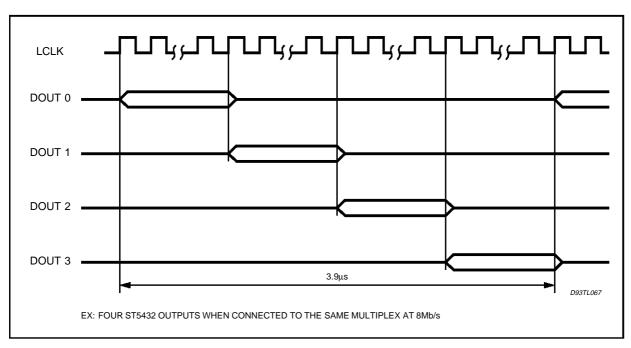

| DOUT                   | 11             | 0      | Data Output. 30 B+D primary access data received from the line.Data can be shifted out from the tristate output DOUT at the LCLK frequency on the rising edges during all the time slots, except Time Slot Zero in accordance with TSOE bit (CR1Register). NB: If parallel micro-interface is selected, DOUT is at high impedance after Reset. DOUT is at low impedance after writing CR4 register.                                                                              |

| DIN                    | 3              | I      | Data Input: 30B+D primary access data to transmit to the line.Data can be shifted in at the LCLK frequency on the falling edges during all the time slots, except Time Slot Zero, in accordance with TSOE bit (CR1 Register).                                                                                                                                                                                                                                                    |

## PIN DESCRIPTION (continued)

| Name         | Pin                 | Туре | Function                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCLK         | 23                  | I    | Local Clock: this clock input determines the data shift rate on the two digital multiplexes. This clock frequency can be indifferently 2048, 4096, 8192 or 16384kHz. Data Out and Data In rate is always 2048 kbit/s when Serial Interface microprocessor: an internal automatic mechanism divides by two the frequency if 4096 kHz.                                              |

| LFSR         | 24                  | I    | Local Frame Synchronization for the Receiver. This clock input defines the start of the frame on the digital multiplex Data (pin DOUT). This clock frequency can be indifferently 8 kHz or a submultiple of 8 kHz.                                                                                                                                                                |

| LFSX         | 25                  | I    | Local Frame Synchronization for the Transmitter. This clock input defines the start of the frame on the digital multiplex Data (pin DIN). This clock frequency can be indifferently 8 kHz or a submultiple of 8 kHz.  If submultiple of 8 kHz, LFSX defines the start of even frame on DIN. The TSO of this even frame will contain the Frame Alignment Signal (FAS) on the line. |

| AL0,<br>AL1  | 32<br>31            | 0    | Alarm 0 Output, alarm 1 Output. These pins are open drain outputs which are normally in high impedance state.                                                                                                                                                                                                                                                                     |

|              |                     |      | AL1 AL0 Alarm definitions                                                                                                                                                                                                                                                                                                                                                         |

|              |                     |      | Z Z Frame or Multiframe recovered,                                                                                                                                                                                                                                                                                                                                                |

|              |                     |      | A bit received is 0.  OVolt Z Frame or Multiframe recovered,                                                                                                                                                                                                                                                                                                                      |

|              |                     |      | A bit received is 1                                                                                                                                                                                                                                                                                                                                                               |

|              |                     |      | Z 0Volt Frame and Multiframe lost, AIS Alarm Indication Signal is detected.                                                                                                                                                                                                                                                                                                       |

|              |                     |      | 0Volt 0Volt Frame and Multiframe lost, AIS Alarm Indication Signal is not detected.                                                                                                                                                                                                                                                                                               |

| DPI          | 38                  | I    | DPI input: The internal DPLL is synchronized either by the signal applied on DPI input (if DPIS bit of CR5 register is = 0) or by the 2MHz clock recovered from the line.                                                                                                                                                                                                         |

| SA/RESET     | 2                   | I    | <b>Stand Alone</b> : When this pin is connected to 5 Volts, the device works without microprocessor. The configuration is given by the values per default of programmable registers. BRDI and BXDI must not be used.                                                                                                                                                              |

|              |                     |      | <b>RESET</b> : When this pin is put to 5 Volts during 100 ns at least every programmable register is reset (value per default). When this pin is set at zero Volt, the type of microprocessor is selected by P0, P1 pins.                                                                                                                                                         |

| P0, P1       | 39, 43              | 1    | Processor interface. These two input pins define the microprocessor interface                                                                                                                                                                                                                                                                                                     |

|              |                     |      | chosen. P1 P0 Microprocessor Interface                                                                                                                                                                                                                                                                                                                                            |

|              |                     |      | 0 0 Serial Microprocessor Interface                                                                                                                                                                                                                                                                                                                                               |

|              |                     |      | 0 1 ST9 Microprocessor Interface                                                                                                                                                                                                                                                                                                                                                  |

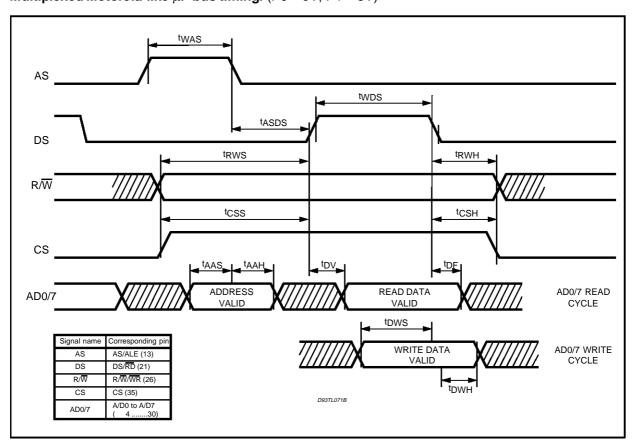

|              |                     |      | 1 0 Multiplexed Motorola processor interface 1 1 Multiplexed Intel processor interface                                                                                                                                                                                                                                                                                            |

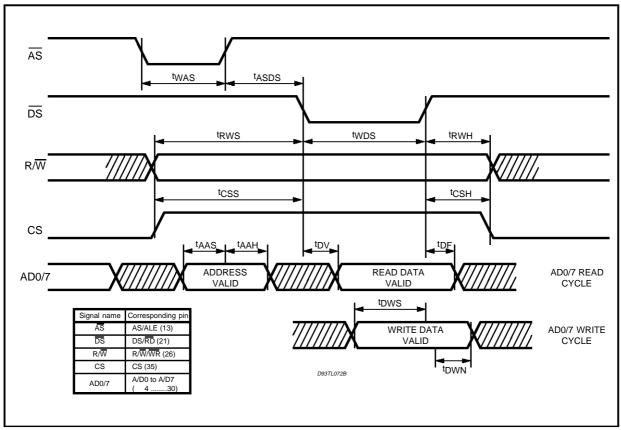

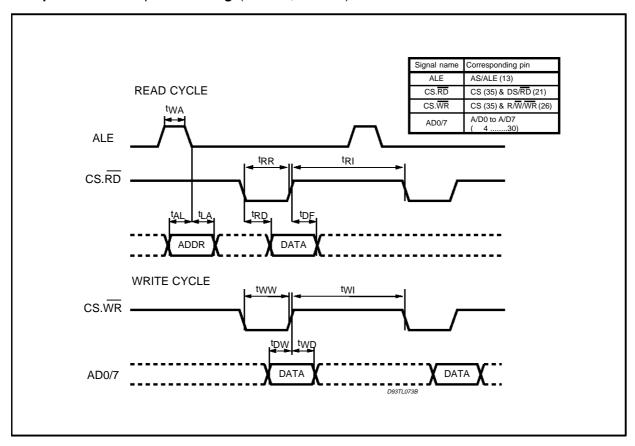

| AS/ALE       | 13                  | ı    | Address Strobe/Address Latch Enable. Input                                                                                                                                                                                                                                                                                                                                        |

| CS           | 35                  | ı    | Chip Select. A high level on this input selects the PRCD for a read write operation.                                                                                                                                                                                                                                                                                              |

| R/W/WR       | 26                  |      | Read/Write/Write Data. Input.                                                                                                                                                                                                                                                                                                                                                     |

| DS/RD        | 21                  | I    | Data Strobe/Read Data. Input.                                                                                                                                                                                                                                                                                                                                                     |

| A/D0 to A/D7 | 4 to 7;<br>27 to 30 | I/O  | Address/Data 0 to 7. Input-Output.                                                                                                                                                                                                                                                                                                                                                |

| ĪNT          | 8                   | 0    | Interrupt Request. The signal is activated low when the PRCD requests an interrupt. It is an open drain output.                                                                                                                                                                                                                                                                   |

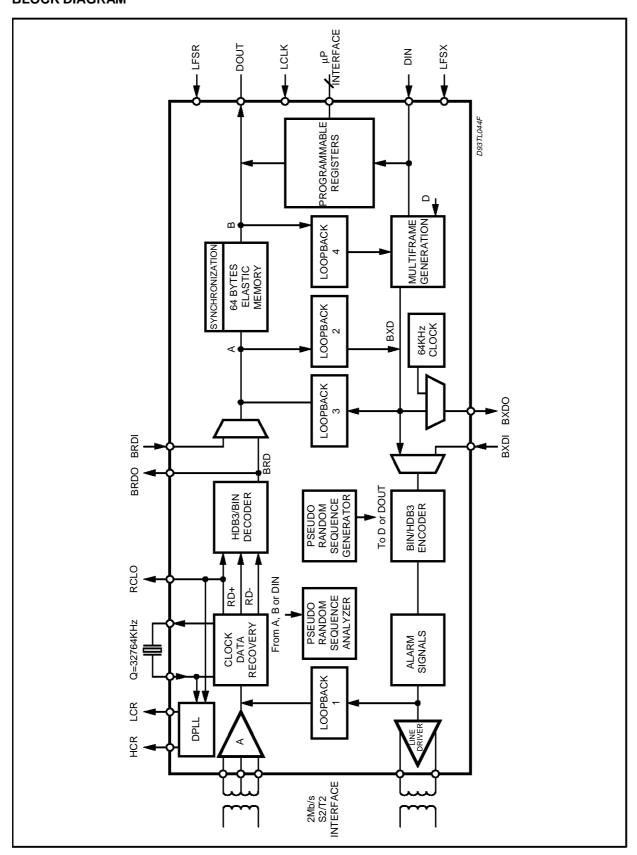

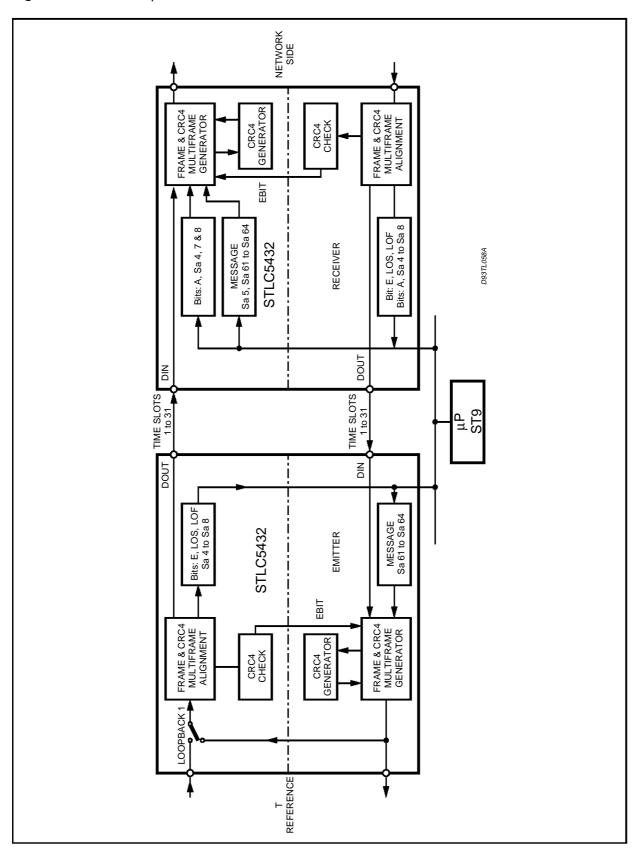

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                              | Parameter                              | Value                       | Unit |

|-------------------------------------|----------------------------------------|-----------------------------|------|

| V <sub>CC</sub> to GND              | Supply Voltage to Ground               | 7                           | V    |

| $V_{I}$                             | Voltage at any digital or analog input | V <sub>CC</sub> +1 to GND-1 | V    |

| I <sub>LO1</sub> , I <sub>OL2</sub> | Current at LO1 and LO2                 | ±100                        | mA   |

| Ic                                  | Current at any digital or analog input | ±30                         | mA   |

| $T_{stg}$                           | Storage temperature range              | -65 to +150                 | °C   |

| TL                                  | Lead Temperature (soldering, 10s)      | +300                        | °C   |

#### **THERMAL DATA**

| Symbol               | Parameter                                   | Value | Unit |

|----------------------|---------------------------------------------|-------|------|

| R <sub>thi-amb</sub> | Thermal Resistance Junction to ambient Max. | 50    | °C/W |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5V \pm 5\%$ ,  $T_{amb} = 0$  to  $70^{\circ}C$ ; Typical characteristics are specified at  $V_{CC} = 5V$ ,  $T_{amb} = 25^{\circ}C$ ; all signal are referenced to GND, unless otherwise specified.)

| Symbol     | Parameter                                                         | Test Condition                                                                                                        | Min.                 | Тур.       | Max.    | Unit   |

|------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------|------------|---------|--------|

| DIGITAL IN | ITERFACE                                                          |                                                                                                                       |                      |            |         |        |

| Vil        | Input Low Voltage                                                 | All digital inputs                                                                                                    |                      |            | 0.8     | V      |

| Vih        | Input High Voltage                                                | All digital inputs                                                                                                    | 2.2                  |            |         | V      |

| Vilx       | Input Low Voltage                                                 | XTAL1 input                                                                                                           |                      |            | 0.5     | V      |

| Vihx       | Input High Voltage                                                | XTAL1 input                                                                                                           | V <sub>CC</sub> -0.5 |            |         | V      |

| Vol        | Output Low Voltage                                                | I <sub>L</sub> = 7mA for pins AL0, AL1,<br>INT, DOUT, HCR, LCR.<br>All other digital outputs:<br>I <sub>I</sub> = 1mA |                      |            | 0.4     | V<br>V |

| Voh        | Output High Voltage                                               | I <sub>L</sub> = 7mA for pins AL0, AL1, INT, DOUT, HCR, LCR. All other digital outputs: I <sub>L</sub> = 1mA          | 2.4<br>2.4           |            |         | V      |

| lil        | Input Low Current                                                 | Any digital input, Gnd < Vin < Vil                                                                                    |                      |            | 10      | μΑ     |

| lih        | Input High Current                                                | Any digital input, Gnd < Vin < V <sub>CC</sub>                                                                        |                      |            | 10      | μΑ     |

| loz        | Output Current in High<br>Impedance (tri-state)                   | All digital tri-state I/Os without internal pull-up or pull-down resistor.                                            |                      |            | 10      | μΑ     |

| LINE INTE  | RFACE FEATURES                                                    |                                                                                                                       |                      |            |         |        |

| Zin        | Differential Input Resistance                                     | DC measurement between LI1 and LI2 with the equalizer not connected                                                   |                      | 200        |         | ΚΩ     |

| Vin        | Rx sensitivity                                                    | Relative to LI1/LI2 pins with fixed detection threshold                                                               | 0.6                  |            |         | Vpk    |

| Vpk75      | Transmit amplitude                                                | 75Ω at transformer secondary                                                                                          | 2.14                 | 2.37       | 2.60    | Vpk    |

| Vpk120     | Transmit Amplitude                                                | 120 $\Omega$ at transformer secondary                                                                                 | 2.7                  | 3          | 3.30    | Vpk    |

| Sym        | Pulses Symetry                                                    | $75\Omega$ or 120Ω at transformer secondary                                                                           |                      |            | 5       | %      |

| Zero       | Zero level                                                        | % nominal amplitude                                                                                                   |                      |            | 10      | %      |

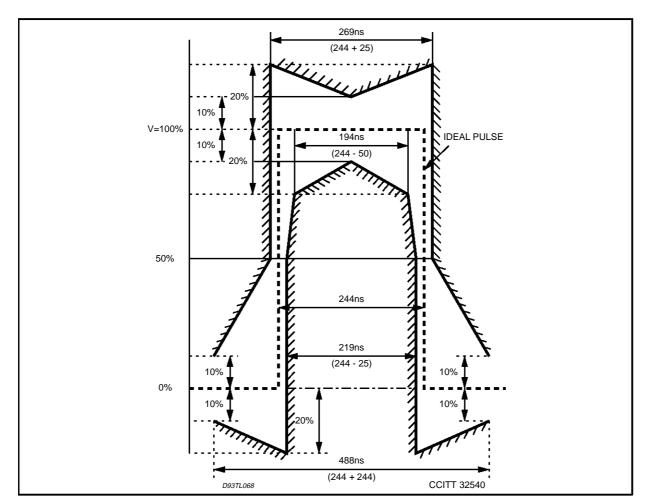

| Pwdth      | Tx pulses width                                                   | at 50% of peak amplitude                                                                                              | 219                  | 244        | 269     | ns     |

| Zout       | Differential Output Resistance                                    |                                                                                                                       |                      | 1          |         | Ω      |

| MASTERCI   | LOCK                                                              |                                                                                                                       |                      |            |         |        |

| MCLK       | MCLK Frequency                                                    |                                                                                                                       |                      | 32.764     |         | MHz    |

|            | MCLK Frequency tolerance                                          |                                                                                                                       | -50                  |            | 50      | ppm    |

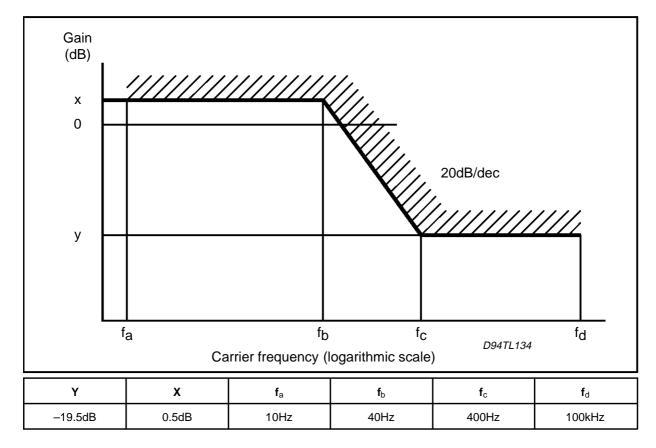

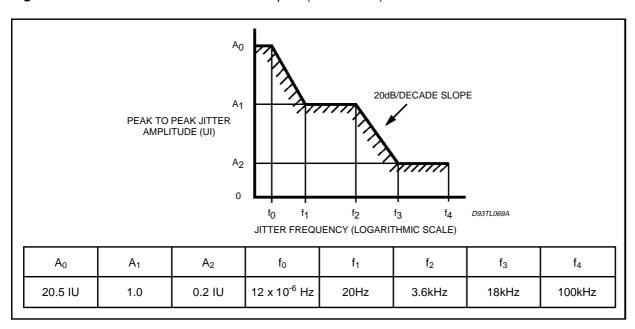

|            | RFORMANCES (for jitter transfer stics plotted in following page). | function and admissible jitter pl                                                                                     | ease repo            | ort to the | corresp | onding |

|            | Intrinsic jitter                                                  | Filter 20Hz - 100KHz                                                                                                  |                      |            | 0.125   | UI     |

|            | Intrinsic jitter                                                  | Filter 700Hz - 100KHz                                                                                                 |                      |            | 0.12    | UI     |

## **ELECTRICAL CHARACTERISTICS** (continued)

| Symbol            | Parameter                                                                                                           | Test Condition                        | Min. | Тур.     | Max. | Unit |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|----------|------|------|--|

| POWER CONSUMPTION |                                                                                                                     |                                       |      |          |      |      |  |

| lcc75             | Active Current (including line current)                                                                             | random output (50% of ones)           |      | 40       |      | mA   |  |

| Icc120            | Active Current (including line current)                                                                             | random output (50% of ones)           |      | 40       |      | mA   |  |

| TRANSFOR          | RMER SPECIFICATION FOR 75 $\Omega$                                                                                  |                                       |      |          |      |      |  |

| L:M:N:            | Turns ratioes                                                                                                       |                                       |      | 1.57:1:1 |      |      |  |

| RL                | L Windings Resistance                                                                                               |                                       |      | 0.23     |      | Ω    |  |

| RMN               | M and N winding resistances                                                                                         |                                       |      | 0.11     |      | Ω    |  |

| LL                | Inductance of winding L                                                                                             | F = 100KHz, Vrms = 100mV              | 2    |          |      | mH   |  |

| Ls                | Leakage inductange of a winding, the other being short circuited                                                    | F = 100KHz, Vrms = 100V               |      |          | 0.3  | μН   |  |

| Ck                | Inter winding capacitance                                                                                           | F = 100KHz, Vrms = 100mV              |      |          | 15   | pF   |  |

| TRANSFOR          | RMER SPECIFICATION FOR 120 $\Omega$                                                                                 |                                       |      | _        |      |      |  |

| L:M:N:            | Turns ratioes                                                                                                       |                                       |      | 2:1:1    |      |      |  |

| RL                | L Windings Resistance                                                                                               |                                       |      | 0.2      |      | Ω    |  |

| RMN               | M and N winding resistances                                                                                         |                                       |      | 0.1      |      | Ω    |  |

| LL                | Inductance of winding L                                                                                             | F = 100KHz, Vrms = 100mV              | 2    |          |      | mH   |  |

| Ls                | Leakage inductange of a winding, the other being short circuited                                                    | F = 100KHz, Vrms = 100mV              |      |          | 0.2  | μН   |  |

| Ck                | Inter winding capacitance                                                                                           | F = 100KHz, Vrms = 100mV              |      |          | 15   | pF   |  |

| XTALL SPE         | CIFICATIONS                                                                                                         |                                       |      |          |      |      |  |

| Co                | Motional capacitance                                                                                                |                                       |      | 0.2      |      | pF   |  |

| Сс                | Shunt capacitance                                                                                                   |                                       |      | 6        |      | pF   |  |

| Lo                | Inductance                                                                                                          |                                       |      | 4.718    |      | mH   |  |

| Rs                | Serial resistance                                                                                                   |                                       |      | 15       |      | Ω    |  |

| CL                | Load (corresponding to two<br>33pF capacitors connected to<br>XTAL1 and XTAL2 pins on the<br>application schematic) |                                       |      | 20       |      | pF   |  |

| DYNAMIC (         | CHARACTERISTICS                                                                                                     |                                       | _    |          |      |      |  |

| tpd               | LCLK high to DOUT valid<br>LCLK high to BXDO valid<br>XTAL1 high to HCR high or low                                 | 150pF; 7mA<br>50pF; 1mA<br>150pF; 7mA |      |          | 50   | ns   |  |

| tpdz              | LCLK high to DOUT HZ                                                                                                | 150pF; 7mA                            |      |          | 50   | ns   |  |

| td                | HCR high to LCR high or low RCLO high to BDRO high or low                                                           | 150pF; 7mA<br>50pF; 1mA               | -20  |          | 20   | ns   |  |

| ts                | All data inputs to clock low                                                                                        |                                       | 10   |          |      | ns   |  |

| th                | Clock low to all data inputs                                                                                        |                                       | 10   |          |      | ns   |  |

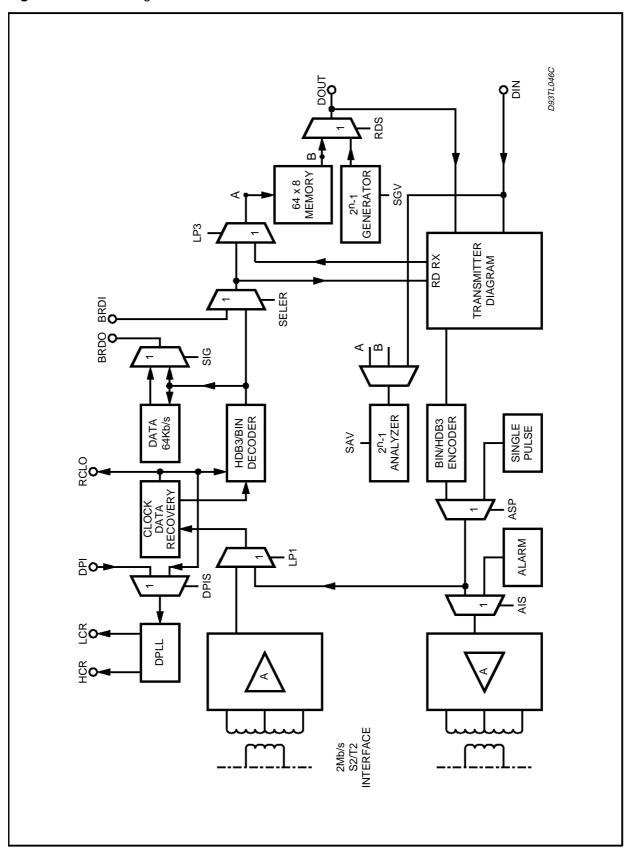

Figure 1: Receiver Diagram

#### INTRODUCTION

This single chip CMOS Device interfaces the physical multiplex of the application to the physical CEPT transmission link at 2048kb/s.

STLC5432 contains analog and digital functions to implement line interface function and frame synchronization. It meets pulse shape and jitter specifications in accordance with CCITT Recommendations and CEPT standards.

#### **FUNCTIONAL DESCRIPTION**

#### 1. LINE INTERFACE

#### 1.1 Receiver

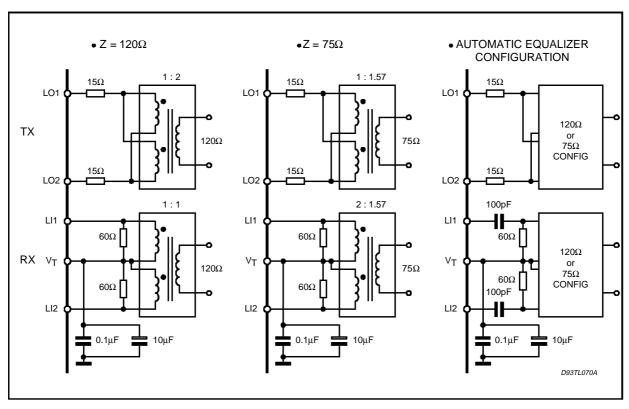

The receive input signal should be derived via a transformer of the same type used for the transmit direction. The suggested transformer is the VAC L4097-X004 or equivalent for the 75 ohms case and the VAC 4097-X012 or equivalent for the 120 ohms case. The electrical models of the transformers are summarized in the following table:

| Loads $(\Omega)$ | n        | Ls<br>(μΗ) | Ck<br>(pF) | Lh<br>(mH) | Rcul<br>(Ω) | Rculli<br>(Ω) |

|------------------|----------|------------|------------|------------|-------------|---------------|

| 75               | 1.57:1:1 | ≤0.3       | ≤15        | ≥2         | 0.11        | 0.23          |

| 120              | 2:1:1    | ≤0.2       | ≤15        | ≥2         | 0.10        | 0.20          |

with:

n: Winding ratioes

Ls: Leakage inductance

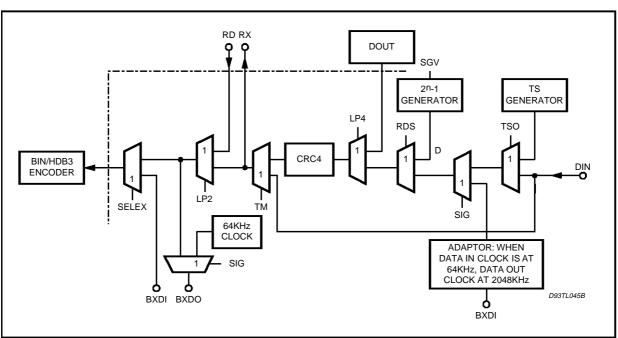

Figure 2: Transmitter Diagram

Ck: Inter winding capacitance

Lh: Principal inductance of

windings

Rcul and RcullI: DC resistances of

winding I and III.

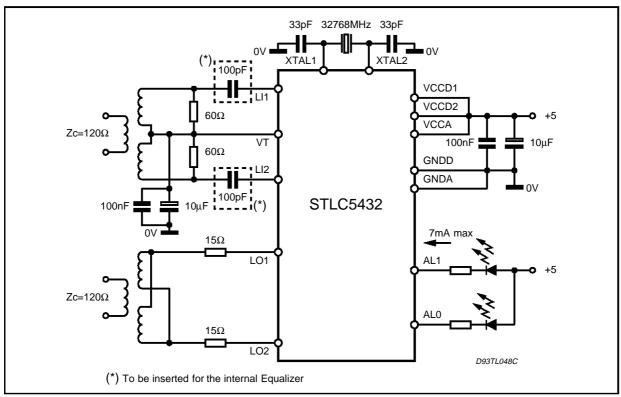

Wiring between the transformer and the circuit should respect the application schematic given in annex. (see fig 4).

The internal fixed threshold is set to 200 mV over the common mode voltage VCM (VCM = 2.375 V nominal) to insure the specified transmission range with a good noise immunity.

Two options are provided for special applications requiring improved transmission ranges:

#### ■ AUTO-ADAPTATIVE THRESHOLD:

- Using the configuration register CR4 (AVT), a peak amplitude detector circuit is connected to the received signal and after digital processing, an adaptative threshold value equal to 3/8 of the peak value is obtained at the output of a D to A converter and used for data detection.

- AUTOMATIC EQUALIZER: connecting two external capacitors of 100pF in series between the transformer and the circuits inputs, and using the configuration register CR4 (EQV), the circuit will select automatically a pre-compensation filter for long line configuration (see application schematic on figure 3 and 4 given in annex).

Using both options allow the reception of a signal attenuated up to 12dB at 1024kHz.

The Clock recovery is performed by a first PLL that guaranties the CCITT I431 requirements for the allowed Jitter, see Figure 23, this clock, RCL, is used internally and as local clock.

A second DPLL starting from this RCL clock attenuate the Jitter, to fulfil the CCITT I431, see figure 8, this DPLL generate HCR, bit clock, and LCR frame clock, practically without Jitter.

#### 1.2 Transmitter

The line driver outputs are designed to drive the suitable transformer mentioned in the previous section. The transformer results in a signal amplitude of 3 volts on the line which meet G.703 pulse shape for a 120 ohm load (2.37 volt for a 75 ohms load).

A special test mode is provided to check the pulse template according to the CCITT mask by using the configuration register CR3 (ASP).

When the ALS command is valid, consecutive logical "ones" are transmitted on the line.

When APS command is valid, consecutive 1, 0, 1... 1, 0, 1, 0... are transmitted on the line.

#### 2 CODING

#### 2.1 HDB3/BIN DECODING

The two constituents of the data signal are decoded and the binary Receive Data Signal (BRD) is processed by the next functions.

#### 2.2 BIN/HDB3 ENCODING

The binary transmit data signal (BXD) is encoded. The entire data stream, including all the time slots, is scanned for an occurence of four consecutive zeros.

Such occurence is replaced by the appropriate HDB3 code.

#### 3. BINARY INPUT-OUTPUT

STLC5432 can directly interface binary data stream by means of the 6 dedicated pins: BRDO, RCLO, BRDI, RCLI, BXDO and BXDI. This allows the use of STLC5432 also for particular cases as for optical fiber or for different purposes. The functions of these 6 pins are defined by the SIG bit (SIGR register).

$3.1 \, SIG = 0$

When the bit SIG = 0 the binary data are exchanged at 2048KHz and the 6 extra pins are defined hereafter.

#### 3.1.1 Extra pins for receive data

The BRDO and RCLO output pins deliver respec-

tively BRD binary receive data at 2048kb/s and the remote clock recovered at 2048kHz.

Two BRDI and RCLI input pins can receive external binary receive data at 2048kb/s and the receive clock associated at 2048kHz.

The SELER command replaces BRD internal signal with BRDI signal.

#### 3.1.2 Extra pins for transmit data

The transmit binary data output pin BXDO delivers transmit binary data BXD.

Input pin BXDI can receive external binary transmit data.

The SELEX command replaces BXD internal signal with BXDI signal.

#### $3.2 \, SIG = 1$

When SIG = 1, a signaling channel at 64 kb/s is implemented.

#### 3.2.1 Extra pins for Receive data

BRDO and RCLO output pins deliver respectively receive data at 64kb/s selected by an internal Time Slot Assigner and the receive clock associated at 64kHz. In this case, BRDI and RCLI are not used.

#### 3.2.2 Extra pins for Transmit Data

Output BXDO delivers the 64kHz clock for an external application. This external entity delivers data at 64kb/s on the rise edge of the clock.

Input BXDI shifts data at 64 kb/s on the fall edge of the 64kHz clock.

The same Time Slot Assigner is used by transmitter and receiver (See SIGR Register).

#### **4 LOOPBACK**

#### 4.1 LOOPBACK 1

When LP1 Command is valid (LP1 bit high, see CRC3 register), output data signal replaces input data signal. Then, the recovery clock function provides the local clock. The loopback is transparent if AIS is at 0. If AISX is at 1, consecutive logical "ones" are transmitted on the line.

#### 4.2 LOOPBACK 2

LP2 Command (LP2 bit high, CR3 register) replaces BXD and XCLK signals (respectively Binary Transmit Data and transmit clock) with BRD and RCLK (respectively Binary Receive data and its clock recovered).

#### 4.3 LOOPBACK 3

LP3 Command (LP3 bit high, CR3 register) replaces BRD and RCLK (respectively Binary Receive Data and its clock recovered) with BXD and

XCLK (respectively Transmit Data and its clock associated). Frame and multiframe generated by the transmitter of the circuit are processed by the receiver of the circuit, without encoding and decoding.

#### 4.4 LOOPBACK 4

LP4 Command replaces Data in with Data out near of DIN and DOUT pins (See LP4R register).

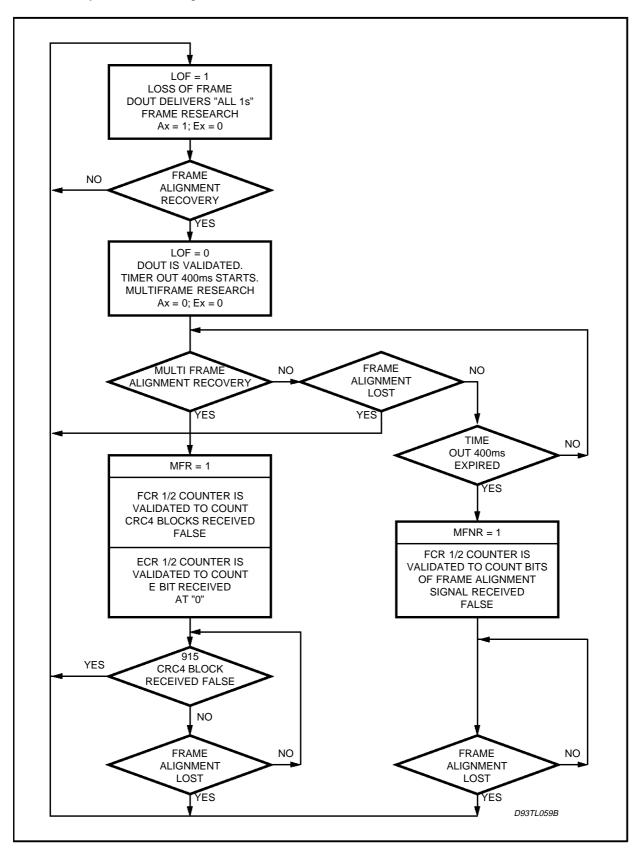

#### **5 FRAME ALIGNMENT**

Time slot 0 is used for the synchronization (G.706). At software Reset Frame and Multiframe are lost and a new research of FAS and MFAS is launched.

#### 5.1 LOSS OF FRAME ALIGNMENT

Frame alignment will be assumed to have been lost:

either when three consecutive incorrect frame alignment signals have been received,

- or when bit 2 in time slot 0 in odd frames has been received with an error, i.e. at 0, on three consecutive occasions.

- or when 915 errored CRC blocks out of 1000 have been detected.

#### 5.2 FRAME ALIGNMENT RECOVERY

Frame alignment will be assumed recovered when the following sequence is detected:

- Detection of the correct Frame Alignment Signal, FAS

- detection of bit 2 of 32nd byte after FAS, at 1.

- detection of the correct Frame Alignment signal in the 64th byte after the first FAS detected.

#### 5.3 MULTIFRAME ALIGNMENT RECOVERY

Multiframe Alignment will be assumed recovered when at least two valid multiframe alignment signals MFAS have been detected within 8 ms.

Table 1: CRC4 Multiframe Structure G.704

| Sub        | Frame    |    |   | TIME | SLOT ZER | O BIT NUMI | BERS |     |     |

|------------|----------|----|---|------|----------|------------|------|-----|-----|

| Multiframe | i iailie | 1  | 2 | 3    | 4        | 5          | 6    | 7   | 8   |

|            | 0        | C1 | 0 | 0    | 1        | 1          | 0    | 1   | 1   |

|            | 1        | 0  | 1 | Α    | Sa4      | Sa5        | Sa61 | Sa7 | Sa8 |

|            | 2        | C2 |   |      | F        | Α          | S    |     |     |

| l l        | 3        | 0  | 1 | Α    | Sa4      | Sa5        | Sa62 | Sa7 | Sa8 |

|            | 4        | C3 |   |      | F        | Α          | S    |     |     |

|            | 5        | 1  | 1 | Α    | Sa4      | Sa5        | Sa63 | Sa7 | Sa8 |

|            | 6        | C4 |   |      | F        | Α          | S    |     |     |

|            | 7        | 0  | 1 | Α    | Sa4      | Sa5        | Sa64 | Sa7 | Sa8 |

|            | 8        | C1 |   |      | F        | Α          | S    |     |     |

|            | 9        | 1  | 1 | Α    | Sa4      | Sa5        | Sa61 | Sa7 | Sa8 |

|            | 10       | C2 |   |      | F        | Α          | S    |     |     |

| II         | 11       | 1  | 1 | Α    | Sa4      | Sa5        | Sa62 | Sa7 | Sa8 |

|            | 12       | C3 |   |      | F        | Α          | S    |     |     |

|            | 13       | E1 | 1 | Α    | Sa4      | Sa5        | Sa63 | Sa7 | Sa8 |

|            | 14       | C4 |   |      | F        | Α          | S    |     |     |

|            | 15       | E2 | 1 | А    | Sa4      | Sa5        | Sa64 | Sa7 | Sa8 |

FAS: Frame Alignment Signal in each even Time Slot.

MFAS: Multi Frame Alignment Signal 0 0 1 0 1 1

E1–E2: CRC4 error Indication bits

C1 to C4: Cyclic Redundancy Check 4 (CRC4) bits

A: Remote Alarm Indication Sa4 to Sa8: Five bits in each odd Time Slot

Sa61 to Sa64: ETSI bits

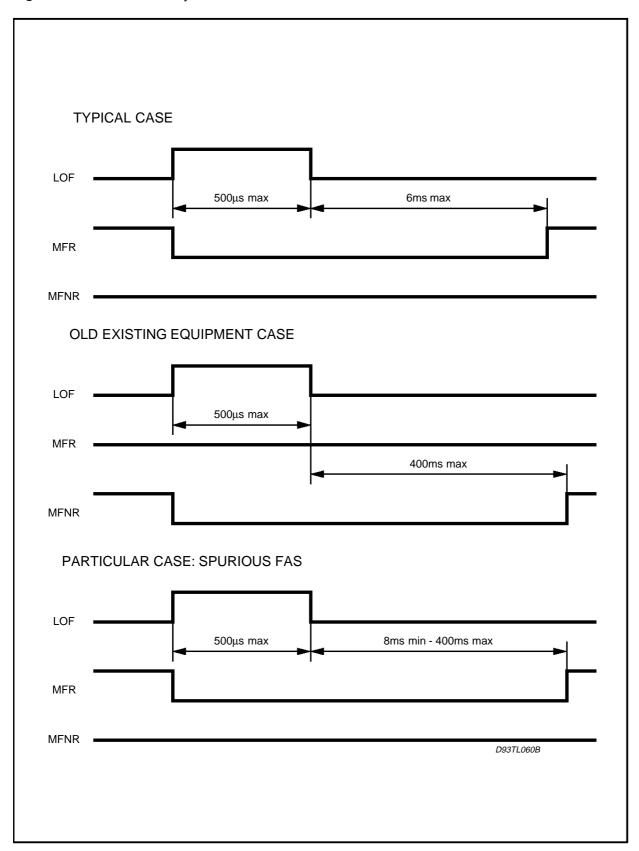

#### 5.3.1 Typical case

Remote entity transmits Frame Alignment Signal (FAS) and Multiframe Alignment Signal (MFAS).

As soon as lost of Frame Alignment is occured (LOF = 1), the local receiver recovers FAS from 254 up to 500µs after. As soon as FAS is recovered (LOF = 0), the local receiver recovers MFAS from 4 up to 6ms after.

#### 5.3.2 Old Existing Equipment Case

Remote entity transmits Frame Alignment Signal (FAS) without Multiframe Alignment Signal (MFAS). As soon as lost of Frame Alignment is occured (LOF=1), the local receiver recovers FAS from 254 up to  $500\mu s$  after. Then LOF = 0, and 400ms after the local receiver indicates that the Multiframe Alignment Signal has not been recovered (MFNR = 1).

#### 5.3.3 <u>Particular Case: Spurious Frame Alignment</u> Signal

Local receiver receives true FAS and true MFAS among several spurious FAS.

Multiframe Alignment signal (MFR=1) is recovered from 8 to 400ms after the Frame Alignment signal is recovered (LOF=0). Then, this FAS is either a spurious one (the "Spurious Time slot Zero" is carrying FAS without MFAS), or true FAS.

Anyway, when the Multiframe Alignment has been recovered (MFR=1), the good Frame Alignment Signal is taken into account and data are loaded into the Frame Memory at the good location. See Fig. 13 synchronization algorithm.

#### 5.3.4 Worst Case

Local receiver receives true FAS and true MFAS among several spurious FAS and several spurious MFAS.

In this case, if the circuit has recovered a spurious FAS and MFAS, the CRC blocks will be detected with an high error rate. As soon as 915 errored CRC block within 1000 will be detected, the MFAS will be assumed as spurious and a new research starts at the point just after the location of the assumed spurious Frame Alignement Signal.

#### 5.4 Transmitter SIDE

The Frame Alignement Signal is transmitted continuously on the transmitter side, with bit 1 of TS0 at logical 1. The MFAS signal is transmitted in accordance with NMF bit register (CR5 Register): if NMF is programmed to "1" Logic, no MFAS is transmitted; if NMF is programmed to "0" Logic the MFAS signal is transmitted continuously.

Table 2.

| LOF | MFR | MFNR | RECEIVER STATE                                                                           |

|-----|-----|------|------------------------------------------------------------------------------------------|

| 1   | 0   | 0    | FAS or MFAS has been lost.<br>State: Research of FAS                                     |

| 0   | 0   | 0    | FAS has been recovered.<br>State: Research of MFAS                                       |

| 0   | 1   | 0    | Frame and Multiframe recovered State: Good working.                                      |

| 0   | 0   | 1    | Frame recovered. State: Good working without multiframe received from transmitting side. |

#### 6 Interfacing with the microprocessor

The device can work in one of the 3 following modes:

- Parallel microprocessor Interface Mode

- Serial microprocessor Interface Mode

- Without microprocessor: Stand Alone Mode.

The choice is done by means of the SA/Reset, P0 and P1 pins.

#### 6.1 Parallel Microprocessor Interface Mode

The microprocessor can read (or write) the registers of the STLC5432 using the fifteen parallel Interface pins.

The use of TSO (Time Slot Zero) of DIN and DOUT digital multiplex is defined by TSOE bit of CR5 Register.

- If TSOE = 1, TSO on DIN multiplex Input is used to transfer Sa4 to Sa8 bits to the line and TSO on DOUT multiplex output is used to transfer Sa4 to Sa8 bits from the line.

- If TSOE = 0, DOUT output is high impedance during TSO, and DIN Input ignores data during TSO.

#### 6.2 Serial Microprocessor Interface Mode

Fifteen parallel Interface pins are ignored, they are tied to ground. In this mode, the time slots 0 of internal multiplexes are considered like a channel used by the devices and the control entity located in the system to communicate. This channel can be switched across a switching network or not- before its final destination.

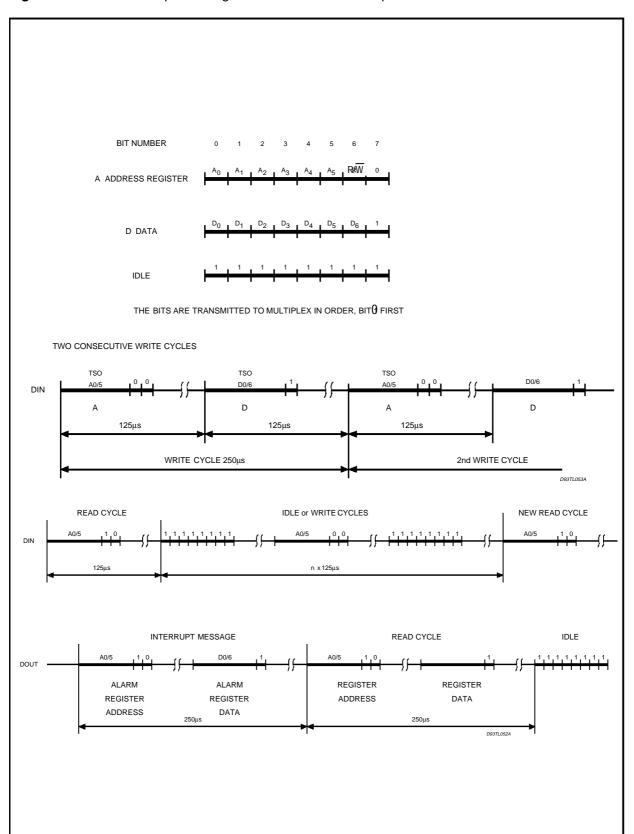

The message is constituted by two bytes which are transmitted on two consecutive Time Slots Zero.

The bits of word are numbered 0 to 7, bit 0 is transmitted first. When the bit 7 of a byte is 0, this byte is the first word of the message.

The bit 6, of the first word, is R/W bit:

R/W = 1. Message to read a register whose address is designated by the following bits of the word ( A 0/5).

R/W = 0. Message to write a register, addressed by the bits A0/5.

The bit 7 of following byte is 1 and the seven D 0/6 bits are data to load into register.

To transfer one message,  $250\mu s$  are necessary. Between two messages, the bits are 1 during TS0. See fig.7 for details.

#### 6.2.1 Reading of a register

The remote entity connected to the DIN and DOUT multiplexes can request reading of a register if it transmits, during TSO, on DIN the address bit A0/5, the R/W bit at 1 and the last bit at 0. The following word, ending with 1, is not taken into account by the device. The device returns two words during TSO of DOUT:

- -The first word begins with 0, R/W bit is put to 1, the address bits of the register are transmitted.

- -The second word begins with 1, then seven data bits of the register are transmitted.

#### 6.2.2 Writing of a register

The remote entity connected to the DIN and DOUT multiplexes can request writing, then it transmits the first bit at 0, the second bit at 0 and the register address A 0/5 during TSO of DIN. The following word begins with 1 and seven next bits are Data to load into register. There is no acknowledge after writing. The writing messages can be transmitted consecutively.

#### 6.3 Stand Alone Mode

Whatever the received frequency on LCLK pin (2.048kHz or 4.096kHz), the device automatically fits and always works at 2.048kHz. When SA pin is at 1, the multiframe research is automatically launched after each lost of frame and the device provides the following alarms on DOUT during the Time Slot 0:

| F/S                      | SKIP | AR                                                                                       | MFNR                     | LOF                           | В                       | AIS | LOS |  |  |

|--------------------------|------|------------------------------------------------------------------------------------------|--------------------------|-------------------------------|-------------------------|-----|-----|--|--|

| LOS<br>AIS<br>B          | ,    | Loss of signal Alarm Indication Signal If LOF = 1, then B = 915 If LOF = 0, then B = WER |                          |                               |                         |     |     |  |  |

| LOF<br>MFN<br>AR<br>SKIF | IR   |                                                                                          | Los<br>Mul<br>A B<br>Jum | s of Fr<br>ti Fran<br>it Rece | rame<br>ne Not<br>eived |     |     |  |  |

Bits definitions are the same than bits definitions of ALR, CAR1 and CAR2 Registers. These bits represent the current state of the line; DIN is ignored during Time Slot Zero.

#### 7 RESET

During Hardware Reset (Pin: SA/RESET):

- All the programmable registers are configurated with the default value.

- Interrupts are not generated (INT PIN is high impedance).

- The research of Multiframe is always active.

At Software Reset (addressing the Reset register):

The registers are configurated with the default value only.

#### After Reset:

The registers may be configurated with any value.

#### **8 INTERRUPT**

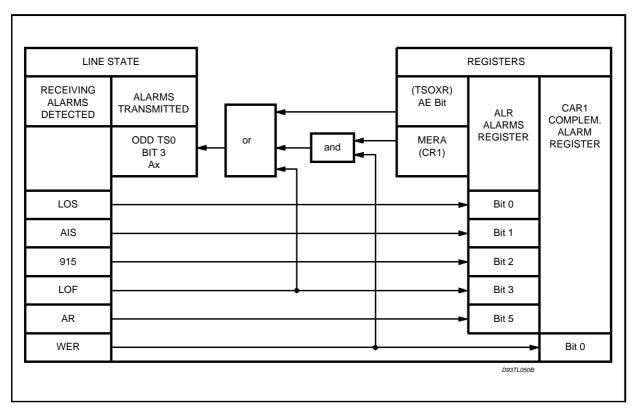

All the bits of Alarm Registers generate an interrupt if they are not masked, except SLC (CAR2).

An alarm generates an interrupt if the mask bit associated is 0. If a temporary event is detected from the line. ALR Alarm Register, CAR1 and CAR2 Complementary Alarm Registers can be read after interrupt or by polling.

In this last case, these Alarm Registers can be considered like particular status registers.

If a temporary event is detected from the line, then the appropriate bit is put to one. After reading by the microprocessor, this bit is put to zero until new event.

If a permanent state occurs, then the appropriate bit is put to one. After reading by the microprocessor, this bit remains at one until disappearance of the cause.

#### 8.1 Parallel Interface Mode

ALR Alarm Register, CAR1 and CAR2 Complementary Alarm Registers can be read after interrupt or by polling.

In this last case, these Alarm Registers can be considered like particular status registers.

INT pin is put to 0 volt. The microprocessor reads Alarm Register.

For example, after reading the ALR and CAR1 registers the microprocessor could act as follows:

- If SC bit (clock 1 second) is 1, then the microprocessor reads fault counter registers.

- If EXT1 bit (EXTENSION 1) is 1, then the microprocessor reads Complementary Alarm Register 1.

- If TSOR (or Sa6R) bit of CAR1 is 1, the microprocessor reads TSORR (or Sa6RR) Register

7

#### 8.2 Serial Interface Mode

When an Alarm bit is put to 1 in ALR (Alarm Register), this bit generates automatically the transmission of two bytes message onto DOUT during Time slot 0 with:

- The first bit of the first byte at 0; the second bit is at 0 and after the address bits of Alarm Register.

- The data of the ALR (Alarm Register) is the second byte.

NB: When TSOR or Sa6R bit of the CAR1 (Complementary Alarm Register 1) is put to "1", it generates a message in which there are address and data of TSORR Register (if TSOR bit is not masked), or address and data of Sa6RR register (if Sa6R is not masked).

If the four occurences to transmit a message are simultaneous, the priority order is:

Priority 1: Transmission of Alarm

Register data if an alarm

has been detected.

Priority 2: Transmission of Register

data after reading message

from remote entity.

Priority 3: Transmission of TSORR

data after loading of this

register.

Priority 4: Transmission of Sa6RR

data after loading of this

register.

#### 8.3 Stand Alone Mode

Interrupts are not generated.

AL0, AL1 pins indicate the current state of three alarms: LOF, AlS, A bit received and DOUT pin indicates the current state of nine alarms during time-slot zero (See Par. 6.3).

Table 3: The registers and their bits.

| ADD<br>(Dec.) | After<br>Reset<br>(Hexa) | Register<br>Name | bit 7 | bit 6 | bit 5  | bit 4      | bit 3       | bit 2     | bit 1   | bit 0 | Read/<br>Write | Page |

|---------------|--------------------------|------------------|-------|-------|--------|------------|-------------|-----------|---------|-------|----------------|------|

| 0             |                          |                  |       |       | •      | NOT        | USED        |           |         |       |                |      |

| 1             |                          | RESET            | 1     |       |        | DUMI       | MY REGIS    | STER      |         |       | W              | 15   |

| 2             | 88                       | ALR              | 1     | EXT1  | AR     | SC         | LOF         | 915       | AIS     | LOS   | R              | 15   |

| 3             | FF                       | AMR              | 1     | MEXT1 | MAR    | MSC        | MLOF        | M915      | MAIS    | MLOS  | R - W          | 15   |

| 4             | 80                       | CAR1             | 1     | EXT2  | 0      | Sa6R       | TS0R        | ER        | CRCF    | WER   | R              | 15   |

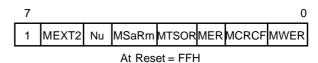

| 5             | FF                       | CAMR1            | 1     | MEXT2 | Nu     | MSa6R      | MTS0R       | MER       | MCRCF   | MWER  | R - W          | 15   |

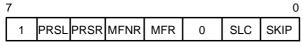

| 6             | 80                       | CAR2             | 1     | PRSL  | PRSR   | MFNR       | MFR         | 0         | SLC     | SKIP  | R              | 16   |

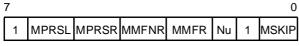

| 7             | FF                       | CAMR2            | 1     | MPRSL | MPRSR  | MMFNR      | MMFR        | Nu        | 1       | MSKIP | R - W          | 16   |

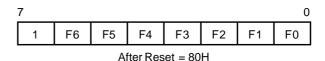

| 8             | 80                       | FCR1             | 1     | F6    | F5     | F4         | F3          | F2        | F1      | F0    | R              | 16   |

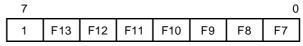

| 9             | 80                       | FCR2             | 1     | F13   | F12    | F11        | F10         | F9        | F8      | F7    | R              | 16   |

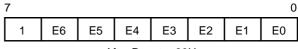

| 10            | 80                       | ECR1             | 1     | E6    | E5     | E4         | E3          | E2        | E1      | E0    | R              | 16   |

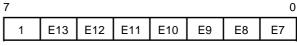

| 11            | 80                       | ECR2             | 1     | E13   | E12    | E11        | E10         | E9        | E8      | E7    | R              | 16   |

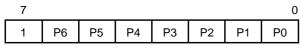

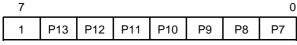

| 12            | 80                       | PCR1             | 1     | P6    | P5     | P4         | P3          | P2        | P1      | P0    | R              | 17   |

| 13            | 80                       | PCR2             | 1     | P13   | P12    | P11        | P10         | P9        | P8      | P7    | R              | 17   |

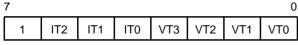

| 14            | B8                       | ERTR             | 1     | IT2   | IT1    | IT0        | VT3         | VT2       | VT1     | VT0   | R - W          | 17   |

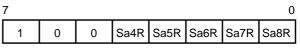

| 15            | 80                       | TS0RR            | 1     | 0     | 0      | Sa4R       | Sa5R        | Sa6R      | Sa7R    | Sa8R  | R              | 17   |

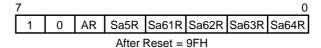

| 16            | 9F                       | Sa6RR            | 1     | 0     | AR     | Sa5R       | Sa61R       | Sa62R     | Sa63R   | Sa64R | R              | 17   |

| 17            | Х                        | RES              |       |       | RES    | ERVED: A   | Avoid Add   | ressing   |         |       |                |      |

| 18            | 9F                       | TS0XR            | 1     | WT    | AE     | Sa4X       | Sa5X        | Sa6X      | Sa7X    | Sa8X  | R - W          | 18   |

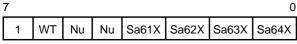

| 19            | 8F                       | Sa6XR            | 1     | WT    | Nu     | Nu         | Sa61X       | Sa62X     | Sa63X   | Sa64X | R - W          | 18   |

| 20            | Х                        | RES              |       |       | RES    | ERVED: A   | Avoid Add   | ressing   |         |       |                |      |

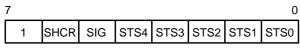

| 21            | 90                       | SIGR             | 1     | SHCR  | SIG    | STS4       | STS3        | STS2      | STS1    | STS0  | R - W          | 18   |

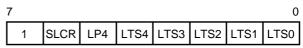

| 22            | 80                       | LP4R             | 1     | SLCR  | LP4    | LTS4       | LTS3        | LTS2      | LTS1    | LTS0  | R - W          | 18   |

| 23            | 84                       | CR1              | 1     | MERA  | LTM    | 8KCR       | MCR1        | MCR0      | SELEX   | SELER | R - W          | 20   |

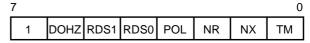

| 24            | 80                       | CR2              | 1     | DOHZ  | RDS1   | RDS0       | POL         | NR        | NX      | TM    | R-W            | 20   |

| 25            | 80                       | CR3              | 1     | ASP   | Nu     | AISX       | ALS         | LP3       | LP2     | LP1   | R - W          | 21   |

| 26            | 80                       | CR4              | 1     | EQV   | AVT    | DEL        | DCP         | M2        | M1      | M0    | R-W            | 21   |

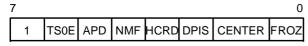

| 27            | 80                       | CR5              | 1     | TS0E  | APD    | NMF        | HCRD        | DPIS      | CENTER  | FROZ  | R - W          | 23   |

| 28            | 80                       | CR6              | 1     | POLSa | OSCD   | SaT        | Sa51        | Sa50      | Sa41    | Sa40  | R-W            | 23   |

| 29            | 80                       | CR7              | 1     | AMI   | Sa81   | Sa80       | Sa71        | Sa70      | Sa61    | Sa60  | R - W          | 24   |

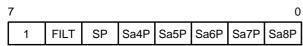

| 30            | FF                       | CR8              | 1     | FILT  | SP     | Sa4P       | Sa5P        | Sa6P      | Sa7P    | Sa8P  | R - W          | 24   |

| 31            | Х                        | RES              |       |       | RES    | ERVED: A   | Avoid Add   | ressing   |         |       |                |      |

| 32            | 80                       | TCR1             | 1     | SGV   | GTS5   | GTS4       | GTS3        | GTS2      | GTS1    | GTS0  | R - W          | 25   |

| 33            | 80                       | TCR2             | 1     | SAV   | ATS5   | ATS4       | ATS3        | ATS2      | ATS1    | ATS0  | R - W          | 25   |

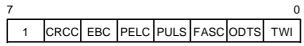

| 34            | 80                       | TCR3             | 1     | CRCC  | EBC    | PELC       | PULS        | FASC      | ODTS    | TWI   | R - W          | 26   |

| 35            | to 63                    |                  |       |       | Reserv | ed for the | die test: A | Avoid Add | ressing |       |                |      |

Nu = Not used.

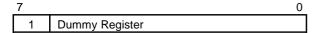

#### 9.1 Reset Register

The software reset of the circuit is performed when this register is addressed whatever the value of its bits may be. Reading or writing is irrelevant. All the programmable registers are configurated by the default value indicated in each register description and the mechanism of multiframe is launched in accordance with the procedure described in the introduction.

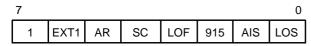

#### 9.2 ALR: Alarm Register

After Reset = 88H

LOS Loss of Signal.

This bit is set to 1 when ten consecutive zeros have been detected before the HDB3/BIN decoder.

AIS Alarm Indication Signal:

this bit is set to 1 in accordance with G.775 when the incoming signal is received with only two, or less, zero for two consecutive double frame period (i.e. 512 x 2 bit).

915 This bit is set to 1 when 915 errored CRC message blocks have been received within 1 second.

LOF Loss of Frame Alignment Word. When at 1, the synchronization is lost.

SC One second Clock.

This bit is set to one every second when there is synchronization. The number of faults which have been counted during the previous second is in fault counters FCR, ECR and PCR.

AR A bit Received.

This bit is set to 1 when the bit 3 of the odd time slot zero has been received consecutively two times at 1.

EXT1 Extension bit 1.

This bit is set to 1 when one bit out of CAR1 Register bits is put to 1.

This register can be written or read.

When a bit of this register is set to 1, the corresponding bit of the ALR register, which has the same number, is masked and an interrupt cannot be generated by this bit.

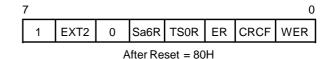

#### 9.4 CAR1: Complementary Alarm Register 1

WER Frame Word Error Rate.

This bit is at "1"when the threshold of fault condition has been reached; this bit is at "0" when the threshold of deactivating has been reached. These two thresholds are indicated by the error Rate Threshold Register (ERTR). The Error Rate function is validated when the synchronization is achieved.

#### CRCF CRC Frame.

After remultiframe time, this bit is at "1" when an eight frame block has been received with an error.

ER E Bit received.

ER bit is at "1" during the frame 13 received when the E1 bit value of the same frame 13 is zero.

ER bit is at "1" during the frame 15 received when the E2 bit value of the previous frame 15 is zero (E1 and E2 = first bit of time slot zero in frames 13 and 15 respective).

TS0R Time slot Zero Register.

This bit is at "1" when the TS0RR Register has been loaded in accordance with CR8 register and bit POLSa(CR6 register).

Sa6R Sa6R Register.

This bit is put to one when Sa6RR Register has been loaded in accordance with SaT bit (CR6 Register).

EXT2 EXTENSION Bit 2

This bit is at "1" when one bit out of CAR2 Register bits has been set to "1".

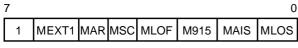

#### 9.3 AMR Alarm Mask Register

After Reset = FFH

#### 9.5 <u>CAMR1 Complementary Alarm Mask</u> <u>Register 1</u>

This register can be read or written.

When a bit of this register is at "1", the CAR1 Register bit which has the same number is masked. The CAR1 bit which is masked do not generate an interrupt.

#### 9.6 CAR2: Complementary Alarm Register 2

After Reset = 80H

SKIP SKIP.

After frame recovery, this bit is at "1" when an entire frame (32 words) has been ignored or has been repeated two times onto DOUT.

SLC Slow Local Clock.

This bit does not generate interrupt.

When the value of this bit is 0, local clock is faster than the remote clock.

When the value is "1", local clock is slower

When the value is "1", local clock is slower than the remote clock (an entire frame has been ignored).

MFR Multiframe recovered within 400 ms. After reframe time, if the multiframe is recovered within 400 ms, MFR is set to "1".

MFNR Multiframe Not recovered within 500 ms.

After reframe time, the circuit researches the multiframe during 500 milliseconds.

After this time, if the multiframe has not been recovered, MFNR is set at "1". Then the circuit is activated with the frame recovery only, and the AX bit (bit 3 of the odd Time Slot Zero transmitted) is set at "0".

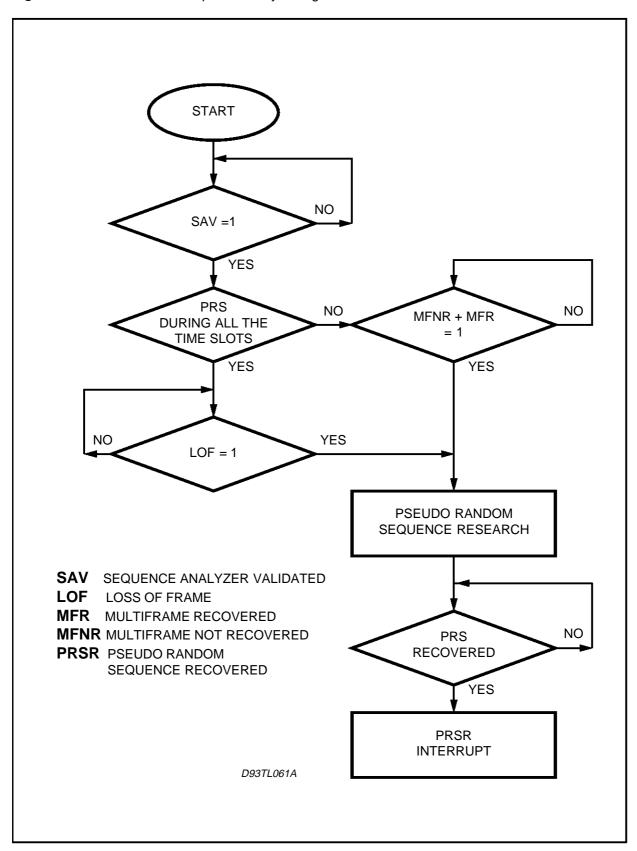

PRSR Pseudo Random Sequence Recovered. When the PRS analyzer is validated (SAV = 1), PRSR bit is set at "1" if the synchronization is performed.

PRSL Pseudo Random Sequence Lost. PRSL, this bit is set to "1" when PCR1/2 (PRS Counter Register) has reached 2<sup>14</sup> detected faults.

#### 9.7 <u>CAMR2: Complementary Alarm Mask</u> Register 2

After Reset = FFH

This register can be read or written. Bits: MMFNR, MMFR and MSKIP mask respectively bit MFNR, MFR and SKIP when they are at "1".

#### 9.8 FCR1: Fault Counter Register 1

F0/6 7 less significant bits of the FCR counter.

#### 9.9 FCR2: Fault Counter Register 2

After Reset = 80H

F7/13 7 most significant bits of the FCR counter.

If POL bit of CR2 register is at "0", the value of 14 bits fault counter is loaded into these registers each second. If POL = 1, the registers are resetted after each access. (POL indicates the difference between polling mode and interrupt mode, see also CR2 register).

When the multiframe has not been recovered within 400ms (MFNR = 1), these two registers indicate the number of errored bits of Frame Alignment Signal received over one second period.

When the multiframe is recovered, these two registers indicate the number of errored CRC blocks received over one second period.

#### 9.10 ECR1: E Bit Counter Register 1

After Reset = 80H

E 0/6 7 less significant bits of ECR counter

#### 9.11 ECR2: E Bit Counter Register 2

After Reset = 80H

E 7/13 7 most significant bits of the ECR counter

ECR1 and ECR2 are two registers associated to ECR counter. Each second, the value of the counter is loaded into these register (POL = 0).

When the multiframe is recovered, these two registers indicate the number of errored E bits received over 1 second period.

#### 9.12 PCR1: PRS Counter Register 1

After Reset = 80H

P0/6 7 less significant bits of the Pseudo Random Counter Register.

#### 9.13 PCR2: PRS Counter Register 2

After Reset = 80H

P7/13 7 most significant bits of the Pseudo Random Counter Register.

PCR1 and PCR2 are two registers associated to Pseudo Random Sequence Counter.

When the Pseudo Random Sequence Analyser is validated, the counter indicates the number of erroneus bits received after the synchronisation of the Pseudo Random Sequence.

#### 9.14 ERTR: Error Rate Threshold Register

After Reset = B8H

VT 0/3 Error Rate Validation Threshold of WER. VT0/3 bits give the threshold of activating the indication of Alarm for erroneous Frame Alignment words.

Alignment words.

WER is set to "1" only if the fault condition is confirmed within the following 2 seconds

| VT3 | VT2 | VT1 | VT0 | Number of erroneous<br>Frame Alignement<br>words received during<br>2 seconds |

|-----|-----|-----|-----|-------------------------------------------------------------------------------|

| 0   | 0   | 0   | 0   | 16                                                                            |

| 0   | 0   | 0   | 1   | 18                                                                            |

| 0   | 0   | 1   | 0   | 20                                                                            |

| 0   | 0   | 1   | 1   | 22                                                                            |

| 0   | 1   | 0   | 0   | 24                                                                            |

| 0   | 1   | 0   | 1   | 26                                                                            |

| 0   | 1   | 1   | 0   | 28                                                                            |

| 0   | 1   | 1   | 1   | 30                                                                            |

| 1   | 0   | 0   | 0   | 32                                                                            |

| 1   | 0   | 0   | 1   | 36                                                                            |

| 1   | 0   | 1   | 0   | 40                                                                            |

| 1   | 0   | 1   | 1   | 44                                                                            |

| 1   | 1   | 0   | 0   | 48                                                                            |

| 1   | 1   | 0   | 1   | 52                                                                            |

| 1   | 1   | 1   | 0   | 56                                                                            |

| l 1 | 1   | 1   | l 1 | 60                                                                            |

IT 0/2 Error Rate Inhibition Threshold of WER

IT 0/2 bits give the threshold of deactivating

the indication of Alarm. Per default, WER is

set at "0" when 12 or less erroneous

Frame Alignment Words are detected.

The Alarm deactivation requires the confirmation of the condition for the following 2 sec.

| IT2 | IT1 | IT0 | Number of erroneous<br>Frame Alignment words<br>received during 2 seconds |  |  |  |

|-----|-----|-----|---------------------------------------------------------------------------|--|--|--|

| 0   | 0   | 0   | 8                                                                         |  |  |  |

| 0   | 0   | 1   | 9                                                                         |  |  |  |

| 0   | 1   | 0   | 10                                                                        |  |  |  |

| 0   | 1   | 1   | 12                                                                        |  |  |  |

| 1   | 0   | 0   | 14                                                                        |  |  |  |

| 1   | 0   | 1   | 16                                                                        |  |  |  |

| 1   | 1   | 0   | 20                                                                        |  |  |  |

| 1   | 1   | 1   | 24                                                                        |  |  |  |

NB: If the threshold value of deactivating the indication of Alarm is superior to threshold value of activating the indication of Alarm, then the value of deactivating is irrelevant.

#### 9.15 TS0RR: Time Slot Zero Received Register

After Reset 80H

Sa4R to Sa8R Bits 4 to 8 of the odd Time Slot Zero (Sa4 to Sa8) received from the line. During reframe time, these bit are at "1". Sa4R to Sa8R fix the content of TS0RR in accordance with CR8 Register and bit POLSa (CR6 register)

#### 9.16 Sa6RR: Sa6 Bits Receive Register

Sa61R to Sa64R

These four bits are received from Sa6 subchannel.

When a new word constituted by these four bits is detected in accordance with SaT (CR6 Registers), a Sa6R interrupt is generated (a new word can occur each millisecond).

Sa5R. This bit is the same as Sa5R in TS0RR register.

AR A bit received. It's the same bit than the AR bit of ALR register (see 9.2).

#### 9.18 TS0XR: Time Slot Zero transmit Register

7 0 1 WT AE Sa4X Sa5X Sa6X Sa7X Sa8X

After Reset = 9FH

Sa4X to Sa8X Bits 4 to 8 of each odd Time Slot Zero to be transmitted onto the line in accordance with CR6 and CR7

AE A bit to transmit.

AX bit to be transmitted onto the line is given by the logical "or" of LOF (Loss of Frame), WER (if the bit MERA is at 0, CR1 register) and AE (see fig 5).

AX(Odd TS0 Bit3) = AE + LOF + WER NOT MERA

WT Word to Transmit. This bit is read only.

First Case FILT = 1.

After TS0XR writing by microprocessor with WT = 1, WT is resetted at "0" after three consecutive transmissions of Sa4X to Sa8X bits onto the line.

Second Case FILT = 0.

After TSOXR writing by microprocessor with WT = 1, WT is resetted at "0" after one transmission of bits located in TSOXR register.

#### 9.19 Sa6XR: Sa6 Bits Transmit Register

After Reset = 8FH

Sa61X, Sa62X, Sa63X, Sa64X

These four bits are transmitted on subchannel Sa6 in accordance with CR6 and CR7 Registers.

WT Word to Transmit. This bit is read only.

First Case SaT = 1.

After Sa6XR writing by microprocessor, WT = 1. WT is resetted at "0" after three consecutive transmissions of Sa61X to Sa64X bits onto the line.

Second Case SaT = "0".

After Sa6XR writing by microprocessor, WT = 1, WT is resetted at "0" after one transmission of bits located in Sa6XR Register.

#### 9.21 SIGR: Signalling Register

After Reset = 90H

STS 0/4 Signalling Time Slot 0/4:

these five bits indicate which time Slot out of 32 to transmit and to receive on BRD0 and BXDI pins respectively, when SIG bit is at 1.

SIG Signalling Validated.

#### Receiver Side:

When SIG is at "1", the contents of Time Slot selected appear on the BRDO pin at 64 kb/s and its clock associated o the RCLO pin at 64kHz.

When SIG is at "0", the contents of 32 Time slots received appear onto BRDO pin at 2 048 kb/s and clock associated onto RCLO pin at 2 048 kHz.

#### transmitter side:

When SIG is at "1", a bit stream at 64 kb/s on BXDI pin will be introduced into time Slot, selected by STS0 to STS4 bits, to the line. The bit stream on the input BXDI pin is clocked by clock at 64KHz delivered by BXDO pin (BXDI pin is an input and BXDO pin is an output).

When SIG is at "0", the bit stream at 2 048 kb/s on BXDI pin will be introduced into 32 Time Slots to the line.

SHCR: Synchronization of High Clock Received.

If DPIS (CR5) = 0:

SHCR = 1, DPLL receives RCLI signal

from RCLI pin.

SHCR = 0, DPLL receives the remote clock

recovered from the line.

If DPIS (CR5) = 1:

SHCR is not taken into account.

| DPIS | SHCR | Source of the signal at the DPLL input: |

|------|------|-----------------------------------------|

| 0    | 0    | line                                    |

| 0    | 1    | RCLI pin                                |

| 1    | 0    | DPI pin                                 |

| 1    | 1    | DPI pin                                 |

#### 9.22 LP4R: Loop Back 4 Register

After Reset = 80 H

LTS 0/4Loo Back time Slot 0/4:

these five bits indicate which time slot out of the 32 is selected for the loopback.

LP4 Loopback 4