## **MPA1000 Product Description**

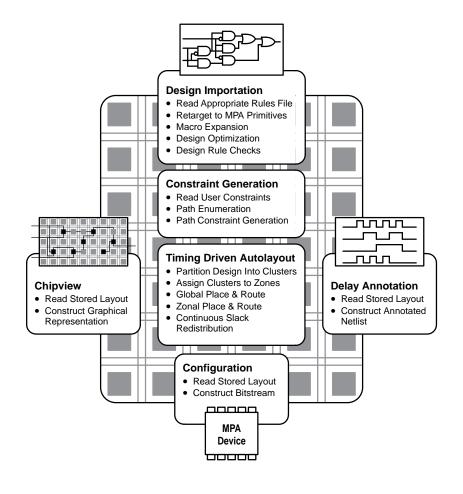

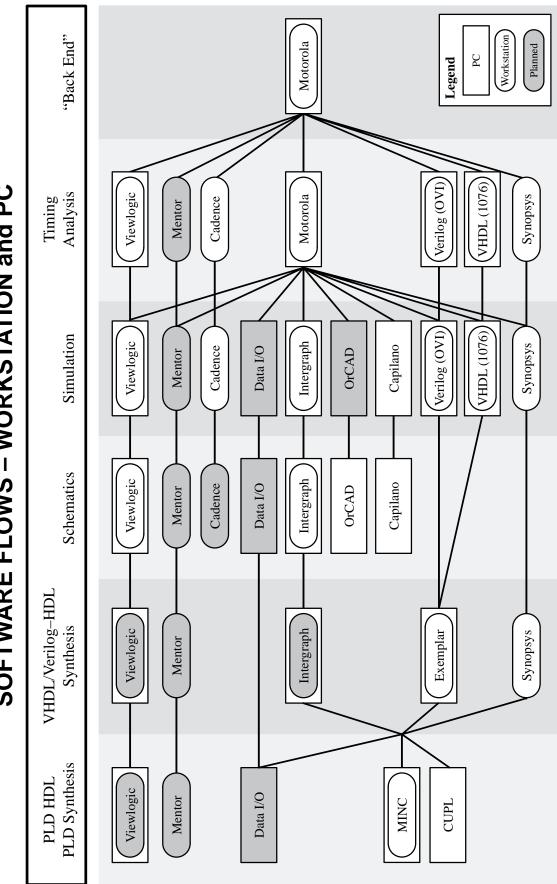

Motorola Programmable Array (MPA) products are a high density, high performance, low cost, solution for your reconfigurable logic needs. When used with our automatic high performance design tools, MPA delivers custom logic solutions in minutes rather than weeks. And the low cost keeps those solutions competitive throughout the product lifecycle.

The MPA architecture has solved the historical problems associated with fine grain devices without sacrificing re–programmability, reliability, or cost. MPA1000 devices are reprogrammable SRAM based products manufactured on a standard 0.5 $\mu$  Leff CMOS process with logic capacities from 3,500 to more than 22,000 equivalent FPGA gates. MPA Logic resources hold a single gate or storage element providing a highly efficient, adaptable, design implementation medium. Gate level logic resources, abundant hierarchical interconnection resources and automatic, timing driven, tools work together to quickly provide design implementations that meet timing constraints without sacrificing device utilization.

Staying focused on end product design rather than implementation tools or device architecture gets the design done faster and, unlike other programmable solutions, without programmable logic device specificity to impede future design migration efforts. The combination of automatic tools and gate level architecture is ideal for traditional schematic driven or high level language based design methodologies. In fact, logic synthesis tools were originally designed for and produce the most efficient results when targeting gate level devices.

High MPA1000 register count and controlled clock skew is ideal for designs employing pipelining techniques such as communications. The unique set of MPA1000 I/O programming options make these devices suitable for industrial and computer Interfacing circuits.

#### Features

- Multiple I/O from 80-200 I/O Pins

- Programmable 3V/5V I/O at Any Site

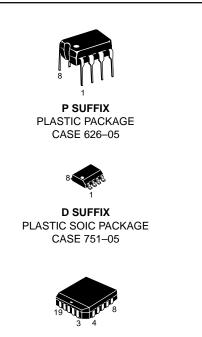

- Multiple Packaging Options

- Fine Grain Structure Is Optimized for Logic Synthesis

- Programmable Output Drive, 6/12mA @ 5.0V

- High Register Count, with 560–2,900 Flip–Flops

- IEEE 1149.1 JTAG Boundary Scan

- Eight Low–Skew (<1ns) Clocks

|               | •                                                |                |                        |                        |                         |                                                            |                                 |

|---------------|--------------------------------------------------|----------------|------------------------|------------------------|-------------------------|------------------------------------------------------------|---------------------------------|

| FPGA<br>Gates | Part No.                                         | Logic<br>Cells | Internal<br>Flip–Flops | I/O Cell<br>Flip–Flops | Signal I/O<br>Pads Max. | Packages                                                   | Availability                    |

| 3500          | MPA1016FN<br>MPA1016DD                           | 1600           | 400                    | 160                    | 80                      | 84–Pin PLCC<br>128–Pin PQFP                                | April 1996<br>April 1996        |

| 8000          | MPA1036FN<br>MPA1036DD<br>MPA1036DH<br>MPA1036HI | 3600           | 900                    | 240                    | 120                     | 84–Pin PLCC<br>128–Pin PQFP<br>160–Pin PQFP<br>181–Pin PGA | NOW<br>April 1996<br>NOW<br>NOW |

| 14200         | MPA1064DH<br>MPA1064DK<br>MPA1064KE              | 6400           | 1600                   | 320                    | 160                     | 160–Pin PQFP<br>208–Pin PQFP<br>224–Pin PGA                | April 1996<br>2Q96<br>1Q96      |

| 22000         | MPA1100DK<br>MPA1100HV                           | 10000          | 2500                   | 400                    | 200                     | 208–Pin PQFP<br>299–Pin PGA                                | 3Q96<br>3Q96                    |

#### Table 2–1. MPA1000 Family Members

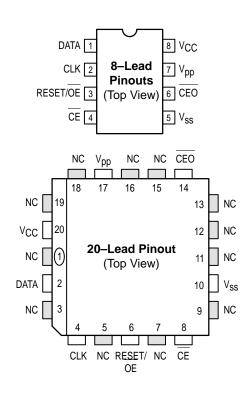

#### MPA17000 Serial EPROM Family

| Capacity | MPA1000 Companion | Part No.                             | Packages                               | Availability |

|----------|-------------------|--------------------------------------|----------------------------------------|--------------|

| 64K      | MPA1016           | MPA1765P<br>MPA1765D<br>MPA1765FN    | 8–Pin DIP<br>8–Pin SOIC<br>20–Pin PLCC | NOW          |

| 128K     | MPA1036           | MPA17128P<br>MPA17128D<br>MPA17128FN | 8–Pin DIP<br>8–Pin SOIC<br>20–Pin PLCC | NOW          |

| 256K     | MPA1064           | MPA17256FN                           | 20–Pin PLCC                            | 1996         |

#### **MPA1000** Capacity

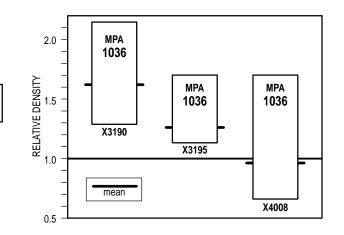

Programmable logic gate capacity is difficult to ascertain because it is design and design tool dependent. Programmable logic capacities can only be meaningfully compared using identical designs and automatic tools. Figure 2–1 shows that under these circumstances, the MPA1036 contains from 2.1 to 1.3 Xc3190 devices.

Figure 2–1. Equivalent Gate Capacity

Table 2–1 on page 2–7 shows the members of the MPA1000 family and lists the I/O, logic cell, flip flop and gate capacities for each device. To facilitate Customer device selection, Motorola rates MPA device capacity in FPGA equivalent gates. The equivalent gate counts shown were derived using identical designs and a push button implementation methodology. While this method is useful in a comparative sense, actual device capacity remains a design dependent quantity. Designs with high register gate or XOR gate to total gate ratio will pack more efficiently than the averages shown in Figure 2–1.

#### **MPA1000** Performance

Device performance is more design and design tool dependent than device capacity. Table 2–2 shows selected cell performance figures for a typical MPA1000 device. Calculating MPA1000 DFF toggle rate from this information yields an unrealistically high expectation for device performance. Some manufacturers publish specifications for small functional blocks like counters. While more useful than toggle rates, they are based on ideal placement and routing conditions seldom achievable without manual intervention. Industry benchmarks are useful for relative comparisons of benchmark design performance, but benchmark designs don't end up in products. In addition, the design methodology used requires, manual, architecture dependent, design optimization and expert level architectural and design tool

expertise. Using this design methodology for real designs means a costly learning curve, severe technology migration limitations and many hours of extra design effort for each end product. If the incentive to use a programmable solution is time to market and product flexibility, this is not the ideal approach. A push button, gate level, approach increases design flexibility and improves time to market. The MPA1000 and MPA design system have been engineered to deliver a high performance gate level solution. Gate level design is widely understood, technology independent and synthesis friendly. A library of common MSI functions with optimized gate level representations are provided to reduce design implementation time.

|                         | Typical |

|-------------------------|---------|

| MEDIUM BUS DELAY        | 1.2ns   |

| DFF CLK TO Q            | 1.2ns   |

| DFF SETUP TIME          | 1.5ns   |

| TYPICAL DFF TOGGLE RATE | 256MHz  |

Table 2–2. Selected MPA1000 Performance Figures

(25° C, V<sub>CC</sub> = 5V)

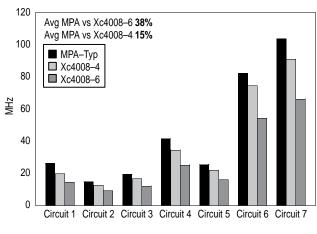

If identical designs and timing constraints are used with automatic, timing driven, design tools, a more appropriate performance comparison can be made. Figure 2–2 compares the MPA1036 vs. the XC4008 for 7 designs. The typical MPA1036 device is 48% faster than the XC4008–6 and 28% faster than the XC4008–4 for 7 identical, complex, chip level designs. In real design situations, gate level flexibility and hierarchical routing coupled with sophisticated, timing driven, design tools results in significant performance gains and reduced time to market.

Figure 2–2. MPA1036 versus XC4008 – 7 Push Button Designs

If step and repeat style designs typical of industry benchmarks are used (Figure 2–3), MPA retains it's performance edge. While the performance gap shrinks by about 10%, absolute design performance increases dramatically compared to those shown in Figure 2–2. As critical path depth decreases, design performance increases as expected. In general these benchmarks tend to have narrowly distributed performance constraints and shallow path depths atypical of many real design implementations. In either case using benchmark information to estimate product performance for arbitrary designs is unlikely to yield reliable results. This information is intended to illustrate the range of performance enhancement possible when MPA is selected.

Figure 2–3. MPA1036 versus XC4008 – 7 Push Button, Step & Repeat Designs

## **MPA1000** Architectural Overview

#### **MPA1000** Architecture

MPA1000 is a high density, high performance, low cost device family which maximizes application flexibility and minimizes time to market by delivering a gate level reprogrammable logic solution. Combined with automatic high performance design tools, the MPA1000 family is ideally suited to logic synthesis or gate level (gate array like) design methods.

Logic resources in the MPA1000 are fine grained – each logic cell holds a single gate or a storage element. This provides a highly efficient, adaptable, design implementation medium. Gate level logic resources, abundant hierarchical interconnection resources and automatic, timing driven, tools work together to quickly provide design implementations that meet timing constraints without sacrificing device utilization.

The MPA1000 architecture has solved the historical problems associated with fine grain architectures without sacrificing re-programmability, reliability, or cost. Previous reprogrammable fine grain architectures utilized routing architectures substantially similar to that of coarse grained products. Other fine grained architectures resorted to antifuse programming elements to address performance issues, increasing cost, while reducing reliability and abandoning reconfigurability. MPA utilizes a new routing structure which takes advantage of fine logic block granularity to achieve superior design performance.

MPA1000 devices are manufactured using a standard submicron CMOS process. SRAM cells comprise device configuration memory. MPA1000 devices can be quickly and infinitely reprogrammed.

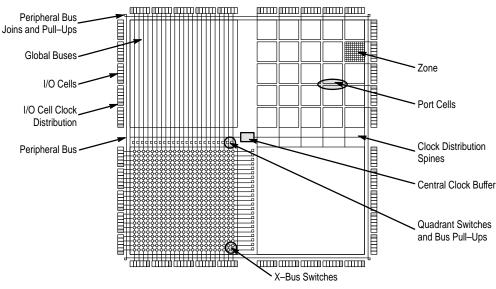

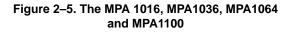

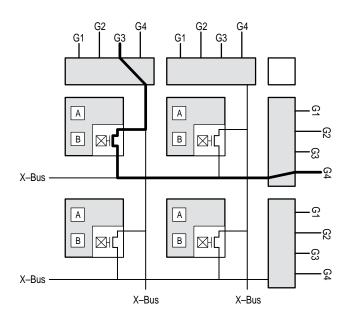

Figure 2–4. MPA Architectural Overview

#### **Partitioned Resources**

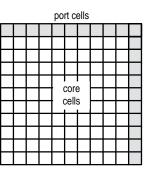

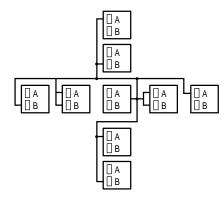

Each device is a multilevel partitioned array of cells. At the highest level of hierarchy each device is partitioned into 4 equal sized sections called quadrants. I/O cells surround the quadrants. Each quadrant is further subdivided into zones. A zone consists of a 10x10 array of core cells, 20 port cells and a clock distribution cell (Figure 2–6). Zone core cells are organized into 2x2 groups called tiles. The number of zones per quadrant defines a particular device as shown in Figure 2–5. Partitioning the device in this manner minimizes bus loading and provides an opportunity to segment device level placement and routing. This speeds design implementation time, especially if multiple processors are used. Figure 2–4 is a synopsis of the overall MPA structure.

| MPA1016 | MPA1036 |

|---------|---------|

|         |         |

| MPA1064 | MPA1100 |

Hierarchical functionality complements the robust routing resource to deliver extremely efficient design realizations. While the look up table approach of non-gate level devices can provide any function of its inputs, this flexibility is costly when simple functions are required. In contrast the simplicity, small size, and hierarchical organization of the MPA1000 delivers a more silicon efficient implementation. Logic blocks of arbitrary size and aspect ratio are automatically constructed, optimized and interconnected based on design constraints and gate level design representations. This capability complements logic synthesis technology and maximizes design migration potential. As FPGA device capacity increases, design diversity will also increase. The malleable granularity and adjustable routing resource of the MPA can accommodate this diversity with consistent silicon efficiency and performance.

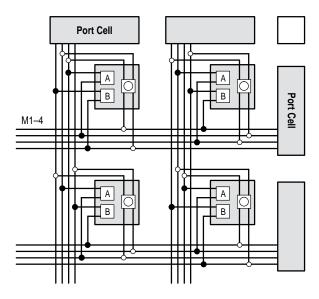

Figure 2–6. Zone Structure

#### Core Cells

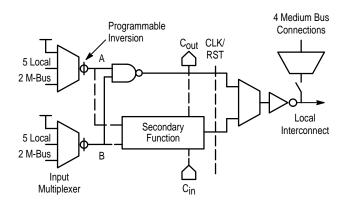

Each core cell has 2 inputs, each input is configured to receive signals from 1 of 7 potential sources (Figure 2–7). 5 sources are from local interconnect and 2 are from zone level interconnect. Each cell output connects to 8 other cells via local interconnect and is configured to connect to up to 4 medium buses. Cells are sometimes used to provide additional routing resource. The ability to use a core cell as a routing resource or as logic provides a programmable means of adjusting routing resource to fit design specific requirements.

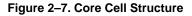

Each cell has three states; repowering buffer, primary function, and secondary function. In addition, all cell inputs have programmable input inversion. MPA1000 core cells are organized in 2x2 groups called tiles. Within a tile, each of the 4 cells has a different secondary function (Figure 2-8). The core cell primary function is a 2 input NAND. Secondary functions include; XOR, register, and wired OR. The register element are configured as a DFF or latch with clock enable and set or reset. There is also special circuitry which used to group the blocks together to form compact multi-cell functions like; 1 bit full adder, 2 input multiplexer, JKFF. A special, 1ns skew, network is provided to drive register clock and reset/set pins. High performance, gate level, cells necessitate controlled clock skew to avoid negative setup time situations. The MPA cell states were chosen based on a careful analysis of macrocell utilization statistics from a large number of ASIC designs implemented in Motorola's H4C array.

Figure 2–8. Core Cell Secondary Function

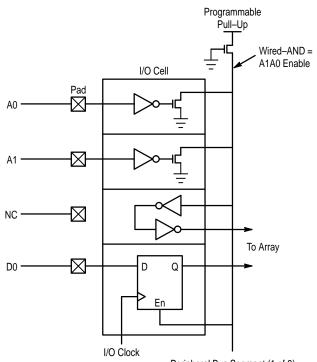

#### I/O cells

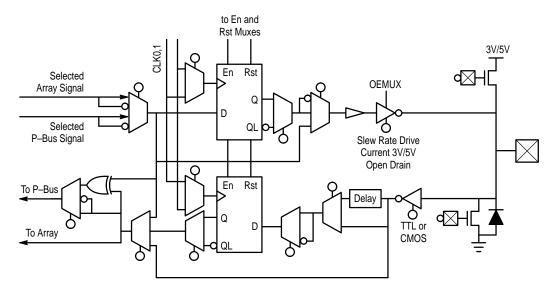

I/O cells are located at the device periphery surrounding the quadrants (Figure 2–4 on page 2–9). Besides direct input and output, each I/O cell is configured to be; input, output, bidirectional, registered input, registered output, registered I/O. The two registers can be independently configured as a latch or D–type flip flop. Input register setup time is adjustable to compensate for clock network input delay. Input buffer threshold adjustment provides either TTL or CMOS levels. Output buffer drive capability is programmable to 6ma or 12ma. And each output can be independently programmed to either 3V or 5V levels with slew rate control. True 3V outputs are useful for system level designs containing any 3V devices which are tolerant to 5V inputs. The output buffer can be configured as an open drain to facilitate system level wired OR applications. Figure 2–9 sums up I/O cell structure. Dedicated, fully IEEE 1149.1 compliant boundary scan is also provided.

#### **Hierarchical Routing Resources**

The MPA interconnection structure is partitioned into 3 levels; Global, Zonal (or medium), and Local. Local interconnection is used to connect a core cell to 8 of it's perpendicular neighbors (Figure 2-10). Zonal interconnect consists of the medium buses and connects groups of cells within a zone (Figure 2-11). Global interconnect includes global buses, x buses and interquadrant switches (Figure 2-4 on page 2-9). Global buses provide quadrant and chip level inter-zone and zone to I/O cell interconnections. Special interconnection resources are also present and consist of clock distribution, wired OR and peripheral bus. Routing specialization provides an opportunity for level specific performance optimization. Specialization also diminishes the amount of interconnection options required at each core cell, reducing cell size and boosting silicon efficiency.

#### Local Interconnect

Local interconnect provides the fastest path between 8 neighboring core cells. Local interconnect is continuous across the device and is not effected by zonal boundaries. Local interconnection favors frequently used connections, the cell to the immediate left and immediate right of the driving cell have 2 connections. Local connections are used for high performance intrazone connections and are also used to cross zone boundaries when necessary.

Figure 2–9. Input/Output Cell Structure

Figure 2–10. Local Interconnect

#### Medium Interconnect

Medium interconnect spans a single zone and provides intrazone connections beyond the span of local interconnect or for connection of zone cells to global signals through the port cells. There are 4 horizontal and 4 vertical medium buses per core cell. Medium bus connectivity to core cells is sparse to minimize loading and limit core cell input multiplexer size. This connectivity is arranged so that a tile can be fully connected to the 16 medium buses which cross it.

Figure 2–11. Medium Interconnect

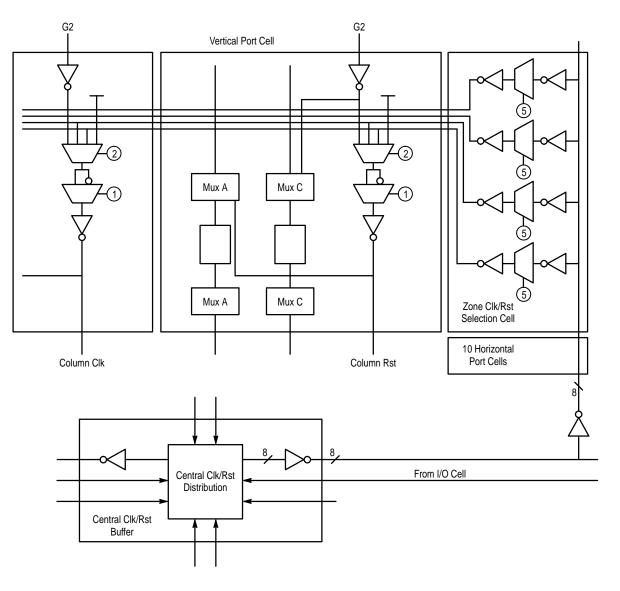

#### Port Cells

At zone edges, port cells provide a bridge between global resources and zonal resources. Port cells transport signals into and out of a zone and are the only interface between zonal and global resources (Figure 2–12). All 4 medium buses, 4 global buses and the x bus in a given row or column connect to the port cell.

Port cells also provide connections to 4 of the 8 low skew clock distribution lines which span the device. Port cells also provide global to x bus access and serve as a pathway for zonal wired OR buses to connect to global busses.

Figure 2–12. Vertical Port Cells

#### **Global Interconnect**

Global interconnect consists of global buses, x buses, interquadrant switches. There are 4 horizontal and 4 vertical global buses passing over each core cell. All Global buses only connect to the port cells, I/O cells and interquadrant switches. Global buses span a quadrant and are used to interconnect the zones within the quadrant together. Between quadrants, interquadrant switches connect two global buses together to form a device level connection.

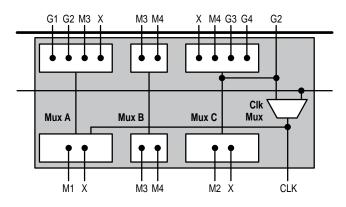

Each core cell contains a x-bus switch (Figure 2–13) which is independent of cell logic or interconnect functions. A single vertical and a single horizontal x bus passes over each core cell and connects to this switch. Each x bus connects to all the core cells is a single zone column or row and terminates at the port cells on opposite edges of the zone. Each x bus has 10 connections inside the zone and 2 port cell connections. Port cell connections are used to make x to global, x to x and medium to x connections. Medium to x connections are used to hop over a single zone X buses are used to facilitate  $90^{\circ}$  global bus turns and provide a means for global bus fanout.

Figure 2–13. Global Bus Turn Using the X–Bus

Peripheral Bus Segment (1 of 8)

Figure 2–14. Using the Peripheral Bus for Address Decoding

#### I/O Cell Connections and Peripheral Bus

I/O cells are a pathway between array and bonding pads. Global buses, x buses and adjacent zone medium buses can be connected to I/O cells at quadrant edges. Each I/O cells is directly connected to the adjacent bonding pad.

A specialized bus, called the peripheral bus, resides in the I/O cell – quadrant interface (Figure 2–4 on page 2–9). The peripheral bus comprises 8 lines which are interrupted at device corners by a peripheral bus switch similar to the interquadrant switch. This switch joins peripheral bus segments to create connections spanning more than a single device edge. Peripheral buses carry I/O control signals common to two or more I/O cells such as a latch enable or tristate control signal. The I/O cells can also drive these buses with an open drain device. When combined with programmable pullups located in the corners of the device, the peripheral bus can be used to form wide gates for address decoding (Figure 2–14).

#### Wired OR Nets

Wired OR nets are constructed using type 1 core cells. When the type 1 secondary function is enabled, the NAND drives an open drain device directly connected to a special bus shared by all the type 1 cells in the same zone row. This bus, the zone wired OR bus, terminates in the port cell and has a single, dedicated, pullup. When this bus is used, the port cell wired OR to global bus connection and the global bus pullup located near the interquadrant switch are enabled. These resources are used to map 3–state buses onto the MPA1000 device.

#### **Clock Distribution**

Clock distribution is implemented through a dedicated, low skew, network consisting of; 8 dedicated clock input lines connected to 2 I/O cells on each device edge, a central clock buffer, a distribution comb structure, zone corner clock selection cells and the zone port cells along the top of each zone. The zone corner cell selects 2 of the 8 lines for zone clocks and 2 of the 8 lines for zone reset (Figure 2–15). Zone registers are connected to these clock and reset signals through the top row of port cells. The comb extends into the I/O cells via a similar clock selection cell attached to each group of 5 I/O cells. This group is called an I/O zone. All 8 clock lines can be driven from the I/O bonding pad or the array. The distribution network is balanced and has a skew of < 1ns between any two register clock inputs.

Connections in the port cells allow the clock network to drive zone logic in addition to the register clock and reset pins. Unused clock lines can be used for efficient distribution of any high fanout signal. If there are more clocks in the design than clock resources, the MPA design system automatically constructs a comb from global buses to generate a secondary clock network with a skew of < 3ns. Secondary clock construction is facilitated by a port cell connection which provides non–clock network access to zone register clock and reset pins.

Figure 2–15. Clock Distribution Network Connectivity

## **MPA1000** Device Configuration

#### **Configuration Overview**

MPA1000 devices have an SRAM configuration memory. Configuration memory contents completely define MPA device function. The MPA1000 design system generates configurations from completed layouts. On chip control logic loads configurations in one of two modes automatically on power up or under external control. MPA1000 devices have a very rapid configuration load cycle, infinite reload and are in system reconfigurable. The configuration modes are; Boot From ROM (BFR) and microprocessor peripheral or MICRO Mode. In either mode, multiple devices can be daisy chained to form a large programmable subsystem.

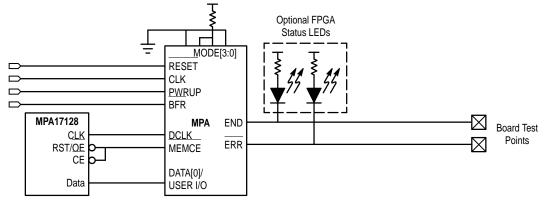

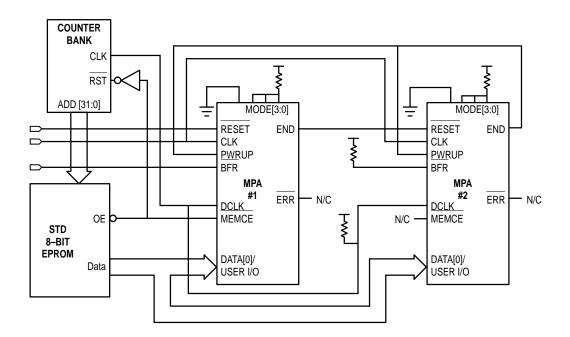

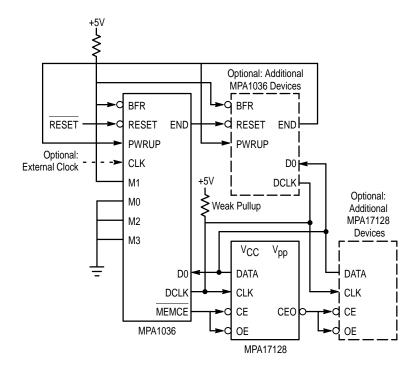

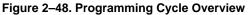

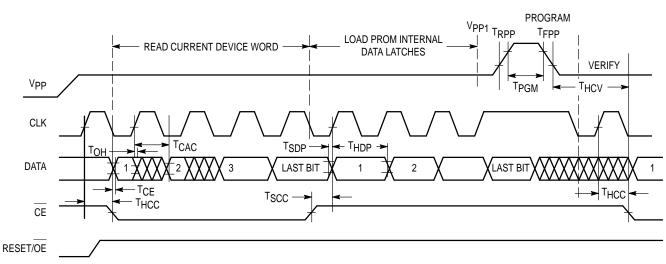

In all BFR modes, the MPA device controls configuration and loads from either a byte wide or serial memory. In BFR mode 1 (Figure 2–17), the device generates 18 bits of address and reads 8 bits of configuration data. MPA devices generate 18 bits of address or 262K bytes (e.g., 17 MPA1036 devices). If a larger address range is required, BFR mode 3 (Figure 2–21 on page 2–20) can be used. In BFR mode 3 an external address generator is used to extend the address space. BFR mode 2 is a special case of BFR 3. In this case the address generator is resident in a serial PROM and data is presented to the device 1 bit at a time. The MPA design system download POD and the MPA17000 serial EPROMs are used with this mode.

In MICRO Mode, the MPA1000 device becomes an 8 bit peripheral slave device. A microcontroller or microprocessor controls the configuration process. MICRO Mode provides more control over configuration and user mode device behavior than other modes. For example MICRO Mode can be used to randomly access and load individual rows of device configuration memory.

Configuration information generated by the MPA Design System includes Error Check Bytes (ECBs). ECBs are used to detect configuration data corruption while configurations are loaded into the device. The configuration process halts and error status is indicated if an ECB mismatch is detected anytime during the configuration process. ECB checks insure the integrity of configuration data and protect MPA devices from damage.

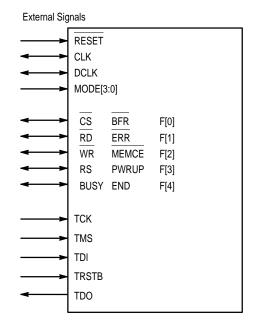

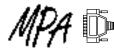

Depending on the selected configuration mode, some user I/O pins become unavailable for post configuration use. These pins are listed as "dedicated" in Table 2–5 on page 2–24 and Table 2–4 on page 2–17. The system level interface for MPA configuration is shown in Figure 2–16. Note that the meaning of the F[4:0] pins is mode specific, refer to Table 2–5 and Table 2–4 for detailed signal descriptions.

Table 2–3. MODE[3:0] Pin Programming

| Mode | Bits |                                                                                                            |  |

|------|------|------------------------------------------------------------------------------------------------------------|--|

| [1]  | [0]  | Description                                                                                                |  |

| 0    | 0    | MICRO Mode — Micro-processor/controller inter-<br>face circuitry with parallel (byte wide) data.           |  |

| 0    | 1    | <b>BFR Mode (1)</b> — Boot From ROM, byte wide data.<br>MPA generates ROM addresses.                       |  |

| 1    | 0    | <b>BFR Mode (2)</b> — Boot From ROM, serial data.<br>(Low pin count serial EPROM generates own addresses.) |  |

| 1    | 1    | <b>BFR Mode (3)</b> — Boot From ROM, byte wide data.<br>MPA does not generate ROM addresses.               |  |

| Mode | Bits |                                                                                                            |  |

| [3]  | [2]  | Description                                                                                                |  |

| Х    | 1    | Use external clock for configuration.                                                                      |  |

| 1    | Х    | Enable JTAG circuitry and pins.                                                                            |  |

#### **Configuration Clock**

The MPA1000 device has an internal oscillator. The internal configuration clock is derived from the oscillator and is presented at the CLK pin when MODE[2] is low. When MODE[2] is high, the internal clock is disconnected from the oscillator and an external clock must be presented on the CLK pin to configure the device.

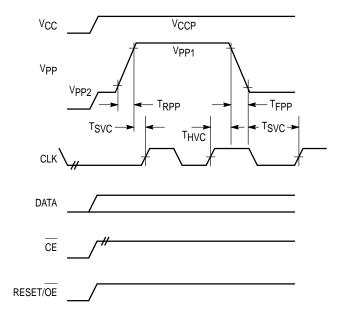

#### **Bootstrap Voltage**

Signal pathways in the MPA 1000 device are controlled with n-channel transistors. The gates of these transistors are connected to individual SRAM configuration memory cells. To pass a rail to rail signal through these transistors during user operation, the gate voltage must be elevated above V<sub>DD</sub> to compensate for transistor threshold and body effect voltage drops. MPA1000 devices contain a charge pump to generate this elevated voltage, called the bootstrap voltage. The charge pump is connected to the supply line of each SRAM cell and is driven by the internal oscillator.

Since configuration memory is generally not dynamically changing during user operation, the charge pump must only supply small leakage current losses and is not designed to supply sufficient current for SRAM read/write operations. During configuration, the charge pump (bootstrap) is internally disabled by shunting the SRAM supply to V<sub>DD</sub> through a large p–channel device. In order for the charge pump to operate properly, the internal oscillator as well as the bootstrap circuitry must be enabled. In MICRO Mode, the processor has control over these functions. In BFR modes, the on chip configuration controller insures proper sequencing of these controls.

The MPA1000 device is only guaranteed to function properly with bootstrap enabled. The internal oscillator must be running and bootstrap should be activated 100 $\mu$ s before user inputs or outputs are enabled. If dynamic configuration modification is desired, the bootstrap voltage can be supplied externally on the V<sub>PP</sub> pin and MICRO Mode can be used to disable bootstrap and on board oscillator. The bootstrap voltage should be V<sub>DD</sub> + 1.5V. At no time should V<sub>PP</sub> exceed 6.5V.

#### JTAG

The MPA1000 device contains dedicated JTAG IEEE 1149.1 boundary scan circuitry. JTAG can be used on unconfigured or fully configured devices. JTAG is enabled any time MODE[3] is raised. When MODE[3] is high, 5 user I/O pins become JTAG controls and user mode operation of those pins is interrupted. When a valid JTAG command sequence is issued, the JTAG TAP controller can take

control of all device pad circuits regardless of device configuration state. Board level testing can be accomplished without first configuring the device. Since the TAP controller can take control of all device pins, care must be used to prevent the TAP controller from interfering with device user mode or configuration operation.

#### Boot From ROM (BFR) Modes

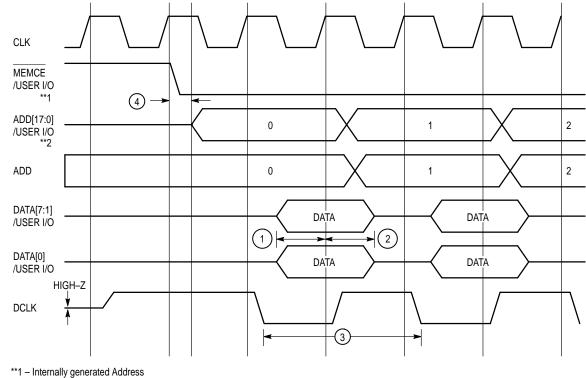

In BFR modes, the MPA device controls device configuration and assumes a memory–processor interface to the configuration store. The MPA device either asserts addresses directly (internal address generation) or issues address reset and increment pulses (external address generation). Data is read either serially or 8 bits at a time. Table 2–4 describes BFR interface signal operation. ADD[17:0] are only used in BFR mode 1. DATA[7:1] are not used in BFR mode 2 (serial data).

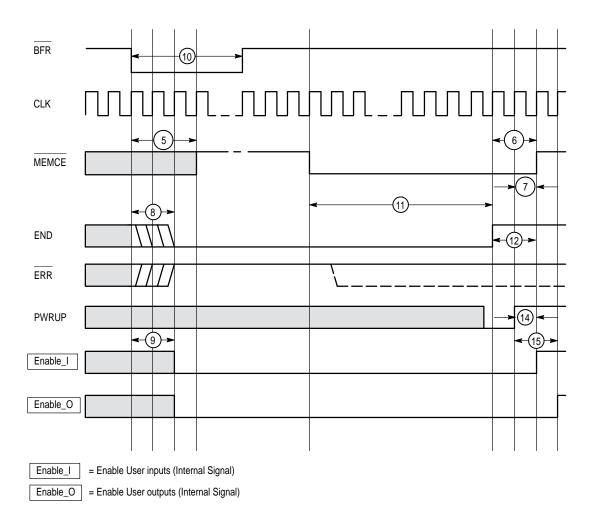

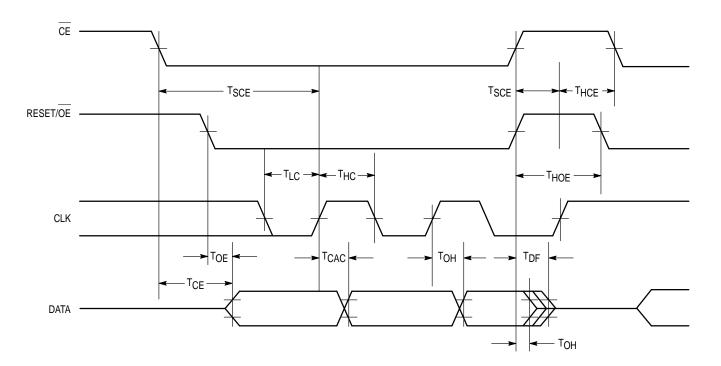

A BFR load sequence is initiated by: a falling edge of BFR, device power up or a rising edge of RESET. MEMCE falls to indicate the start of a configuration load sequence. On subsequent alternate rising edges of CLK, the data bus value is latched. The configuration process terminates when a complete configuration is successfully loaded and END is asserted or when a configuration error is detected and ERR is asserted. After END is asserted, the device will begin user mode operation 2 clocks after PWRUP is asserted or 2 clocks after END if PWRUP was already high. All configuration timing is synchronous with the internal or externally supplied configuration clock. Figure 2–19 describes BFR sequence timing details.

All BFR sequences begin with an internal device reset sequence where the entire configuration memory is reset. The duration of this sequence depends on <u>the size</u> of the MPA device being configured. A falling MEMCE edge indicates configuration commencement and data loads begin after 2 subsequent configuration clocks. The first positive edge of DCLK signals the external add<u>ress generator to increment the byte or bit address. Prior to MEMCE assertion, DCLK is tristated.</u>

The duration of the configuration process is also dependent on device size. Configuration duration can be estimated for BFR 1,3 by dividing the total number of configuration bytes by 1/2 the configuration clock frequency. For example, the MPA1036 device has 139 rows of 105 bytes including the ECB or 14,595 bytes. If the configuration clock is 2MHz, configuration will take approximately 15ms. If BFR 2 is used, the configuration process will take approximately 8 times longer. See "Device Configuration Memory Organization" on page 2–31 for device specific configuration memory sizes.

| Pin Name    | BFR       | I/O |              | Description                                                                                                                                            |

|-------------|-----------|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE[3:0]   | MODE[3:0] | Ι   | Dedicated*   | Configuration mode                                                                                                                                     |

| RESET       | RESET     | Ι   | Dedicated    | <b>Configuration reset</b> — Clear configuration memory. Configure when released.                                                                      |

| CLK         | CLK       | I/O | Dedicated    | <b>Configuration clock</b> — If MODE[2] is low, the internal configuration clock is presented. If MODE[2] is high, an external clock must be supplied. |

| F0          | BFR       | Ι   | Dedicated    | <b>BFR initiate</b> — A falling edge starts a reset and configure sequence.                                                                            |

| F1          | ERR       | 0   | Dedicated    | Error — Configuration checksum (ECB) or incorrect device ID error. Open drain output.                                                                  |

| F2          | MEMCE     | 0   | Dedicated    | Memory Enable — Active low during configuration sequence.                                                                                              |

| F3          | PWRUP     | Ι   | Dedicated    | <b>Power up</b> — After configuration complete; enable bootstrap, enable user inputs, enable user outputs.                                             |

| F4          | END       | 0   | Dedicated    | <b>Configuration completed</b> — Asserted when a configuration has been successfully loaded into the device.                                           |

| DCLK        | DCLK      | I/O | Dedicated    | <b>Data clock</b> — Each pulse indicates current data bus value has been latched and data address should increment.                                    |

| DATA[7:0]   | DATA[7:0] | Ι   | User/Data    | Data port                                                                                                                                              |

| ADD[17:0]   | ADD[17:0] | 0   | User/Address | Address output — If internal address generation is selected. (BFR Mode 1)                                                                              |

| JTAG[4:0] = |           | I/O | User/JTAG    | JTAG pins — Active when MODE[3] is asserted.                                                                                                           |

Table 2–4. BFR Mode Configuration Control Pins

\* Dedicated — Pins used for configuration. Not available for user I/O.

Figure 2–17. BFR Mode 1: 8–Bit Data, Internal Address, External Clock

# BFR Mode 1 Operation: 8 bit data, Internal Address Generation

In BFR 1, MPA configuration logic asserts an 18 bit address and reads data 8 bits at a time as shown in Figure 2–17 on page 2–17. A paging scheme could also be used where additional upper address bits were provided by an external page register. Multiple configurations<u>could</u> be accessed by writing the page register, asserting BFR, and self loading the referenced configuration.

ADD[17:0] are tristated during device reset, asserted during configuration and released for <u>user mode</u> operation. DCLK is tristated until 1 clock prior to MEMCE assertion. The

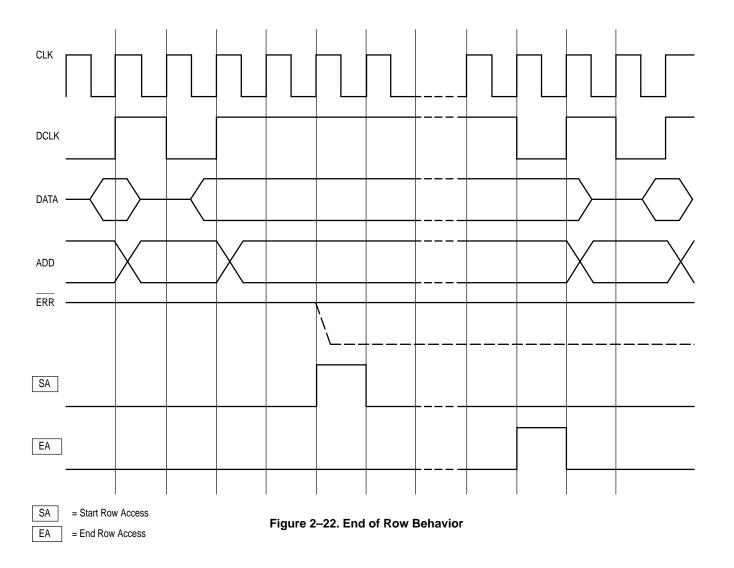

first address is asserted coincident with the falling edge of MEMCE and the data bus is latched 2 configuration clocks later. The internal address counter is incremented on each positive DCLK edge (Figure 2–18). This process proceeds until an entire row of configuration data is loaded into the internal row data register and the ECB is verified. ADD[17:0] (current address) and DCLK (=1) hold while the internal write cycle takes place. Start Access (SA) marks the beginning of the write cycle and End Access (EA) marks write completion (Figure 2–22). After the write completes, the address presentation and data latching process resumes. When the entire device configuration is loaded, END is asserted and 1

clock later user inputs are enabled, MEMCE is deasserted and DCLK tristated. One additional clock and user outputs are enabled and user mode operation commences. If the written ECB does not match the internally calculated value, ERR is asserted 2 clocks after the ECB is written. Once ERR is asserted, the configuration process halts and cannot be restarted until a new configuration process is initiated using BFR, RESET or a power down. When END is asserted, DCLK becomes an input and the internal address counter remains active until PWRUP is asserted. Figure 2–25 shows how this can be used in a multiple device subsystem. Because DCLK becomes an input, it must be tied high with a weak pullup when used in a single device configuration (Figure 2–17) to prevent a floating input condition.

\*\*2 – Externally generated Address

| Figure 2–18. E | 3FR Data | Access | Detail |

|----------------|----------|--------|--------|

|----------------|----------|--------|--------|

| Number | Characteristic                            | Min | Max | Unit | Notes |

|--------|-------------------------------------------|-----|-----|------|-------|

| 1      | Data Setup to CLK                         | 20  |     | ns   |       |

| 2      | Data Hold after CLK                       | 0   |     | ns   |       |

| 3      | DCLK Period (When Active)                 | 2   | 2   | CLK  |       |

| 4      | CLK to Address Valid (Internal Generator) | 15  |     | ns   |       |

Figure 2–19. BFR Sequence

| Number | Characteristic                  | Min | Max | Unit | Notes                                           |

|--------|---------------------------------|-----|-----|------|-------------------------------------------------|

| 5      | BFR Low to MEMCE High           |     | 3   | CLK  |                                                 |

| 6      | END High to MEMCE High          | 1   |     | CLK  |                                                 |

| 7      | PWRUP to MEMCE High             | 1   |     | CLK  |                                                 |

| 8      | BFR Low to END Low              | 0   | 3   | CLK  |                                                 |

| 9      | BFR Low to Internal Disable     | 0   | 3   | CLK  |                                                 |

| 10     | BFR Pulse Width                 | 50  |     | ns   |                                                 |

| 11     | Configuration Sequence Duration |     |     |      | Configuration sequence dependent on device size |

| 12     | END to Enable User Inputs       | 1   |     | CLK  | If PWRUP asserted                               |

| 13     | END to Enable User Outputs      | 2   |     | CLK  | If PWRUP asserted                               |

| 14     | PWRUP to Enable User Inputs     | 1   |     | CLK  |                                                 |

| 15     | PWRUP to Enable User Outputs    | 2   |     | CLK  |                                                 |

Fr-

#### BFR Mode 2 Operation: 1 bit (serial) data, External **Address Generation**

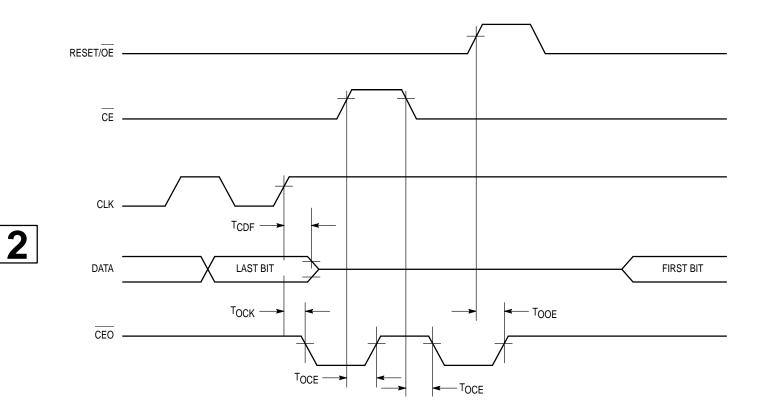

BFR mode 2 is used for connecting MPA devices to a serial configuration memory. The MPA device provides an address increment signal (DCLK) rather than an internally generated address as in BFR mode 1. Low pin count serial memories, like the MPA17128, contain address generation logic which responds to a single increment signal. Addressing is sequential starting at zero. Multiple MPA17128 devices can be daisy chained if a larger memory is required (See MPA17128 data sheet on page 2-52). Serial memories are programmed (written) in the opposite bit order from the way they are read. The MPA Design System configuration generation program will generate a correctly formatted PROM programming file by reflecting each configuration byte prior to writing the file.

MEMCE is high until configuration commences. MEMCE is connected to the RST/OE pin of the MPA17128 holding its internal address counter at 0 and its outputs tristated. The falling edge of MEMCE enables the memory data pin and 2 clocks later a data bit is latched into the MPA1000 device. The first rising edge of DCLK signals the memory to index its address register and present the next locations data bit.

Each time 8 bits are accumulated by the MPA1000, they are written to the internal row data register. As in BFR 1, this process proceeds until a complete row is loaded and the ECB is verified. DCLK holds while the row data register is written to the current configuration memory row. After the write completes, additional bits are loaded until the next row boundary is reached. Configuration completion and error indications are identical to BFR 1.

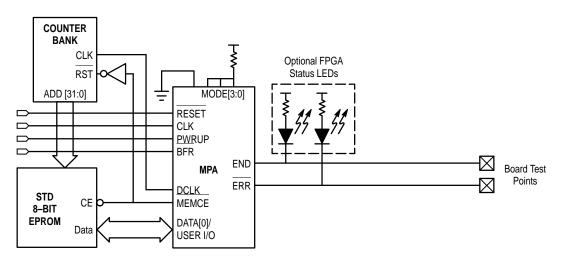

#### BFR Mode 3 Operation: 8 bit data, External Address Generation

BFR mode 3 is identical to BFR mode 2 except that 8 bits of data are loaded rather than one. An external address generator is used and responds to the MPA address increment signal (DCLK). BFR mode 3 is useful because BFR 1 requires 18 user I/O signals (ADD[17:0]) during configuration. While these are subsequently released, it does impose restrictions on surrounding circuitry complicating overall system design. Secondly in applications requiring rapid configuration of a large number of MPA devices or many alternate configurations, the MPA 18 bit address space may not be large enough and an external counter (address generator) would required anyway.

Figure 2–20. BFR Mode 2: 1–Bit (Serial) Data, External Address, External Clock

Figure 2–21. BFR Mode 3: 8–Bit Data, External Address, External Clock

### MPA1000 Product Description

2

#### **BFR Multiple Device Subsystems**

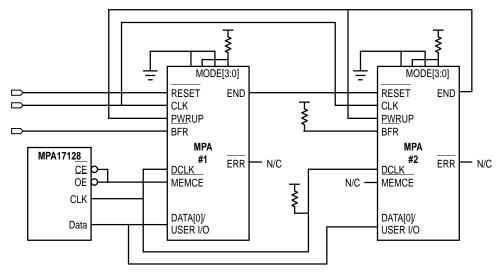

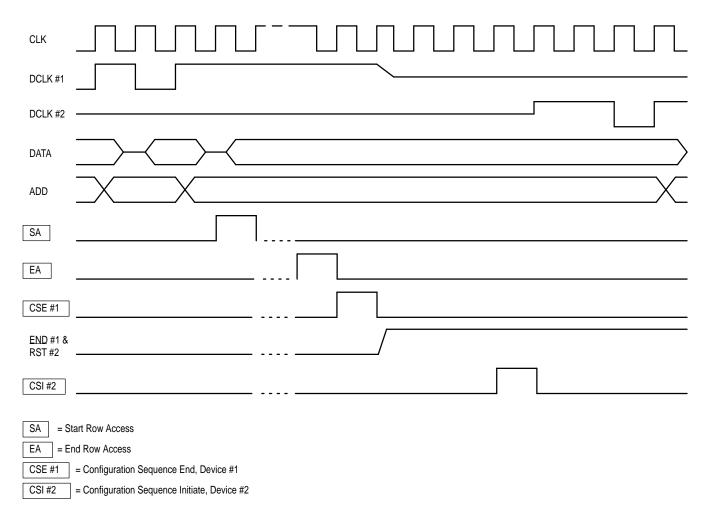

If multiple devices are used together in BFR mode, the first device loads first <u>and the</u> END signal on each device is connected to the RESET pin of the next device. As an upstream device completes configuration, a configuration sequence is initiated on the next device. This daisy chain extends to the last device. This devices END is connected to the PWRUP pins of all subsystem MPA devices. All devices enter user mode when the last device successfully configures.

Care must be taken to insure proper operation. BFR on all but the first device must be tied high and the subsystems composite DCLK line must be pulled up to eliminate spurious clock signals as one device tristates DCLK and the next device asserts it. Figure 2–24 illustrates the control signal hand off.

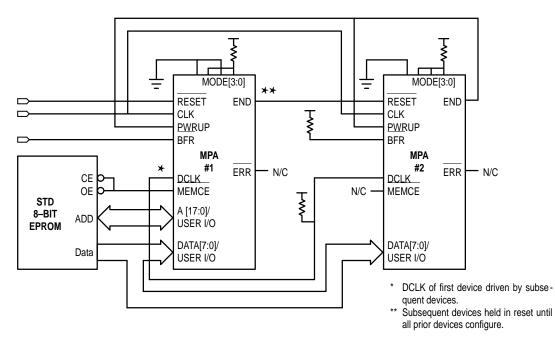

When constructing a subsystem in which the first device asserts the 18 bit address (BFR mode 1), this device provides address generation for all devices in the subsystem. The DCLK pin of the first device becomes an input when it successfully configures and its internal counter remains active. Positive edges applied to this pin will increment the first devices internal address counter and present the resulting address on the first devices 18 bit address bus. Subsequent devices in this subsystem should use BFR mode 3 (external address, 8 bit data).

Figure 2–24. BFR Mode Daisy Chain Timing

Figure 2–25. Multiple Device Subsystem: BFR1 and BFR3; 8 Bit Data, Internal Address, External Clock

Figure 2–26. Multiple Device Subsystem: BFR3, 2; 8 Bit Data, External Address, External Clock

2

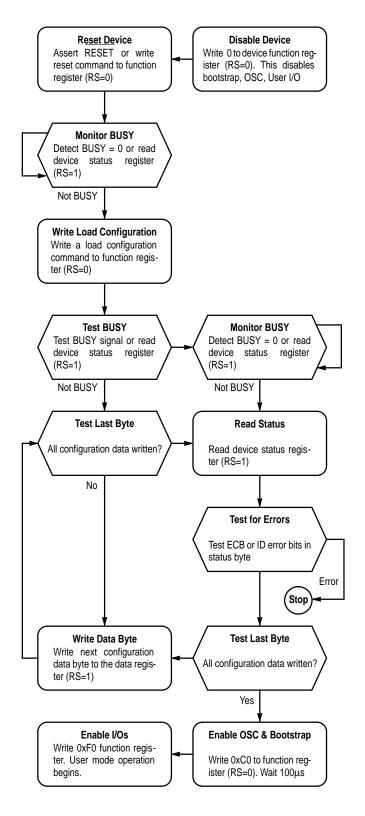

#### MICRO Mode

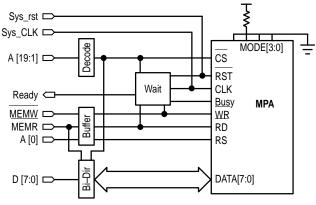

In MICRO Mode the MPA device behaves as an asynchronous microprocessor peripheral. Table 2-5 on page 2-24 details MICRO Mode configuration pin function. A chip select (/CS) is derived from the processor address and enables a single MPA device. In a multiple device subsystem, a chip select for each MPA device is required. When a device is selected, the data bus is used to write commands, read status, write configuration data and read configuration data. There are two device configuration registers, the function register (RS=0) and the data/status register (RS=1). Configuration commands are written to the function register. Subsequent behavior is specific to the command issued and is documented in Table 2-6. The data register is either used to read device status, read device configuration data or write device configuration data. RS is normally connected to the least significant address line to map the function register to address A and the data/status register to address A+1.

Configuration data format information can be found in the

"Device Configuration Data Format" section on page 2–31. Configuration data is generated by the MPA design system configuration generator after a layout is complete.

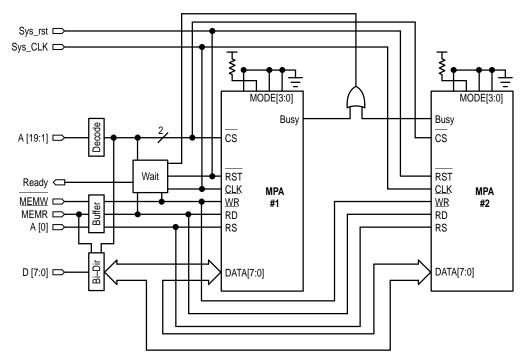

Figure 2–27. MICRO Mode: Single Device With External Clock and Wait State Insertion

| Pin Name   | Micro     | I/O |            | Description                                                                                                                                                                  |

|------------|-----------|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE[3:0]  | MODE[3:0] | I   | Dedicated* | Mode Pins                                                                                                                                                                    |

| RESET      | RESET     | I   | Dedicated  | General configuration reset                                                                                                                                                  |

| CLK        | CLK       | I/O | Dedicated  | <b>Clock for configuration circuitry</b> — If external clock is selected, pin is an input. If not selected internal configuration clock is used and output through this pin. |

| F0         | CS        | I   | Dedicated  | Chip select for device in MICRO Mode.                                                                                                                                        |

| F1         | RD        | I   | Dedicated  | Micro read signal                                                                                                                                                            |

| F2         | WR        | I   | Dedicated  | Micro write signal                                                                                                                                                           |

| F3         | RS        | I   | Dedicated  | <b>Register select</b> — Two register locations are active: Function Register (RS = 0) and Data (RS = 1).                                                                    |

| F4         | Busy      | 0   | Dedicated  | <b>Busy signal</b> — Active high when device is not ready to accept data, i.e. while device is resetting data in array or a data register to array transfer is taking place. |

| DATA[7:0]  | DATA[7:0] | I/O | Dedicated  | Micro data port — for configuration logic.                                                                                                                                   |

| JTAG [4:0] | J [4:0]   | I/O | User/JTAG  | JTAG pins — JTAG or User I/O is selected by MODE[3].                                                                                                                         |

Table 2–5. MICRO Mode Configuration Control Pins

\* Dedicated — Pins used for configuration. Not available for user I/O.

2

۴.

| DATA<br>[7:4] | DATA<br>[3:0] | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XXXX          | 0000          | Normal operation — No function performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| XXXX          | 0001          | Reset Device — Entire device configuration is reset. BUSY is asserted until reset completes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| XXXX          | 0010          | Load Configuration — After writing this command, an entire normal format device configuration is presented to the data register in 8 bit segments starting with the configuration header block. At any time during the loading process, a read to the data register will return status register contents. As complete rows including ECB are loaded, BUSY is temporarily asserted while row data is internally transferred from the internal data register to the currently addressed memory row. Once this write operation is complete, BUSY is deasserted and additional data can be written. Each time BUSY is deasserted, the status register should be checked for incorrect ID or row configuration data error(s). Once an error is detected, NO further write accesses to the data register will be accepted until the device is reset or another load configuration command is issued. |

| XXXX          | 0011          | <b>Reset Row</b> — Indicates that the next data written to the data register will be a device row address. After the address is written, the contents of that configuration memory row are reset. BUSY is asserted after the address is written and deasserted when the operation is complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XXXX          | 0100          | Load Row — The next data written to the data register consists of a row address followed by configuration data for that row including the terminating ECB. After the ECB is written, BUSY will be asserted during internal write and deasserted when the write completes. Reading the data register returns status register contents. The status register should be checked for row configuration data error(s). Once an error has been detected, NO further write accesses to the data register will be accepted until the device is reset or a load configuration command is issued.                                                                                                                                                                                                                                                                                                         |

| XXXX          | 0101          | <b>Read Row</b> — The next data written to the data register will be interpreted as a row address. After the row address is written, BUSY is asserted while row data is read into the internal data register. BUSY is deasserted when the transfer is completed. Subsequent successive reads from the data register will return row configuration data. No ECB is returned. The row data read back is in the same order as it is written, rightmost byte first.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| XXXX          | 0110          | <b>Read Device ID</b> — 4 subsequent reads from the data register return device ID. The most significant ID byte is read first. Refer to "configuration data format" for individual device ID values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| _             | 0111          | Bits [3:0] — Reserved pattern.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               | 1XXX          | Bits [3:0] — Reserved pattern.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1XXX          | XXXX          | Bootstrap Enabled — Should be enabled after configuration is completed and disabled during configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| X1XX          | XXXX          | Internal Oscillator Disabled — Normally always enabled. Can be disabled if external clock and VPP are supplied. If internal configuration clock is used, oscillator cannot be disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XX1X          | XXXX          | User Inputs Enabled — Normally user inputs are enabled after a configuration is successfully loaded into the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| XXX1          | XXXX          | User Outputs Enabled — Normally user outputs are enabled one or more clocks after user inputs are enabled to insure valid input values have propagated into the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### Table 2–7. MICRO Mode Status Register

| Bit Position |     |     |     | 1   |     |     |     |                                                                                            |  |  |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--------------------------------------------------------------------------------------------|--|--|--|

| [7]          | [6] | [5] | [4] | [3] | [2] | [1] | [0] | Function                                                                                   |  |  |  |

| 0            | 0   | 0   | 0   | 0   | Х   | Х   | 1   | Incorrect Device ID.                                                                       |  |  |  |

| 0            | 0   | 0   | 0   | 0   | Х   | 1   | Х   | Row configuration data error. ECB mismatch.                                                |  |  |  |

| 0            | 0   | 0   | 0   | 0   | 1   | Х   | Х   | Busy signal asserted. Allows software handshaking if hardware wait states are not to used. |  |  |  |

## MPA1000 Product Description

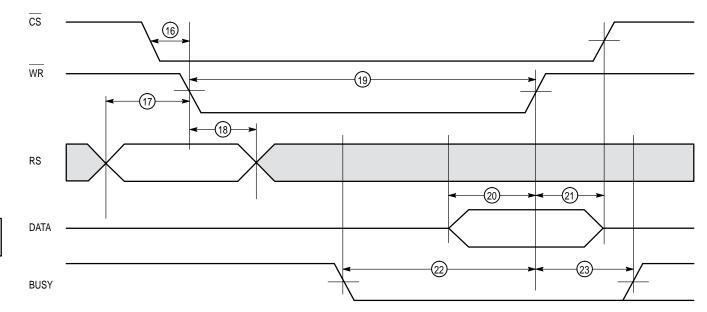

Figure 2–28. MICRO Mode External Timings (Write Cycle)

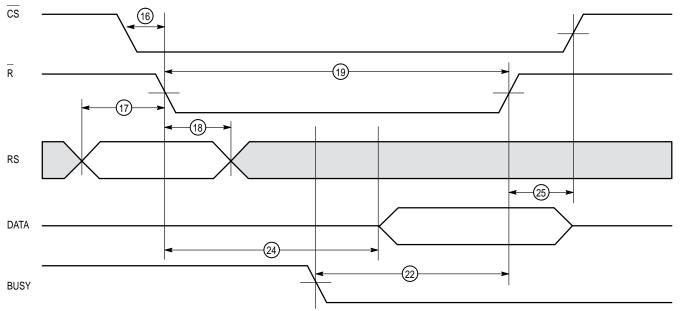

Figure 2–29. MICRO Mode External Timings (Read Cycle)

| Number | Characteristic                         | Min | Max | Unit | Notes |

|--------|----------------------------------------|-----|-----|------|-------|

| 16     | CS Setup before Read/Write             | 10  |     | ns   |       |

| 17     | RS Setup before Read/Write             | 10  |     | ns   |       |

| 18     | RS Hold after Read/Write Falling Edge  | 10  |     | ns   |       |

| 19     | Read/Write Pulse Width                 | 50  |     | ns   |       |

| 20     | Data Setup to End of Write             | 20  |     | ns   |       |

| 21     | Data Hold after Write                  | 10  |     | ns   |       |

| 22     | Busy Inactive before End of Read/Write | 50  |     | ns   |       |

| 23     | Busy Active after Write                | 0   | 20  | ns   |       |

| 24     | Data Access Time                       | 20  | 40  | ns   |       |

| 25     | Data Hold Time after Read              | 0   | 10  | ns   |       |

#### **MICRO Mode Maximum Data Transfer Rate**

The maximum MICRO Mode data transfer rate is governed by the R/W timing described in Figure 2-28 and Figure 2-29. The processor must only write data when BUSY is inactive. BUSY is only asserted when data cannot be accepted at the maximum rate. The specific behavior of BUSY for each MICRO Mode function is described in Table 2-6. When the device is powered up, an internal reset sequence is initiated BUSY is asserted (see "Behavior and Durina Power-On-Reset"). BUSY will be deasserted when the internal reset sequence completes. The processor can monitor BUSY directly or the status register can be read.

If processor R/W cycles are faster than the timing shown, external circuitry must be used to insert wait states. Figure 2–27 and Figure 2–34 show an application circuit consisting of one or more MPA devices and an optional wait <u>state insertion block</u> used to lengthen R/W timing based on CS, MEMW, MEMR, BUSY, and RESET using an externally provided clock.

#### Multiple Devices in MICRO Mode

If multiple devices are used in MICRO Mode, external logic is <u>re</u>quired to individually address each MPA device using CS (chip select) signals. After configuration, the processor must write bootstrap enable, enable inputs and enable outputs commands to each device. A subsystem BUSY signal can be derived by OR-ing the BUSY signals from each individual device. Refer to Figure 2–34.

#### **Internal Clock Specification**

The internal ring oscillator is a clock source with possible frequencies ranging from 10MHz to 40Mhz. This variation is expected and does not present a problem for proper charge pump or configuration operation. The internal configuration clock is derived by dividing the oscillator frequency by 8. The internal configuration clock can be used for user mode operation and is presented on the CLK pin when MODE[2] is low.

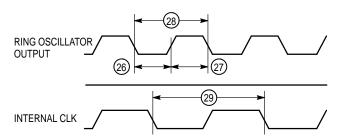

Figure 2–30. Internal Oscillator and Clock Specification

| Num | Characteristic         | Min | Тур | Max | Unit |

|-----|------------------------|-----|-----|-----|------|

| 26  | Ring Oscillator Low    | 10  | 25  | 50  | ns   |

| 27  | Ring Oscillator High   | 10  | 25  | 50  | ns   |

| 28  | Ring Oscillator Period | 25  | 20  | 100 | ns   |

| 29  | Internal Clock Period  | 200 | 400 | 800 | ns   |

Figure 2–31. MICRO Mode Configuration Load Sequence Example

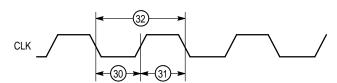

#### **External Clock Specification**

To improve configuration performance an external clock can be connected to the CLK pin when MODE[2] is asserted. The specifications for this clock are given in figure 1–26.

Figure 2–32. External Clock Specification

| Num | Characteristic        | Min | Max | Unit | Notes |

|-----|-----------------------|-----|-----|------|-------|

| 30  | External Clock Low    | 10  |     | ns   |       |

| 31  | External Clock High   | 10  |     | ns   |       |

| 32  | External Clock Period | 25  |     | ns   |       |

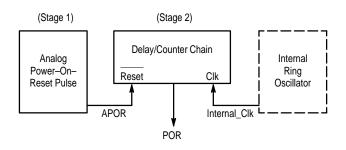

#### **Power On Reset Operation**

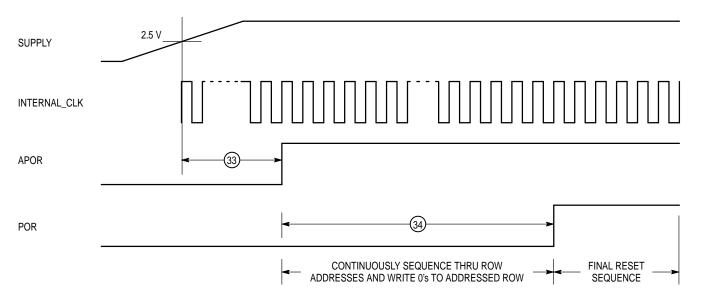

The MPA1000 devices contain circuitry to insure reliable self configuration when power is applied to the device. An counter clocked by the internal configuration clock and triggered by an analog power on reset circuit delays configuration until the power supply has been given sufficient settling time (Figure 2–35).

The analog power on reset circuit provides a reliable signal (APOR) to indicate that  $V_{DD}$  is sufficient to reliably operate device logic. While APOR is low a 17 bit counter is held reset. When APOR is asserted, the counter is enabled and

POR occurs when the most significant counter bit reaches 1. Between APOR assertion and POR, the configuration circuitry is continuously resetting configuration memory row by row. When POR is asserted, a final internal reset sequence is performed (Figure 2–35). If an external clock is selected by asserting MODE[2], this selection will not take effect until 4 internal configuration clocks after POR occurs.

Figure 2–33. 2–Stage Power–On–Reset

#### **External Reset**

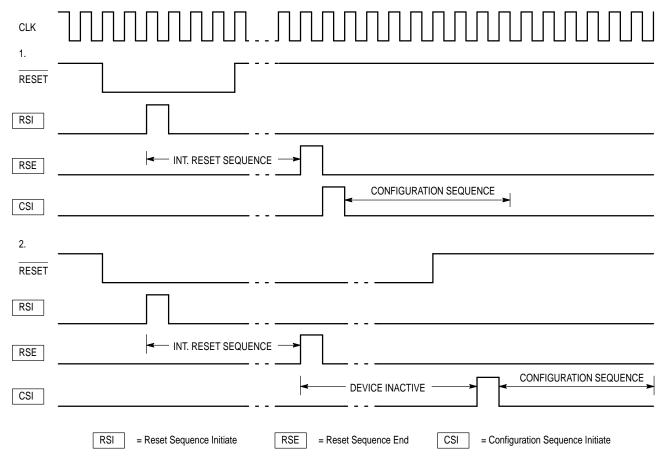

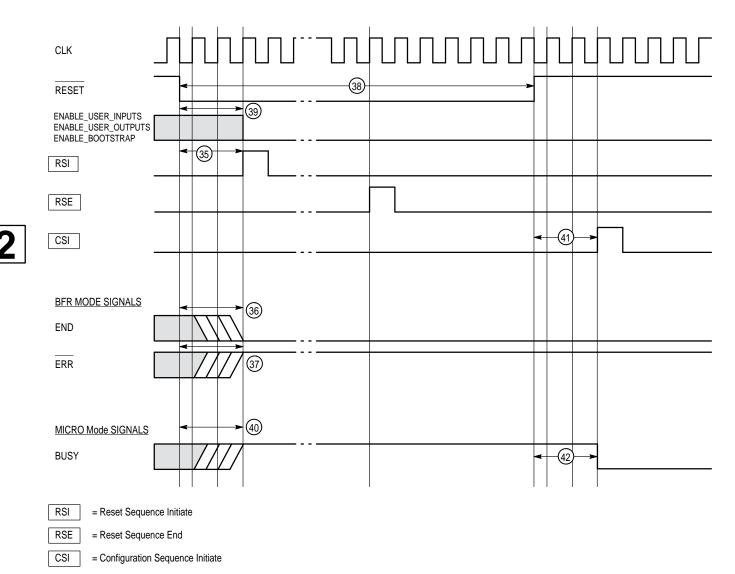

A reset sequence is initiated by a falling edge of RESET. Once a reset sequence is initiated it cannot be terminated by a subsequent rising edge of RESET.

If RESET is low when the internal reset <u>sequence</u> completes, configuration will not commence until RESET is deasserted (Figure 2–36). This feature can be used to hold off configuration until other external events occur. This feature is used in conjunction with the multiple device daisy chain. Figure 2–37 shows RESET effect on other configuration mode, internal reset and internal configuration signals.

Figure 2–34. MICRO Mode: Multiple Devices With External Clock and Wait State Insertion

Fr-

| Number | Characteristic | Min  | Max  | Unit | Notes |

|--------|----------------|------|------|------|-------|

| 33     | APOR           | 10   | 1000 | μs   |       |

| 34     | POR (Active)   | 13.2 | 52.5 | ms   |       |

## MPA1000 Product Description

| Number | Characteristic                | Min | Max | Unit | Notes                    |

|--------|-------------------------------|-----|-----|------|--------------------------|

| 35     | RESET Low to Reset Sequence   | 2   | 3   | CLK  |                          |

| 36     | RESET Low to END Low          | 0   | 3   | CLK  |                          |

| 37     | RESET Low to ERR High         | 0   | 3   | CLK  |                          |

| 38     | RESET Pulse Width             | 50  |     | ns   |                          |

| 39     | RESET Low to Internal Disable | 0   | 3   | CLK  |                          |

| 40     | RESET Low to Busy Active      | 0   | 3   | CLK  |                          |

| 41     | RESET High to CSI Pulse       | 2   |     | CLK  | RESET Released After RSE |

| 42     | RESET High to Busy Inactive   | 2   |     | CLK  | RESET Released After RSE |

In MICRO Mode, the busy signal remains high while the reset signal is asserted and until the internal reset sequence is completed.

## **MPA1000 Configuration Data Format**

#### **Device Configuration Memory Organization**

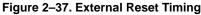

The MPA1000 devices are programmed by loading configuration data into on chip configuration memory constructed of SRAM cells. This memory is organized differently from standard memory products. The configuration SRAM is distributed throughout the MPA device. Data is read and written to the device 1 row at a time via the internal row data register (RDR). Individual rows are addressed via the row address register (RAR). Each device has a different size RDR and RAR (Figure 2-38). The configuration logic is responsible for the control of these resources.

| Device | # Rows | # Real<br>Bits | # Filler | # ECB | Total<br>Row<br>Bits |

|--------|--------|----------------|----------|-------|----------------------|

| 1016   | 95     | 562            | 6        | 8     | 576                  |

| 1036   | 139    | 828            | 4        | 8     | 840                  |

| 1064   | 183    | 1090           | 6        | 8     | 1104                 |

| 1100   | 227    | 1352           | 0        | 8     | 1360                 |

#### Figure 2–38. Device Memory Organization

Configuration logic writes data to the leftmost (most significant) RDR byte and reads from the rightmost (least significant) RDR byte. Each of these transfers occurs in 8 bit increments. When serial data is presented, the bits are accumulated into a byte before RDR transfer. Each configuration logic RDR write operation first shifts the RDR eight 8 bits and transfers the new byte into the leftmost RDR byte position. Configuration read operations transfer the rightmost RDR byte to the configuration logic and then shifts RDR contents right 8 bits.

The RAR enables a single configuration memory row. MPA configuration logic writes a row addresses into the RAR. Subsequent read or write operations are performed between the RDR and the RAR selected row in parallel.

Filler bits are used to round the RDR up to the nearest byte boundary. The ECB is not part of the RDR. During configuration a single row data vector is written to the RDR and an ECB is calculated from the data written. The calculated value is compared to the ECB contained in the data vector. If a mismatch is detected, ERR is asserted and the configuration process terminates. The ECB mechanism prevents data write disturbances from causing unpredictable device function.

#### **Device Configuration Data Formats**

When whole configurations are loaded into a device, the first 40 bits contain a 32 bit device ID followed by an 8 bit data type field. The device ID is the same as the JTAG device ID described in "JTAG Boundary Scan". If an incorrect ID is presented, ERR is asserted and configuration stops. Device ID comparison prevents incompatible configurations from causing unpredictable device behavior. The data type field identifies subsequent data format. Recognized data types are shown in Table 2-8.

#### Table 2-8.

| [7:3] | [2] | [1] | [0] | Data Type                                                                                          |

|-------|-----|-----|-----|----------------------------------------------------------------------------------------------------|

| 00000 | Х   | Х   | 0   | Sequential data (Normal data)                                                                      |

| 00000 | Х   | Х   | 1   | Test data – Multiple row access                                                                    |

| 00000 | Х   | 0   | Х   | Unencrypted data                                                                                   |

|       | х   | 1   | Х   | Encrypted data – Not supported on first product. <b>Reserved</b> for future implementations        |

|       | 0   | Х   | Х   | Uncompressed data                                                                                  |

|       | 1   | х   | Х   | Compressed data – Not supported<br>on first product. <b>Reserved</b> for future<br>implementations |

#### Header Block

| Device ID [3] |

|---------------|

| Device ID [2] |

| Device ID [1] |

| Device ID [0] |

| Data Type     |

Two data formats are supported; Normal data and test data. Normal data is generated by the MPA Design System and is the only data type users are expected to use. Test data is a special format developed to aid device testing where many very regular configuration patterns must be rapidly loaded during production test. Test mode data only results in a memory savings when many rows of configuration memory contain identical information. Since this is unlikely for real designs, test mode data offers little or no benefit for reducing user configuration memory storage requirements. If configuration data compression is desired a simple Run Length Encoding (RLE) approach can be used to exploit the fact that most configuration memory bits will be 0.

### MPA1000 Product Description

Normal data consists of a series of configuration memory row images including filler bits and ECB. Each device has a different number of bytes per row and a different number of rows. A generalized normal data representation is shown in Figure 2–39. Bytes are presented to the device from left to right and from top–most row (row 0) to bottom–most row. The ECB is calculated by summing the row data byte by byte, complementing the carry and using this as the carry into the next addition.

| Data 0 ( <i>Row 0</i> ) | Data 1 (Row 0) | ~ | ~ | ~ | ECB 0 |

|-------------------------|----------------|---|---|---|-------|

| Data 0 ( <i>Row 1</i> ) | Data 1 (Row 1) | ۲ | ۲ | ۲ | ECB 1 |

|                         |                | " | " | " |       |

|                |                | " | " | " |       |

|----------------|----------------|---|---|---|-------|

| Data 0 (Row x) | Data 1 (Row x) | 1 | 2 | ~ | ECB x |

| Data 0 (Row y) | Data 1 (Row y) | 1 | ~ | ~ | ECB y |

|                |                |   |   |   |       |

Figure 2–39. Configuration Data Block (Normal Data)

Test data format is similar to normal data except that a row count and address list follows the ECB. The RDR is loaded and the ECB calculated normally. Each address is written to the RAR, a write cycle initiated to transfer the RDR to the addressed configuration memory row, the expected address count is decremented and the next address is loaded until the expected address count reaches zero. The next byte is assumed to be the first byte of a new row data vector. Configuration ends when a row address of 255 is presented. Figure 2–40 shows the generalized test data format.

|               | _ |       |          |       |

|---------------|---|-------|----------|-------|

| Data 0 Data 1 | ~ | ECB M | No. Rows | Row A |

|               |   |       |          | Row B |

|               |   |       |          | Row C |

|               |   |       |          | Row D |

|               |   | 33    |          |       |

| Data 0 Data 1 | ~ | ECB N | No. Rows | Row E |

|               |   |       |          | Row F |

|               |   |       |          | Row G |

Row 255

(Row 255 = Configuration Terminating Byte)

#### Figure 2–40. Test Data Configuration

## MPA1000 JTAG Boundary Scan

#### **JTAG Boundary Scan Functions**

JTAG is a standardized boundary scan methodology used for board level testing to detect faults in package and board connections, as well as internal circuitry. The MPA1000 JTAG boundary scan cell is designed to meet the IEEE std. 1149.1 for testability test of an integrated circuit.

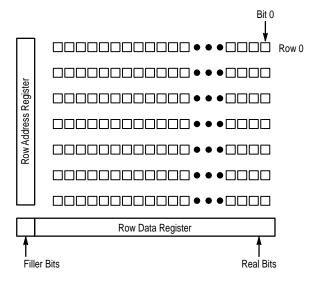

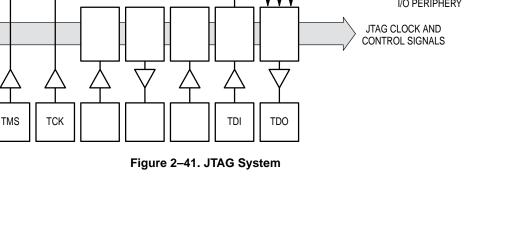

#### **IEEE 1149.1 Architecture**

Figure 2-41 shows the general diagram of the IEEE 1149.1 MPA1000 JTAG system. Its design is compatible to Motorola H4C and H4C+ family of arrays. The MPA1000 JTAG design is hard wired.

#### TAP and I/O Periphery Signals

The TAP (Test Access Port) consists of five externally accessible signals which are used to control and observe boundary scan data. These five pins; TCK, TMS, TDI, TRSTB, and TDO are multiplexed with normal signal pins. After JTAG testing, these pins can be programmed as normal I/O pins when MODE[3] is deasserted. The test clock pin, TCK, is used to synchronize all JTAG functions. The TCK, TMS and TRSTB control the TAP controller. TDI is the test data input pin and TDO is the test data output pin.

#### **JTAG Control and Test Register**

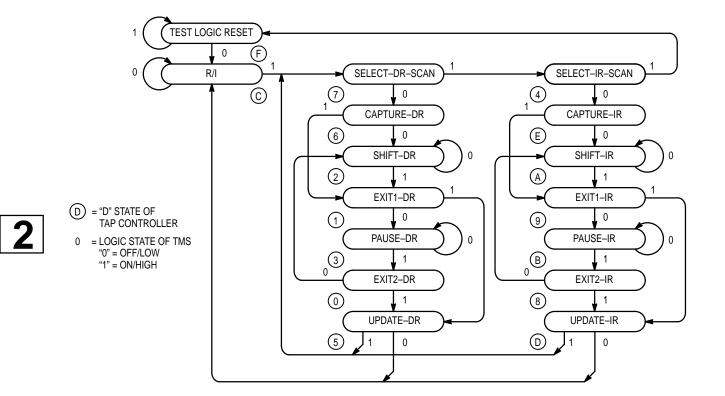

The **TAP Controller** is a synchronous, 16-state machine, which selects the mode of operation for the test circuitry. An example of the operation of the TAP controller is shown in Figure 2-42 where the TAP controller is sequenced through most of its test states.

|    | +    | +    | +       | +    | +     | +           | +    | +        | +    | +          | +     | TRSTB  |

|----|------|------|---------|------|-------|-------------|------|----------|------|------------|-------|--------|

| L  |      | www  | JUUUU   | uuu  | www   | MM          | www  | vvv      | uuuu | MM         | www   | ПП тск |

| F  | +    | +    |         | +    |       | +           |      | <u>+</u> |      | +          | +     | TMS    |

|    | +    | + 07 | 4 E A 9 | 9 B+ | 8 A + | 9 D C       | 762  | 1 3 +    | 02+  | 1 5 C      | 74F   | STATE  |

| L  | +    | +    | +       | +    | +     | +           | +    | +        | +    | +          |       | RB     |

| F  | +    | +    | -100    | +    | THU   | +           | +    | +        | +    | +          | +     | CKIR   |

| F  | +    | +    | +       | +    | +     | +           | +    | +        | +    | +          | +     | SHIR   |