SDNS041 - NOVEMBER 1996

- Single-Chip Scheduler for Scheduling Available Bit Rate (ABR) Connections

- Used With the TNETA1575 to Provide a Complete Solution for Segmentation and Reassembly of Data on ABR Connections as Specified in the Asynchronous Transfer Mode (ATM) Forum's Traffic Management 4.0 Document (TM4.0) and ITU-TI.371

- Supports Scheduling of Variable-Bit-Rate Non-Real Time (VBR-nrt) Using Host-Programmable Peak Cell Rate (PCR), Sustained Cell Rate (SCR), and Maximum Burst Size (MBS)

- On-Chip Self-Sorting FIFO-Based Scheduler Used to Schedule the Transmission of Cells for All Connections

- Simultaneously Supports Both Virtual Path (VP) and Virtual Channel (VC) Level ABR Traffic Management

- Provides Scheduling for up to 2047 ABR Connections Required for Large-Scale LAN Emulation Installations

- On-Chip Processors Implement the End-System Behavior as Defined in TM4.0, Providing a High-Performance and Flexible Solution to Track Future Standards

- On-Chip Instruction RAMs Hold the Microcode for the Source and Destination Processors, Providing Fast Execution of Code on Chip

- Configuration Support for all Primary and Optional TM4.0 Parameters, Providing Maximum Implementation Flexibility

- Supports TM4.0-Defined Resource Management (RM)-Cell Formats and Provides the RM-Cell Payload and Information on How to Configure the RM-Cell Header to the Segementation and Reassembly (SAR) Device

- Supports Out-of-Rate Forward and Backward RM-Cell Generation to Prevent Deadlock Situations When the Rates of Sources and Destinations Are Driven to or Below a Minimum Cell Rate of 10 Cells Per Second

- Processes Received RM Cells, Maintaining Parameters and Variables in Accordance With TM4.0

- Hardware Assistance Is Provided for 1/ACR Calculations That Support Scheduling Operations to Maximize Performance

- Hardware Assistance Is Provided for 15-bit Floating-Point To/From Integer Conversions to Maximize Performance

- UTOPIA Revision 2.01-Compliant Receive (Observe-Only) Cell Interface

- Internal 8-Cell Receive FIFO

- Receive-Cell Interface Can Be Programmed to Operate as Either a Physical (PHY-Layer) Interface or as a SAR/Switch (ATM-Layer) Interface.

- Supports Boundary Scan Through a Five-Wire JTAG Interface in Accordance With IEEE Std 1149.1-1990 (Includes IEEE Std 1149.1a-1993) IEEE Standard Test-Access-Port and Boundary-Scan Architecture

#### description

The TNETA1585 is an asynchronous transfer mode (ATM) programmable traffic management scheduler device that is used with a segmentation and reassembly (SAR) device to provide a flexible, high-performance solution for the available bit rate (ABR) service category. Its programmability enables it to support other special modes including variable-bit-rate non-real-time (VBR-nrt) service category and virtual path (VP) level ABR in addition to and simultaneously with ABR. Combining the TNETA1585 with the TNETA1575 provides a high-performance solution for classical LAN to ATM backbone applications including high-performance networking hubs.

This data sheet provides information on the device hardware specifications that includes device interfaces, timing diagrams, electrical characteristics, terminal and package information, and an overview of device operation. All information on the TNETA1585 data structures, configuration, and features is provided in the *TNETA1585 Programmer's Reference Guide*, literature number SDNU016.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

SDNS041 - NOVEMBER 1996

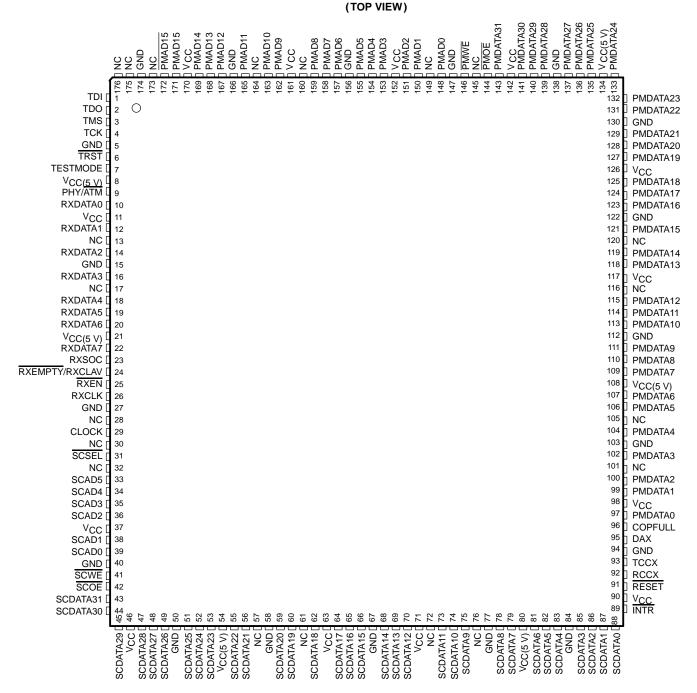

PGF PACKAGE

NC - No internal connection

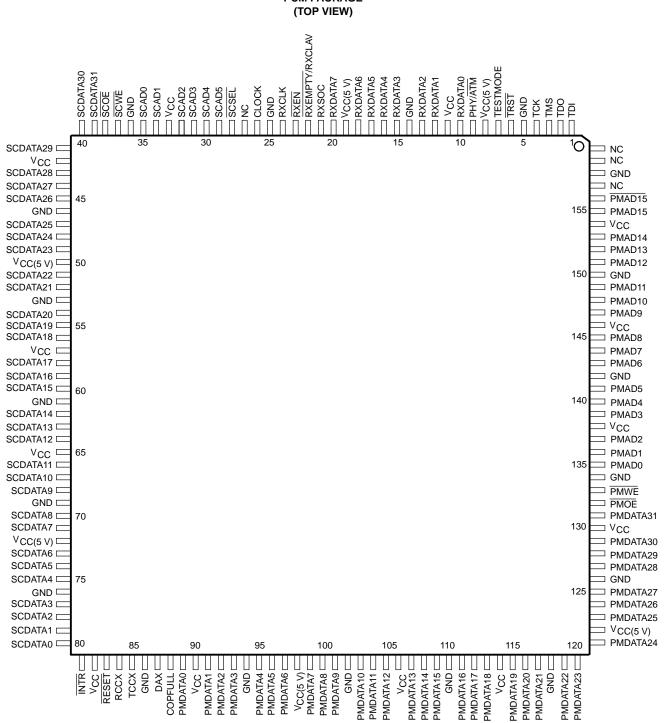

PCM PACKAGE

NC - No internal connection

**PRODUCT PREVIEW**

SDNS041 - NOVEMBER 1996

## **Terminal Functions**

## slave interface

| TERM         | TERMINAL                                                                                              |                                                                                                 |                       | RESET |                                                                                                                       |  |

|--------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------|-------|-----------------------------------------------------------------------------------------------------------------------|--|

| NAME         | NO.<br>PGF                                                                                            | NO.<br>PCM                                                                                      | I/O                   | STATE | DESCRIPTION                                                                                                           |  |

| SCAD(5-0)    | 33–36<br>38–39                                                                                        | 29–32<br>34–35                                                                                  | I (TTL)               | I     | Slave-control address. SCAD(5–0) consists of a 6-bit address.                                                         |  |

| SCDATA(31–0) | 43–45<br>47–49<br>51–53<br>55–56<br>59–60<br>62<br>64–66<br>68–70<br>73–75<br>78–79<br>81–83<br>85–88 | 39-41<br>43-45<br>47-49<br>51-52<br>54-56<br>58-60<br>62-64<br>66-68<br>70-71<br>73-75<br>77-80 | I/O<br>(TTL/<br>CMOS) | Hi-Z  | Slave-control data. SCDATA(31–0) consists of 32-bit data.                                                             |  |

| SCOE         | 42                                                                                                    | 38                                                                                              | I (TTL)               | I     | Slave-control output enable. SCOE is active low. When the SCOE and SC are low, TNETA1585 reads are enabled.           |  |

| SCSEL        | 31                                                                                                    | 28                                                                                              | I (TTL)               | I     | Slave-control select. SCSEL is active low. SCSEL enables the slave-control interface.                                 |  |

| SCWE         | 41                                                                                                    | 37                                                                                              | I (TTL)               | I     | Slave-control write enable. SCWE is active low. When the SCWE and SCSEL inputs are low, TNETA1585 writes are enabled. |  |

## coprocessor interface

| TER     | TERMINAL   |            |             | DECET          |                                                                                                                                                                                                                                                                                                                    |

|---------|------------|------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO.<br>PGF | NO.<br>PCM | I/O         | RESET<br>STATE | DESCRIPTION                                                                                                                                                                                                                                                                                                        |

| CLOCK   | 29         | 26         | I (TTL)     | I              | Clock. The RCCX, TCCX, and DAX inputs are clocked into the device on the rising edge of the clock input. This clock also is used as an operating clock source for the TNETA1585.                                                                                                                                   |

| COPFULL | 96         | 88         | O<br>(CMOS) | Low            | Receive-FIFO full indication. COPFULL provides an indication of the status of the receive UTOPIA interface FIFO. When the PHY/ATM input is low, COPFULL goes high when the receive UTOPIA interface FIFO is full. When the PHY/ATM input is high, COPFULL goes high when the FIFO is within 4 bytes of being full. |

| DAX     | 95         | 87         | I (TTL)     | I              | Data-availability indication. DAX provides an indication to the device when data is available on a particular channel or when the SAR has completed segmentation of queued packets.                                                                                                                                |

| INTR    | 89         | 81         | O<br>(CMOS) | High           | Local interrupt. INTR provides an interrupt indication from the traffic coprocessor to the SAR.                                                                                                                                                                                                                    |

| RCCX    | 92         | 84         | I (TTL)     | I              | Receive-cell status indication. RCCX provides an indication to the device that a cell has been received on the UTOPIA interface along with the receive channel number assigned to the cell.                                                                                                                        |

| RESET   | 91         | 83         | I (TTL)     | I              | Reset. When low, RESET resets the device.                                                                                                                                                                                                                                                                          |

| тссх    | 93         | 85         | I (TTL)     | I              | Transmit-cell status indication. TCCX provides an indication to the device that a cell has been transmitted from the SAR along with the channel number of that cell.                                                                                                                                               |

SDNS041 - NOVEMBER 1996

## **Terminal Functions (Continued)**

### receive-UTOPIA interface

| TER                | MINAL                               |                            |         | RESET                                                                                                         |                                                                                                        |

|--------------------|-------------------------------------|----------------------------|---------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| NAME               | NO.<br>PGF                          | NO.<br>PCM                 | I/O     | STATE DESCRIPTION                                                                                             |                                                                                                        |

| RXCLK              | 26                                  | 24                         | I (TTL) | I                                                                                                             | Receive clock. RXCLK is the data transfer/synchronization clock for synchronizing transfers on RXDATA. |

| RXDATA(7–0)        | 22<br>20–18<br>16<br>14<br>12<br>10 | 20<br>18–15<br>13–12<br>10 | I (TTL) | I                                                                                                             | Receive data. Eight-bit data lines. RXDATA(7) is the MSB.                                              |

| RXEMPTY/<br>RXCLAV | 24                                  | 22                         | I (TTL) | Receive-empty/receive-cell available. RXEMPTY/RXCLAV is an ind a transfer of a complete cell can be accepted. |                                                                                                        |

| RXEN               | 25                                  | 23                         | I (TTL) | I                                                                                                             | Receive enable. $\overline{\text{RXEN}}$ indicates to the TNETA1585 when RXDATA contains a valid byte. |

| RXSOC              | 23                                  | 21                         | I (TTL) | Receive start of cell. RXSOC is received by the device when RXDATA the first valid byte of the cell.          |                                                                                                        |

#### parameter-memory interface

| TERMINAL     |                                                                                                                                             |                                                                                                                    |                   | RESET |                                                                                                                                               |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.<br>PGF                                                                                                                                  | NO.<br>PCM                                                                                                         | I/O               | STATE | DESCRIPTION                                                                                                                                   |

| PMAD(15-0)   | 171<br>169–167<br>165<br>163–162<br>159–157<br>155–153<br>151–150<br>148                                                                    | 155<br>153–151<br>149–147<br>145–143<br>141–139<br>137–135                                                         | O (CMOS)          | Low   | Parameter-memory address. PMAD(15–0) provides a 16-bit physical address to the parameter memory.                                              |

| PMDATA(31-0) | 143<br>141–139<br>137–135<br>133–131<br>129–127<br>125–123<br>121<br>119–118<br>115–113<br>111–109<br>107–106<br>104<br>102<br>100–99<br>97 | 131<br>129–127<br>125–123<br>121–119<br>117–115<br>113–111<br>109–107<br>105–103<br>101–99<br>97–95<br>93–91<br>89 | I/O<br>(TTL/CMOS) | Low   | Parameter-memory data. PMDATA(31–0) provides 32-bit data to/from the parameter memory.                                                        |

| PMWE         | 146                                                                                                                                         | 133                                                                                                                | O (CMOS)          | High  | $\frac{Parameter}{PMWE}$ is low.                                                                                                              |

| PMAD15       | 172                                                                                                                                         | 156                                                                                                                | O (CMOS)          | High  | Inverse of PMAD15. PMAD15 can be used with PMAD15 to provide SRAM bank switching.                                                             |

| PMOE         | 144                                                                                                                                         | 132                                                                                                                | O (CMOS)          | High  | Parameter-memory output enable. The PMAD(15–0) address is valid when PMOE is low. Data is read into the TNETA1585 on the rising edge of PMOE. |

SDNS041 - NOVEMBER 1996

## **Terminal Functions (Continued)**

## boundary-scan interface

| TER  | MINAL      |            |             | RESET                                                                   |                                                                                                                                 |

|------|------------|------------|-------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO.<br>PGF | NO.<br>PCM | I/O         | STATE DESCRIPTION                                                       |                                                                                                                                 |

| ТСК  | 4          | 4          | I (TTL)     | I                                                                       | Test clock. TCK is used to clock the TAP operation.                                                                             |

| TDI  | 1          | 1          | I (TTL)     | I                                                                       | Test data input. TDI is used to shift serial test data and instruction into the device during test-access-port (TAP) operation. |

| TDO  | 2          | 2          | O<br>(CMOS) | Hi-Z                                                                    | Test data output. TDO is used to shift serial test data and instructions out of the device during TAP operation.                |

| TMS  | 3          | 3          | I (TTL)     | I Test mode select. TMS is used to control the state of the TAP control |                                                                                                                                 |

| TRST | 6          | 6          | I (TTL)     | I                                                                       | Test reset. TRST asynchronously forces the TAP controller to a known state.                                                     |

## miscellaneous signals

| TERM     | IINAL      |            |         | RESET |                                                                                       |

|----------|------------|------------|---------|-------|---------------------------------------------------------------------------------------|

| NAME     | NO.<br>PGF | NO.<br>PCM | I/O     | STATE | DESCRIPTION                                                                           |

| PHY/ATM  | 9          | 9          | I (TTL) | I     | PHY/ATM mode select. PHY/ATM selects ATM mode when low and PHY mode when high.        |

| TESTMODE | 7          | 7          | I (TTL) | I     | Test/normal mode. TESTMODE selects test mode when high and normal operation when low. |

## power and ground

|          | TERMINAL                                                                                                 |                                                                   | DESCRIPTION                                                                                                                                                                                                                 |  |

|----------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO.<br>PGF                                                                                               | NO.<br>PCM                                                        |                                                                                                                                                                                                                             |  |

| GND      | 84, 94, 103,                                                                                             | 46, 53, 61, 69,                                                   | Ground. GND is the 0-volt reference for the device.                                                                                                                                                                         |  |

| NC       | 13, 17, 28, 30,<br>32, 57, 61, 72,<br>76, 101, 105,<br>116, 120, 145,<br>149, 160, 164,<br>173, 175, 176 | 27, 157, 159,<br>160                                              | No internal connection. NC terminals are terminals with no internal connections. For potential functionality additions, it is recommended that these terminals not be connected to any signal, power, or ground connection. |  |

| Vcc      | 11, 37, 46, 63,<br>71, 90, 98,<br>117, 126, 142,<br>152, 161, 170                                        | 11, 33, 42, 57,<br>65, 82, 90,<br>106, 114, 130,<br>138, 146, 154 | Supply voltage. $V_{CC}$ is the 3.3-V (with respect to GND) supply for the functional logic gates.                                                                                                                          |  |

| VCC(5 V) | 8, 21, 54, 80,<br>108, 134                                                                               | 8, 19, 50, 72,<br>98, 122                                         | Supply voltage. V <sub>CC(5 V)</sub> is the 5-V secondary supply voltage for the clamp diodes of 5-V tolerant input and output buffers. The clamp diodes provide protection for the buffers in a 5-V switching environment. |  |

#### detail description

The TNETA1585 device contains the following interfaces:

- COPI interface: Slave-control interface Coprocessor interface

- Receive-UTOPIA interface

- Parameter-memory interface

- JTAG interface

#### **COPI** interface

The traffic-coprocessor interface (COPI) provides the means of communication between the TNETA1585 and the master device. It consists of the slave interface and the coprocessor interface.

#### slave-control interface

The slave-control (SC) interface consists of a 32-bit data bus, a 6-bit address bus, an output-enable terminal (SCOE), a write-enable terminal (SCWE) and a select terminal (SCSEL). When used with the TNETA1575 SAR device, the TNETA1585 slave-control interface is mapped into the SAR's control-memory space starting at address 10000h and extending to address 1FFFFh. This equates to a total address space of 64K 32-bit words with 64 locations applicable to the TNETA1585. The TNETA1575 uses its select terminal to choose between its control memory and the TNETA1585. The TNETA1585 is a slave to all to-and-from transfers. These are initiated by the master device that is a SAR or switch port controller.

Table 1 lists the slave registers that are directly accessible through the slave interface. A heading specifies the slave-interface addresses as control-memory addresses because of the TNETA1575 mapping of the TNETA1585. Each register is either host associated or SAR associated.

The host accesses the host-associated registers through the SAR and are used by the host to initialize the TNETA1585 and to configure the TNETA1585's other internal-data structures and associated parameter memory. The host has access to the TNETA1585's other internal-data structures and associated parameter memory through the host-associated read address, read data, write address, and write data registers as described in the *TNETA1585 Programmer's Reference Guide*, literature number SDNU016.

The SAR-associated registers are used by the SAR to obtain information related to the scheduling of cells. The next-cell register indicates when one of the TNETA1585 scheduled connections is ready to transmit and what type of cell to transmit. It also provides information on how to build the associated cell's header. In addition, if the SAR is instructed by the TNETA1585 to transmit an RM cell for ABR connections, the SAR obtains the properly formatted RM-cell payload from one of the RM-cell-contents FIFOs of the TNETA1585.

SDNS041 – NOVEMBER 1996

#### slave-control interface (continued)

| DESCRIPTION               | HOST/SAR<br>ASSOCIATED | R/W | CONTROL<br>MEMORY ADDRESS<br>(TNETA1575) | PCI OFFSET<br>ADDRESS<br>(TNETA1575) |

|---------------------------|------------------------|-----|------------------------------------------|--------------------------------------|

| Next-cell register        | SAR                    | R   | h10000                                   | h40000                               |

| RM-cell-contents FIFO A   | SAR                    | R   | h10001                                   | h40004                               |

| RM-cell-contents FIFO B   | SAR                    | R   | h10002                                   | h40008                               |

| RM-cell-contents FIFO C   | SAR                    | R   | h10003                                   | h4000C                               |

| RM-cell-contents FIFO D   | SAR                    | R   | h10004                                   | h40010                               |

| Reserved                  | N/A                    | N/A | h10005–7                                 | h40014–1C                            |

| Configuration register    | Host                   | R/W | h10008                                   | h40020                               |

| Status register           | Host                   | R   | h10009                                   | h40024                               |

| Interrupt-mask register   | Host                   | R/W | h1000A                                   | h40028                               |

| Schedule-on register      | Host                   | W   | h1000B                                   | h4002C                               |

| Schedule-off register     | Host                   | W   | h1000C                                   | h40030                               |

| Read-address register     | Host                   | R/W | h1000D                                   | h40034                               |

| Read-data register        | Host                   | R   | h1000E                                   | h40038                               |

| Write-address register    | Host                   | R/W | h1000F                                   | h4003C                               |

| Write-data register       | Host                   | W   | h10010                                   | h40040                               |

| Clock-frequency register  | Host                   | R/W | h10011                                   | h40044                               |

| Revision-number register  | Host                   | R   | h10012                                   | h40048                               |

| ACR-low register          | Host                   | R   | h10013                                   | h4004C                               |

| ACR-OK register           | Host                   | R   | h10014                                   | h40050                               |

| Reserved                  | N/A                    | N/A | h10015–19                                | h40054–64                            |

| General-purpose registers | Host                   | R/W | h1001A-1D                                | h40068–74                            |

| Reserved                  | N/A                    | N/A | h100IE-3F                                | h40078–FC                            |

#### Table 1. Slave-Control Interface Register Map

The following describes the SAR-associated registers with respect to what the TNETA1575 requires of the interface. However, these registers can be used by other COPI-compliant ATM-layer devices to assist in the scheduling of cells and the generation of RM cells.

#### next-cell register

The TNETA1575 uses the next-cell register to determine if one of the TNETA1585's scheduled connections is ready to transmit and, if so, which channel and what type of cell (i.e., data, forward RM, backward RM). This register is read only.

| READY | CELL COUNT | RESERVED | CHANNEL NUMBER | CLP | CELL TYPE |  |  |  |  |

|-------|------------|----------|----------------|-----|-----------|--|--|--|--|

|       | BIT        |          |                |     |           |  |  |  |  |

| 31    | 30–26      | 25–15    | 14–4           | 3   | 2–0       |  |  |  |  |

Bit 31 (ready). The TNETA1585 sets bit 31 to indicate that the contents of the register are valid and ready to read.

Bits 30–26 (cell count). This field indicates the number of cells minus one that are to be sent by the SAR for this particular channel. A zero entry tells the SAR to send a single cell and an all-ones entry tells the SAR to send 32 cells.

#### (next-cell register continued)

Bits 14-4 (channel number). This field contains the channel number that the cell(s) is sent on.

Bit 3 (CLP). This field contains the cell-loss-priority indication that the SAR should insert in the outgoing cell's header.

Bits 2–0 (cell type). This field indicates the source of cell(s) to be sent. Several options are available for outgoing cells, and this field, along with the CLP bit, indicates where the cell should be obtained. If the cell type is an RM cell, then the SAR must obtain the RM-cell payload from one of the RM-cell-contents FIFOs through the slave interface. If the cell type is data, then the SAR must obtain data from its own transmit buffers. Details are provided in Table 2:

| CLP |       | CELL TYPE |                                                           |                                                           |

|-----|-------|-----------|-----------------------------------------------------------|-----------------------------------------------------------|

| CLP | BIT 2 | BIT 1     | BIT 0                                                     | INDICATION                                                |

| 0   | 0     | 0         | 0                                                         | In-rate VC-level RM cell from RM-cell-contents FIFO A     |

| 0   | 0     | 0         | 1                                                         | In-rate VC-level RM cell from RM-cell-contents FIFO B     |

| 0   | 0     | 1         | 0                                                         | In-rate data cell                                         |

| 0   | 0     | 1         | 1                                                         | Reserved                                                  |

| 0   | 1     | 0         | 0                                                         | In-rate VP-level RM cell from RM-cell-contents FIFO A     |

| 0   | 1     | 0         | 1                                                         | In-rate VP-level RM cell from RM-cell-contents FIFO B     |

| 0   | 1     | 1         | 0                                                         | Reserved                                                  |

| 0   | 1     | 1         | 1                                                         | Reserved                                                  |

| 1   | 0     | 0         | 0                                                         | Out-of-rate VC-level RM cell from RM-cell-contents FIFO C |

| 1   | 0     | 0         | 1                                                         | Out-of-rate VC-level RM cell from RM-cell-contents FIFO D |

| 1   | 0     | 1         | 0                                                         | Out-of-rate data cell                                     |

| 1   | 0     | 1         | 1                                                         | Reserved                                                  |

| 1   | 1     | 0         | 0                                                         | Out-of-rate VP-level RM cell from RM-cell-contents FIFO C |

| 1   | 1     | 0         | 1 Out-of-rate VP-level RM cell from RM-cell-col<br>FIFO D |                                                           |

| 1   | 1     | 1         | 0                                                         | Reserved                                                  |

| 1   | 1     | 1         | 1                                                         | Reserved                                                  |

| Table 2  | Novt-Coll | Rogistor | Coll-Type | Definition |

|----------|-----------|----------|-----------|------------|

| Table 2. | Mext-Cell | register | Cell-Type | Demilion   |

If an RM cell is sent, the TNETA1575 reads the payload portion for the cell from the appropriate FIFO, using 12 sequential accesses to the associated control-memory location.

#### RM-cell-contents FIFO A

When the TNETA1575 reads the next-cell register and an indication is given that an RM cell should be sent from the RM-cell-contents FIFO A, the TNETA1575 must make 12 accesses to control-memory location 10001h to fetch one entire cell payload. The data that is returned by the TNETA1585 is in big-endian format as follows:

| Byte 0 (31–24) | Bvte 1 (23–16) | Byte 2 (15–8) | Byte 3 (7–0) |

|----------------|----------------|---------------|--------------|

| Byle 0 (31–24) | Byte I (23–10) | Dyte 2 (15–6) | Byte 3 (7–0) |

The ordering and formatting of data (as it is sequentially read from this register) is

Word 0 – Bytes 0, 1, 2, 3 Word 1 – Bytes 0, 1, 2, 3

#### RM-cell-contents FIFO B

When the TNETA1575 reads the next-cell register and an indication is given than an RM cell should be sent from the RM-cell-contents FIFO B, the TNETA1575 must make 12 accesses to control-memory location 10002h to fetch one entire cell payload. The data that is returned by the TNETA1585 is in big-endian format as follows:

| Byte 0 (31–24) Byte 1 (23–16) Byte 2 (15–8) Byte 3 (7–0) |                |                |  |

|----------------------------------------------------------|----------------|----------------|--|

|                                                          | Byte 0 (31–24) | Byte 1 (23–16) |  |

The ordering and formatting of data (as it is sequentially read from this register) is

```

Word 0 – Bytes 0, 1, 2, 3

Word 1 – Bytes 0, 1, 2, 3

•

```

#### RM-cell-contents FIFO C

When the TNETA1575 reads the next-cell register and an indication is given that an RM cell should be sent from the RM-cell-contents FIFO C, the TNETA1575 must make 12 accesses to control-memory location 10003h to fetch one entire cell payload. The data that is returned by the TNETA1585 is in big-endian format as follows:

| Byte 0 (31–24) Byte 1 (23–16) Byte 2 (15–6) Byte 3 (7–0) | Byte 0 (31–24) | Byte 1 (23–16) | Byte 2 (15–8) | Byte 3 (7–0) |

|----------------------------------------------------------|----------------|----------------|---------------|--------------|

|----------------------------------------------------------|----------------|----------------|---------------|--------------|

The ordering and formatting of data (as it is sequentially read from this register) is

Word 0 – Bytes 0, 1, 2, 3 Word 1 – Bytes 0, 1, 2, 3

- •

- •

#### RM-cell-contents FIFO D

When the TNETA1575 reads the next-cell register and an indication is given that an RM cell should be sent from the RM-cell contents FIFO D, the TNETA1575 must make 12 accesses to control-memory location 10004h to fetch one entire cell payload. The data that is returned by the TNETA1585 is in big-endian format as follows:

| Byte 0 (31–24) | Byte 1 (23–16) | Byte 2 (15–8) | Byte 3 (7–0) |

|----------------|----------------|---------------|--------------|

The ordering and formatting of data (as it is sequentially read from this register) is

Word 0 – Bytes 0, 1, 2, 3 Word 1 – Bytes 0, 1, 2, 3

#### coprocessor interface

The coprocessor interface consists of a group of unidirectional serial channels through which real-time information concerning the transmission and reception of cells by the SAR/switch port is passed between the TNETA1585 and the SAR/switch port. Reset and interrupt capabilities are also provided by the coprocessor interface. The unidirectional serial-interface implementation by the TNETA1575 SAR is described below. Similar requirements apply when interfacing to a different SAR device or a switch port. The coprocessor interface consists of:

received cell-indication interface (RCCX) transmitted cell-indication interface (TCCX) data-availability interface (DAX) COP full-indication interface (COPFULL)

#### received-cell-indication interface (RCCX)

A serial-bit interface allows the TNETA1575 to signal to the TNETA1585 that a cell has been received on the UTOPIA interface on a particular channel. This interface is necessary to avoid duplicating the hardware that is used to resolve a virtual path identifier (VPI) or virtual channel identifier (VCI) to a channel number. When a cell is received, the VPI/VCI value from the header is extracted by the TNETA1575 and is used as a key in a lookup algorithm to resolve its associated channel number. When the lookup is complete, the TNETA1575 passes relevant information to the TNETA1585 by sending a 13-bit frame formatted as follows:

| Channel number (12–2) | Good/bad cell indicator (1) | Framing (0) |

|-----------------------|-----------------------------|-------------|

|-----------------------|-----------------------------|-------------|

Bits 12-2 (channel number). These bits indicate which of the 2K channels the last cell was received on.

Bit 1 (good/bad cell indicator). This bit indicates whether or not the last cell passed the lookup test or if it should be discarded. The bit is encoded as follows:

| BIT 1 | INDICATION                                      |

|-------|-------------------------------------------------|

| 0     | Cell is good (VPI/VCI was found in the lookup). |

| 1     | Cell should be discarded.                       |

Bit 0 (framing). This bit is set to a 1 to denote the start of a frame.

The frame is transmitted to the TNETA1585 through the RCCX terminal starting with bit 0. When a frame is not actively being transmitted, the RCCX terminal is driven to a 0.

SDNS041 - NOVEMBER 1996

#### transmitted-cell-indication interface (TCCX)

A single-bit interface allows the TNETA1575 to signal to the TNETA1585 that a cell will be transmitted on a particular channel. This interface can be used to facilitate statistics processing in the TNETA1585 and to aid in ATM Forum available-bit-rate scheduling. When the TNETA1575 determines that it has the data to send a cell, it simultaneously sends an 18-bit frame to the TNETA1585 that is formatted as follows. The information reflected by this interface confirms the information reflected in the next-cell register, if the TNETA1575 is transmitting a TNETA1585 scheduled cell.

| CHANNEL CLP<br>NUMBER INDICATOR CELL TYPE |   | SCHEDULING<br>SOURCE | SEND<br>ACKNOWLEDGE | FRAMING |   |  |

|-------------------------------------------|---|----------------------|---------------------|---------|---|--|

| BIT                                       |   |                      |                     |         |   |  |

| 17–7                                      | 6 | 5–3                  | 2                   | 1       | 0 |  |

Bits 17–7 (channel number). These bits indicate which one of the 2K channels transmitted the last cell.

Bit 6 (CLP). This field contains the cell-loss-priority indication that was inserted in the outgoing cell's header.

Bits 5-3 (cell type). This field indicates what type of cell was sent. This field, along with the CLP bit, indicates the origin of the cell sent. Details are provided in Table 3.

| CLP |       | CELL TYPE |       | INDICATION                                                |

|-----|-------|-----------|-------|-----------------------------------------------------------|

| CLP | BIT 2 | BIT 1     | BIT 0 | INDICATION                                                |

| 0   | 0     | 0         | 0     | In-rate VC-level RM cell from RM-cell-contents FIFO A     |

| 0   | 0     | 0         | 1     | In-rate VC-level RM cell from RM-cell-contents FIFO B     |

| 0   | 0     | 1         | 0     | In-rate data cell                                         |

| 0   | 0     | 1         | 1     | Reserved                                                  |

| 0   | 1     | 0         | 0     | In-rate VP-level RM cell from RM-cell-contents FIFO A     |

| 0   | 1     | 0         | 1     | In-rate VP-level RM cell from RM-cell-contents FIFO B     |

| 0   | 1     | 1         | 0     | Reserved                                                  |

| 0   | 1     | 1         | 1     | Reserved                                                  |

| 1   | 0     | 0         | 0     | Out-of-rate VC-level RM cell from RM-cell-contents FIFO C |

| 1   | 0     | 0         | 1     | Out-of-rate VC-level RM cell from RM-cell-contents FIFO D |

| 1   | 0     | 1         | 0     | Out-of-rate data cell                                     |

| 1   | 0     | 1         | 1     | Reserved                                                  |

| 1   | 1     | 0         | 0     | Out-of-rate VP-level RM cell from RM-cell-contents FIFO C |

| 1   | 1     | 0         | 1     | Out-of-rate VP-level RM cell from RM-cell-contents FIFO D |

| 1   | 1     | 1         | 0     | Reserved                                                  |

| 1   | 1     | 1         | 1     | Reserved                                                  |

#### Table 3. TCCX Cell-Type Definition

Bit 2 (scheduling source). This bit indicates whether the cell was scheduled directly from the TNETA1575 scheduler table or if it was scheduled by the TNETA1585. This bit is encoded as follows:

| BIT 2                      | INDICATION                     |  |

|----------------------------|--------------------------------|--|

| 0                          | Scheduler-table scheduled cell |  |

| 1 TNETA1585 scheduled cell |                                |  |

#### transmitted-cell-indication interface (TCCX) (continued)

Bit 1 (send acknowledge). This bit indicates whether the SAR will send a cell. The bit is encoded as follows:

| BIT 1 | INDICATION             |

|-------|------------------------|

| 0     | Cell will not be sent. |

| 1     | Cell will be sent.     |

Bit 0 (framing). This bit is set to a 1 to denote the start of a frame.

The frame is transmitted to the coprocessor through the TCCX terminal starting with bit 0. When a frame is not actively being transmitted, the TCCX terminal is driven to a 0.

#### data-availability interface (DAX)

A single-bit interface allows the TNETA1575 to signal to the TNETA1585 when data is available or unavailable on a particular channel. A 13-bit frame is sent to the TNETA1585 for a particular channel only when its data-availability status changes (i.e., when the host writes to the transmit-queue register to notify the TNETA1575 that a packet has been queued, or if the TNETA1575 completes segmentation of the last packet on a particular channel). The frame is formatted as follows:

| Channel number (12–2) | Data available/unavailable (1) | Framing (0) |

|-----------------------|--------------------------------|-------------|

Bits 12-2 (channel number). These bits indicate which one of the 2K channels has available or unavailable data.

Bit 1 (data available/unavailable). This field indicates the new status of the segmentation queue for the given channel number. This field is encoded as follows:

| BIT 1 | INDICATION                                      |

|-------|-------------------------------------------------|

| 0     | All data has been segmented (data unavailable). |

| 1     | New data has been added (data available).       |

Bit 0 (framing). This bit is set to a 1 to denote the start of a frame.

The frame is transmitted to the TNETA1585 through the DAX terminal starting with bit 0. When a frame is not actively being transmitted, the DAX terminal is driven to a 0.

#### COP full-indication interface (COPFULL)

A single-bit interface allows the TNETA1585 to signal to the TNETA1575 the status of the TNETA1585's receive-UTOPIA-interface FIFO. When in ATM mode ( $PHY/\overline{ATM} = 0$ ), this output goes high when the receive-UTOPIA-interface FIFO is full. When in PHY mode ( $PHY/\overline{ATM} = 1$ ), this output goes high when the FIFO is within four bytes of being full.

SDNS041 - NOVEMBER 1996

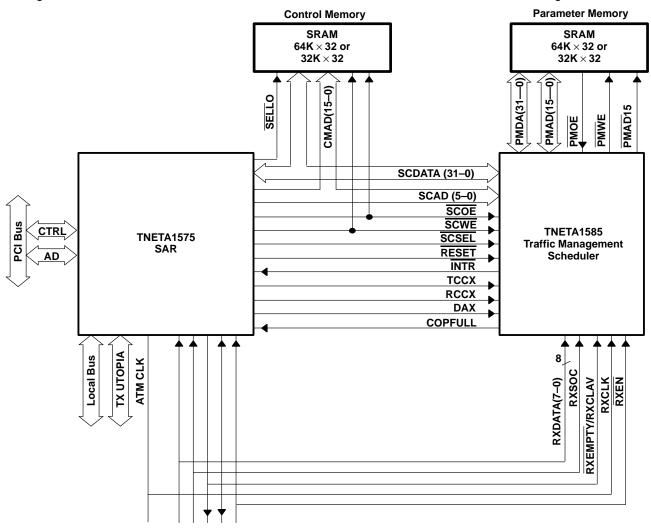

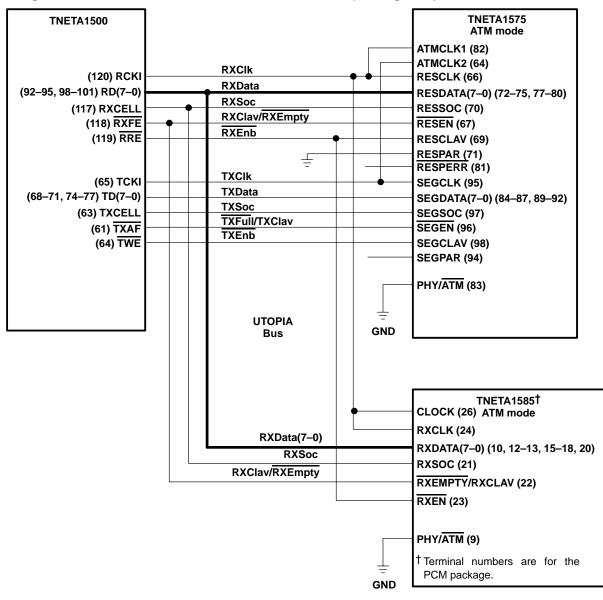

#### TNETA1585-to-TNETA1575 interconnection

Figure 1 shows the interconnection of the TNETA1575 SAR and the TNETA1585 traffic management scheduler.

#### Figure 1. TNETA1585 Interconnection to TNETA1575

#### receive-UTOPIA interface

The TNETA1585 receives ATM cells through the receive-UTOPIA interface. This interface is designed in accordance with the ATM Forum UTOPIA revision 2.01 specification and is configurable as either an 8-bit PHY or ATM interface. The ATM mode is chosen when the TNETA1585 interfaces with a framer (such as the TNETA1500). The PHY mode is chosen when the TNETA1585 interfaces with a switch port. The operation of this dual PHY/ATM interface requires the use of the PHY/ATM input.

In both modes, the receive UTOPIA interface on the TNETA1585 monitors only, i.e., the device does not actively participate in the UTOPIA protocol. If the system is to work correctly, a fully compliant UTOPIA-peer device is required. This interface is designed in this manner so that the TNETA1585 could be connected as a peer to the TNETA1575, which are both then connected to an ATM (e.g., switch port) or PHY device (e.g., TNETA1500).

#### receive-UTOPIA interface (continued)

In ATM mode, the TNETA1585 receive-UTOPIA interface behaves as an RX UTOPIA, monitoring incoming cells from a framer such as the TNETA1500 into the reassembly interface of a SAR device such as the TNETA1575. The PHY/ATM is active low in this mode. An external clock input provides for data transfers/synchronization between the TNETA1585 receive-UTOPIA and TNETA1500 interfaces.

In PHY mode, the TNETA1585 receive-UTOPIA interface behaves as a TX UTOPIA of a PHY device, monitoring incoming cells from a switching element into the reassembly interface of a SAR device such as the TNETA1575. The PHY/ATM is active high in this mode. An external clock input provides for data transfers/synchronization between the TNETA1585 receive-UTOPIA and ATM switching-element TX UTOPIA interfaces.

The receive-UTOPIA interface operates as a synchronous 8-bit (byte-wide) data path. The interface functions with both octet-level and cell-level handshaking. The maximum clock speed supported by this interface is 33 MHz.

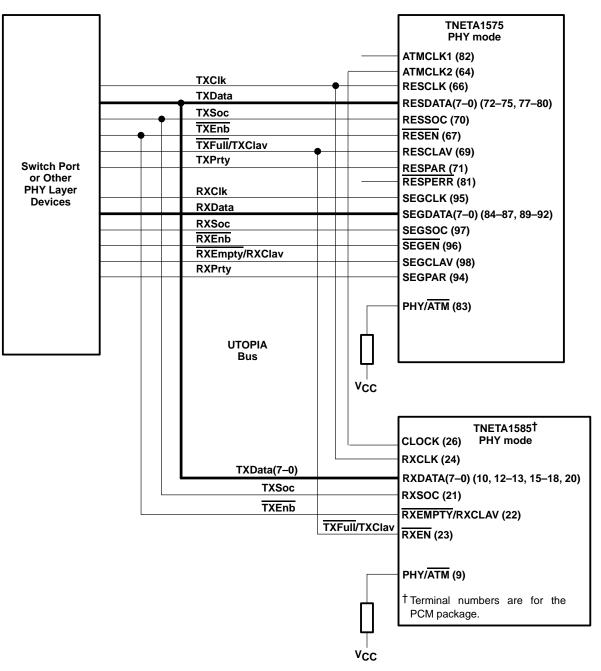

#### receive-UTOPIA interface in PHY mode

The receive-UTOPIA interface on the TNETA1585 operates as the TX UTOPIA interface in a PHY device when the TNETA1585 is operating in PHY mode. The PHY/ATM input has to be active high to operate in PHY mode.

This cell interface works on the low-to-high transition of RXCLK to sample and generate signals.

| TNETA1585<br>SIGNAL NAME | UTOPIA<br>SIGNAL NAME |

|--------------------------|-----------------------|

| RXCLK                    | TXCLK                 |

| RXDATA(7–0)              | TXDATA(7–0)           |

| RXSOC                    | TXSOC                 |

| RXEN                     | TXFull/TXClav         |

| RXEMPTY/RXCLAV           | TXEnb                 |

SDNS041 - NOVEMBER 1996

Figure 2. UTOPIA Bus Connections In PHY Mode

#### receive-UTOPIA interface in ATM mode

The receive-UTOPIA interface on the TNETA1585 functions as the RX UTOPIA interface in a ATM device when the TNETA1585 is operating in ATM mode. The PHY/ATM input has to be low to operate in ATM mode.

This receive-cell interface works on the low-to-high transition of RXCLK to sample and generate signals.

| TNETA1585<br>SIGNAL NAME | UTOPIA<br>SIGNAL NAME |

|--------------------------|-----------------------|

| RXCLK                    | RXCLK                 |

| RXDATA(7–0)              | RXDATA(7–0)           |

| RXSOC                    | RXSOC                 |

| RXEMPTY/RXCLAV           | RXClav/RxEmpty        |

| RXEN                     | RXEnb                 |

connecting the TNETA1585 to the UTOPIA bus in ATM mode (see Figure 3)

SDNS041 - NOVEMBER 1996

#### parameter-memory interface

The parameter-memory interface on the TNETA1585 is used for interface to the external SRAM containing the connection-state information and parameters required per channel. The interface consists of a 32-bit data bus, a 16-bit address bus, an output-enable terminal, and a write-enable terminal. The interface also provides an additional address terminal (PMAD15) that can be used with address terminal (PMAD15) to provide support for SRAM bank switching. This allows the user to use two  $32K \times 32$  banks of SRAM instead of one  $64K \times 32$ bank by using PMAD15 and PMAD15 as chip selects. The TNETA1585 is designed to operate with a 15 ns or faster asynchronous SRAM. The total SRAM requirement for parameter memory to support 2K connections is  $32K \times 32$ .

The parameter-memory information is accessed by the host via the slave interface. Details of the parameters in parameter memory are found in the TNETA1585 Programmer's Reference Guide, literature number SDNU016.

#### JTAG interface

The TNETA1585 supports boundary scan through a five-wire JTAG interface in accordance with IEEE Std 1149.1-1990 (includes IEEE Std 1149.1a-1993) IEEE Standard Test-Access Port and Boundary-Scan Architecture.

The maximum operating frequency is 10 MHz for the JTAG interface.

#### JTAG instruction set

The TNETA1585 supports the following instructions:

| INSTRUCTION    | OP CODE (BINARY FORMAT) |

|----------------|-------------------------|

| EXTEST         | 000                     |

| IDCODE         | 100                     |

| SAMPLE/PRELOAD | 001                     |

| BYPASS         | 111                     |

| INTERNAL SCAN  | 010                     |

| HIGH Z         | 101                     |

idcode

|              | VARIANT | PART NUMBER | MANUFACTURER | LSB |

|--------------|---------|-------------|--------------|-----|

| Bit number   | 31–28   | 27–12       | 11–1         | 0   |

| Bincary code | 0000    | TBD         | 00000010111  | 1   |

SDNS041 - NOVEMBER 1996

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to the GND terminals.

- 2. Applies for external input and bidirectional buffers without hysteresis.  $V_I > V_{CC}$  does not apply to fail-safe terminals. Use  $V_I > V_{CC(5 V)}$  for 5-V tolerant terminals.

- 3. Applies for external output and bidirectional buffers.  $V_O > V_{CC}$  does not apply to fail-safe terminals. Use  $V_O > V_{CC(5 V)}$  for 5-V tolerant terminals.

#### recommended operating conditions

|                |                                  |                               | MIN | NOM | MAX                  | UNIT |

|----------------|----------------------------------|-------------------------------|-----|-----|----------------------|------|

| VCC            | Supply voltage                   | Commercial                    | 3   | 3.3 | 3.6                  | V    |

| VCC(5 V)       | Supply voltage, 5-V tolerant TTL | Commercial                    | 4.5 | 5   | 5.5                  | V    |

| <u>۱</u>       | loout veltege                    | TTL                           | 0   |     | VCC                  | V    |

| VI             | Input voltage                    | 5-V tolerant TTL              | 0   |     | VCC(5 V)             | v    |

| Va             | Output voltage                   | TTL                           | 0   |     | Vcc                  | V    |

| Vo             | Ouput voltage                    | 5-V tolerant TTL <sup>‡</sup> | 0   |     | Vcc                  | v    |

|                | High-level input voltage         | TTL                           | 2   |     | Vcc                  | V    |

| VIH            | ngn-level input voltage          | 5-V tolerant TTL              | 2   |     | V <sub>CC(5</sub> V) | v    |

| \/             |                                  | TTL                           | 0   |     | 0.8                  | V    |

| VIL            | Low-level input voltage          | 5-V tolerant TTL              | 0   |     | 0.8                  | v    |

| Т <sub>А</sub> | Operating free-air temperature   |                               | 0   |     | 70                   | °C   |

<sup>‡</sup>V<sub>CC</sub> must be applied to drive the output to a high-impedance state (Z) for 5-V tolerant operation.

SDNS041 – NOVEMBER 1996

## electrical characteristics over recommended operating conditions (unless otherwise noted)

|                 | PARAMETER                           |                  | TEST CONDITIONS                                     | MIN                  | MAX  | UNIT |

|-----------------|-------------------------------------|------------------|-----------------------------------------------------|----------------------|------|------|

|                 |                                     | TTL              | I <sub>OH</sub> = 8 mA                              |                      |      |      |

| Val             | High lovel output voltage           |                  | I <sub>OH</sub> = 4 mA                              | V <sub>CC</sub> -0.6 |      | V    |

| VOH             | High-level output voltage           | 5-V tolerant TTL | I <sub>OH</sub> = 8 mA                              | V <sub>CC</sub> -0.6 |      | v    |

|                 |                                     |                  | I <sub>OH</sub> = 4 mA                              | VCC-0.0              |      |      |

|                 |                                     | TTL              | I <sub>OL</sub> = 8 mA                              |                      | 0.4  |      |

| Val             | Low-level output voltage            |                  | I <sub>OL</sub> = 4 mA                              |                      | 0.4  | V    |

| VOL             |                                     | 5-V tolerant TTL | I <sub>OL</sub> = 8 mA                              |                      | 0.4  | v    |

|                 |                                     |                  | I <sub>OL</sub> = 4 mA                              |                      | 0.4  |      |

|                 | High-level input current            | TTL              | V <sub>I</sub> = V <sub>IH (max)</sub> , See Note 4 |                      | ±1   | μA   |

| ін              | nigh-level input current            | 5-V tolerant TTL | $V_{I} = V_{IH}$ (min)                              |                      | -760 | μΛ   |

|                 | Low-level input current             | TTL              | VI = VIL (min), See Note 5                          |                      | ±1   | μA   |

| <sup>I</sup> IL | Low-level input current             | 5-V tolerant TTL | $v_1 = v_{1L} (min),$ See Note 3                    |                      | ±1   | μΑ   |

| 10-             | High impodence state output current | TTL              |                                                     |                      | ±20  |      |

| loz             | High-impedance-state output current | 5-V tolerant TTL | 1                                                   |                      | ±20  | μA   |

NOTES: 4. These specifications apply only when the pulldown terminator is turned off.

5. These specifications apply only when the pullup terminator is turned off.

#### recommended power-supply sequencing for mixed-voltage devices

The recommended power-supply sequencing in a mixed-voltage system is as follows:

- When the power supply is being turned on, all 3.3-V and 5-V supplies should start ramping from 0 V and reach 95 percent of their end-point values within a 25-ms time window. All bus contention between the TNETA1585 and external devices is eliminated by the end of the 25-ms time window. The preferred order of supply ramping is to ramp the 3.3-V supply followed by the 5-V supply. This order is not mandatory, but it allows a larger cumulative number of power supply on events than the reverse order.

- When the power supply is being turned off, all 3.3-V and 5-V supplies should start ramping from steady state values and reach 5 percent of these values within a 25-ms time window. All bus contention between the TNETA1585 and external devices is eliminated by the end of the 25-ms time window. The preferred order of supply ramping is to ramp down the 5-V supply followed by the 3.3-V supply. This order is not mandatory, but it allows a larger cumulative number of power supply off events than the reverse order.

If these precautions and guidelines are not followed, the TNETA1585 device may experience failures.

SDNS041 - NOVEMBER 1996

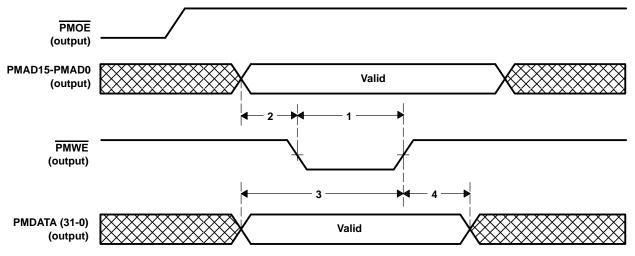

#### switching characteristics (see Note 6 and Figure 4) parameter-memory interface - write operation

| NO. |                        | PARAMETER                                                     | MIN | MAX | UNIT |

|-----|------------------------|---------------------------------------------------------------|-----|-----|------|

| 1   | <sup>t</sup> w(PMWEL)  | Pulse duration, PMWE low                                      | 28  | 31  | ns   |

| 2   | <sup>t</sup> d(PMWE)1  | Delay time, PMAD15–PMAD0 valid to $\overline{PMWE}\downarrow$ | 12  | 15  | ns   |

| 3   | <sup>t</sup> d(PMWE)2  | Delay time, PMDATA31–PMDATA0 valid to PMWE↑                   | 10  | 14  | ns   |

| 4   | <sup>t</sup> d(PMDATA) | Delay time, PMWE↑ to PMDATA31–PMDATA0 invalid                 | 15  | 19  | ns   |

Figure 4. Parameter-Memory-Interface Write Operation

SDNS041 - NOVEMBER 1996

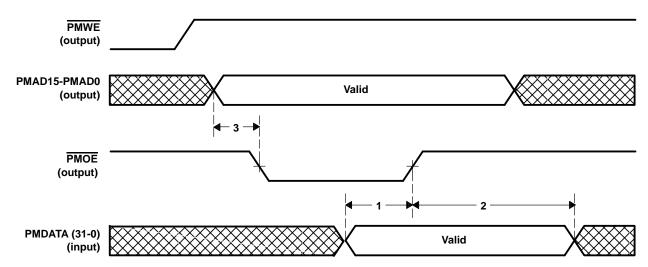

#### switching characteristics (see Note 6 and Figure 5) parameter-memory interface - read operation

| NO. |                         | PARAMETER                                                     | MIN | MAX | UNIT |

|-----|-------------------------|---------------------------------------------------------------|-----|-----|------|

| 1   | <sup>t</sup> su(PMDATA) | Setup time, PMDATA31–PMDATA0 valid before PMOE                | 10  |     | ns   |

| 2   | <sup>t</sup> h(PMDATA)  | Hold time, PMDATA31–PMDATA0 valid after PMOE↑                 | 0   |     | ns   |

| 3   | <sup>t</sup> d(PMOE)    | Delay time, PMAD15–PMAD0 valid to $\overline{PMOE}\downarrow$ |     | 3   | ns   |

Figure 5. Parameter-Memory-Interface Read Operation

#### SDNS041 - NOVEMBER 1996

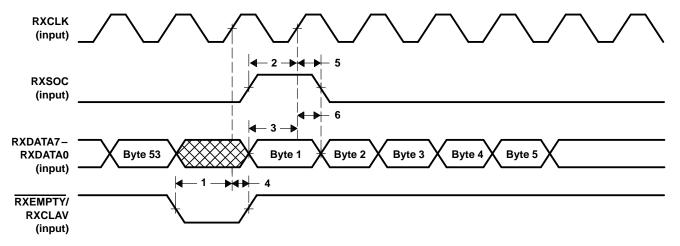

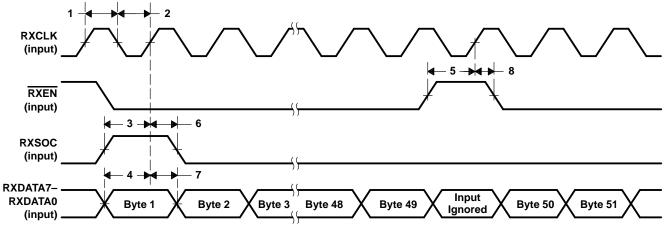

# timing requirements (see Note <u>6 and</u> Figure 6) receive-UTOPIA interface (PHY/ATM low)

| NO. |                                |                                                         | MIN | MAX | UNIT |

|-----|--------------------------------|---------------------------------------------------------|-----|-----|------|

| 1   | tsu(RXEMPTY/RXCLAV)            | Setup time, RXEMPTY/RXCLAV low before RXCLK             | 10  |     | ns   |

| 2   | <sup>t</sup> su(RXSOC)         | Setup time, RXSOC high before RXCLK↑                    | 10  |     | ns   |

| 3   | <sup>t</sup> su(RXDATA)        | Setup time, RXDATA(7–0) valid before RXCLK <sup>↑</sup> | 10  |     | ns   |

| 4   | <sup>t</sup> h(RXEMPTY/RXCLAV) | Hold time, RXEMPTY/RXCLAV low after RXCLK1              | 1   |     | ns   |

| 5   | <sup>t</sup> h(RXSOC)          | Hold time, RXSOC high after RXCLK↑                      | 1   |     | ns   |

| 6   | <sup>t</sup> h(RXDATA)         | Hold time, RXDATA(7–0) valid after RXCLK↑               | 1   |     | ns   |

Figure 6. Receive-UTOPIA Interface (PHY/ATM Low)

SDNS041 – NOVEMBER 1996

# timing requirements (see Note <u>6 and</u> Figure 7) receive-UTOPIA interface (PHY/ATM) high

| NO. |                         |                                                           | MIN | MAX | UNIT |

|-----|-------------------------|-----------------------------------------------------------|-----|-----|------|

| 1   | <sup>t</sup> w(RXCLKH)  | Pulse duration, RXCLK high                                | 12  | 18  | ns   |

| 2   | <sup>t</sup> w(RXCLKL)  | Pulse duration, RXCLK low                                 | 12  | 18  | ns   |

| 3   | t <sub>su</sub> (RXSOC) | Setup time, RXSOC high before RXCLK1                      | 10  |     | ns   |

| 4   | <sup>t</sup> su(RXDATA) | Setup time, RXDATA7-RXDATA0 valid before RXCLK1           | 10  |     | ns   |

| 5   | <sup>t</sup> su(RXEN)   | Setup time, RXEN high before RXCLK↑                       | 10  |     | ns   |

| 6   | <sup>t</sup> h(RXSOC)   | Hold time, RXSOC high after RXCLK <sup>↑</sup>            | 1   |     | ns   |

| 7   | <sup>t</sup> h(RXDATA)  | Hold time, RXDATA7-RXDATA0 valid after RXCLK <sup>↑</sup> | 1   |     | ns   |

| 8   | <sup>t</sup> h(RXEN)    | Hold time, RXEN high after RXCLK↑                         | 1   |     | ns   |

Figure 7. Receive-UTOPIA Interface (PHY/ATM High)

SDNS041 - NOVEMBER 1996

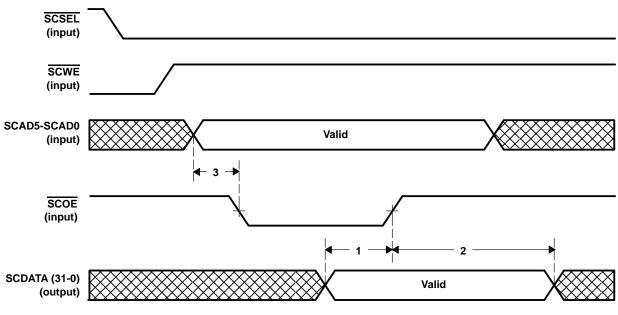

#### switching characteristics (see Note 6 and Figure 8) slave interface - read operation

| NO. |                         | PARAMETER                                                    | MIN | MAX | UNIT |

|-----|-------------------------|--------------------------------------------------------------|-----|-----|------|

| 1   | <sup>t</sup> su(SCDATA) | Setup time, SCDATA31–SCDATA0 valid before SCOE↑              | 10  |     | ns   |

| 2   | <sup>t</sup> h(SCDATA)  | Hold time, SCDATA31–SCDATA0 valid after SCOE↑                | 0   |     | ns   |

| 3   | <sup>t</sup> d(SCOE)    | Delay time, SCAD5–SCAD0 valid to $\overline{SCOE}\downarrow$ |     | 3   | ns   |

Figure 8. Slave-Interface Read Operation

SDNS041 - NOVEMBER 1996

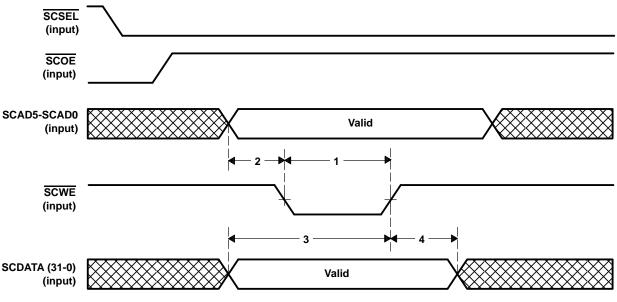

# timing requirements (see Note 6 and Figure 9) slave interface – write operation

| NO. |                        |                                                              | MIN | MAX | UNIT |

|-----|------------------------|--------------------------------------------------------------|-----|-----|------|

| 1   | <sup>t</sup> w(SCWEL)  | Pulse duration, SCWE low                                     | 28  | 31  | ns   |

| 2   | <sup>t</sup> d(SCWE)1  | Delay time, SCAD5–SCAD0 valid to $\overline{SCWE}\downarrow$ | 12  | 15  | ns   |

| 3   | <sup>t</sup> d(SCWE)2  | Delay time, SCDATA31–SCDATA0 valid to SCWE↑                  | 10  | 14  | ns   |

| 4   | <sup>t</sup> d(SCDATA) | Delay time, SCWE↑ to SCDATA31–SCDATA0 invalid                | 15  | 19  | ns   |

#### SDNS041 - NOVEMBER 1996

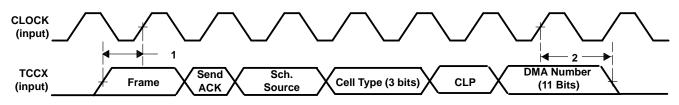

#### timing requirements (see Note 6 and Figure 10) coprocessor interface (TCCX)

| NO. |                       |                                                | MIN | MAX | UNIT |

|-----|-----------------------|------------------------------------------------|-----|-----|------|

| 1   | <sup>t</sup> su(TCCX) | Setup time, TCCX high before CLOCK $\uparrow$  | 10  |     | ns   |

| 2   | <sup>t</sup> h(TCCX)  | Hold time, TCCX valid after CLOCK <sup>↑</sup> | 1   |     | ns   |

NOTE 6: All timing requirements and switching-characteristic values are preliminary and subject to change upon production release.

Figure 10. TCCX Interface

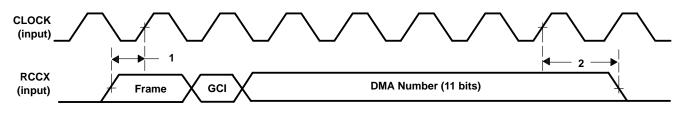

#### timing requirements (see Note 6 and Figure 11) coprocessor interface (RCCX)

| NO. |                       |                                               | MIN | MAX | UNIT |

|-----|-----------------------|-----------------------------------------------|-----|-----|------|

| 1   | t <sub>su(RCCX)</sub> | Setup time, RCCX high before CLOCK $\uparrow$ | 10  |     | ns   |

| 2   | <sup>t</sup> h(RCCX)  | Hold time, RCCX valid after CLOCK $\uparrow$  | 1   |     | ns   |

NOTE 6: All timing requirements and switching-characteristic values are preliminary and subject to change upon production release.

#### Figure 11. RCCX Interface

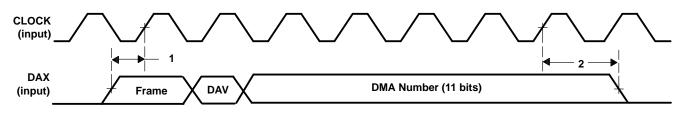

#### timing requirements (see Note 6 and Figure 12) coprocessor interface (DAX)

| NO. |                                                                     | MIN | MAX | UNIT |

|-----|---------------------------------------------------------------------|-----|-----|------|

| 1   | t <sub>SU(DAX)</sub> Setup time, DAX high before CLOCK <sup>↑</sup> | 10  |     | ns   |

| 2   | th(DAX) Hold time, DAX valid after CLOCK1                           | 1   |     | ns   |

NOTE 6: All timing requirements and switching-characteristic values are preliminary and subject to change upon production release.

Figure 12. DAX Interface

SDNS041 - NOVEMBER 1996

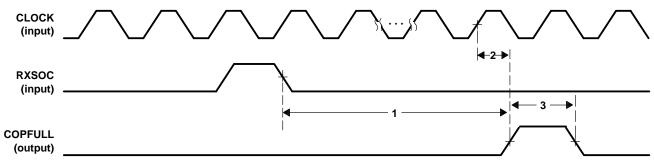

#### switching characteristics (see Notes 6 and 7 and Figure 13) coprocessor interface

| NO. | PARAMETER                                               |    |    | UNIT           |

|-----|---------------------------------------------------------|----|----|----------------|

| 1   | <sup>t</sup> d(COPFULL)1 Delay time, RXSOC↓ to COPFULL↑ | 53 |    | Clock<br>Cycle |

| 2   | <sup>t</sup> d(COPFULL)2 Delay time, CLOCK↑ to COPFULL↑ | 2  | 11 | ns             |

| 3   | <sup>t</sup> w(COPFULLH) Pulse duration, COPFULL high   | 1  |    | Clock<br>Cycle |

NOTES: 6. All timing requirements and switching-characteristic values are preliminary and subject to change upon production release. 7. The COPFULL signal is asserted high after the last byte of the seventh cell in the UTOPIA FIFO is received by the TNETA1585, or if a new RXSOC is received by the TNETA1585 for the cell that fills the FIFO. It remains high until a cell location is available in the FIFO.

Figure 13. COPFULL Timing

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated