SDLS066

- Independent Read/Write Addressing Permits Simultaneous Reading and Writing

- Organized as Eight Words of Two Bits Each

- Fast Access Times: From Read Enable . . . 15 ns Typical From Read Select . . . 33 ns Typical

- 3-State Outputs Simplify Use in \_ Bus-Organized Systems

- Applications: Stacked Data Registers Scratch-Pad Memory Buffer Storage Between Processors Fast Multiplication Schemes

## description

The SN74172, containing the equivalent of 201 gates on a monolithic chip, is a high-performance 16-bit register file organized as eight words of two bits each.

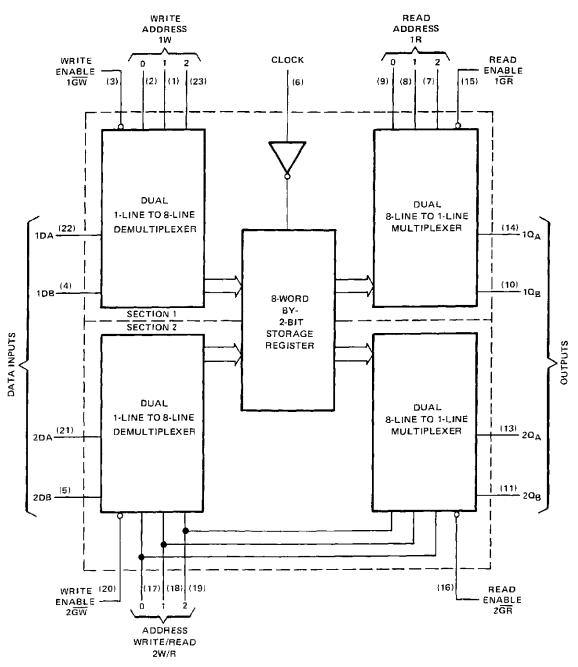

Multiple address decoding circuitry is used so that the read and write operation can be performed independently on two word locations. This provides a true simultaneous read/write capability. Basically, the file consists of two distenct sections (see Figure 1).

Section 1 permits the writing of data into any two-bit word location while reading two bits of data from another location simultaneously. To provide this flexibility, independent decoding is incorporated.

Section 2 of the register file is similar to section 1 with the exception that common read/write address circuitry is employed. This means that section 2 can be utilized in one of three modes:

- 1) Writing new data into two bits

- 2) Reading from two bits

- 3) Writing into and simultaneously reading from the same two bits.

Regardless of the mode, the operation of section 2 is entirely independent of section 1.

| SN741             |            | N P<br>P VIEW | ACKAGE<br>/)    |

|-------------------|------------|---------------|-----------------|

| 1W1               | 1          | U 24          | Dvcc            |

| 1W0               | 2          | 23            | 1W2             |

| 1GW               | 3          | 22            | 1DA             |

| 1DB               | 4          | 21            | 2DA             |

| 2DB               | 5          | 20            | 2GW             |

| CLK (             | 6          | 19            | 2W/R2           |

| 1R2 (             | 7          | 18            | 2W/R1           |

| 1R1 [             | 8          | 17            | 2W/R0           |

| 1R0 [             | <b>_</b> 9 | 16            | 2 GR            |

| 10 <sub>8</sub> [ | ]10        | 15            | ] 1GR           |

| 20 <sub>B</sub> [ | 11         | 14            | ]10A            |

| GND [             | 12         | 13            | 20 <sub>A</sub> |

MAY 1972-REVISED MARCH 1988

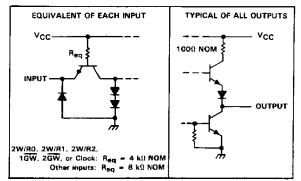

#### schematics of inputs and outputs

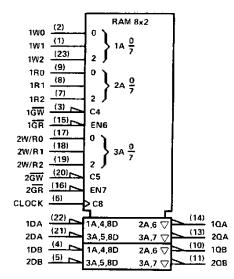

#### logic symbol<sup>†</sup>

<sup>&</sup>lt;sup>†</sup>This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### description (continued)

The three-state outputs of this register file permit connection of up to 129 compatible outputs and one Series 54/74 high-logic-level load to a common system bus. The outputs are controlled by the read-enable circuitry so that they operate as standard TTL totem-pole outputs when the appropriate read-enable input is low or they are placed in a high-impedance state when the associated read-enable input is at a high logic level. To minimize the possibility that two outputs from separate register files will attempt to take a common bus to opposite logic levels, the read-enable circuitry is designed such that disable times are shorter than enable times.

All inputs are buffered to lower the drive requirements of the clock, read/write address, and write-enable inputs to one normalized Series 54/74 load, and of all other inputs to one-half of one normalized Series 54/74 load.

| FUNCTION      | SECTION 1                         | SECTION 2                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|---------------|-----------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Write Address | 1w0, 1w1, 1w2                     | 2W/R0, 2W/R1, 2W/R2               | Binary write address selects one of eight two-bit word locations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Write Enable  | 1 <del>GW</del>                   | 2 <del>GW</del>                   | When low, permits the writing of new data into<br>the selected word location on a positive transition<br>of the clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Data Inputs   | Data Inputs 1DA, 1DB              |                                   | Data at these inputs is entered on a positive<br>transition of the clock input into the location<br>selected by the write address inputs if the write<br>enable input is low. Since the two sections are<br>independent, it is possible for both write function<br>to be activated with both write addresses selecting<br>the same word location. If this occurs and the<br>information at the data inputs is not the same for<br>both sections (i.e., $1DA \neq 2DA$ and/or<br>$1DB \neq 2DB$ ) the low-level data will predominate<br>in each bit and be stored. |  |  |  |  |  |  |  |

| Read Address  | 1R0, 1R1, 1R2                     | Common with<br>write address      | Binary write address selects one of eight two-bit word locations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Read Enable   | 1GR                               | 2GR                               | When read enable is low, the outputs assume the<br>levels of the data stored in the location selected by<br>read address inputs. When read enable is high, the                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Data Outputs  | 1Q <sub>A</sub> , 1Q <sub>B</sub> | 20 <sub>A</sub> , 20 <sub>B</sub> | associated outputs remain in the high-impedance<br>state and neither significantly load nor drive the<br>lines to which they are connected.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Clock         |                                   | СК                                | The positive-going transition of the clock input<br>will enter new data into the addressed location if<br>the write enable input is low. The clock is<br>common to both sections.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

Functions of the inputs and outputs of the SN74172 are as shown in the following table.

FIGURE 1

---

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage (see Note 1)          |   |  |  |   |  |  |  |   |  |  | - |  |   |  |    |     |      | 7 ۱   | 1 |

|--------------------------------------|---|--|--|---|--|--|--|---|--|--|---|--|---|--|----|-----|------|-------|---|

| Input voltage                        |   |  |  |   |  |  |  |   |  |  |   |  | - |  |    |     |      | 5.5 \ | 1 |

| Output voltage (see Note 2)          |   |  |  |   |  |  |  |   |  |  |   |  |   |  |    |     |      |       |   |

| Operating free-air temperature range |   |  |  |   |  |  |  |   |  |  |   |  |   |  |    |     |      |       |   |

| Storage temperature                  | - |  |  | · |  |  |  | - |  |  |   |  |   |  | -6 | 5°C | to : | 150°( | 2 |

NOTES: 1. Voltage values are with respect to network ground terminal.

2. This is the maximum voltage which should be applied to any output when it is in the high-impedance state.

#### recommended operating conditions

|                                                                      |                                       | MIN          | NOM | MAX  | UNIT |

|----------------------------------------------------------------------|---------------------------------------|--------------|-----|------|------|

| Supply voltage, V <sub>CC</sub>                                      |                                       | 4.75         | 5   | 5.25 | V    |

| High-level output current, IOH                                       |                                       | 1            |     | -5.2 | mA   |

| Low-level output current, IOL                                        |                                       |              |     | 16   | mA   |

| Clock frequency, f <sub>clock</sub>                                  | · · · · · · · · · · · · · · · · · · · | 0            |     | 20   | MHz  |

| Width of clock pulse, tw(clock)                                      |                                       | 25           |     |      | ns   |

| Low-level output current, IOL<br>Clock frequency, f <sub>clock</sub> | Write select                          | tw(clock)+10 | )   |      |      |

|                                                                      | High-level data                       | 30           |     |      | Ī    |

|                                                                      | Low-level data                        | 45           |     | _    | ns   |

|                                                                      | Write enable                          | 35           |     |      |      |

|                                                                      | Write select                          | 0            |     |      |      |

| Hota time, th(see Figure 1)                                          | Write enable                          | 0            |     |      | ns   |

|                                                                      | High-level data                       | 0            |     |      |      |

| Data release time, trelease (see Figure 1)                           | Low-level data                        | 0            |     |      | ns   |

| Operating free-air temperature, T <sub>A</sub>                       |                                       | 0            |     | 70   | °C   |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|         | PARAMETER                          | R                                          | TEST                                               | CONDITIONS                                          | MIN | TYP‡                                 | MAX  | UNIT |

|---------|------------------------------------|--------------------------------------------|----------------------------------------------------|-----------------------------------------------------|-----|--------------------------------------|------|------|

| ⊻ін     | High-level input voltage           |                                            | 1                                                  |                                                     | 2   |                                      |      | V    |

| VIL     | Low-level input voltage            |                                            |                                                    |                                                     |     |                                      | 0.8  | v    |

| VIK     | Input clamp voltage                |                                            | VCC = MIN,                                         | l <sub>I</sub> = −12 mA                             | 1   |                                      | -1.5 | V    |

| VOH     | High-level output voltage          |                                            | V <sub>CC</sub> ≠ MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = -5.2 mA | 2.4 | 3                                    |      | v    |

| VOL     | Low-level output voltage           | - <u> </u>                                 | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>IOL = 16 mA               |     | 0.2                                  | 0.4  | v    |

| lO(off) | Off-state (high-impedance state) o | output current                             | VCC = MAX.<br>VCC = MAX,                           |                                                     |     |                                      | 40   | μA   |

| 1       | Input current at maximum input     | voltage                                    | V <sub>CC</sub> = MAX,                             | · · · · · · · · · · · · · · · · · · ·               | ┼── |                                      | 1    | mA   |

| Чн      | High-level input current           |                                            | VCC = MAX,                                         | V <sub>1</sub> = 2.4 V                              |     |                                      | 40   | μA   |

| н.      | Low-level input current            | 2W/R0, 2W/R1, 2W/R2,<br>1GW, 2GW, or clock | Vcc = MAX,                                         | VI = 0.4 V                                          |     | 40<br>-40<br>1<br>40<br>-1.6<br>-0.8 | mA   |      |

|         |                                    | Any other input                            |                                                    | ·                                                   |     |                                      | -0.8 |      |

| los     | Short-circuit output current \$    |                                            | V <sub>CC</sub> = MAX                              |                                                     | -18 |                                      | -55  | mA   |

| lcc     | Supply current                     |                                            | VCC = MAX,<br>Outputs open                         | All inputs at 4.5 V,                                |     | 112                                  | 170  | mΑ   |

$^\dagger$  For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

‡All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> =  $25^{\circ}$ C.

\$Not more than one output should be shorted at a time.

# switching characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C, R<sub>L</sub> = 400 $\Omega$

|                  | PARAMETER                                                         | TEST<br>CONDITIONS      | MIN     | түр | MAX | UNIT |

|------------------|-------------------------------------------------------------------|-------------------------|---------|-----|-----|------|

| f <sub>max</sub> | Maximum clock frequency                                           |                         | 20      |     |     | MHz  |

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level cutput from read select |                         |         | 33  | 45  |      |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level output from read select |                         | ·       | 30  | 45  | ns   |

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level output from clock       | C <sub>L</sub> = 50 pF, |         | 35  | 50  | ·    |

| tp H L           | Propagation delay time, high-to-low-level output from clock       | See Figure 2            |         | 35  | 50  | ns   |

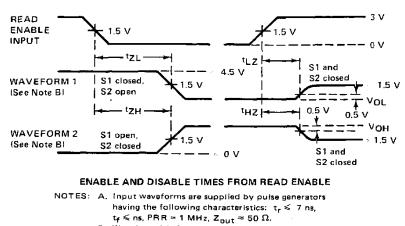

| <sup>t</sup> PZH | Output enable time to high level                                  |                         |         | 14  | 30  |      |

| <sup>t</sup> PZL | Output enable time to low level                                   |                         |         | 16  | 30  | ns   |

| tPHZ             | Output disable time from high level                               | CL = 5 ρF,              |         | 6   | 20  |      |

| TPLZ             | Output disable time from low level                                | See Figure 2            | <b></b> | 11  | 20  | nş   |

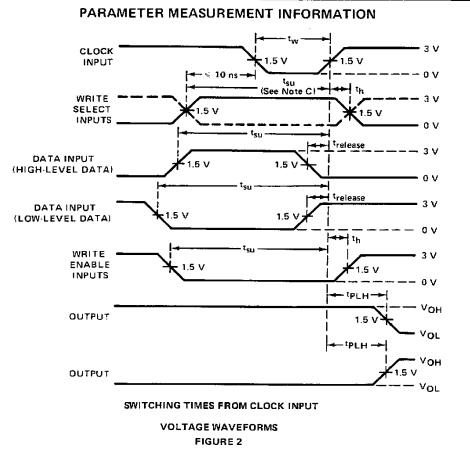

#### PARAMETER MEASUREMENT INFORMATION

tr ≤ ns, PRR ≈ 1 MHz, Z<sub>DUt</sub> ≈ 50 Ω.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled.

- C. Write select setup time, as specified, will protect data

- written into previous address. D. Load circuit is shown on page

VOLTAGE WAVEFORMS FIGURE 2 (continued)

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated