# **ICs for Consumer Electronics**

8-Bit Microcontroller with LCD-Dot Matrix Driver SDA 20C440

Advanced Data Sheet 01.94

| SDA 20C44<br>Revision H |                                        | 01.94 |  |  |

|-------------------------|----------------------------------------|-------|--|--|

| Previous Re             | eleases:                               | 05.93 |  |  |

| Page                    | Subjects (changes since last revision) |       |  |  |

|                         |                                        |       |  |  |

|                         |                                        |       |  |  |

#### **Data Classification**

#### **Maximum Ratings**

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

#### Characteristics

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25$  °C and the given supply voltage.

#### **Operating Range**

In the operating range the functions given in the circuit description are fulfilled.

For detailed technical information about "**Processing Guidelines**" and "**Quality Assurance**" for ICs, see our "**Short Form Catalog**".

#### Edition 01.94

This edition was realized using the software system FrameMaker®

# Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, D-81541 München.

© Siemens AG 1994. All Rights Reserved.

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics. Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you - get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

### Contents

|        | Fastures                                    |

|--------|---------------------------------------------|

| 1      | Features                                    |

| 1.1    | Functional Overview                         |

| 1.2    | Pin Configuration                           |

| 1.3    | Pin Definition and Functions.               |

| 1.4    | Block Diagram                               |

| 2      | Functional Description                      |

| 2.1    | Architecture                                |

| 2.1.1  | CPU Hardware                                |

| 2.2    | Memory Organization                         |

| 2.2.1  | Internal Program ROM 13                     |

| 2.2.2  | Internal Data RAM                           |

| 2.2.3  | Special Function Registers                  |

| 2.3    | Interrupt System                            |

| 2.4    | Processor Reset and Clock Circuit           |

| 2.5    | Ports and I/O Pins                          |

| 2.5.1  | Port 0                                      |

| 2.5.2  | Port 1                                      |

| 2.5.3  | Port 2                                      |

| 2.5.4  | Read-Modify-Write Feature                   |

| 2.6    | Timer                                       |

| 2.7    | Serial Interface                            |

| 2.8    | Analog to Digital Converter                 |

| 2.9    | LCD-Matrix Controller                       |

| 2.9.1  | LCD-Special Function Registers              |

| 2.10   | Instuction Set                              |

| 2.10.1 | Notes on Data Addressing Modes 39           |

| 2.10.2 | Notes on Program Addressing Modes           |

| 2.10.3 | Instruction Set Description                 |

| 2.10.4 | Instruction Opcodes in Hexadecimal Order 44 |

| 3      | Electrical Characteristics                  |

| 3.1    | Absolute Maximum Ratings                    |

| 3.2    | DC-Characteristics                          |

| 3.3    | AC-Characteristics                          |

| 4      | Application Example                         |

|        |                                             |

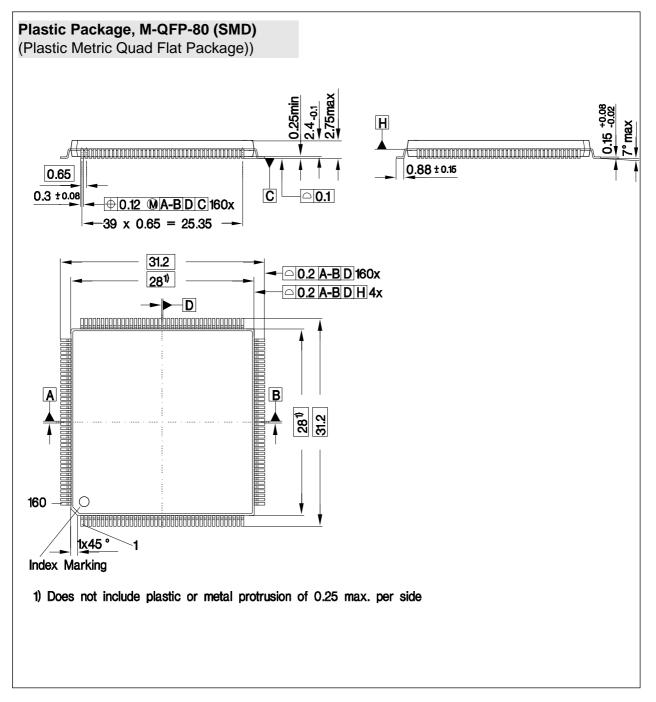

| 5      | Package Outlines                            |

# VAKATSEITE

•

## 8-Bit Microcontroller with LCD-Dot Matrix Driver

### Preliminary Data

### 1 Features

### Architecture

- CMOS-technology

- Processor core op-code compatible with SAB 8051 series

- On-chip oscillator and clock circuits (quartz oscillator or RC-oscillator, mask option)

- Binary or decimal arithmetic

- Signed-overflow detection and parity computation

- Integrated Boolean processor for control applications

- 83-ns clock cycle / 12-MHz internal operation frequency (4-MHz external frequency reference)

- Hardware multiply and divide

- Full depth stack for subroutine return linkage and data storage

- Three interrupt sources

| Туре       | Ordering Code     | Package         |

|------------|-------------------|-----------------|

| SDA 20C440 | Customer specific | P-MQFP-80 (SMD) |

#### **LCD-Dot Matrix Driver Unit**

- 5 ¥ 7 dot character matrix

- 128 user defined characters (mask-programmable)

- SW-definable characters and symbols

- 2 ¥ 40 bytes of display RAM

- Selectable 8 or 16 line multiplexing drive (45 or 40 column drivers / 8 or 16 row drivers)

- Internal LCD-driving voltage divider with input for external reference voltage

#### **On-Chip RAM**

- Direct byte and bit addressability

- Four register banks

- •

- 128 bytes of data memory (including 128 user-defined software flags)

#### **On-Chip ROM**

• Up to 4096 bytes of mask-programmable program memory

## SDA 20C440

**CMOSIC**

### I/O-Lines

- One bidirectional 8-bit port (P0) comprising one line for external interrupt

- One 4-bit input port (P1) comprising four lines for digital or analog voltage input

- One bidirectional 2-bit port (P2) comprising two lines for the serial interface

#### Serial Interface

- Interface for asynchronous serial data communication

- Baudrate generator

#### Timer

• One 16-bit general purpose timer with 4-bit prescaler

#### 1.1 Functional Overview

Designed for the use in car radio applications, the SDA 20C440 provides high processor performance as well as peripheral functions, specially a dedicated LCD-Dot Matrix Driver unit. The processor is based on the Siemens ECO-51 core, which is op-code compatible to the widely used 8051 controller series. This makes the controller suitable for even more applications using liquid crystal matrix displays.

The members of the SDA 20C440 family of microcontrollers are:

- SDA 20C440 with factory-programmable 4-Kbyte on-chip ROM

- SDA 30C440E emulation version of the SDA 20C440

- SDA 20C840 with factory-programmable 8-Kbyte on-chip ROM

- SDA 30C840E emulation version of the SDA 20C840

Whereas the SDA 20C440 executes instructions from its internal ROM, the SDA 30C440E fetches them from the external emulation memory via an additional bus interface.

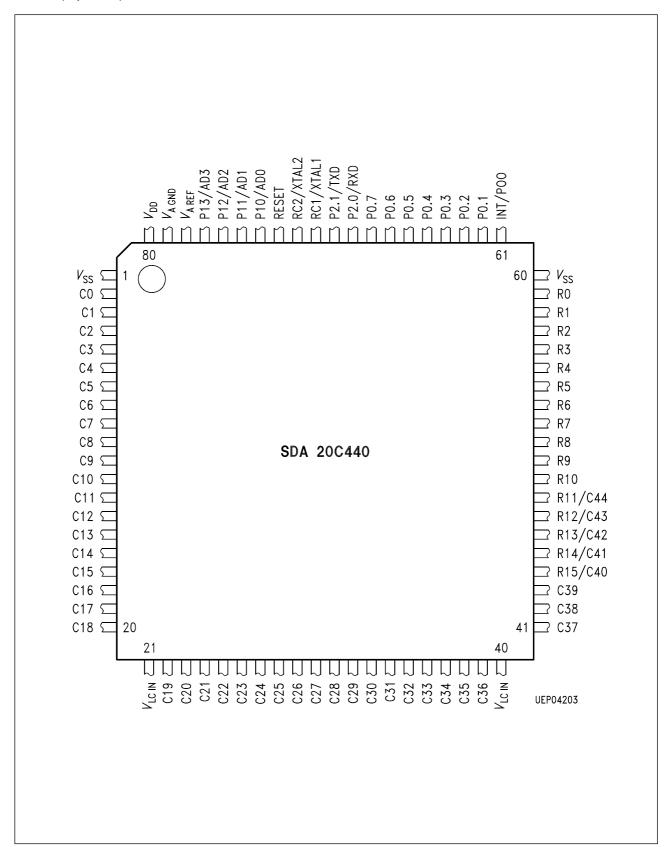

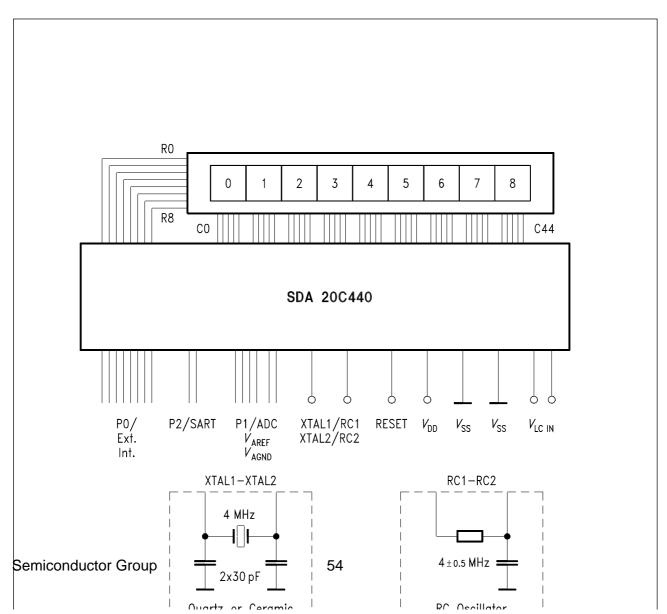

#### 1.2 Pin Configuration

(top view)

SDA 20C440

#### 1.2 Pin Configuration

(top view)

| 1.3 FILL Delimitions and Fullcuous | 1.3 | Pin Definitions and Functions |

|------------------------------------|-----|-------------------------------|

|------------------------------------|-----|-------------------------------|

| Pin<br>No.                                   | Symbol                                                           | Input (I)<br>Output (O)<br>Supply (S)         | Function                                                                                                                                                  |

|----------------------------------------------|------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61<br>62<br>63<br>64<br>65<br>66<br>67<br>68 | P0.0/INT<br>P0.1<br>P0.2<br>P0.3<br>P0.3<br>P0.5<br>P0.6<br>P0.7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Port 0 is an 8-bit bidirectional I/O-port,<br>comprising one line for external interrupt.                                                                 |

| 74<br>75<br>76<br>77                         | P1.0/AD0<br>P1.1/AD1<br>P1.2/AD2<br>P1.3/AD3                     | <br> <br> <br>                                | Port 1 is a 4-bit input port, comprising four analog inputs for A/D-conversion.                                                                           |

| 69<br>70                                     | P2.0/RXD<br>P2.1/TXD                                             | I/O<br>I/O                                    | Port 2 is a 2-bit bidirectional I/O-port, comprising the receive and transmit line for the serial interface.                                              |

| 71                                           | XTAL1                                                            | 1                                             | Input of the inverting oscillator amplifier. To<br>drive the device from an external clock source,<br>XTAL1 should be driven while XTAL2 is left<br>open. |

| 72                                           | XTAL2                                                            | 0                                             | Output of the inverting oscillator amplifier. Only supported, if an external quartz oscillator is used.                                                   |

| 71                                           | RC1                                                              | 1                                             | Input to a Schmitt trigger inverter for RC-type oscillator (optional)                                                                                     |

| 72                                           | RC2                                                              | 0                                             | Output of the Schmitt trigger inverter (optional)                                                                                                         |

| 73                                           | RESET                                                            | I                                             | A low level on this pin for at least 4 $\mu$ s while the oscillator is running resets the processor.                                                      |

| 80<br>1, 60                                  | V <sub>DD</sub><br>V <sub>SS</sub>                               | S<br>S                                        | Power supply voltage<br>Ground (0 V)                                                                                                                      |

| 79<br>78                                     | VAGND<br>VAREF                                                   | S<br>S                                        | ADC-low reference voltage<br>ADC-high reference voltage                                                                                                   |

| 21,40                                        | V <sub>LCIN</sub>                                                | S                                             | LCD-reference voltage inputs                                                                                                                              |

| Pin<br>No.                                                                                                                                 | Symbol                                                                                                                                                            | Input (I)<br>Output (O)<br>Supply (S)                              | Function                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 59<br>58<br>57<br>56<br>55<br>54<br>53<br>52<br>51<br>50<br>49                                                                             | R0<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7<br>R8<br>R9<br>R10                                                                                                   | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0           | LCD-row driver output 0-10                                                                                     |

| 44<br>45<br>46<br>47<br>48                                                                                                                 | R15/C40<br>R14/C41<br>R13/C42<br>R12/C43<br>R11/C44                                                                                                               | 0<br>0<br>0<br>0<br>0                                              | LCD-row driver output 11-15<br>or LCD-column driver output 40-44<br>(depending on the selected multiplex mode) |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>22<br>23<br>24<br>25<br>26<br>27 | C0<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18<br>C19<br>C20<br>C21<br>C22<br>C23<br>C24 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | LCD-column driver output 0-39                                                                                  |

## **1.3 Pin Definitions and Functions** (cont'd)

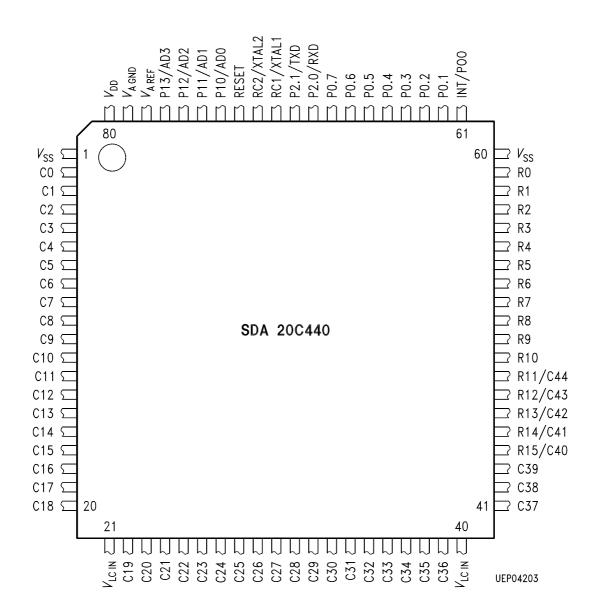

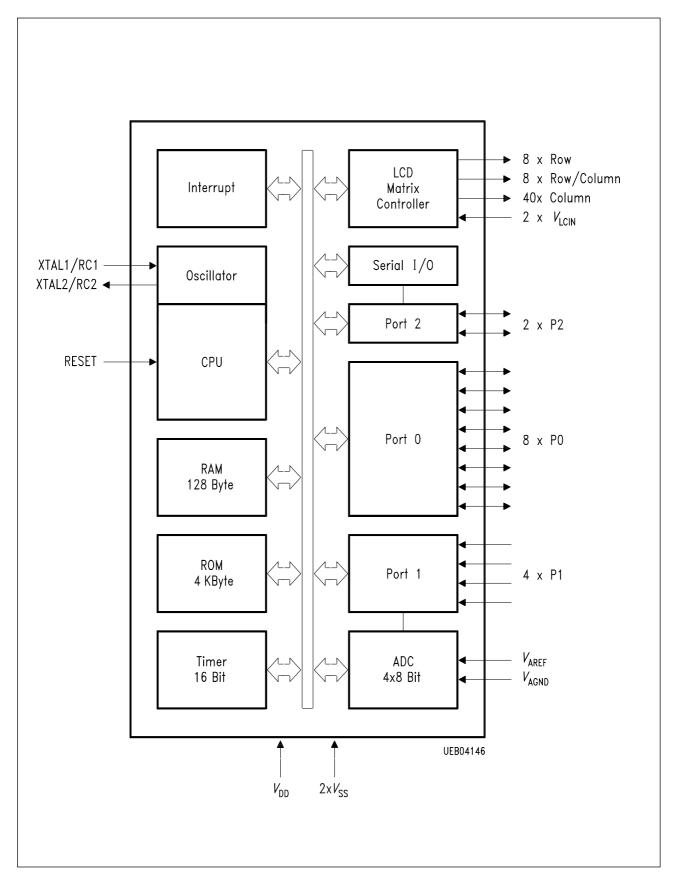

#### 1.4 Block Diagram

| Pin<br>No. | Symbol | Input (I)<br>Output (O)<br>Supply (S) | Function                               |

|------------|--------|---------------------------------------|----------------------------------------|

|            |        |                                       | LCD-column driver output 0-39 (cont'd) |

| 28         | C25    | 0                                     |                                        |

| 29         | C26    | 0                                     |                                        |

| 30         | C27    | 0                                     |                                        |

| 31         | C28    | 0                                     |                                        |

| 32         | C29    | 0                                     |                                        |

| 33         | C30    | 0                                     |                                        |

| 34         | C31    | 0                                     |                                        |

| 35         | C32    | 0                                     |                                        |

| 36         | C33    | 0                                     |                                        |

| 37         | C34    | 0                                     |                                        |

| 38         | C35    | 0                                     |                                        |

| 39         | C36    | 0                                     |                                        |

| 41         | C37    | 0                                     |                                        |

| 42         | C38    | 0                                     |                                        |

| 43         | C39    | 0                                     |                                        |

## **1.3 Pin Definitions and Functions** (cont'd)

#### 2 Functional Description

#### 2.1 Architecture

The controller uses the Siemens ECO-51 processor core. This core is opcode compatible to the 8051 microcontroller series. Because of a different internal timing, the instruction times differ from the original 8051 behavior.

For detailed information see chapter 'Instruction Set'.

#### 2.1.1 CPU Hardware

#### **Program Memory**

The controller addresses 4 Kbyte of internal mask programmable ROM.

#### Program Status Word Register (PSW)

The PSW-flags record processor status information and controls the operation of the processor. The carry (CY), auxiliary carry (AC), two user flags (F0 and F1), register bank select (RS0 and RS1), overflow (OV) and parity (P) flags reside in the Program Status Word Register. These flags are bitmemory-mapped within the byte-memory-mapped PSW. The CY-, AC-, and OV-flags generally reflect the status of the latest arithmetic operations. The CY-flag is also the Boolean accumulator for bit operations. The P-flag always reflects the parity of the A-register. F0 and F1 are general purpose flags which are pushed onto the stack as part of a PSW-save. The two register bank select bits (RS1 and RS0) determine which one of the four register banks is selected as follows:

| RS1 | RS0 | Register<br>Bank | Register<br>Location              |

|-----|-----|------------------|-----------------------------------|

| 0   | 0   | 0                | 00 <sub>H</sub> – 07 <sub>H</sub> |

| 0   | 1   | 1                | 08 <sub>H</sub> – 0F <sub>H</sub> |

| 1   | 0   | 2                | 10 <sub>H</sub> – 17 <sub>H</sub> |

| 1   | 1   | 3                | 18 <sub>H</sub> – 1F <sub>H</sub> |

| MSB                      | MSB SFR-Address: D0 <sub>H</sub> |  |  |  |  |   | LSB |

|--------------------------|----------------------------------|--|--|--|--|---|-----|

| PSW: Program Status Word |                                  |  |  |  |  |   |     |

| CY AC F0 RS1 RS0 OV F1   |                                  |  |  |  |  | Р |     |

#### Stack Pointer (SP)

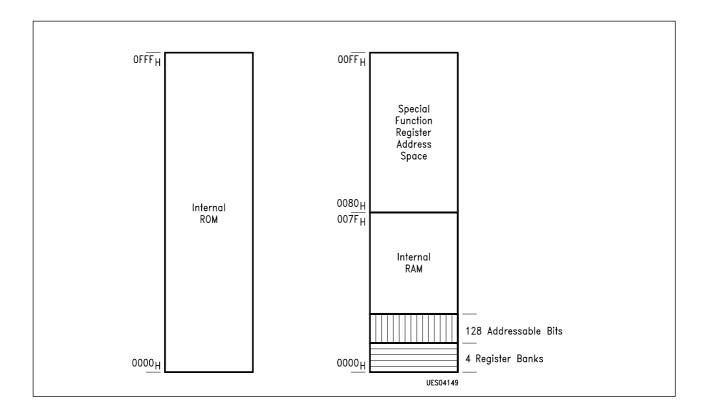

The 8-bit stack pointer contains the address at which the last byte was pushed onto the stack. This is also the address of the next byte that will be popped. The SP is incremented during a push. SP can be read from or written to under software control. The stack may be located anywhere within the internal data RAM-address space and may be as large as 128 bytes. **Figure 1**

#### Memory Map

#### Data Pointer Register (DPTR)

The 16-bit data pointer register DPTR is the concatenation of registers DPH (high-order byte) and DPL (low-order byte). The DPTR is used in register-indirect addressing to move program memory constants. DPTR may be manipulated as one 16-bit register or as two independent 8-bit registers DPL and DPH.

#### Port 0, Port 1, Port 2

The three ports P0 ... 2 provide 10 I/O-lines to interface to the external world. Port 0 and Port 1 are both byte and bit addressable. Port 2 is only byte addressable and contains two bits, which can be selected as a serial interface and for normaly I/O. Port 0 is used for binary I/O. Port 1 contains up to four ADC-input channels.

#### 2.2 Memory Organization

#### 2.2.1 Internal Program ROM

An internal program ROM of 4 Kbyte is provided. The ROM is mask-programmable. After reset, the operation starts at address 0000<sub>H</sub>.

#### 2.2.2 Internal Data RAM

An internal data RAM of 128 bytes of memory is provided. This internal RAM comprises 128 software flags, which are usable by the implemented bit operation instructions.

### 2.2.3 Special Function Registers

Accesses to peripheral and CPU functions are done by writing to or reading from special function registers.

| Register Function                                                                                                | Symbolic Name                     | Address<br>(hexadecimal)                                                                                       | Value after Reset                                                                           |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Timer High Byte                                                                                                  | TH                                | F9 <sub>H</sub>                                                                                                | 00H                                                                                         |

| Timer Low Byte                                                                                                   | TL                                | F7 <sub>H</sub>                                                                                                | 00H                                                                                         |

| Timer Reload Value High Byte                                                                                     | TRH                               | F6 <sub>H</sub>                                                                                                | 00H                                                                                         |

| Timer Reload Value Low Byte                                                                                      | TRL                               | F5 <sub>H</sub>                                                                                                | 00H                                                                                         |

| Timer Control Register 0                                                                                         | TCON                              | DC <sub>H</sub>                                                                                                | 00H                                                                                         |

| ADC-Control Register *                                                                                           | ADCON                             | 90 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| ADC-Address Register                                                                                             | ADADR                             | 91 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| ADC-Data Register                                                                                                | ADDAT                             | 92 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Data Pointer High<br>Data Pointer Low<br>Stack Pointer<br>Accumulator *<br>B-Register *<br>Program Status Word * | DPH<br>DPL<br>SP<br>A<br>B<br>PSW | 83 <sub>H</sub><br>82 <sub>H</sub><br>81 <sub>H</sub><br>E0 <sub>H</sub><br>F0 <sub>H</sub><br>D0 <sub>H</sub> | 00 <sub>H</sub><br>00 <sub>H</sub><br>07 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub> |

| Oscillator Control Register                                                                                      | OSCON                             | 9A <sub>H</sub>                                                                                                | 01 <sub>H</sub>                                                                             |

| Interrupt Enable Register 0                                                                                      | IENA0                             | C8 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Interrupt Enable Register 2                                                                                      | IENA2                             | C9 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Interrupt Request Register *                                                                                     | IREQ0                             | A8 <sub>H</sub>                                                                                                | 02 <sub>H</sub>                                                                             |

| Serial Port Control Register 0                                                                                   | SACON0                            | C1 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Serial Port Control Register 1 *                                                                                 | SACON1                            | C0 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Serial Port Transmit/Receive Buffer                                                                              | SABUF                             | C3 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Serial Port Prescaler                                                                                            | SASCAL                            | C4 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Serial Port Baud Rate Counter                                                                                    | SABAUD                            | C2 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Port 0 Register *                                                                                                | P0                                | <sup>80</sup> H                                                                                                | 00 <sub>H</sub>                                                                             |

| Port 0 Direction Register                                                                                        | P0PDR                             | <sup>84</sup> H                                                                                                | 00 <sub>H</sub>                                                                             |

| Port 1 Register *                                                                                                | P1                                | 88 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Port 2 Register                                                                                                  | P2                                | 8F <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Port 2 Direction Register                                                                                        | P2PDR                             | 94 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| Port 2 Function Register                                                                                         | P2PFR                             | 95 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| LCD-Address Register                                                                                             | LCDADR                            | BC <sub>H</sub>                                                                                                | <sup>00</sup> H                                                                             |

| LCD-Code Register                                                                                                | LCDCOD                            | B9 <sub>H</sub>                                                                                                | <sup>00</sup> H                                                                             |

| LCD-Bit Data Register                                                                                            | LCDBIT                            | BB <sub>H</sub>                                                                                                | <sup>00</sup> H                                                                             |

| LCD-Word Data Register                                                                                           | LCDWRD                            | BA <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

| LCD-Mode Register *                                                                                              | LCDMOD                            | B8 <sub>H</sub>                                                                                                | 00 <sub>H</sub>                                                                             |

\*) These registers are bit-addressable

#### 2.3 Interrupt System

Three interrupt sources are provided, which are:

- Timer Interrupt

- Serial Interface Interrupt

- External Interrupt

Each of these interrupt vectors to its special interrupt routine location. All interrupts are serviced at the same priority level. Before enabling an interrupt source, the corresponding request bit in IREQ0 has to be set to 0.

Three special function registers are used to control the interrupt functions:

- IENA0: The Interrupt Enable Register contains one enable bit for each interrupt source.

- IENA2: The Global Interrupt Enable Register contains one global enable bit to enable or disable all individually enabled interrupts.

- IREQ0: The Interrupt Request Register contains one request bit for each interrupt; these bits are set and cleared by hardware but may be set or cleared by software as well.

Each interrupt vector to its own interrupt location:

| INT0 | Serial Port Interrupt | 0006 <sub>H</sub> |

|------|-----------------------|-------------------|

| INT1 | External Interrupt    | 0009 <sub>H</sub> |

| INT2 | Timer Interrupt       | 000CH             |

Response time: between 0.91  $\mu$ s and 2.3  $\mu$ s at an internal operating frequency of 12 MHz.

#### Interrupt Registers:

| MSB SFR-Address: C9 <sub>H</sub>        |     |  |  |  |   |  |  |  |

|-----------------------------------------|-----|--|--|--|---|--|--|--|

| IENA2: Global Interrupt Enable Register |     |  |  |  |   |  |  |  |

|                                         | IEA |  |  |  |   |  |  |  |

|                                         | •   |  |  |  | • |  |  |  |

Default after reset: XXXX XXX0 IEA: = 1 enable all Interrupts IENA2.1 – IENA2.7: reserved, to be set to 0

| MSB |                                    |  | SFR-Add | ress: <b>C8<sub>H</sub></b> |  |  | LSB |  |

|-----|------------------------------------|--|---------|-----------------------------|--|--|-----|--|

|     | IENA0: Interrupt Enable Register 0 |  |         |                             |  |  |     |  |

|     | IE2 IE1 IE0                        |  |         |                             |  |  |     |  |

Default after reset: XXXX X000

| IE2: = 1 | enable Timer Interrupt    |

|----------|---------------------------|

| IE1: = 1 | enable External Interrupt |

| · — -    |                           |

IE0: = 1 enable Serial Port Interrupt

IENA0.3 - IENA0.7: reserved, to be set to 0

| MSB |                                   |  | SFR-Add | ress: <b>A8<sub>H</sub></b> |      |      | LSB  |

|-----|-----------------------------------|--|---------|-----------------------------|------|------|------|

|     | IREQ0: Interrupt Request Register |  |         |                             |      |      |      |

|     |                                   |  |         |                             | INT2 | INT1 | INT0 |

Default after reset: XXXX XXXX

- INT1: = 1 External Interrupt is requested

- INT0: = 1 Serial Port Interrupt is requested

IREQ0.3 - IREQ0.7: reserved, to be set to 0, if writing to IREQ0

#### 2.4 Processor Reset and Clock Circuit

#### **Processor Reset and Initialization**

A low level at pin RESET for at least  $4 \mu s$  resets the processor. All port lines are set to input mode. After reset, most special function registers are set to 00H, except for:

- Stack Pointer Register (set to 07<sub>H</sub>)

- Oscillator Control Register (set to 01<sub>H</sub>)

(for detail see chapter 'Memory Organization')

**Important Note:** When entering reset, port lines P0.0 and P0.1 are to be held at high level (or left open). Otherwise the processor test mode is entered.

#### **Processor Clock Circuit**

The internal processor clock is derived from an external reference, which may be a quartz/ceramic resonator or an RC-oscillator (selected by mask option). The reference frequency is 4 MHz, the internal operating frequency is 12 MHz. See chapter 'AC-Characteristics' for reference frequency limits.

The operating frequency is generated by a PLL circuit. After reset, the PLL is disabled and the processor runs at the external reference frequency (4 MHz). By setting the oscillator control register (OSCON, see below), the operating frequency is set to 12 MHz. Once being activated, the PLL cannot be switched off any more. The following sequence is to be used for initializing the clock system after reset:

#### MOV OSCON,#41<sub>H</sub> MOV OSCON,#10<sub>H</sub>

This should be done before using one of the peripheral modules (timer, LCD-unit etc.)

| MSB | MSB SFR-Address: <b>9A<sub>H</sub></b> |  |  |  |  |  |  |  |

|-----|----------------------------------------|--|--|--|--|--|--|--|

|     | OSCON: Oscillator Control Register     |  |  |  |  |  |  |  |

|     | OSC OSF                                |  |  |  |  |  |  |  |

PLLD:

PLL disable

= 1: PLL is deactivated

= 0: PLL is activated

Note: After activating the PLL once after reset, a deactivation is not possible any more.

OSC, OSF: Oscillator frequency select for 12-MHz system clock (see initialization sequence)

Default after reset: 01<sub>H</sub>

#### 2.5 Ports and I/O Pins

#### 2.5.1 Port 0

Port 0 is an eight-bit bidirectional port for digital I/O. One line of Port 0 (P0.0) is alternatively used for external interrupts. The port register (P0) is used for reading data from and writing data to the port pins. Two hardware modes are provided (I/O-mode and output mode), where I/O-mode is selected by default after reset. During reset, port lines P0.0 and P0.1 have to be held at a logical high level or left open to prevent the processor from entering the processor test mode.

In I/O-mode (which is the default after reset), an instruction that uses a port's bit/byte as a source operand reads a value that is the logical AND of the last value written to the bit/byte and the polarity being applied to the pin/pins by an external device (this assumes that none of the processor's electrical specs are being violated). An instruction that reads a bit/byte, operates on the content, and writes the result back to the bit/byte, reads the last value written to the bit/byte instead of the logical level at the pin/pins. Pins comprising a single port can be made a mixed collection of inputs and outputs by writing a "one" to each pin that is to be an input. Each time an instruction uses a port as the destination, the operation must write "ones" to those bits that correspond to the input pins.

All the port latches have "one"s written to them by the reset function. If a "zero" is subsequently written to a port latch, it can be reconfigured as an input by writing a "one" to it. The instructions that perform a read of, operation on, and write to a port's bit/byte are INC, DEC, IB, JBC, SET, CL, MV P.X., CJD, DJNZ, AND, OR, and XOR. The source read by these operations is the last value that was written to the port, without regard to the levels being applied at the pins. This insures that bits written to a "one" (for use as inputs) are not inadvertently cleared. Ports 0 has "quasi-bidirectional" output drivers which comprise an internal pullup resistor. When configured as inputs they pull high and will source current when externally pulled low.

In Port 0 the output drivers provide source current for a short time if, and only if, software updates the bit in the output latch from a "zero" to an "one". Sourcing current only on "zero to one" transition prevents a pin, programmed as an I/O-line, from sourcing current into the external device that is driving the input pin.

If a bit in port direction register P0PDR is cleared (i.e. set to 0), the corresponding pin high level is constantly driven by a strong output transistor. In this case the pin should not be pulled high or low externally (output mode).

#### 2.5.2 Port 1

Port 1 is a four-bit input port for digital or analog signals (may be used as input to the internal A/Dconverter). Only deselected analog lines may be used as digital inputs. The upper four bits of port 1 register are not implemented and may show random values, if read.

#### 2.5.3 Port 2

Port 2 is a two-bit bidirectional port and may be used as the serial interface receive and transmit lines.

Port function of Port 2 is the same as for Port 0. The upper six bits of Port 2 register P2 and Port 2 direction register P2PDR are not implemented and may show random values, if read. If the serial interface is used, the Port 2 function register P2PFR has to be set to  $03_{\rm H}$ . If the serial interface is not

used, the P2PFR is to be set to  $00_{H}$ , which is default value after reset. Writing of other values than  $00_{H}$  or  $03_{H}$  to P2PFR is not allowed.

#### 2.5.4 Read-Modify-Write Feature

"Read-modify-write" commands are instructions that read a value, possibly change it, and then rewrite it to the latch. When the destination operand is a port or a port bit, these instructions read the latch rather than the pin. The read-modify-write instructions are listed below:

INC, DEC, JB, JBC, SET, CL, MV P.X., DJNZ, AND, OR, and XOR.

The read-modify-write instructions are directed to the latch rather than the pin in order to avoid a possible misinterpretation of the voltage level at the pin. For example, a port bit might be used to drive the base of a transistor. When a "one" is written to the bit, the transistor is turned on.

If the CPU then reads the same port bit at the pin rather than the latch, it will read the base voltage of the transistor and interpret it as a 0. Reading the latch rather than the pin will return the correct value of "one".

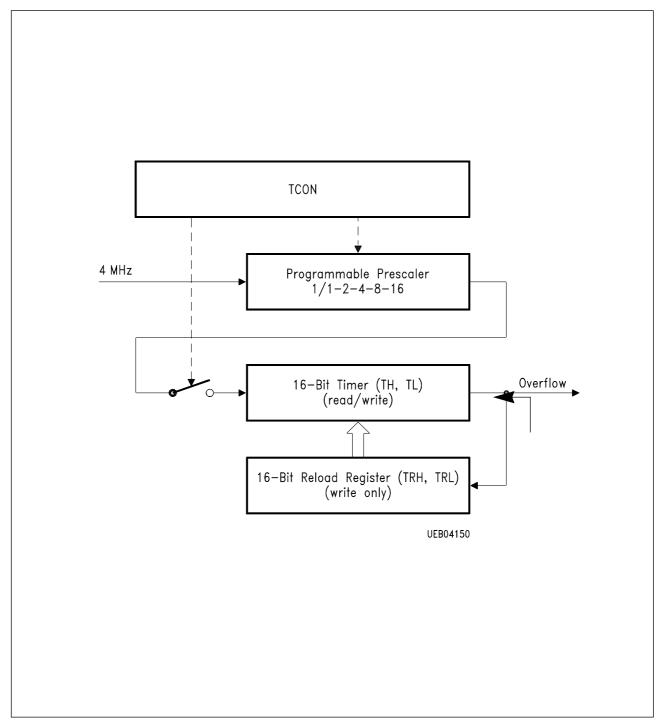

#### 2.6 Timer

A 16-bit timer with auto-reload is provided. The timer clock is derived from the external oscillator clock rate (4 MHz) by a programmable prescaler in five steps (1 - 1/2 - 1/4 - 1/8 - 1/16).

An interrupt request is generated by timer overflow which may be masked by use of the interrupt enable registers IENA0 and IENA2 (see chapter 'Interrupt System'). The timer is started/stopped by setting/clearing bit RUN in register TCON. The prescale factor is selected by setting a three bit value (bits PS0, PS1 and PS2) in register TCON. If a 16-bit timer value is to be written to the timer register or to the timer reload register, the high byte (TH, TRH) is to be written first. After writing the low byte (TL, TRL), the complete 16-bit word will be transferred from a 16-bit shadow register into the internal pair of registers (timer registers TH/TL, reload registers TRH/TRL). If a 16-bit value is to be read from the timer registers or timer reload register. After this, the high byte can be read. Please note, that for correct operation always two read or write access in the right order are necessary. After reset, the values of the timer registers, the reload registers and the two pairs of shadow registers are undefined and the timer is stopped.

| MSB             | MSB SFR-Address: DC <sub>H</sub> |  |  |  |  |  |  |

|-----------------|----------------------------------|--|--|--|--|--|--|

|                 | TCON: Timer Control Register     |  |  |  |  |  |  |

| RUN PS2 PS1 PS0 |                                  |  |  |  |  |  |  |

```

PS0..2

```

- prescaler = 000: factor 1 = 001: factor 1/2 = 010: factor 1/4

- = 011: factor 1/8

- = 100: factor 1/16

RUN start and stop bit

= 1: start

= 0: stop

TCON.4 - TCON.7: reserved, to be set to 0

Default after reset: XXXX 0000H

#### Figure 2 Timer Block Diagram

#### 2.7 Serial Interface

The asynchronous serial interface (SART, Serial Asynchronous Receiver & Transmitter) is used for communication with other controllers or electrical systems. This modul works in full-duplex mode, so it can send and receive data at the same time. Moreover, it comprises a dedicated programmable baud-rate generator.

Port 2.0 and Port 2.1 are used for input and output of the serial data. To allocate these pins to the SART-module, the according bits of the port function register in the special function register must be set.

Three types of data transmission errors are detected: Parity-, Framing- and Overwrite-Error. Three different interrupt-outputs exist for the following events: Transmit-Ready, Receive-Ready and Error-Detected.

The transmit and receive registers are double buffered, so that during the reception of the first byte the second byte can be received, as well as the transmission can run continuously.

#### Data Sequence

The data words consists of:

1 start bit (= '0')

in mode I: 8 data bits in mode II: 8 data bits, 1 parity bit in mode III: 8 data bits, 1 address bit

1 stop bit (= '1')

During idle state the output is held at '1'...

The transfer of the data bits starts with the least significant bit (LSB).

|      | I |   | II: ´ | no bit<br>I parity I<br>I addres |   |   |   |   |   |      |

|------|---|---|-------|----------------------------------|---|---|---|---|---|------|

| Idle | 0 | 1 | 2     | 3                                | 4 | 5 | 6 | 7 | 8 | Idle |

Start

Stop

#### **Operating Modes**

The three possible modes are switched with bits SM0 and SM1 of the register SACON0 as shown in table below.

| SM0 | SM1 | Mode | Description                  |

|-----|-----|------|------------------------------|

| 0   | 0   | I    | 8-bit data                   |

| 0   | 1   | II   | 8-bit data,<br>1 parity bit  |

| 1   | 0   | 111  | 8-bit data,<br>1 address bit |

| 1   | 1   | IV   | reserved                     |

#### **Multiprocessor-Communication**

Mode III is used for communication in multiprocessor systems. In this mode, 9 data bits are received and transmitted. The contents of the nineth received data bit is written into bit RB8 of register SACON1, and the nineth transmitted data bit is taken from bit TB8 of the register SACON1.

When the mask-address-interrupt bit MAI of register SACON1 is set, the SART-module can be programmed in a way that after a stopbit was received, a transmit-interrupt is released only if bit RB8 is set. If bit MAI is not set, a transmit-interrupt is never caused when nine databits and the stopbit are received. Setting of bit MAI is only to be used in mode III.

#### Loop Back Mode

The loop back mode is only used for test purpose. It is activated when the bit LBE of the SACON0 register is set. In this case, the transmitted informations do not appear on the output pin but they are switched to the receive part of the SART-module internally. Therefore the transmitted bits are received simultaneously. The disconnecting of the pins is independend of the setting of the port function register.

All the control bits are in function, the test can use all kinds of data transmission, all unmasked interrupt sources also release an interrupt and the receiver must be activated.

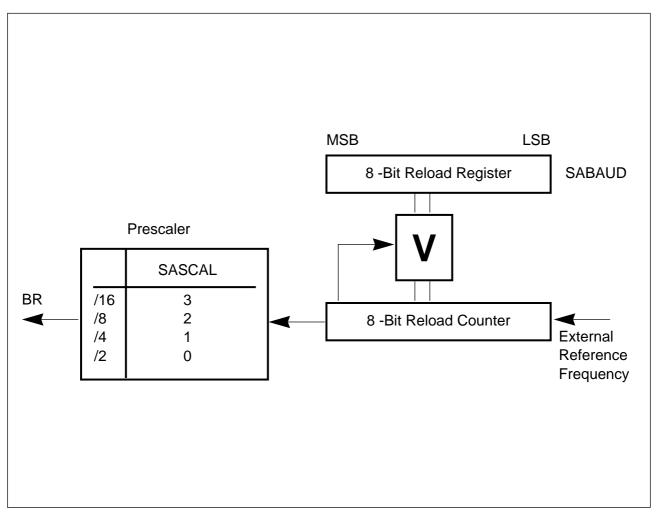

#### **Baudrate Generator**

The speed of the communication is set by programming the 8-bit-reload-counter and the divider of the integrated baudrate generator. The baudrate is derived from the clock of a central prescaler and based on the external reference frequency (quartz, ceramic resonator or RC-oscillator).

Any value between 0 and  $FF_H$  may be written into the baudrate reload register SABAUD. The baudrate is calculated as follows:

$$BR: = \frac{f_{REF}}{2^{(SASCAL+1)} \times (SABAUD + 1)}$$

| Baudrate<br>[kBd] | SASCAL | SABAUD | Fault [%] |

|-------------------|--------|--------|-----------|

| 2.4               | 3      | 103    | + 0.16    |

| 4.8               | 3      | 51     | + 0.16    |

| 9.6               | 3      | 25     | + 0.16    |

| 10.4              | 3      | 23     | + 0.16    |

| 19.2              | 3      | 12     | + 0.16    |

| 38.4              | 0      | 51     | + 0.16    |

| 57.6              | 0      | 34     | - 0.79    |

| 76.8              | 0      | 25     | + 0.16    |

| 115.2             | 0      | 16     | + 2.12    |

| 180               | 0      | 10     | + 1.01    |

Standard baudrates may be set according to the following table:

#### Security of Data

Following errors are detected by the SART-module:

Framing Error

A logical '0' is received instead of the expected stopbit (logic '1'). A framing-error sets error flag FE.

- Parity Error

The value of the received parity bit is not equal to the parity of the according data byte. Even parity is assumed. A parity error sets error flag PE.

- Overwrite Error

The databyte in the register RXBUF is overwritten by a new databyte before the first databyte was read by the CPU. An overwrite error sets error flag OE.

The occurrence of one of these errors is signaled to the CPU using the control interrupt CNTRINT. The evaluation of the error flags identifies the appropriate cause. The release of the control interrupt CNTRINT can be suppressed for each fault individually by setting the appropriate mask bit to 0 (MFE, MPE and MOE).

#### Figure 3 Block Diagram of the Baudrate Generator

#### **Data Reception**

In idle state the dataline on pin RXD is held at high level. The beginning of a data byte starts with the first '1 – 0' transition (start bit), which also synchronizes the baudrate generator. After this, eight or nine data bits are read according to the selected mode with the clock of the baudrate generator. In mode II the parity of the data byte is compared with the parity bit automatically. The stop bit is always tested for the value '1'. If an error is detected, the appropriate error flag is set and causes an interrupt, if enabled.

In case of no error, the received data byte is written into the register RXBUF and at the same time the reception is signaled to the CPU using interrupt RXINT. If the data byte in the receive register RXBUF is to be overwritten by a new data byte before the CPU has read this register, the overwrite error flag is set and the control interrupt is activated.

#### **Data Transmission**

The transmission of a data word is started automatically by writing to the transmit register. The data word of register TXBUF is loaded into the shift register TSREG. With the clock of the baudrate generator the data value is shifted to pin TXD. The data word consists of an automatically generated start bit, eight or nine data bits and one stop bit. In mode II the parity bit is computed and is transmitted as the nineth data bit.

#### **Transmit and Receive Register**

The CPU writes the data to be sent into the transmit buffer TXBUF. It is a special function register with write-only access. While reading from this address location, the receive register RXBUF will be available.

| MSB |                                            |    | SFR-Add | ress: <b>C3<sub>H</sub></b> |    |    | LSB |

|-----|--------------------------------------------|----|---------|-----------------------------|----|----|-----|

|     | SABUF: Serial Port Transmit/Receive Buffer |    |         |                             |    |    |     |

| D7  | D6                                         | D5 | D4      | D3                          | D2 | D1 | D0  |

#### **Receive-Register**

The SART-module writes the received data into the receive register RXBUF. It is a special-functionregister with 'read-only' access. While writing with this address the transmit register will be written.

### **Control Register SACON0 and SACON1**

| MSB         |                                                        |                                                      | SFR-Addı      | ress: C1 <sub>H</sub> |                |                | LSB |  |  |  |  |

|-------------|--------------------------------------------------------|------------------------------------------------------|---------------|-----------------------|----------------|----------------|-----|--|--|--|--|

|             | SACONO: Serial Port Control Register 0                 |                                                      |               |                       |                |                |     |  |  |  |  |

| MOE         | MFE                                                    | MPE                                                  | SM1           | SM0                   | LBE            | REN            | ENA |  |  |  |  |

| MOE:        | Masking Ove<br>= 0: Overwrit                           |                                                      |               |                       |                |                |     |  |  |  |  |

| MFE:        | Masking Framing Error*<br>= 0: Framing error is masked |                                                      |               |                       |                |                |     |  |  |  |  |

| MPE:        | •                                                      | Masking Parity Error*<br>= 0: Parity error is masked |               |                       |                |                |     |  |  |  |  |

| SM0<br>SM1: | These bits se                                          | elect the ope                                        | rating mode   |                       |                |                |     |  |  |  |  |

| LBE:        | Loop-Back E<br>= 1 Loop-bac                            |                                                      |               |                       |                |                |     |  |  |  |  |

| REN:        |                                                        | Receiver Enable<br>= 1 Receiver is enabled           |               |                       |                |                |     |  |  |  |  |

| ENA:        | SART-Modul<br>= 1 The SAR                              |                                                      | enabled       |                       |                |                |     |  |  |  |  |

| *) The m    | asking of an e                                         | rror suppres                                         | sas tha start | of an interr          | unt If an erro | or is detected | 4   |  |  |  |  |

\*) The masking of an error suppresses the start of an interrupt. If an error is detected the corresponding error flag is set independent of the masking.

Default after reset: 0000 0000

| MSB  |                                                                                                                          | SFR-Address: <b>C0<sub>H</sub></b> |  |  |  |  |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|--|

|      | SACON1: Serial Port Control Register 1                                                                                   |                                    |  |  |  |  |  |  |  |

| OE   | FE                                                                                                                       | FE PE MAI TB8 RB8 TI RI            |  |  |  |  |  |  |  |

| OE:  | Overwrite Error Flag<br>This flag is set by hardware when an overwrite error occurred. It must be cleared by software.   |                                    |  |  |  |  |  |  |  |

| FE:  | Framing Error Flag<br>This flag is set by hardware when a framing error occurred. It must be cleared by software.        |                                    |  |  |  |  |  |  |  |

| PE:  | Parity Error Flag<br>This flag is set by hardware when a parity error occurred. It must be cleared by software.          |                                    |  |  |  |  |  |  |  |

| MAI: | Masking Address Interrupt<br>= 1 address interrupt is enabled (only in mode III)                                         |                                    |  |  |  |  |  |  |  |

| TB8: | Transmitter Data Bit<br>In mode III this bit is transmitted as the nineth data bit.                                      |                                    |  |  |  |  |  |  |  |

| RB8: | Receiver Data Bit<br>In mode III the ninety received bit is written to RB8.                                              |                                    |  |  |  |  |  |  |  |

| TI:  | Transmitter Interrupt<br>This flag is set by hardware when the start bit is transmitted and must be cleared by software. |                                    |  |  |  |  |  |  |  |

| RI:  | Receiver Interrupt<br>This flag is set by hardware when the stop bit is received and must be cleared by<br>software.     |                                    |  |  |  |  |  |  |  |

|      | Default after react, 0000 0000                                                                                           |                                    |  |  |  |  |  |  |  |

Default after reset: 0000 0000

#### **Baudrate Register**

With this register the baud rate is adjusted.

| MSB                                   |                             | SFR-Address: C2 <sub>H</sub> |  |  |  |  |  |

|---------------------------------------|-----------------------------|------------------------------|--|--|--|--|--|

| SABAUD: Serial Port Baud Rate Counter |                             |                              |  |  |  |  |  |

| BD7                                   | BD7 BD6 BD5 BD4 BD3 BD2 BD1 |                              |  |  |  |  |  |

The contents of this register defines the reload value of the baud rate reload counter.

#### **Baudrate Divider Register (Prescaler)**

The divider value for the prescaler is selected with this register.

| MSB SFR-Address: C4 <sub>H</sub> |                               |  |  |  |  | LSB |  |

|----------------------------------|-------------------------------|--|--|--|--|-----|--|

|                                  | SASCAL: Serial Port Prescaler |  |  |  |  |     |  |

| SCL1                             |                               |  |  |  |  |     |  |

| SCL 1/0 | Division by |

|---------|-------------|

| 00      | 2           |

| 01      | 4           |

| 10      | 8           |

| 11      | 16          |

Default after reset: XXXX XX11

#### 2.8 Analog to Digital Converter

The Analog to Digital Converter unit (ADC) provides the following features:

- 8-bit resolution

- four multiplexed analog inputs

- inputs for external reference voltages

- about 17-μs conversion time, including sample and hold at 12-MHz internal operating frequency

For detailed information see chapter 'DC-Characteristics'.

The ADC uses the principle of successive approximation by switched capacitance array. ADC-Special Function Registers:

| MSB                         | MSB SFR-Address: 91 <sub>H</sub> |  |  |  |  |  | LSB |

|-----------------------------|----------------------------------|--|--|--|--|--|-----|

| ADADR: ADC-Address Register |                                  |  |  |  |  |  |     |

|                             | ADR2 ADR1                        |  |  |  |  |  |     |

ADADR.0: to be set to 1

ADR1, ADR2: selection of the channel result to be read:

|          | 00 – channel 0 (P1.0)<br>01 – channel 1 (P1.1)<br>10 – channel 2 (P1.2)<br>11 – channel 3 (P1.3) |

|----------|--------------------------------------------------------------------------------------------------|

| ADADR.3: | reserved, to be set to 0                                                                         |

| ADADR.4: | reserved, to be set to 0                                                                         |

| ADADR.5: | reserved, to be set to 0                                                                         |

| ADADR.6: | reserved, to be set to 0                                                                         |

#### ADADR.7: reserved, to be set to 0

Default after reset: XXXX X00X

| MSB SFR-Address: 92 <sub>H</sub> |                                    |  |  |  |  | LSB |  |

|----------------------------------|------------------------------------|--|--|--|--|-----|--|

|                                  | ADDAT: ADC-Data Register           |  |  |  |  |     |  |

| DAT7                             | DAT7 DAT6 DAT5 DAT4 DAT3 DAT2 DAT1 |  |  |  |  |     |  |

#### DAT0 ... 7: conversion result of the channel addressed by ADADR

Default after reset: XXXX XXXX

| MSB | MSB SFR-Address: 90 <sub>H</sub> |  |  |  |  |  | LSB |

|-----|----------------------------------|--|--|--|--|--|-----|

|     | ADCON: ADC-Control Register      |  |  |  |  |  |     |

| BSY | BSY ADS EOC MX2 MX1              |  |  |  |  |  |     |

| MX1, MX0:            | Selection of the analog input:<br>00 – channel 0 (P1.0)<br>01 – channel 1 (P1.1)<br>10 – channel 2 (P1.2)<br>11 – channel 3 (P1.3) |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| MX2:                 | <ul> <li>1 deselects all channels</li> <li>Deselected channels may be used as digital inputs (Port 1)</li> </ul>                   |

| EOC:                 | End of Conversion;<br>set by ADC after completion of a conversion, to be cleared by software                                       |

| ADS:                 | ADC Start; setting to 1 starts a conversion, reset by hardware after the end of a conversion                                       |

| BSY:                 | Busy Bit; a '1' indicates, that a conversion is in progress or that the result has not been read yet                               |

| ADCON.3/5:           | reserved, to be set to 0                                                                                                           |

| Default after reset: | 00X0 XX00<br>This register is bit-addressable.                                                                                     |

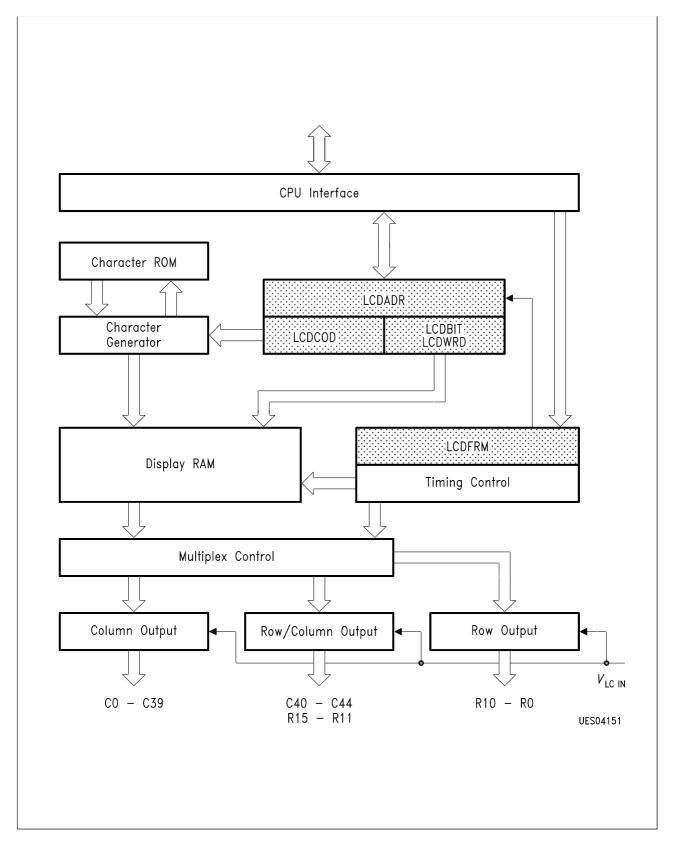

#### **LCD-Matrix Controller**

For the use of multiplexed Liquid Crystal Displays, the processor provides an LCD-control module, which allows to connect a multiplex driven LCD. The module communicates with the CPU via an interface and all settings are done by writing to special function registers. An overview of this module is given in **figure 4**.

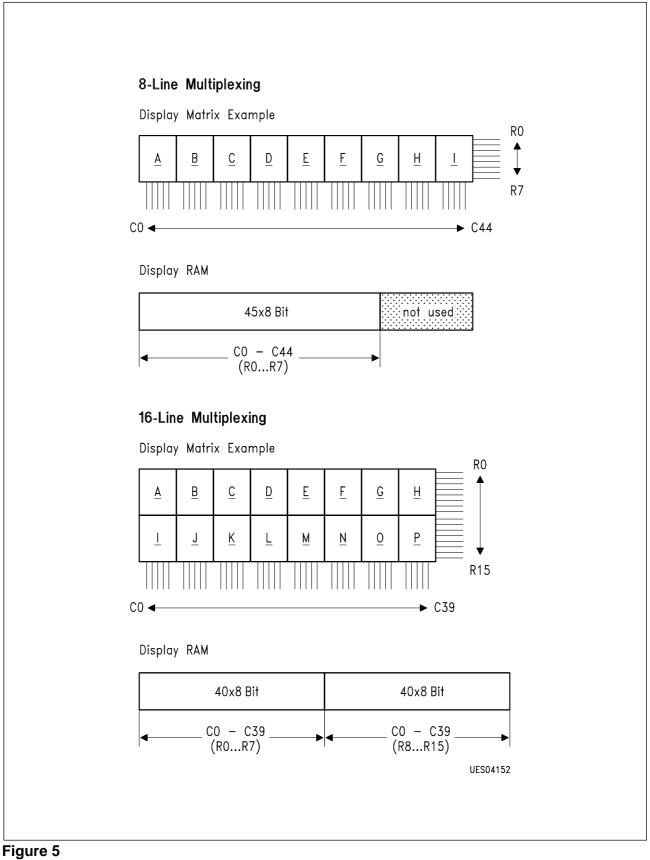

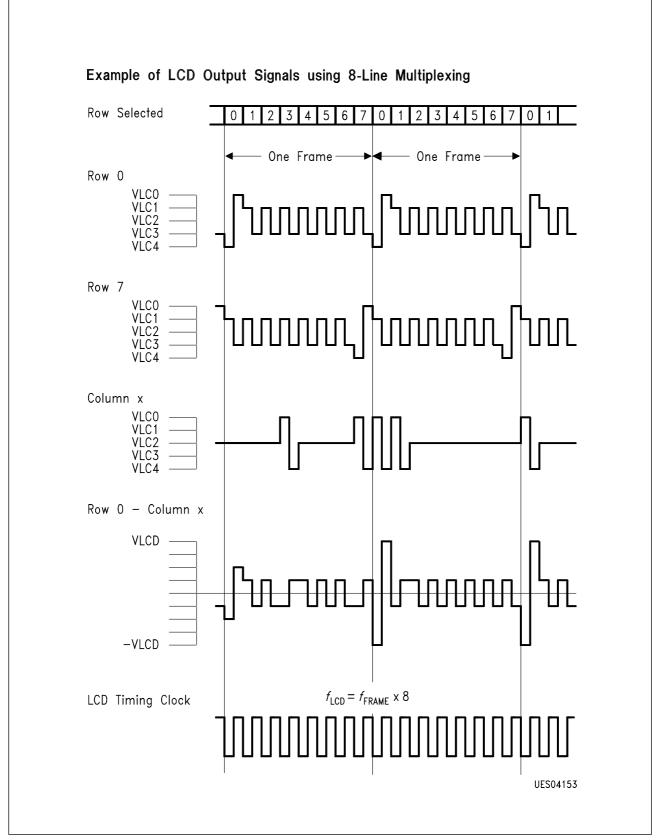

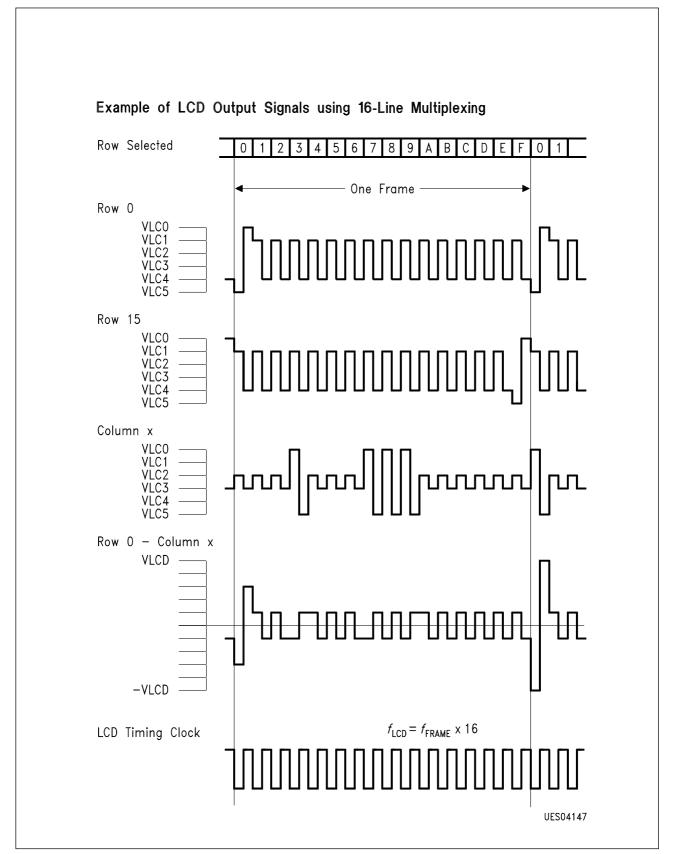

The device can be used for 8-line or 16-line multiplexing drive as shown in figures 5 to 7.

#### Figure 4 LCD-Matrix Controller Unit

Multiplexing Modes and Display RAM-Configuration

Figure 6 8-Line Multiplexing Modes and Output Signals

#### Figure 7 16-Line Multiplexing Modes and Output Signals

#### **Row and Column Driving Voltages**

The voltages for selected and not selected row and column signals for both 8-line and 16-line multiplexing are given in the following tables:

| Driving Signal (8-Line)  | Value            |

|--------------------------|------------------|

| Row Selected/-           | V <sub>LC4</sub> |

| Row Selected/+           | V <sub>LC0</sub> |

| Row Not Selected/-       | V <sub>LC1</sub> |

| Row Not Selected/+       | V <sub>LC3</sub> |

| Column Selected/-        | V <sub>LC0</sub> |

| Column Selected/+        | V <sub>LC4</sub> |

| Column Not Selected/-, + | V <sub>LC2</sub> |

$$\begin{split} V_{\rm LC0} &= V_{\rm LCIN} \\ V_{\rm LC1} &= V_{\rm LCIN} \times 0.8 \\ V_{\rm LC2} &= V_{\rm LCIN} \times 0.5 \\ V_{\rm LC3} &= V_{\rm LCIN} \times 0.2 \\ V_{\rm LC4} &= V_{\rm SS} \end{split}$$

| Driving Signal (16-Line) | Value            |  |

|--------------------------|------------------|--|

| Row Selected/-           | V <sub>LC5</sub> |  |

| Row Selected/+           | V <sub>LC0</sub> |  |

| Row Not Selected/-       | V <sub>LC1</sub> |  |

| Row Not Selected/+       | V <sub>LC4</sub> |  |

| Column Selected/-        | V <sub>LC0</sub> |  |

| Column Selected/+        | V <sub>LC5</sub> |  |

| Column Not Selected/-    | V <sub>LC3</sub> |  |

| Column Not Selected/+    | V <sub>LC2</sub> |  |

$$\begin{split} V_{\rm LC0} &= V_{\rm LCIN} \\ V_{\rm LC1} &= V_{\rm LCIN} \times 0.8 \\ V_{\rm LC2} &= V_{\rm LCIN} \times 0.6 \\ V_{\rm LC3} &= V_{\rm LCIN} \times 0.4 \\ V_{\rm LC4} &= V_{\rm LCIN} \times 0.2 \\ V_{\rm LC5} &= V_{\rm SS} \end{split}$$

#### 2.9.1 LCD-Special Function Registers

| MSB | 3 SFR-Address: <b>BC<sub>H</sub></b> |  |  |  |  |  | LSB |  |

|-----|--------------------------------------|--|--|--|--|--|-----|--|

|     | LCDADR: Display RAM-Address Register |  |  |  |  |  |     |  |

|     | ADR6 ADR5 ADR4 ADR3 ADR2 ADR1        |  |  |  |  |  |     |  |

ADR0 ... 6: Display RAM-Address

Valid Range:

8-line mode –  $00_H \dots 2C_H$ 16-line mode –  $00_H \dots 4F_H$

LCDADR.7: reserved, to be set to 0

Default after reset : X000 0000

The address will be **incremented automatically** after each data transfer to the display RAM (during character generation or single bit / word access).

| MSB                                | SFR-Address: <b>BA<sub>H</sub></b> |  |  |  |  |  | LSB |

|------------------------------------|------------------------------------|--|--|--|--|--|-----|

| LCDWRD: Display RAM-Word Register  |                                    |  |  |  |  |  |     |

| WRD6 WRD5 WRD4 WRD3 WRD2 WRD1 WRD0 |                                    |  |  |  |  |  |     |

Default after reset : X000 0000

After the word is transferred to the display RAM, the display RAM-Address Register will be incremented once.

| MSB                              | SFR-Address: <b>BB<sub>H</sub></b> |  |  |  |  |    | LSB |

|----------------------------------|------------------------------------|--|--|--|--|----|-----|

| LCDBIT: Display RAM-Bit Register |                                    |  |  |  |  |    |     |

|                                  |                                    |  |  |  |  | SB |     |

SB: Single Bit, used to set or clear a single 'cursor bit' or 'special segment bit' in the display RAM

LCDDAT.1 ... 7: reserved, to be set to 0

Default after reset: XXXX XXX0

After the bit is transferred to the display RAM, the display RAM-Address Register will be incremented once.

| MSB                                | SFR-Address: <b>B9<sub>H</sub></b> |  |  |  |  |  | LSB  |

|------------------------------------|------------------------------------|--|--|--|--|--|------|

| LCDCOD: Display RAM-Code Register  |                                    |  |  |  |  |  |      |

| COD6 COD5 COD4 COD3 COD2 COD1 COD0 |                                    |  |  |  |  |  | COD0 |

COD0 ... 6: ASCII-Character Code

LCDCOD.7: reserved, to be set to 0

Default after reset : X000 0000

Writing to this register starts a character generation procedure. This will be completed within three  $\mu$ s, therefore subsequent write accesses to LCDCOD and accesses to LCDADR, LCDBIT and LCDWRD are not allowed within this time.

After each of the five transfer cycles to the display RAM, the display RAM-Address Register will be incremented once.

| MSB                             | SFR-Address: <b>B8<sub>H</sub></b> |  |  |  |  |  | LSB  |

|---------------------------------|------------------------------------|--|--|--|--|--|------|

| LCDMOD: LCD-Frame Mode Register |                                    |  |  |  |  |  |      |

| DE MM TCLK DIV1 DIV0            |                                    |  |  |  |  |  | DIV0 |

DIV0 ... 1: Multiplex frequency division factor

| DIV1/0 | Frame Frequency (Hz) |

|--------|----------------------|

| 11     | 61                   |

| 10     | 81                   |

| 01     | 122                  |

| 00     | 244                  |

(at 4-MHz oscillator frequency)

| TCLK: | used for test purposes, to be set to 0 |                                      |  |  |  |

|-------|----------------------------------------|--------------------------------------|--|--|--|

| MM:   | Multiplex Mode                         |                                      |  |  |  |

|       | = 0:                                   | 8-line multiplexing                  |  |  |  |

|       | = 1:                                   | 16-line multiplexing                 |  |  |  |

| DE:   | Display Enable                         |                                      |  |  |  |

|       | = 0:                                   | display disabled                     |  |  |  |

|       |                                        | (output lines switched to $V_{SS}$ ) |  |  |  |

|       | = 1:                                   | display enabled                      |  |  |  |

| LCDFRM.2:            | reserved, to be set to 0 |

|----------------------|--------------------------|

| LCDFRM.3:            | reserved, to be set to 0 |

| LCDFRM.7:            | reserved, to be set to 0 |

| Default after reset: | X000 XX00                |

This register is bit-addressable.

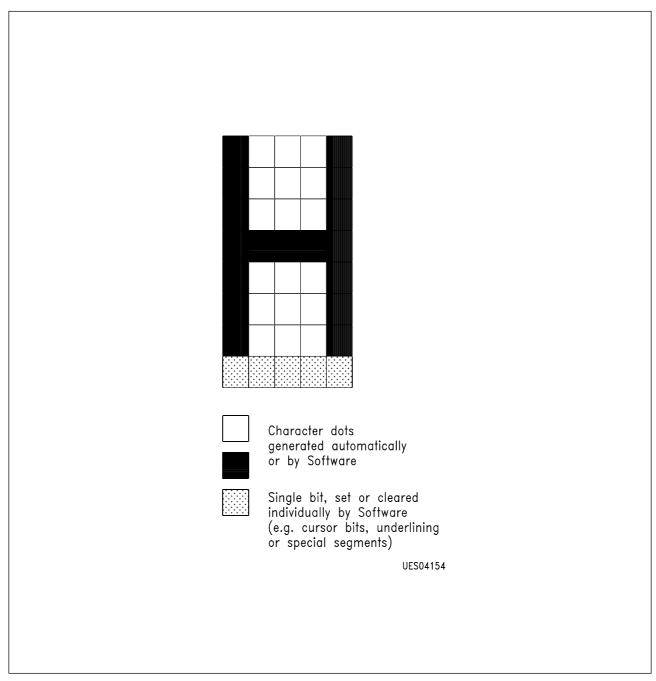

#### **Character Generation**

The character generator interpretes each ASCII-character code written to the LCD-code register (LCDCOD) and generates a  $5 \times 7$  matrix character in the display RAM. The starting address is given in the LCD-address register (LCDADR). The address is incremented five times during the generation process, which starts after the write operation to special function register LCDCOD.

The character set is user definable and stored in a mask-programmable ROM. This ROM holds 128 character definitions. The character definitions have to be supported as an ASCII-file according to the following syntax:

\$CODE = XX<sub>H</sub> 00000 00000 00000 00000 00000 00000 \$CODE = yy<sub>H</sub> 11111 11111

•••

\$END

Empty lines and lines beginning with '#', '/', '\*' are ignored and may be used to insert comments. '\$CODE =' and '\$END' are reserved keywords. The character code has to be given in hexadecimal notation.

#### **Single Bit Access**

In addition to the character matrix produced by the character generator, each display RAM-field holds five bits, which may be used for underlining characters (if 8-line displays are used) or to access special segments of a user specific display (**see figure 8**). Addressed by the contents of LCDADR, each single bit can be set or cleared by setting or clearing bit SB in register LCDBIT. The address register LCDADR is incremented once after each write operation to LCDBIT. The range of valid addresses depends on the selected display mode (**see LCD-Special Function Registers**).

#### Figure 8 Display RAM-Field

### Display RAM

The display RAM contains  $80 \times 8$  bits (80 bytes). Each byte contains 7 character dots generated by the character generator or by software and one single bit for cursor representation or special segments.

The bytes of the display RAM are addressed by the contents of register LCDADR.

The valid addresses are from 00<sub>H</sub> to  $4F_{H},$  where locations  $2D_{H}$  to  $4F_{H}$  are unused in 8-line operation mode.

#### 2.10 Instruction Set

The assembly language uses the same instruction set and the same instruction opcodes as the 8051 microcomputer family.

#### 2.10.1 Notes on Data Addressing Modes

| А       | _ | Accumulator                                                           |

|---------|---|-----------------------------------------------------------------------|

| Rn      | _ | Working register R0–R7.                                               |

| Ra      | _ | Working register R0 and R1 used for indirect addressing of the RAM.   |

| adr     | — | 128 internal RAM-locations, any I/O-port, control or status register. |

| (Ra)    | _ | Indirect internal RAM-location addressed by register R0 or R1.        |

| data    | _ | 8-bit constant included in instruction.                               |

| wadr    | _ | 16-bit constant included as bytes 2 & 3 of instruction                |

| bit adr | _ | 128 software flags and bit addressable special function register.     |

|         |   |                                                                       |

Operations working on external data memory (MOVX ...) are not used.

#### 2.10.2Notes on Program Addressing Modes

| wadr | - | Destination address for CALL & JP may be anywhere within the program memory address space.                                                     |

|------|---|------------------------------------------------------------------------------------------------------------------------------------------------|

| disp | - | PJP and all conditional jumps include an 8-bit offset byte. Range is + 127/<br>-128 bytes relative to first byte of the following instruction. |

#### LCD-RAM-Addresses

LCD-fields for 8-line multiplexing:

|   |   | 1 |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

LCD-fields for 16-line multiplexing:

| 1A | 2A | 3A | 4A | 5A | 6A | 7A | 8A |

|----|----|----|----|----|----|----|----|

| 1B | 2B | 3B | 4B | 5B | 6B | 7B | 8B |

| LCDADR          | Addressed LCD-Field<br>Using 8-Line Multiplexing | Addressed LCD-Field<br>Using 16-Line Multiplexing |

|-----------------|--------------------------------------------------|---------------------------------------------------|

| 00 <sub>H</sub> | 1                                                | 1A                                                |

| 05 <sub>H</sub> | 2                                                | 2A                                                |

| 0A <sub>H</sub> | 3                                                | 3A                                                |

| 0FH             | 4                                                | 4A                                                |

| <sup>14</sup> H | 5                                                | 5A                                                |

| 19 <sub>H</sub> | 6                                                | 6A                                                |

| 1E <sub>H</sub> | 7                                                | 7A                                                |

| 23 <sub>H</sub> | 8                                                | 8A                                                |

| 28 <sub>H</sub> | 9                                                | 1B                                                |

| 2D <sub>H</sub> | unused                                           | 2B                                                |

| 32 <sub>H</sub> | unused                                           | 3B                                                |

| 37 <sub>H</sub> | unused                                           | 4B                                                |

| 3C <sub>H</sub> | unused                                           | 5B                                                |

| 41 <sub>H</sub> | unused                                           | 6B                                                |

| 46 <sub>H</sub> | unused                                           | 7B                                                |

| 48 <sub>H</sub> | unused                                           | 8B                                                |

## 2.10.3 Instruction Set Description

## **Arithmetic Operations**

| Mnem | onic   | Description                                 | Byte | Clocks |

|------|--------|---------------------------------------------|------|--------|

| ADD  | A,Rn   | Add Register to Accumulator                 | 1    | 5      |

| ADD  | A,adr  | Add Direct Byte to Accumulator              | 2    | 8      |

| ADD  | A,(Ra) | Add Indirect RAM to Accumulator             | 1    | 6      |

| ADD  | A,data | Add Immediate Data to Accumulator           | 2    | 7      |

| ADC  | A,Rn   | Add Register to Accumulator with Carry Flag | 1    | 5      |

| ADC  | A,adr  | Add Direct Byte to A with Carry Flag        | 2    | 8      |

| ADC  | A,(Ra) | Add Indirect RAM to A with Carry Flag       | 1    | 6      |

| ADC  | A,data | Add Immediate Data to A with Carry Flag     | 2    | 7      |

| SUB  | A,Rn   | Subtract Register from A with Borrow        | 1    | 5      |

| SUB  | A,adr  | Subtract Direct Byte from A with Borrow     | 2    | 8      |

| SUB  | A,(Ra) | Subtract Indirect RAM from A with Borrow    | 1    | 6      |

| SUB  | A,data | Subtract Immediate Data from A with Borrow  | 2    | 7      |

| INC  | А      | Increment Accumulator                       | 1    | 3      |

| INC  | Rn     | Increment Register                          | 1    | 5      |

| INC  | adr    | Increment Direct Byte                       | 2    | 8      |

| INC  | (Ra)   | Increment Indirect RAM                      | 1    | 6      |

| INC  | DP     | Increment Data Pointer                      | 1    | 3      |

| DEC  | А      | Decrement Accumulator                       | 1    | 3      |

| DEC  | Rn     | Decrement Register                          | 1    | 5      |

| DEC  | adr    | Decrement Direct Byte                       | 2    | 8      |

| DEC  | (Ra)   | Decrement Indirect RAM                      | 1    | 6      |

| MUL  |        | Multiply A&B                                | 1    | 14     |

| DIV  |        | Divide A&B                                  | 1    | 17     |

| DA   |        | Decimal Adjust Accumulator                  | 1    | 3      |

# Logical Operations

| Mnemo | onic     | Description                                    | Byte | Clocks |