### SN54HC664, SN54HC665, SN74HC664, SN74HC665 OCTAL BUS TRANSCEIVERS WITH PARITY

SCLS152

D2839 MARCH 1984-REVISED SEPTEMBER 1987

- Bus Transceivers with Inverting Outputs ('HC664) or True Outputs ('HC665)

- Generates a Parity Bit for A Bus and B Bus

- Easily Cascadable

- Internal Active Pull-Ups and Pull-Downs

- High-Current 3-State Outputs Can Drive Up to 15 LSTTL Loads

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs

- Dependable Texas Instruments Quality and Reliability

#### description

These octal bus transceivers are designed for asynchronous, bidirectional communication between data buses. The devices transmit data from the A Bus to the B Bus or from the B Bus to the A Bus, depending on the level at the direction control input, DIR. The enable input  $\overline{G}$ , can be used to disable the device so that the buses are isolated. These devices will also generate parity outputs, APO and BPO, which reflect the number of high levels at the A Bus and B Bus, respectively, taking into account the parity inputs API and BPI.

The bidirectional I/O ports feature active circuitry on the input stage that, when the output shared by that pin is disabled, will maintain the input in the last state taken by the output. This state will be maintained until changed by the activity on

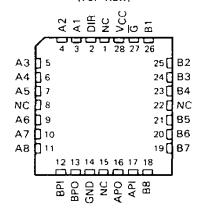

SN54HC664, SN54HC665 . . . JT PACKAGE SN74HC664, SN74HC665 . . . DW OR NT PACKAGE (TOP VIEW)

SN54HC664, SN54HC665 . . . FK PACKAGE (TOP VIEW)

NC-No internal connection

the bus. The advantage of this arrangement is that when all outputs on the bus are disabled, the inputs will be prevented from floating, resulting in minimum power dissipation and minimum susceptibility to noise. This eliminates any need for external pull-up or pull-down resistors. The parity inputs API and BPI have similar circuitry. For futher information, see the Typical Application Data.

The SN54HC664 and SN54HC665 are characterized for operation over the full military temperature range of ~55°C to 125°C. The SN74HC664 and SN74HC665 are characterized for operation from ~40°C to 85°C.

#### **FUNCTION TABLE**

| CONTROL |     | NUMBER OF HIGH |               |   | PUTS  | OPERATION       |                 |  |  |

|---------|-----|----------------|---------------|---|-------|-----------------|-----------------|--|--|

| Ğ       | DIR | A BUS AND API  |               |   | HC664 | HC665           |                 |  |  |

|         |     | X              | 0, 2, 4, 6, 8 | Z | Н     | Ŧ               |                 |  |  |

|         |     | X              | 1, 3, 5, 7, 9 | Z | L     | B Data to A Bus | B Data to A Bus |  |  |

| ,       | н   | 0, 2, 4, 6, 8  | X             | Н | Z     | <del></del>     |                 |  |  |

| _       |     | 1, 3, 5, 7, 9  | X             | L | Z     | A Data to B Bus | A Data to B Bus |  |  |

| Н       | Х   | X              | X             | Z | Z     | Isolation       | Isolation       |  |  |

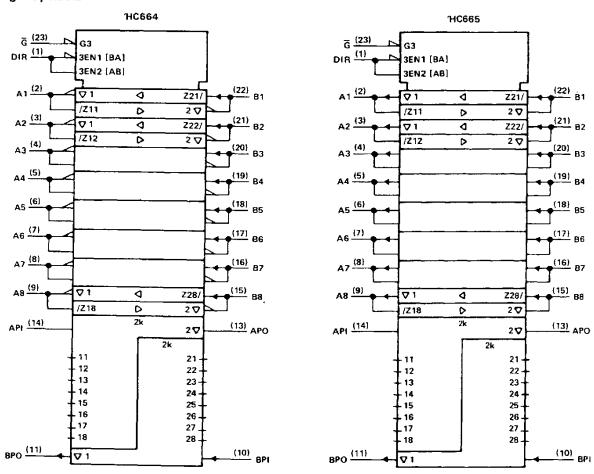

### logic symbols†

<sup>&</sup>lt;sup>†</sup> These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for DW, JT, and NT packages.

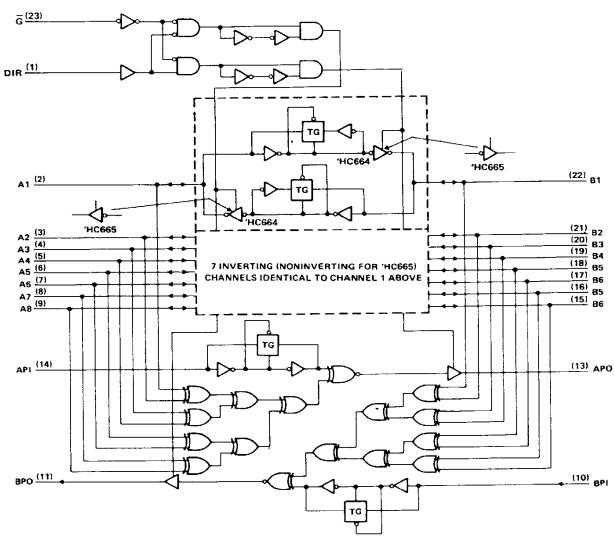

### logic diagram (positive logic)

Pin numbers shown are for DW, JT, and NT packages.

### SN54HC664, SN54HC665, SN74HC664, SN74HC665 OCTAL BUS TRANSCEIVERS WITH PARITY

### absolute maximum ratings over operating free-air temperature range<sup>†</sup>

| Supply voltage, VCC                                                    | -0.5  | V to 7 V |

|------------------------------------------------------------------------|-------|----------|

| Input clamp current, $I_{IK}$ ( $V_{I}$ < 0 or $V_{I}$ > $V_{CC}$ )    |       | ± 20 mA  |

| Output clamp current, IOK (VO < 0 or VO > VCC)                         |       |          |

| Continuous output current, Io (Vo = 0 to Vcc)                          |       | ±35 mA   |

| Continuous current through VCC or GND pins                             |       | ± 70 mA  |

| Lead temperature 1,6 mm (1/16 in) from case for 60 s: FK or JT package |       | . 300°C  |

| Lead temperature 1,6 mm (1/16 in) from case for 10 s: DW or NT package |       | . 260°C  |

| Storage temperature range6                                             | 5°C 1 | o 150°C  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions

|                                |                                        | . ,,                    | 1    | SN54HC664<br>SN54HC665 |      |      | SN74HC664<br>SN74HC665 |      |    |

|--------------------------------|----------------------------------------|-------------------------|------|------------------------|------|------|------------------------|------|----|

|                                |                                        |                         | MIN  | NOM                    | MAX  | MIN  | NOM                    | MAX  |    |

| V <sub>CC</sub> Supply voltage |                                        |                         | 2    | 5                      | 6    | 2    | 5                      | 6    | V  |

|                                |                                        | V <sub>CC</sub> = 2 V   | 1.5  |                        |      | 1.5  |                        |      |    |

| VtH                            | High-level input voltage               | $V_{CC} = 4.5 V$        | 3.15 |                        |      | 3.15 |                        |      | V  |

|                                |                                        | V <sub>CC</sub> = 6 V   | 4.2  |                        |      | 4.2  |                        |      |    |

|                                |                                        | V <sub>CC</sub> = 2 V   | 0    |                        | 0.3  | 0    |                        | 0.3  |    |

| VIL                            | Low-level input voltage                | V <sub>CC</sub> = 4.5 V | 0    |                        | 0.9  | 0    |                        | 0.9  | V  |

|                                |                                        | $V_{CC} = 6 V$          | 0    |                        | 1.2  | 0    |                        | 1.2  |    |

| Vi                             | Input voltage                          |                         | 0    |                        | Vcc  | 0    |                        | VCC  | ٧  |

| Vo                             | Output voltage                         |                         | 0    |                        | VCC  | 0    |                        | Vcc  | ٧  |

|                                | -                                      | V <sub>CC</sub> = 2 V   | 0    |                        | 1000 | 0    |                        | 1000 |    |

| tt                             | Input transition (rise and fall) times | $V_{CC} = 4.5 V$        | 0    |                        | 500  | 0    |                        | 500  | ns |

|                                |                                        | V <sub>CC</sub> = 6 V   | 0    |                        | 400  | 0    |                        | 400  |    |

| TA                             | Operating free-air temperature         | •                       | - 55 |                        | 125  | -40  |                        | 85   | °C |

### SN54HC664, SN54HC665, SN74HC664, SN74HC665 OCTAL BUS TRANSCEIVERS WITH PARITY

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                       | TEST CONDITIONS                                                | Vcc                 | T <sub>A</sub> = 25°C |                         |                   |                   | HC664<br>HC665    | SN74HC664<br>SN74HC665 |                   | UNIT |

|-----------------|-----------------------|----------------------------------------------------------------|---------------------|-----------------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------|

|                 |                       |                                                                |                     |                       |                         |                   | MIN               | MAX               | MIN                    | MAX               | ]    |

| ۷он             |                       | $V_{I} = V_{IH} \text{ or } V_{IL},  I_{OH} = -20 \mu\text{A}$ | 2 V<br>4.5 V<br>6 V | 1.9<br>4.4<br>5.9     |                         | :                 | 1.9<br>4.4<br>5.9 |                   | 1.9<br>4.4<br>5.9      | <del>-</del> "    |      |

|                 | All outputs except    | VI = VIH or VIL. IOH = -6 mA                                   | 4.5 V               | 3.98                  | 4.30                    |                   | 3.7               |                   | 3.84                   |                   | v    |

|                 | APO & BPO             | $V_1 = V_{IH}$ or $V_{IL}$ , $I_{OH} = -7.8$ mA                | 6 V                 | 5.48                  | 5.80                    |                   | 5.2               |                   | 5.34                   |                   |      |

| ∨он             | VOH APO               | $V_1 = V_{IH}$ or $V_{IL}$ , $I_{OH} = -4$ mA                  | 4.5 V               | 3.98                  | 4.30                    |                   | 3.7               |                   | 3.84                   |                   |      |

|                 | вро                   | $V_i = V_{iH}$ or $V_{iL}$ , $I_{OH} = -5.2$ mA                | 6 V                 | 5.48                  | 5.80                    |                   | 5.2               |                   | 5.34                   |                   |      |

| VOL             |                       | $V_{I} = V_{IH} \text{ or } V_{IL},  i_{OL} = 20 \mu A$        | 2 V<br>4.5 V<br>6 V |                       | 0.002<br>0.001<br>0.001 | 0.1<br>0.1<br>0.1 | -                 | 0.1<br>0.1<br>0.1 |                        | 0.1<br>0.1<br>0.1 |      |

|                 | All outputs except    | $V_{I} = V_{IH}$ or $V_{IL}$ , $I_{OL} = 6$ mA                 | 4.5 V               |                       | 0.17                    | 0.26              |                   | 0.4               |                        | 0.33              | ] v  |

|                 | APO & BPO             | $V_1 = V_{1H}$ or $V_{1L}$ , $I_{OL} = 7.8$ mA                 | 6 V                 |                       | 0.15                    | 0.26              |                   | 0.4               |                        | 0.33              |      |

| VOL             | APO<br>or             | VI = VIH or VIL, IOL = 4 mA                                    | 4.5 V               |                       | 0.17                    | 0.26              |                   | 0.4               |                        | 0.33              | ]    |

|                 | BPO                   | VI = VIH or VIL, IOL = 5.2 mA                                  | 6 V                 |                       | 0.15                    | 0.26              |                   | 0.4               |                        | 0.33              |      |

| l <sub>1</sub>  | G, DIR, API<br>or BPI | V <sub>I</sub> = V <sub>CC</sub> or 0                          | 6 V                 |                       | ±0.1                    | ±100              | =                 | ± 1000            | =                      | ± 1000            | nA   |

| loz             | A or B                | VO = VCC or 0                                                  | 6 V                 |                       | ±0.01                   | ±0.5              |                   | ±10               |                        | ± 5               | μΑ   |

| Icc             |                       | $V_1 = V_{CC} \text{ or } 0, I_0 = 0$                          | 6 V                 |                       |                         | 8                 |                   | 160               |                        | 80                | μA   |

| Ci <sup>†</sup> |                       |                                                                | 2 to 6 V            |                       | 3                       | 10                |                   | 10                |                        | 10                | ρF   |

<sup>&</sup>lt;sup>†</sup>This parameter, C<sub>i</sub>, does not apply to 1/0 ports.

## switching characteristics over recommended operating free-air temperature range (unless otherwise noted), $C_L = 50$ pF (see Note 1)

| 242145           | FROM     | то                   | 1 .,    | TA             | <b>⇒ 25</b> | °C                  | SN54 | HC664 | SN74HC664 |          |      |

|------------------|----------|----------------------|---------|----------------|-------------|---------------------|------|-------|-----------|----------|------|

| PARAMETER        | (INPUT)  | (OUTPUT)             | VCC     | MIN            | TYP         | MAX                 | MIN  | MAX   | MIN       | MAX      | UNIT |

|                  |          |                      | 2 V     |                | 75          | 150                 |      | 225   |           | 190      |      |

| t <sub>pd</sub>  | A or B   | B or A               | 4.5 V   |                | 15          | 30                  |      | 45    |           | 38       | ns   |

|                  |          |                      | 6 V     |                | 13          | 26                  |      | 38    |           | 32       |      |

| _                |          | APQ or               | 2 V     |                | 115         | 230                 |      | 345   |           | 290      |      |

| t <sub>pd</sub>  | A or B   | B BPO                | 4.5 V   |                | 23          | 46                  |      | 69    |           | 58       | ns   |

|                  |          |                      | 6 V     |                | 20          | 39                  |      | 59    |           | 49       |      |

|                  | API or   | APQ or               | 2 V     |                | 77          | 155                 |      | 235   |           | 195      |      |

| tpd              |          |                      | 4.5 V   |                | 15          | 31                  |      | 47    |           | 39       | ns   |

|                  | BPI      | BPO                  | 6 V     |                | 13          | 26                  |      | 40    |           | 33       |      |

|                  | Ğ or     |                      | 2 V     |                | 125         | 255                 |      | 385   |           | 320      |      |

| t <sub>en</sub>  |          | A or B               | 4.5 V   |                | 25          | 51                  | İ    | 77    |           | 64       | ns   |

|                  | ÐIR      |                      | 6 V     |                | 22          | 43                  |      | 65    |           | 54       |      |

|                  | <br>G or |                      | 2 V     |                | 125         | 255                 |      | 385   |           | 320      |      |

| t <sub>dis</sub> | DIR      | A or B               | 4.5 V   |                | 25          | 51                  |      | 77    |           | 64       | ំពន  |

|                  | DIR      | Ì                    | 6 V     |                | 22          | 43                  |      | 65    |           | 54       |      |

|                  |          |                      | 2 V     |                | 28          | 60                  |      | 90    |           | 75       |      |

| tt               |          | Any                  | 4.5 V   |                | 8           | 12                  |      | 18    |           | 15       | ns   |

|                  |          | <u> </u>             | 6 V     | <u> </u>       | 6           | 10                  | ,    | 15    |           | 13       | Ĺ    |

| C <sub>pd</sub>  | Powe     | er dissipation capac | citance | T <sub>N</sub> | o load      | I, T <sub>A</sub> = | 25°C |       | 5(        | 6 pF typ |      |

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted), $C_L = 150 \text{ pF}$ (see Note 1)

| PARAMETER       | FROM    | 10       | Ţ ,,  | TA = 25°C |     |     | SN54I | HC664 | SN74HC664 |     |      |

|-----------------|---------|----------|-------|-----------|-----|-----|-------|-------|-----------|-----|------|

| PARAMETER       | (INPUT) | (OUTPUT) | Vcc   | MIN       | TYP | MAX | MIN   | MAX   | MIN       | MAX | UNIT |

|                 | -       |          | 2 V   | 1         | 116 | 235 |       | 355   |           | 295 |      |

| t <sub>pd</sub> | A or B  | BorA     | 4.5 V |           | 23  | 47  | 1     | 71    |           | 59  | กร   |

|                 |         |          | , e A | [         | 20  | 41  |       | 60    | ĺ         | 51  | _    |

|                 | ,       | APO or   | 2 V   |           | 157 | 315 |       | 475   |           | 395 | _    |

| <sup>t</sup> pd | A or B  | BPO B    | 4.5 V |           | 31  | 63  |       | 95    |           | 79  | ns   |

|                 |         | BPO      | 6 V   |           | 27  | 54  | 81    |       | 68        |     |      |

| -               | API or  | APO or   | 2 V   | 1         | 120 | 240 |       | 365   |           | 300 |      |

| t <sub>pd</sub> |         | 1 1 1 4  | 4.5 V |           | 24  | 48  | Í     | 73    |           | 60  | ns   |

|                 |         | ВРО      | 6 V   |           | 20  | 41  | 1     | 62    |           | 52  |      |

|                 | G or    |          | 2 V   |           | 170 | 340 |       | 515   |           | 425 |      |

| t <sub>en</sub> | DIR     | A or B   | 4.5 V |           | 34  | 68  | ĺ     | 103   | ĺ         | 85  | ns   |

|                 |         |          | 6 V   |           | 29  | 58  | ļ     | 87    |           | 73  | _    |

|                 |         |          | 2 V   |           | 37  | 210 |       | 315   |           | 265 |      |

| t <sub>t</sub>  |         | Any      | 4.5 V |           | 12  | 42  |       | 63    |           | 53  | กร   |

|                 |         |          | 6 V   |           | 10  | 36  |       | 53    |           | 45  |      |

NOTE 1: Load circuits and voltage waveforms are shown in Section 1.

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted), $C_L = 50 \text{ pF}$ (see Note 1)

| PARAMETER        | FROM    | то            | v     | T <sub>A</sub> | TA = 25°C |     |     | HC665 | SN74 | UNIT |         |

|------------------|---------|---------------|-------|----------------|-----------|-----|-----|-------|------|------|---------|

| PARAMETER        | (INPUT) | (OUTPUT)      | VCC   | MIN            | TYP       | MAX | MIN | MAX   | MIN  | MAX  | _ Gilli |

|                  |         |               | 2 V   |                | 70        | 140 |     | 210   |      | 175  |         |

| tpd              | A or B  | BorA          | 4.5 V |                | 14        | 28  | i   | 42    |      | 35   | ກຣ      |

|                  |         | 1             | 6 V   |                | 12        | 24  |     | 36    |      | 30   |         |

|                  |         | APO or        | 2 V   |                | 115       | 230 |     | 345   |      | 290  |         |

| tpd              | A or B  | BPO BPO       | 4.5 V |                | 23        | 46  | ĺ   | 69    |      | 58   | กร      |

|                  |         | BPU           | 6 <   |                | 20        | 39  |     | 59    |      | 49   |         |

|                  | A DI -  | 4.00          | 2 V   |                | 77        | 155 |     | 235   |      | 195  |         |

| tpd              | API or  | APO or<br>BPO | 4.5 V |                | 15        | 31  | [   | 47    |      | 39   | ns      |

|                  | BPI BPI | Bru           | 6 V   |                | 13        | 26  |     | 40    |      | 33   |         |

|                  | ਰ or    |               | 2 V   |                | 125       | 255 |     | 385   |      | 320  |         |

| t <sub>en</sub>  |         | A or B        | 4.5 V | 1              | 25        | 51  |     | 77    |      | 64   | ns      |

| _                | DIR     |               | 6 V   | 1              | 22        | 43  |     | 65    |      | 54   |         |

|                  |         |               | 2 V   |                | 125       | 255 |     | 385   |      | 320  |         |

| t <sub>dis</sub> | DIR     | A or B        | 4.5 V | ļ              | 25        | 51  |     | 77    |      | 64   | 'ns     |

|                  | UIK     | l             | 6 V   |                | 22        | 43  |     | 65    |      | 54   |         |

|                  |         |               | 2 V   | 1              | 28        | 60  |     | 90    |      | 75   |         |

| tt               |         | Апу           | 4.5 V | İ              | 8         | 12  |     | 18    |      | 15   | ns      |

|                  |         |               | 6 V   |                | 6         | 10  |     | 15    |      | 13   |         |

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted), C<sub>L</sub> = 150 pF (see Note 1)

No load,  $T_A = 25 \,^{\circ}C$

56 pF typ

Power dissipation capacitance

| PARAMETER       | FROM    | то       |       | TA  | TA = 25°C |     | SN54HC665 |     | SN74HC665 |     | LIANT |

|-----------------|---------|----------|-------|-----|-----------|-----|-----------|-----|-----------|-----|-------|

| PARAMETER       | (INPUT) | (OUTPUT) | Vcc   | MIN | TYP       | MAX | MIN       | MAX | MIN       | MAX | UNIT  |

|                 |         |          | 2 V   |     | 112       | 225 |           | 340 |           | 280 |       |

| <sup>†</sup> pď | A or B  | B or A   | 4.5 V | -   | 22        | 45  |           | 68  |           | 56  | คร    |

|                 |         |          | · 6 V | [   | 20        | 39  |           | 58  |           | 49  |       |

|                 |         | APO or   | 2 V   |     | 157       | 315 |           | 475 |           | 395 |       |

| <sup>t</sup> pd | A or B  | BPO Br   | 4.5 V |     | 31        | 63  |           | 95  |           | 79  | กร    |

|                 |         | ВРО      | 6 V   |     | 27        | 54  |           | 81  |           | 68  |       |

| T               | API or  | APO or   | 2 V   |     | 120       | 240 |           | 365 |           | 300 |       |

| <sup>t</sup> pd | BPI     |          | 4.5 V |     | 24        | 48  |           | 73  |           | 60  | ns    |

|                 |         | ВРО      | 6 V   |     | 20        | 41  |           | 62  |           | 52  |       |

|                 | G or    |          | 2 V   |     | 170       | 340 |           | 515 |           | 425 |       |

| t <sub>en</sub> | DIR     | A or B   | 4.5 V |     | 34        | 68  |           | 103 |           | 85  | ns    |

|                 | OIR     |          | 6 V   | 1   | 29        | 58  |           | 87  |           | 73  |       |

|                 |         |          | 2 V   | 1   | 37        | 210 |           | 315 |           | 265 |       |

| tt              |         | Any      | 4.5 V | ĺ   | 12        | 42  |           | 63  |           | 53  | ns    |

|                 |         |          | 6 V   |     | 10        | 36  |           | 53  |           | 45  |       |

NOTE 1: Load circuits and voltage waveforms are shown in Section 1.

$C_{pd}$

#### TYPICAL APPLICATION DATA

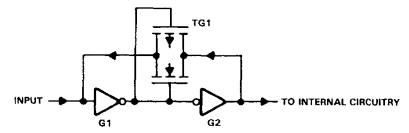

The unique structure used on the I/O ports and the parity inputs of these devices deserves some special consideration (see Figure 1). Only the input structure is shown. The conventional 3-state output structure associated with each I/O port has been omitted to facilitate understanding.

FIGURE 1. INPUT STRUCTURE

The two inverters (G1 and G2) have a transmission gate (TG1) connected in a feedback loop around them. This transmission gate is connected in an unusual fashion, that is, with the gates of both transistors connected to the output of G1. Thus, with the output of G1 at either a high or a low level, one or the other of the transistors will be turned on allowing feedback of the output of G2 to the input of G1. The effect of TG1 is that the input level will be maintained at whatever level existed prior to the bus being disabled or the level currently existing on the bus will be reinforced.

To understand the operation of this input, assume that initially the input is at a low logic level. As the input voltage is raised, TG1 sinks current to attempt to maintain the low level. However, TG1 consists of small geometry transistors and appears resistive as current flows thus allowing the input voltage to rise toward the threshold voltage of G1. When the threshold voltage is reached, G1 changes state causing G2 to change state. G2 then attempts to maintain a high level on the input through TG1. A similar operation occurs when the input voltage is decreased toward the threshold voltage of G1. G2 sources current through TG1 until the threshold is reached.

This characteristic of the input stage has some implications for the input current levels. With the input held at either V<sub>CC</sub> or GND, there is no voltage across TG1 and negligible input current. However, as the input voltage is raised from GND or lowered from V<sub>CC</sub>, the input current rises as the voltage across TG1 increases. The input current continues to rise until it reaches a maximum just as the threshold voltage of G1 is reached.

This configuration provides for minimum power dissipation when the bus is inactive (all outputs on the bus in the high-impedance state) and minimum susceptibility to noise on the bus during this time. The increase in input current may go unnoticed as it only occurs during transitions on the bus. Care must be taken when measuring input currents (e.g., at incoming inspection) to ensure that the input voltage is set to the correct value.

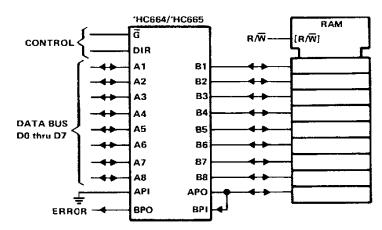

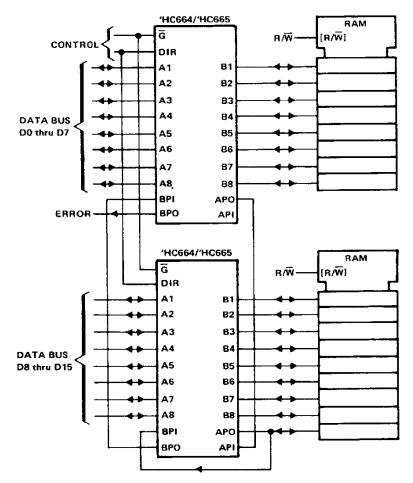

The use of these devices for interfacing to 8-, 16-, 24-bit-wide memory arrays with parity is illustrated in Figures 2, 3 and 4.

### TYPICAL APPLICATION DATA

FIGURE 2. 8-BIT-WIDE MEMORY ARRAY WITH PARITY

FIGURE 3. 16-BIT-WIDE MEMORY ARRAY WITH PARITY

#### TYPICAL APPLICATION DATA 'HC664/'HC665 CONTROL G (R/W) DIR A1 81 A2 **B**2 АЗ **B3** Α4 **B4** DATA BUS **A5 B**5 D0 thru D7 A6 В6 **A**7 87 8A API APO BPO BP! 'HC664/'HC665 MAR (R/W) DIR A1 81 A2 82 ΑЗ 83 DATA BUS **A5** 85 D8 thru D15 A6 86 A7 **B7 A8** 89 API APO 'HC280 вро BPI PART OF 2k 'HC367 8 PART OF EN С **'HC00** 'HC664/'HC665 EVEN O DIR A1 82 G A2 Σ ERROR В3 A3 Α4 84 DATA BUS D16 thru D23 **A5** 85 86 A6 Α7 8A 88 API APO BPO BP1

FIGURE 4. 24-BIT-WIDE MEMORY ARRAY WITH PARITY

NOTE: The 'HC280 eliminates ripple carry delays associated with Figures 2 and 3. However, in those two cases the delays are probably too small to be of concern.

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated