#### PLUS153B/D

#### DESCRIPTION

The PLUS153 PLDs are high speed, combinatorial Programmable Logic Arrays. The Philips Semiconductors state-of-the-art Oxide Isolated Bipolar fabrication process is employed to produce propagation delays as short as 12ns.

The 20-pin PLUS153 devices have a programmable AND array and a programmable OR array. Unlike PAL® devices, 100% product term sharing is supported. Any of the 32 logic product terms can be connected to any or all of the 10 output OR gates. Most PAL ICs are limited to 7 AND terms per OR function; the PLUS153 devices can support up to 32 input wide OR functions.

The polarity of each output is user-programmable as either active-High or active-Low, thus allowing AND-OR or AND-NOR logic implementation. This feature adds an element of design flexibility, particularly when implementing complex decoding functions.

The PLUS153 devices are user-programmable using one of several commercially available, industry standard PLD programmers.

#### **FEATURES**

- I/O propagation delays (worst case)

- PLUS153B 15ns max.

- PLUS153D 12ns max.

- Functional superset of 16L8 and most other 20-pin combinatorial PAL devices

- Two programmable arrays

- Supports 32 input wide OR functions

- 8 inputs

- 10 bi-directional I/O

- 42 AND gates

- 32 logic product terms

- 10 direction control terms

- Programmable output polarity

- Active-High or Active-Low

- Security fuse

- 3-State outputs

- Power dissipation: 750mW (typ.)

- TTL Compatible

#### **APPLICATIONS**

- Random logic

- Code converters

- Fault detectors

- Function generators

- Address mapping

- Multiplexing

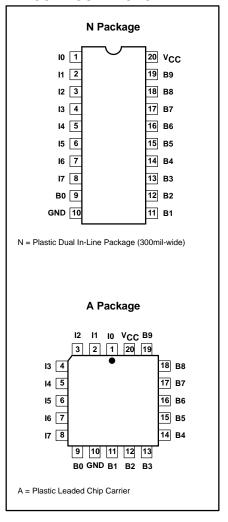

#### PIN CONFIGURATIONS

#### ORDERING INFORMATION

| DESCRIPTION                             | t <sub>PD</sub> (MAX) | ORDER CODE | DRAWING NUMBER |

|-----------------------------------------|-----------------------|------------|----------------|

| 20-Pin Plastic Dual-In-Line 300mil-wide | 15ns                  | PLUS153BN  | 0408D          |

| 20-Pin Plastic Dual-In-Line 300mil-wide | 12ns                  | PLUS153DN  | 0408D          |

| 20-Pin Plastic Leaded Chip Carrier      | 15ns                  | PLUS153BA  | 0400E          |

| 20-Pin Plastic Leaded Chip Carrier      | 12ns                  | PLUS153DA  | 0400E          |

<sup>®</sup>PAL is a registered trademark of Monolithic Memories, Inc., a wholly owned subsidiary of Advanced Micro Devices Corporation.

PLUS153B/D

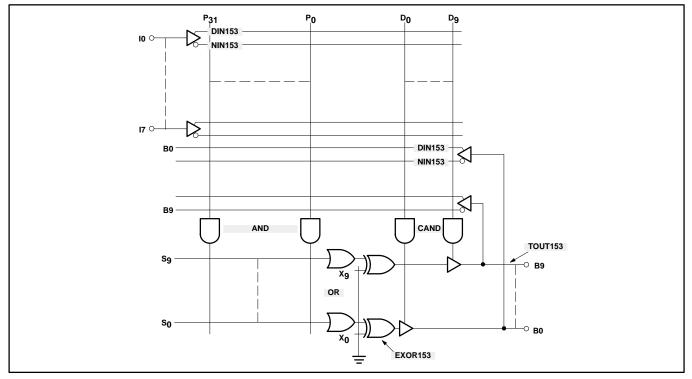

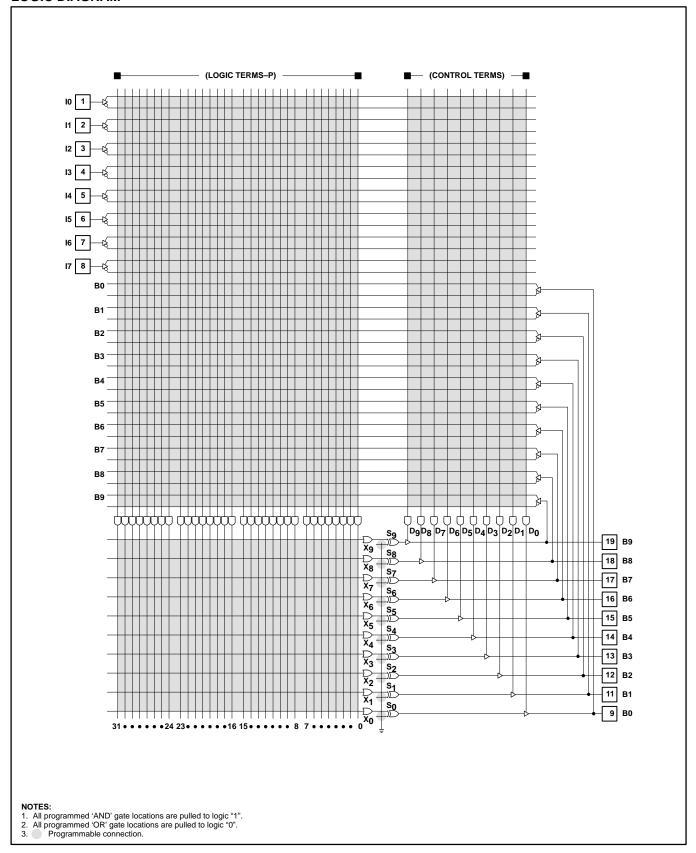

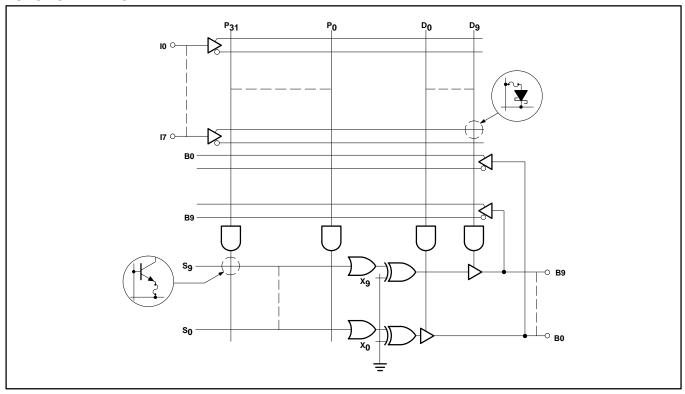

#### **LOGIC DIAGRAM**

PLUS153B/D

#### **FUNCTIONAL DIAGRAM**

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

|                  |                                      | RAT |      |          |  |

|------------------|--------------------------------------|-----|------|----------|--|

| SYMBOL           | PARAMETER                            | MIN | MAX  | UNIT     |  |

| V <sub>CC</sub>  | Supply voltage                       |     | +7   | $V_{DC}$ |  |

| V <sub>IN</sub>  | Input voltage                        |     | +5.5 | $V_{DC}$ |  |

| V <sub>OUT</sub> | Output voltage                       |     | +5.5 | $V_{DC}$ |  |

| I <sub>IN</sub>  | Input currents                       | -30 | +30  | mA       |  |

| I <sub>OUT</sub> | Output currents                      |     | +100 | mA       |  |

| T <sub>amb</sub> | Operating free-air temperature range | 0   | +75  | °C       |  |

| T <sub>stg</sub> | Storage temperature range            | -65 | +150 | °C       |  |

#### THERMAL RATINGS

| TEMPERATURE                                |       |  |  |  |  |

|--------------------------------------------|-------|--|--|--|--|

| Maximum junction                           | 150°C |  |  |  |  |

| Maximum ambient                            | 75°C  |  |  |  |  |

| Allowable thermal rise ambient to junction | 75°C  |  |  |  |  |

#### NOTES:

Stresses above those listed may cause malfunction or permanent damage to the device.

This is a stress rating only. Functional operation at these or any other condition above those indicated in the operational and programming specification of the device is not implied.

PLUS153B/D

#### DC ELECTRICAL CHARACTERISTICS

$0^{\circ}C \leq T_{amb} \leq +75^{\circ}C,~4.75 \leq V_{CC} \leq 5.25V$

|                  |                                             |                                |     | LIMITS           |      |      |  |

|------------------|---------------------------------------------|--------------------------------|-----|------------------|------|------|--|

| SYMBOL PARAMETER |                                             | TEST CONDITIONS                | MIN | TYP <sup>1</sup> | MAX  | UNIT |  |

| Input volt       | age <sup>2</sup>                            |                                |     |                  |      |      |  |

| V <sub>IL</sub>  | Low                                         | V <sub>CC</sub> = MIN          |     |                  | 0.8  | V    |  |

| $V_{IH}$         | High                                        | $V_{CC} = MAX$                 | 2.0 |                  |      | V    |  |

| $V_{IC}$         | Clamp                                       | $V_{CC} = MIN, I_{IN} = -12mA$ |     | -0.8             | -1.2 | V    |  |

| Output vo        | oltage <sup>2</sup>                         |                                |     |                  |      |      |  |

|                  |                                             | V <sub>CC</sub> = MIN          |     |                  |      |      |  |

| $V_{OL}$         | Low <sup>4</sup>                            | I <sub>OL</sub> = 15mA         |     |                  | 0.5  | V    |  |

| $V_{OH}$         | High <sup>5</sup>                           | $I_{OH} = -2mA$                | 2.4 |                  |      | V    |  |

| Input curi       | rent <sup>9</sup>                           |                                |     |                  |      |      |  |

|                  |                                             | V <sub>CC</sub> = MAX          |     |                  |      |      |  |

| I <sub>IL</sub>  | Low                                         | $V_{IN} = 0.45V$               |     |                  | -100 | μΑ   |  |

| I <sub>IH</sub>  | High                                        | $V_{IN} = V_{CC}$              |     |                  | 40   | μΑ   |  |

| Output cu        | ırrent                                      |                                |     |                  |      |      |  |

|                  |                                             | V <sub>CC</sub> = MAX          |     |                  |      |      |  |

| $I_{O(OFF)}$     | Hi-Z state <sup>8</sup>                     | V <sub>OUT</sub> = 2.7V        |     |                  | 80   | μΑ   |  |

|                  |                                             | V <sub>OUT</sub> = 0.45V       |     |                  | -140 |      |  |

| Ios              | Short circuit <sup>3, 5, 6</sup>            | $V_{OUT} = 0V$                 | -15 |                  | -70  | mA   |  |

| I <sub>CC</sub>  | V <sub>CC</sub> supply current <sup>7</sup> | V <sub>CC</sub> = MAX          |     | 150              | 200  | mA   |  |

| Capacitar        | nce                                         |                                |     |                  |      |      |  |

|                  |                                             | V <sub>CC</sub> = 5V           |     |                  |      |      |  |

| $C_{IN}$         | Input                                       | V <sub>IN</sub> = 2.0V         |     | 8                |      | pF   |  |

| C <sub>B</sub>   | I/O                                         | V <sub>B</sub> = 2.0V          |     | 15               |      | pF   |  |

- 1. All typical values are at  $V_{CC}$  = 5V,  $T_{amb}$  = +25°C. 2. All voltage values are with respect to network ground terminal.

- 3. Test one at a time.

- 4. Measured with inputs I0 I2 = 0V, inputs I3 I5 = 4.5V, inputs I7 = 4.5V and I6 = 10V. For outputs B0 B4 and for outputs B5 B9 apply the same conditions except I7 = 0V.

- Same conditions as Note 4 except I7 = +10V.

- 6. Duration of short circuit should not exceed 1 second.

7. I<sub>CC</sub> is measured with inputs I0 I7 and B0 B9 = 0V.

- 8. Leakage values are a combination of input and output leakage.

- 9.  $I_{IL}$  and  $I_{IH}$  limits are for dedicated inputs only (I0 I7).

PLUS153B/D

#### AC ELECTRICAL CHARACTERISTICS

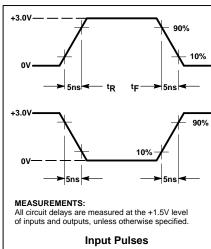

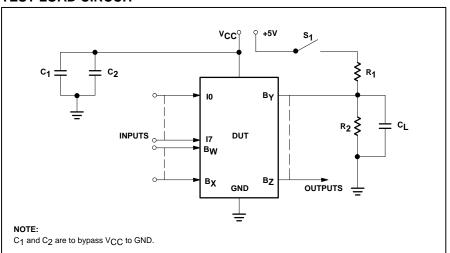

$0^{\circ}C \leq T_{amb} \leq +75^{\circ}C,~4.75V \leq V_{CC} \leq 5.25V,~R_{1} = 300\Omega,~R_{2} = 390\Omega$

|                 |                                |           |            |                       | LIMITS |        |     |     |        |     |      |

|-----------------|--------------------------------|-----------|------------|-----------------------|--------|--------|-----|-----|--------|-----|------|

| SYMBOL          | PARAMETER                      | FROM      | то         | TEST                  | Р      | LUS153 | В   | Р   | LUS153 | D   | UNIT |

|                 |                                |           |            | CONDITION             | MIN    | TYP    | MAX | MIN | TYP    | MAX |      |

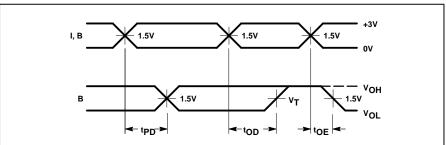

| t <sub>PD</sub> | Propagation Delay <sup>2</sup> | Input +/- | Output +/- | C <sub>L</sub> = 30pF |        | 11     | 15  |     | 10     | 12  | ns   |

| t <sub>OE</sub> | Output Enable <sup>1</sup>     | Input +/- | Output –   | C <sub>L</sub> = 30pF |        | 11     | 15  |     | 10     | 12  | ns   |

| t <sub>OD</sub> | Output Disable <sup>1</sup>    | Input +/- | Output +   | $C_L = 5pF$           |        | 11     | 15  |     | 10     | 12  | ns   |

#### NOTES:

- 1. For 3-State output; output enable times are tested with  $C_L = 30pF$  to the 1.5V level, and  $S_1$  is open for high-impedance to High tests and closed for high-impedance to Low tests. Output disable times are tested with  $C_L = 5pF$ . High-to-High impedance tests are made to an output voltage of  $V_T = (V_{OH} 0.5V)$  with  $S_1$  open, and Low-to-High impedance tests are made to the  $V_T = (V_{OL} + 0.5V)$  level with  $S_1$  closed.

- 2. All propagation delays are measured and specified under worst case conditions.

#### **VOLTAGE WAVEFORMS**

#### **TEST LOAD CIRCUIT**

#### **TIMING DEFINITIONS**

| SYMBOL          | PARAMETER                                                                   |

|-----------------|-----------------------------------------------------------------------------|

| t <sub>PD</sub> | Propagation delay between input and output.                                 |

| t <sub>OD</sub> | Delay between input change and when output is off (Hi-Z or High).           |

| t <sub>OE</sub> | Delay between input change and when output reflects specified output level. |

#### **TIMING DIAGRAM**

PLUS153B/D

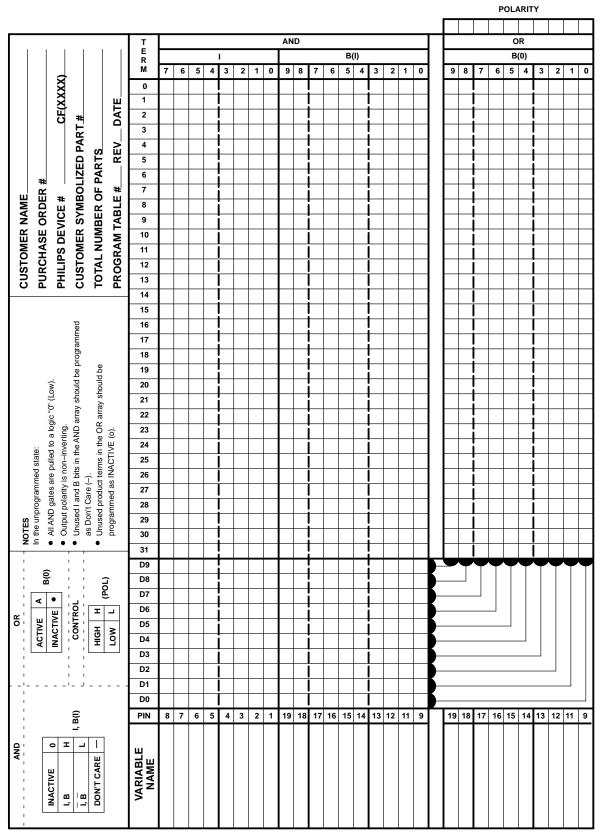

#### LOGIC PROGRAMMING

The PLUS153B/D is fully supported by industry standard (JEDEC compatible) PLD CAD tools, including Philips Semiconductors SNAP design software package. ABEL™ and CUPL™ design software packages also support the PLUS153B/D architecture.

All packages allow Boolean and state equation entry formats. SNAP, ABEL and CUPL also accept, as input, schematic capture format.

PLUS153B/D logic designs can also be generated using the program table entry format, which is detailed on the following page. This program table entry format is supported by SNAP only.

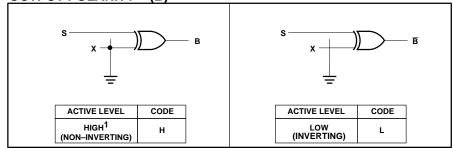

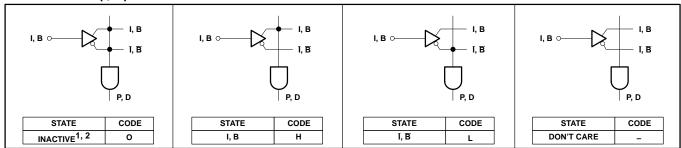

To implement the desired logic functions, the state of each logic variable from logic equations (I, B, O, P, etc.) is assigned a symbol. The symbols for TRUE, COMPLEMENT, INACTIVE, PRESET, etc., are defined below.

### PROGRAMMING AND SOFTWARE SUPPORT

Refer to Section 9 (Development Software) and Section 10 (Third-Party Programmer/Software Support) of this data handbook for additional information.

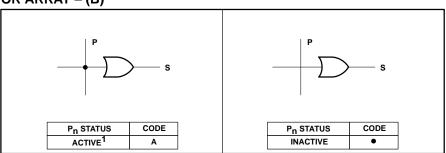

**OUTPUT POLARITY - (B)**

#### AND ARRAY - (I, B)

#### OR ARRAY - (B)

#### NOTES:

- 1. This is the initial unprogrammed state of all links.

- Any gate P<sub>n</sub> will be unconditionally inhibited if both the true and complement of an input (either I or B) are left intact.

#### **VIRGIN STATE**

A factory shipped virgin device contains all fusible links intact, such that:

- All outputs are at "H" polarity.

- 2. All P<sub>n</sub> terms are disabled.

- 3. All P<sub>n</sub> terms are active on all outputs.

ABEL is a trademark of Data I/O Corp. CUPL is a trademark of Logical Devices, Inc.

#### PLUS153B/D

#### **PROGRAM TABLE**

PLUS153B/D

#### **SNAP RESOURCE SUMMARY DESIGNATIONS**