# INTEGRATED CIRCUITS

Product specification Supersedes data of 1999 Oct 19 2000 May 17

# **PCK2010R**

#### **FEATURES**

- Mixed 2.5 V and 3.3 V operation

- Four CPU clocks at 2.5 V

- Eight PCI clocks at 3.3 V, one free-running (synchronous with CPU clocks)

- Four 3.3 V fixed clocks @ 66 MHz

- Two 2.5 V CPUDIV2 clocks @ 1/2 CPU clock frequency

- Three 2.5 V IOAPIC clocks @ 16.67 MHz

- One 3.3 V 48 MHz USB clock

- Two 3.3 V reference clocks @ 14.318 MHz

- Reference 14.31818 MHz Xtal oscillator input

- 133 MHz or 100 MHz operation

- Power management control input pins

- CPU clock jitter ≤ 250 ps cycle-cycle

- CPU clock skew ≤ 175 ps pin-pin

- 0.0ns 1.5 ns CPU 3V66 delay

- 1.5ns 3.5 ns 3V66 PCI delay

- 1.5ns 4.0 ns CPU IOAPIC delay

- 1.5ns 4.0 ns CPU PCI delay

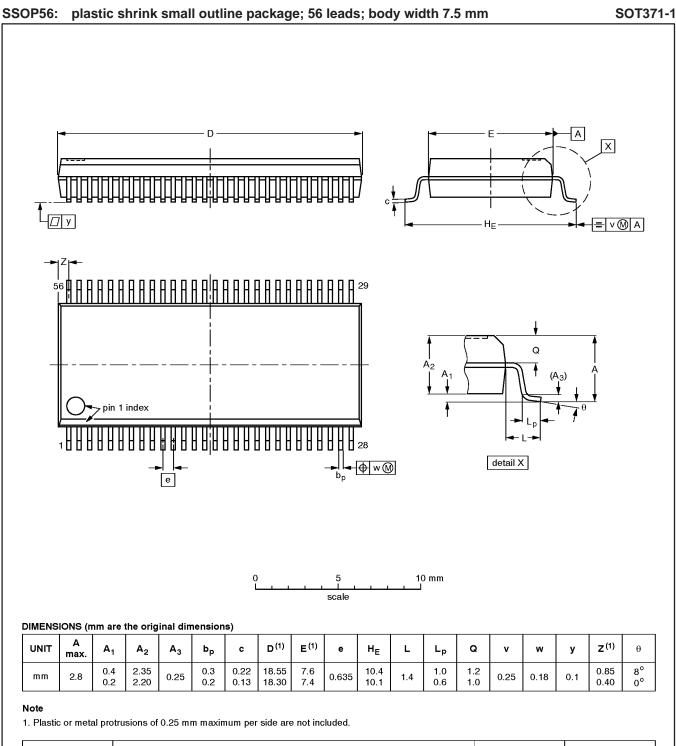

- Available in 56-pin SSOP package

- ±0.5% center spread spectrum capability via select pins

- -0.5% down spread spectrum capability via select pins

#### DESCRIPTION

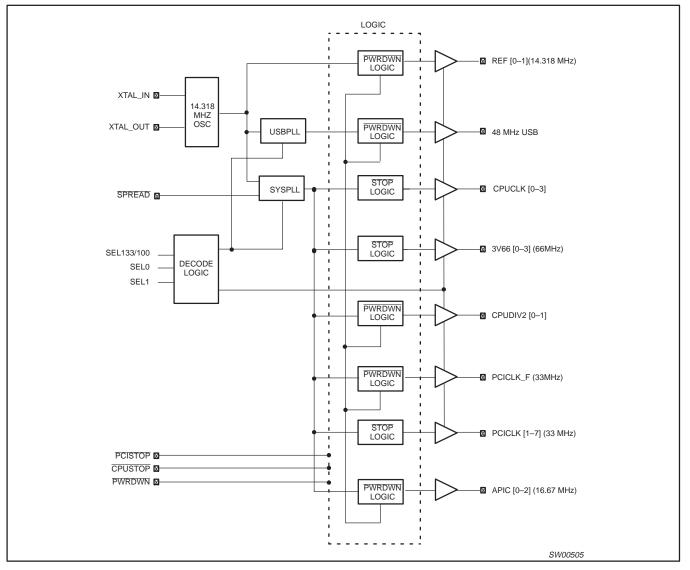

The PCK2010R is a clock generator (frequency synthesizer) chip for a Pentium II and other similar processors.

The PCK2010R has four CPU clock outputs at 2.5 V, two CPUDIV2 clock outputs running at ½ CPU clock frequency (66 MHz or 50 MHz depending on the state of SEL133/100) and four 3V66 clocks running at 66MHz. There are eight PCI clock outputs running at 33 MHz. One of the PCI clock outputs is free-running. Additionally, the part has three 2.5 V IOAPIC clock outputs at 16.67 MHz and two 3.3 V reference clock outputs at 14.318 MHz. All clock outputs meet Intel's drive strength, rise/fall time, jitter, accuracy, and skew requirements.

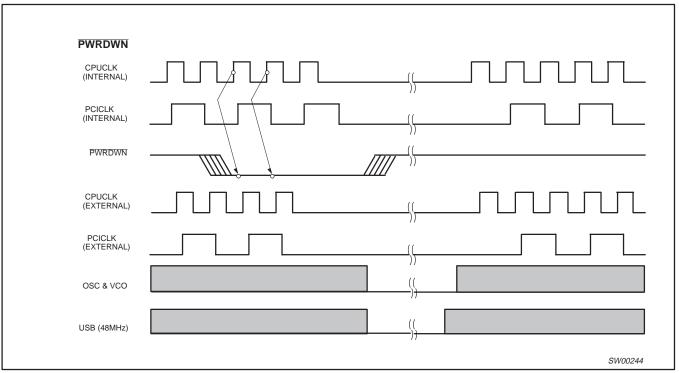

The part possesses dedicated power-down, CPUSTOP, and PCISTOP input pins for power management control. These inputs are synchronized on-chip and ensure glitch-free output transitions. When the CPUSTOP input is asserted, the CPU clock outputs and 3V66 clock outputs are driven LOW. When the PCISTOP input is asserted, the PCI clock outputs are driven LOW.

Finally, when the PWRDWN input pin is asserted, the internal reference oscillator and PLLs are shut down, and all outputs are driven LOW.

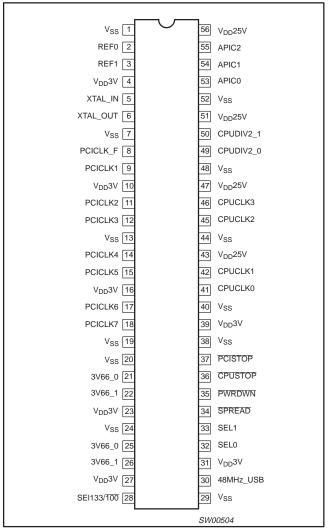

#### **PIN CONFIGURATION**

#### **ORDERING INFORMATION**

| PACKAGES            | TEMPERATURE RANGE | ORDER CODE  | DRAWING NUMBER |  |  |

|---------------------|-------------------|-------------|----------------|--|--|

| 56-Pin plastic SSOP | 0°C to +70°C      | PCK2010R DL | SOT371-1       |  |  |

Intel and Pentium are registered trademarks of Intel Corporation.

### **PCK2010R**

#### **PIN DESCRIPTION**

| PIN NUMBER                                      | SYMBOL             | FUNCTION                                                                                                        |

|-------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------|

| 2,3                                             | REF [0–1]          | 3.3 V 14.318 MHz clock output                                                                                   |

| 5                                               | XTAL_IN            | 14.318 MHz crystal input                                                                                        |

| 6                                               | XTAL_OUT           | 14.318 MHz crystal output                                                                                       |

| 8                                               | PCICLK_F           | 3.3 V free running PCI clock                                                                                    |

| 9, 11, 12, 14, 15, 17, 18                       | PCICLK [1–7]       | 3.3 V PCI clock outputs                                                                                         |

| 21, 22, 25, 26                                  | 3V66 [0–3]         | 3.3 V fixed 66 MHz clock outputs                                                                                |

| 28                                              | SEL133/100         | Select input pin for enabling 133 MHz or 100 MHz CPU outputs. H = 133 MHz, L = 100 MHz                          |

| 30                                              | 48 MHz USB         | 3.3 V fixed 48 MHZ clock output                                                                                 |

| 32, 33                                          | SEL [0–1]          | Logic select pins. TTL levels.                                                                                  |

| 34                                              | SPREAD             | 3.3 V LVTTL input. Enables spread spectrum mode when held LOW.                                                  |

| 35                                              | PWRDWN             | 3.3 V LVTTL input. Device enters powerdown mode when held LOW.                                                  |

| 36                                              | CPUSTOP            | 3.3 V LVTTL input. Stops all CPU clocks and 3V66 clocks when held LOW. CPUDIV_2 output remains on all the time. |

| 37                                              | PCISTOP            | 3.3 V LVTTL input. Stops all PCI clocks except PCICLK_F when held LOW.                                          |

| 41, 42, 45, 46                                  | CPUCLK [0-3]       | 2.5 V CPU output. 133 MHz or 100MHz depending on state of input pin SEL133/100.                                 |

| 49, 50                                          | CPUDIV_2 [0-1]     | 2.5 V output running at 1/2 CPU clock frequency. 66 MHz or 50 MHz depending on state of input pin SEL133/100.   |

| 53, 54, 55                                      | IOAPIC [0-2]       | 2.5 V clock outputs running divide synchronous with the CPU clock frequency. Fixed 16.67 MHz limit.             |

| 4, 10, 16, 23, 27, 31, 39                       | V <sub>DD3V</sub>  | 3.3 V power supply.                                                                                             |

| 1, 7, 13, 19, 20, 24, 29,<br>38, 40, 44, 48, 52 | V <sub>SS</sub>    | Ground                                                                                                          |

| 43, 47, 51, 56                                  | V <sub>DD25V</sub> | 2.5 V power supply                                                                                              |

#### NOTE:

V<sub>DD3V</sub>, V<sub>DD25V</sub> and V<sub>SS</sub> in the above tables reflects a likely internal POWER and GROUND partition to reduce the effects of internal noise on the performance of the device. In reality, the platform will be configured with the V<sub>DD25V</sub> pins tied to a 2.5 V supply, all remaining V<sub>DD</sub> pins tied to a common 3.3 V supply and all V<sub>SS</sub> pins being common.

# PCK2010R

#### **BLOCK DIAGRAM**

#### **FUNCTION TABLE**

| SEL<br>133/100 | SEL1 | SEL0 | CPU     | CPUDIV2 | 3V66   | PCI    | 48 MHz | REF        | IOAPIC    | NOTES   |

|----------------|------|------|---------|---------|--------|--------|--------|------------|-----------|---------|

| 0              | 0    | 0    | HI-Z    | HI-Z    | HI-Z   | HI-Z   | HI-Z   | HI-Z       | HI-Z      | 1       |

| 0              | 0    | 1    | N/A     | N/A     | N/A    | N/A    | N/A    | N/A        | N/A       | 2       |

| 0              | 1    | 0    | 100 MHz | 50 MHz  | 66 MHz | 33 MHz | HI-Z   | 14.318 MHz | 16.67 MHz | 3       |

| 0              | 1    | 1    | 100 MHz | 50 MHz  | 66 MHz | 33 MHz | 48 MHz | 14.318 MHz | 16.67 MHz | 4, 7, 8 |

| 1              | 0    | 0    | TCLK/2  | TCLK/4  | TCLK/4 | TCLK/8 | TCLK/2 | TCLK       | TCLK/16   | 5, 6    |

| 1              | 0    | 1    | N/A     | N/A     | N/A    | N/A    | N/A    | N/A        | N/A       | 2       |

| 1              | 1    | 0    | 133 MHz | 66 MHz  | 66 MHz | 33 MHz | HI-Z   | 14.318 MHz | 16.67 MHz | 3       |

| 1              | 1    | 1    | 133 MHz | 66 MHz  | 66 MHz | 33 MHz | 48 MHz | 14.318 MHz | 16.67 MHz | 4, 7, 8 |

#### NOTES:

1. Required for board level "bed-of-nails" testing.

2. Used to support Intel confidential application.

3. 48 MHz PLL disabled to reduce component jitter. 48 MHz outputs to be held Hi-Z instead of driven to LOW state.

4. "Normal" mode of operation.

5. TCLK is a test clock over driven on the XTALIN input during test mode. TCLK mode is based on 133 MHz CPU select logic.

6. Required for DC output impedance verification.

7. Frequency accuracy of 48 MHz must be +167 PPM to match USB default.

8. Range of reference frequency allowed is MIN = 14.316 MHz, NOMINAL = 14.31818 MHz, MAX = 14.32 MHz

| CLOCK OUTPUT        | CLOCK OUTPUT TARGET FREQUENCY (MHz) |        | PPM |

|---------------------|-------------------------------------|--------|-----|

| USBCLK <sup>7</sup> | 48.0                                | 48.008 | 167 |

#### **CLOCK ENABLE CONFIGURATION**

| CPUSTOP | PWRDWN | PCISTOP | CPUCLK | CPUDIV2 | APIC | 3V66 | PCI | PCI_F | REF / 48 MHz | OSC | VCOs |

|---------|--------|---------|--------|---------|------|------|-----|-------|--------------|-----|------|

| Х       | 0      | Х       | LOW    | LOW     | LOW  | LOW  | LOW | LOW   | LOW          | OFF | OFF  |

| 0       | 1      | 0       | LOW    | ON      | ON   | LOW  | LOW | ON    | ON           | ON  | ON   |

| 0       | 1      | 1       | LOW    | ON      | ON   | LOW  | ON  | ON    | ON           | ON  | ON   |

| 1       | 1      | 0       | ON     | ON      | ON   | ON   | LOW | ON    | ON           | ON  | ON   |

| 1       | 1      | 1       | ON     | ON      | ON   | ON   | ON  | ON    | ON           | ON  | ON   |

NOTES:

1. LOW means outputs held static LOW as per latency requirement below

2. ON means active.

3. PWRDWN pulled LOW, impacts all outputs including REF and 48 MHz outputs.

4. All 3V66 clocks as well as CPU clocks should stop cleanly when CPUSTOP is pulled LOW.

CPUDIV2, IOAPIC, REF, 48 MHz signals are not controlled by the CPUSTOP functionality and are enabled all in all conditions except when <u>PWRDWN</u> is LOW.

#### **POWER MANAGEMENT REQUIREMENTS**

| SIGNAL  | SIGNAL STATE         | LATENCY                                    |  |  |

|---------|----------------------|--------------------------------------------|--|--|

| SIGNAL  | SIGNAL STATE         | NO. OF RISING EDGES OF FREE RUNNING PCICLK |  |  |

| CPUSTOP | 0 (DISABLED)         | 1                                          |  |  |

|         | 1 (ENABLED)          | 1                                          |  |  |

| PCISTOP | 0 (DISABLED)         | 1                                          |  |  |

|         | 1 (ENABLED)          | 1                                          |  |  |

| PWRDWN  | 1 (NORMAL OPERATION) | 3 ms                                       |  |  |

|         | 0 (POWER DOWN)       | 2 MAX                                      |  |  |

NOTES:

1. Clock ON/OFF latency is defined as the number of rising edges of free running PCICLKs between the clock disable goes HIGH/LOW to the first valid clock that comes out of the device.

2. Power up latency is when PWRDWN goes inactive (HIGH) to when the first valid clocks are driven from the device.

### **PCK2010R**

#### ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>

In accordance with the Absolute Maximum Rating System (IEC 134) Voltages are referenced to  $V_{SS}$  ( $V_{SS}$  = 0 V)

| SYMBOL            | PARAMETER                                                  | CONDITION                                                                         | I    | LIMITS                |      |  |

|-------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|------|-----------------------|------|--|

| STWBUL            | FARAMETER                                                  | CONDITION                                                                         | MIN  | MAX                   | UNIT |  |

| V <sub>DD3</sub>  | DC 3.3 V core supply voltage                               |                                                                                   | -0.5 | +4.6                  | V    |  |

| V <sub>DDQ3</sub> | DC 3.3 V I/O supply voltage                                |                                                                                   | -0.5 | +4.6                  | V    |  |

| V <sub>DDQ2</sub> | DC 2.5 V I/O supply voltage                                |                                                                                   | -0.5 | +3.6                  | V    |  |

| I <sub>IK</sub>   | DC input diode current                                     | V <sub>1</sub> < 0                                                                |      | -50                   | mA   |  |

| VI                | DC input voltage                                           | Note 2                                                                            | -0.5 | 5.5                   | V    |  |

| I <sub>ОК</sub>   | DC output diode current                                    | $V_{O} > V_{CC} \text{ or } V_{O} < 0$                                            |      | ±50                   | mA   |  |

| Vo                | DC output voltage                                          | Note 2                                                                            | -0.5 | V <sub>CC</sub> + 0.5 | V    |  |

| Ι <sub>Ο</sub>    | DC output source or sink current                           | $V_{O} = 0$ to $V_{CC}$                                                           |      | ±50                   | mA   |  |

| T <sub>STG</sub>  | Storage temperature range                                  |                                                                                   | -65  | +150                  | °C   |  |

| P <sub>TOT</sub>  | Power dissipation per package plastic medium-shrink (SSOP) | For temperature range: -40 to +125°C<br>above +55°C derate linearly with 11.3mW/K |      | 850                   | mW   |  |

NOTES:

Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

#### **RECOMMENDED OPERATING CONDITIONS**

| CYMDOL             | DADAMETED                                                                                       | CONDITIONS                                                                                                                                                                                                  | LIM                                    | ITS                                     |                                  |

|--------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|----------------------------------|

| SYMBOL             | PARAMETER                                                                                       | CONDITIONS                                                                                                                                                                                                  | MIN                                    | MAX                                     | UNIT                             |

| V <sub>DD3V</sub>  | DC 3.3 V core supply voltage                                                                    |                                                                                                                                                                                                             | 3.135                                  | 3.465                                   | V                                |

| V <sub>DD25V</sub> | DC 2.5 V I/O supply voltage                                                                     |                                                                                                                                                                                                             | 2.375                                  | 2.625                                   | V                                |

| CL                 | Capacitive load on:<br>CPUCLK<br>PCICLK<br>CPUDIV2<br>3V66<br>48 MHz clock USB<br>REF<br>IOAPIC | 1 device load, possible 2 loads<br>Must meet PCI 2.1 requirements<br>1 device load, possible 2 loads<br>1 device load, possible 2 loads<br>1 device load<br>1 device load<br>1 device load<br>1 device load | 10<br>10<br>10<br>10<br>10<br>10<br>10 | 20<br>30<br>20<br>30<br>20<br>20<br>20  | pF<br>pF<br>pF<br>pF<br>pF<br>pF |

| VI                 | DC input voltage range                                                                          |                                                                                                                                                                                                             | 0                                      | V <sub>DD3V</sub>                       | V                                |

| V <sub>O</sub>     | DC output voltage range                                                                         |                                                                                                                                                                                                             | 0                                      | V <sub>DD25V</sub><br>V <sub>DD3V</sub> | V                                |

| f <sub>REF</sub>   | Reference frequency, oscillator nominal value                                                   |                                                                                                                                                                                                             | 14.31818                               | 14.31818                                | MHz                              |

| T <sub>amb</sub>   | Operating ambient temperature range in free air                                                 |                                                                                                                                                                                                             | 0                                      | +70                                     | °C                               |

#### **POWER MANAGEMENT**

| CK133<br>CONDITION                                                              | $\begin{array}{l} \mbox{MAXIMUM 2.5V SUPPLY CONSUMPTION} \\ \mbox{MAXIMUM DISCRETE CAP LOADS,} \\ \mbox{V}_{DD25V} = 2.625 \ \mbox{V} \\ \mbox{ALL STATIC INPUTS} = \mbox{V}_{DD3V} \ \mbox{OR V}_{SS} \end{array}$ | $\begin{array}{l} \mbox{MAXIMUM 3.3V SUPPLY CONSUMPTION} \\ \mbox{MAXIMUM DISCRETE CAP LOADS,} \\ \mbox{V}_{DD25V} = 3.465 \ V \\ \mbox{ALL STATIC INPUTS} = V_{DD3V} \ \mbox{OR } V_{SS} \end{array}$ |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-down mode<br>(PWRDWN = 0)                                                 | 100 µA                                                                                                                                                                                                              | 200 μΑ                                                                                                                                                                                                 |

| Full active 100 MHz<br>SEL133/100# = 0<br>SEL1, 0 = 1 1<br>CPUSTOP, PCISTOP = 1 | 80 mA                                                                                                                                                                                                               | 160 mA                                                                                                                                                                                                 |

| Full active 133 MHz<br>SEL133/100# = 1<br>SEL1, 0 = 1 1<br>CPUSTOP, PCISTOP = 1 | 90 mA                                                                                                                                                                                                               | 160 mA                                                                                                                                                                                                 |

#### Product specification

## **PCK2010R**

#### **DC CHARACTERISTICS**

| SYMBOL           | DADAMETED                                            |                       | TEST CONDITION                               | S                                 |                      | LIMITS<br>0°C to | ;<br>) +70°C          | UNIT |

|------------------|------------------------------------------------------|-----------------------|----------------------------------------------|-----------------------------------|----------------------|------------------|-----------------------|------|

| STMBOL           | PARAMETER                                            | V <sub>DD</sub> OTHER |                                              |                                   | MIN                  | ТҮР              | МАХ                   |      |

| V <sub>IH</sub>  | HIGH level input voltage                             | 3.135 to 3.465        |                                              | V <sub>DD25V</sub> =<br>2.5 V ±5% | 2.0                  |                  | V <sub>DD</sub> + 0.3 | V    |

| VIL              | LOW level input voltage                              | 3.135 to 3.465        |                                              | V <sub>DD3V</sub> =<br>3.3 V ±5%  | V <sub>SS</sub> -0.3 |                  | 0.8                   | V    |

| V <sub>OH2</sub> | 2.5 V output HIGH voltage<br>CPUCLK, IOAPIC, CPUDIV2 | 2.375 to 2.625        | I <sub>OH</sub> = -1 mA                      |                                   | 2.0                  |                  | -                     | V    |

| V <sub>OL2</sub> | 2.5 V output LOW voltage<br>CPUCLK, IOAPIC, CPUDIV2  | 2.375 to 2.625        | I <sub>OL</sub> = 1 mA                       |                                   | -                    |                  | 0.4                   | V    |

| V <sub>OH3</sub> | 3.3 V output HIGH voltage<br>REF, 48 MHz USB         | 3.135 to 3.465        | I <sub>OH</sub> = -1 mA                      |                                   | 2.0                  |                  | -                     | V    |

| V <sub>OL3</sub> | 3.3 V output LOW voltage<br>REF, 48 MHz USB          | 3.135 to 3.465        | I <sub>OL</sub> = 1 mA                       |                                   | -                    |                  | 0.4                   | V    |

| V <sub>OH3</sub> | 3.3 V output HIGH voltage<br>PCI, 3V66               | 3.135 to 3.465        | I <sub>OH</sub> = -1 mA                      |                                   | 2.4                  |                  | -                     | V    |

| V <sub>OL3</sub> | 3.3 V output LOW voltage<br>PCI, 3V66                | 3.135 to 3.465        | I <sub>OL</sub> = 1 mA                       |                                   | -                    |                  | 0.55                  | V    |

|                  | CPUCLK                                               | 2.375                 | V <sub>OUT</sub> = 1.0 V                     |                                   | -27                  | 1                | -                     |      |

| I <sub>ОН</sub>  | output HIGH current                                  | 2.625                 | V <sub>OUT</sub> = 2.375 V                   |                                   | -                    |                  | -27                   | mA   |

|                  | 48 MHz USB, REF                                      | 3.135                 | V <sub>OUT</sub> = 1.0 V                     |                                   | -29                  |                  | -                     |      |

| I <sub>ОН</sub>  | output HIGH current                                  | 3.465                 | V <sub>OUT</sub> = 3.135 V                   |                                   | -                    |                  | -23                   | mA   |

| l                | PCI, 3V66                                            | 3.135                 | V <sub>OUT</sub> = 1.0 V                     |                                   | -33                  |                  | -                     | mA   |

| I <sub>ОН</sub>  | output HIGH current                                  | 3.465                 | V <sub>OUT</sub> = 3.135 V                   |                                   | -                    |                  | -33                   |      |

|                  | CPUCLK                                               | 2.375                 | V <sub>OUT</sub> = 1.2 V                     |                                   | 27                   |                  | -                     | mA   |

| I <sub>OL</sub>  | output LOW current                                   | 2.625                 | V <sub>OUT</sub> = 0.3 V                     |                                   | -                    |                  | 30                    |      |

| I <sub>OL</sub>  | 48 MHz USB, REF                                      | 3.135                 | V <sub>OUT</sub> = 1.95 V                    |                                   | 29                   |                  | -                     | mA   |

| 'OL              | output LOW current                                   | 3.465                 | $V_{OUT} = 0.4 V$                            |                                   | -                    |                  | 27                    | 110. |

| IOL              | PCI, 3V66                                            | 3.135                 | V <sub>OUT</sub> = 1.95 V                    |                                   | 30                   |                  | -                     | mA   |

| IOL              | output LOW current                                   | 3.465                 | V <sub>OUT</sub> = 0.4 V                     |                                   | -                    |                  | 38                    |      |

| ±II              | Input leakage current                                | 3.465                 |                                              |                                   | -                    |                  | 5                     | μΑ   |

| ±I <sub>OZ</sub> | 3-State output OFF-State<br>current                  | 3.465                 | V <sub>OUT</sub> =<br>V <sub>dd</sub> or GND | $I_{O} = 0$                       | -                    |                  | 10                    | μA   |

| Cin              | Input pin capacitance                                |                       |                                              |                                   |                      |                  | 5                     | pF   |

| Cxtal            | Xtal pin capacitance, as seen<br>by external crystal |                       |                                              |                                   |                      | 18               |                       | pF   |

| Cout             | Output pin capacitance                               |                       |                                              |                                   |                      |                  | 6                     | рF   |

## **PCK2010R**

#### AC CHARACTERISTICS

$V_{DD3V}$  = 3.3 V  $\pm$  5%; VDDAPIC =  $V_{DD25V}$  = 2.5 V  $~\pm$  5%; f\_{crystal} = 14.31818 MHz

#### CPU CLOCK OUTPUTS, CPU(0-3) (LUMP CAPACITANCE TEST LOAD = 20 pF)

| CVMDOL              |                           |        | LIMITS<br>T <sub>amb</sub> = 0°C to +70°C |        | IITS<br>C to +70°C |    | NOTES |

|---------------------|---------------------------|--------|-------------------------------------------|--------|--------------------|----|-------|

| SYMBOL              | PARAMETER                 | 133 MF | Iz MODE                                   | 100 MH | z MODE             |    | NOTES |

|                     |                           | MIN    | MAX                                       | MIN    | MAX                | 1  |       |

| T <sub>HKP</sub>    | CPUCLK period             | 7.5    | 8.0                                       | 10.0   | 10.5               | ns | 2, 9  |

| Т <sub>НКН</sub>    | CPUCLK HIGH time          | 1.87   | n/a                                       | 3.0    | n/a                | ns | 5, 10 |

| T <sub>HKL</sub>    | CPUCLK LOW time           | 1.67   | n/a                                       | 2.8    | n/a                | ns | 6, 10 |

| T <sub>HRISE</sub>  | CPUCLK rise time          | 0.4    | 1.6                                       | 0.4    | 1.6                | ns | 8     |

| T <sub>HFALL</sub>  | CPUCLK fall time          | 0.4    | 1.6                                       | 0.4    | 1.6                | ns | 8     |

| T <sub>JITTER</sub> | CPUCLK cycle-cycle jitter |        | 250                                       |        | 250                | ps |       |

| DUTY CYCLE          | Output Duty Cycle         | 45     | 55                                        | 45     | 55                 | %  | 1     |

| T <sub>HSKW</sub>   | CPUCLK pin-pin skew       |        | 175                                       |        | 175                | ps | 2     |

#### CPUDIV2 CLOCK OUTPUTS, CPUDIV2 (0–1) (LUMP CAPACITANCE TEST LOAD = 20 pF)

| CVMDOL              |                                | LIMITS<br>T <sub>amb</sub> = 0°C to +70°C |        | LIM<br>T <sub>amb</sub> = 0°C |        |    | NOTES |

|---------------------|--------------------------------|-------------------------------------------|--------|-------------------------------|--------|----|-------|

| SYMBOL              | PARAMETER                      | 133 MH                                    | z MODE | 100 MH                        | z MODE |    | NOTES |

|                     |                                | MIN                                       | MAX    | MIN                           | MAX    | 1  |       |

| T <sub>HKP</sub>    | CPUDIV2 CLK period             | 15.0                                      | 16.0   | 20.0                          | 21.0   | ns | 2, 9  |

| Т <sub>НКН</sub>    | CPUDIV2 CLK HIGH time          | 5.25                                      | n/a    | 7.5                           | n/a    | ns | 5, 10 |

| T <sub>HKL</sub>    | CPUDIV2 CLK LOW time           | 5.05                                      | n/a    | 7.3                           | n/a    | ns | 6, 10 |

| T <sub>HRISE</sub>  | CPUDIV2 CLK rise time          | 0.4                                       | 1.6    | 0.4                           | 1.6    | ns | 8     |

| T <sub>HFALL</sub>  | CPUDIV2 CLK fall time          | 0.4                                       | 1.6    | 0.4                           | 1.6    | ns | 8     |

| T <sub>JITTER</sub> | CPUDIV2 CLK cycle-cycle jitter |                                           | 250    |                               | 250    | ps |       |

| DUTY CYCLE          | CPUDIV2 CLK Duty Cycle         | 45                                        | 55     | 45                            | 55     | %  | 1     |

| T <sub>HSKW</sub>   | CPUDIV2 CLK pin-pin skew       |                                           | 175    |                               | 175    | ps | 2     |

#### PCI CLOCK OUTPUTS, PCI(0-7) (LUMP CAPACITANCE TEST LOAD = 30 pF)

|                     |                           |        | /ITS<br>C to +70°C |        | /ITS<br>C to +70°C |    |       |

|---------------------|---------------------------|--------|--------------------|--------|--------------------|----|-------|

| SYMBOL              | PARAMETER                 | 133 MH | Iz MODE            | 100 MH | Iz MODE            |    | NOTES |

|                     |                           | MIN    | MAX                | MIN    | MAX                | 1  |       |

| T <sub>HKP</sub>    | PCICLK period             | 30.0   | n/a                | 30.0   | n/a                | ns | 2, 9  |

| Т <sub>НКН</sub>    | PCICLK HIGH time          | 12.0   | n/a                | 12.0   | n/a                | ns | 5, 10 |

| T <sub>HKL</sub>    | PCICLK LOW time           | 12.0   | n/a                | 12.0   | n/a                | ns | 6, 10 |

| T <sub>HRISE</sub>  | PCICLK rise time          | 0.5    | 2.0                | 0.5    | 2.0                | ns | 8     |

| T <sub>HFALL</sub>  | PCICLK fall time          | 0.5    | 2.0                | 0.5    | 2.0                | ns | 8     |

| T <sub>JITTER</sub> | PCICLK cycle-cycle jitter |        | 500                |        | 500                | ps |       |

| DUTY CYCLE          | PCICLK Duty Cycle         | 45     | 55                 | 45     | 55                 | %  | 1     |

| T <sub>HSKW</sub>   | PCICLK pin-pin skew       |        | 500                |        | 500                | ps | 2     |

## PCK2010R

#### APIC(0–1) CLOCK OUTPUT (LUMP CAPACITANCE TEST LOAD = 20 pF)

| • •                 | •                             |        |                   | • •    |                   |      |       |

|---------------------|-------------------------------|--------|-------------------|--------|-------------------|------|-------|

|                     |                               |        | NTS<br>C to +70°C |        | NTS<br>C to +70°C |      |       |

| SYMBOL              | PARAMETER                     | 133 MH | z MODE            | 100 MH | z MODE            | UNIT | NOTES |

|                     |                               | MIN    | MAX               | MIN    | MAX               | 1    |       |

| T <sub>HKP</sub>    | IOAPIC CLK period             | 60.0   | 64.0              | 60.0   | 64.0              | ns   | 2, 9  |

| Т <sub>НКН</sub>    | IOAPIC CLK HIGH time          | 25.5   | n/a               | 25.5   | n/a               | ns   | 5, 10 |

| T <sub>HKL</sub>    | IOAPIC CLK LOW time           | 25.3   | n/a               | 25.3   | n/a               | ns   | 6, 10 |

| T <sub>HRISE</sub>  | IOAPIC CLK rise time          | 0.4    | 1.6               | 0.4    | 1.6               | ns   | 8     |

| T <sub>HFALL</sub>  | IOAPIC CLK fall time          | 0.4    | 1.6               | 0.4    | 1.6               | ns   | 8     |

| T <sub>JITTER</sub> | IOAPIC CLK cycle-cycle jitter |        | 500               |        | 500               | ps   |       |

| DUTY CYCLE          | IOAPIC CLK Duty Cycle         | 45     | 55                | 45     | 55                | %    | 1     |

| T <sub>HSKW</sub>   | IOAPIC CLK pin-pin skew       |        | 250               |        | 250               | ps   | 2     |

#### 3V66 CLOCK OUTPUT, 3V66 (0-3) (LUMP CAPACITANCE TEST LOAD = 30 pF)

|                     | 212111222                   |        | /ITS<br>C to +70°C |        | /ITS<br>C to +70°C |      | NOTEO   |

|---------------------|-----------------------------|--------|--------------------|--------|--------------------|------|---------|

| SYMBOL              | PARAMETER                   | 133 MH | Iz MODE            | 100 MH | Iz MODE            | UNIT | NOTES   |

|                     |                             | MIN    | MAX                | MIN    | MAX                | 1    |         |

| T <sub>HKP</sub>    | 3V66 CLK period             | 15.0   | 16.0               | 15.0   | 16.0               | ns   | 2, 9, 4 |

| Т <sub>НКН</sub>    | 3V66 CLK HIGH time          | 5.25   | n/a                | 5.25   | n/a                | ns   | 5, 10   |

| T <sub>HKL</sub>    | 3V66 CLK LOW time           | 5.05   | n/a                | 5.05   | n/a                | ns   | 6, 10   |

| T <sub>HRISE</sub>  | 3V66 CLK rise time          | 0.4    | 1.6                | 0.4    | 1.6                | ns   | 8       |

| T <sub>HFALL</sub>  | 3V66 CLK fall time          | 0.4    | 1.6                | 0.4    | 1.6                | ns   | 8       |

| T <sub>JITTER</sub> | 3V66 CLK cycle-cycle jitter |        | 500                |        | 500                | ps   |         |

| DUTY CYCLE          | 3V66 CLK Duty Cycle         | 45     | 55                 | 45     | 55                 | %    | 1       |

| T <sub>HSKW</sub>   | 3V66 CLK pin-pin skew       |        | 250                |        | 250                | ps   | 2       |

#### 48MHZ(0-1) CLOCK OUTPUT (LUMP CAPACITANCE TEST LOAD = 20 pF)

| SYMBOL                               | PARAMETER                                          | TEST CC | NDITIONS               |     | IITS<br>C to +70°C | UNIT |

|--------------------------------------|----------------------------------------------------|---------|------------------------|-----|--------------------|------|

|                                      |                                                    |         | NOTES                  | MIN | MAX                |      |

| f                                    | Frequency, Actual                                  |         | ned by PLL<br>er ratio | 48. | 008                | MHz  |

| f <sub>D</sub>                       | Deviation from 48 MHz                              | (48.008 | 8 – 48)/48             | +1  | 67                 | ppm  |

| T <sub>HRISE</sub> (t <sub>R</sub> ) | Output rise edge rate                              |         |                        | 1   | 4                  | ns   |

| T <sub>HFALL</sub> (t <sub>F</sub> ) | Output fall edge rate                              |         |                        | 1   | 4                  | ns   |

| DUTY CYCLE (t <sub>D</sub> )         | Duty Cycle                                         |         |                        | 45  | 55                 | %    |

|                                      |                                                    | 133     | MHz                    | 100 | MHz                |      |

| T <sub>JITTER</sub>                  | CLK cycle-cycle jitter                             | MIN     | MAX                    | MIN | MAX                | ps   |

|                                      |                                                    |         | 500                    |     | 500                |      |

| Т <sub>НSTB</sub> (f <sub>ST</sub> ) | Frequency stabilization from Power-up (cold start) |         |                        |     | 3                  | ms   |

NOTE:

1. See Figure 5 for measure points.

### **PCK2010R**

#### AC CHARACTERISTICS (Continued)

| SYMBOL                | PARAMETER                           | TEST COND                     | ITIONS                        | T <sub>amb</sub> : | LIMITS<br>= 0°C to +7 | 70°C |    | NOTES |

|-----------------------|-------------------------------------|-------------------------------|-------------------------------|--------------------|-----------------------|------|----|-------|

| STMBOL                | TANAMETER                           | Measurement loads<br>(lumped) | Measure points                | MIN                | ТҮР                   | МАХ  |    | NOTED |

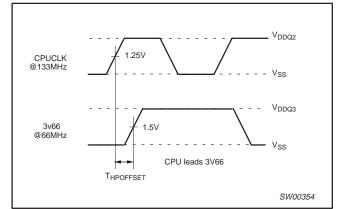

| T <sub>HPOFFSET</sub> | CPUCLK to 3V66 CLK,<br>CPU leads    | CPU@20 pF,<br>3V66@30 pF      | CPU@1.25 V,<br>3V66@1.5 V     | 0.0                | 0.45                  | 1.5  | ns | 1     |

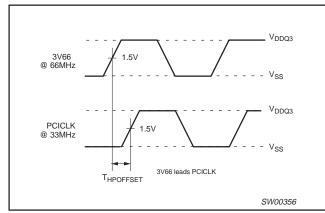

| T <sub>HPOFFSET</sub> | 3V66 CLK to PCICLK,<br>3V66 leads   | 3V66@30 pF,<br>PCI@30 pF      | 3V66@1.5 V,<br>PCI@1.5 V      | 1.5                | 2.0                   | 3.5  | ns | 1     |

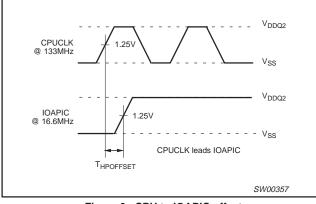

| T <sub>HPOFFSET</sub> | CPUCLK to IOAPIC,<br>CPU leads      | CPU@20 pF,<br>IOAPIC@20 pF    | 3CPU@1.25 V,<br>IOAPIC@1.25 V | 1.5                | 2.4                   | 4.0  | ns | 1     |

| T <sub>HPOFFSET</sub> | CPUCLK to PCICLK ,<br>CPU leads     | CPU@20 pF<br>PCI@30 pF        | CPU@1.25 V<br>PCI@1.5 V       | 1.5                | 2.7                   | 4.0  | ns |       |

| T <sub>HPOFFSET</sub> | CPUDIV2 to CPUCLK,<br>CPUDIV2 leads | CPUDIV2@20 pF<br>CPU@20 pF    | CPUDIV2@<br>CPU@1.25 V        | 0.75               | 1.6                   | 2.5  | ns |       |

#### NOTES:

1. Output drivers must have monotonic rise/fall times through the specified  $V_{\text{OL}}/V_{\text{OH}}$  levels.

2. Period, jitter, offset and skew measured on rising edge @1.25 V for 2.5 V clocks and @ 1.5 V for 3.3 V clocks.

The PCICLK is the CPUCLK divided by four at CPUCLK = 133 MHz. The 3V66 CLK is internal VCO frequency divided by three at CPUCLK = 100 MHz.

4. 3V66 CLK is internal VCO frequency divided by two at CPUCLK = 133 MHz. The 3V66 CLK is internal VCO frequency divided by three at CPUCLK = 100 MHz.

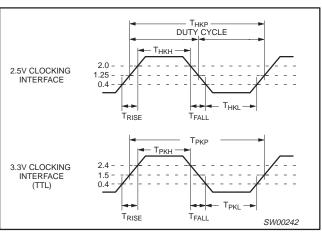

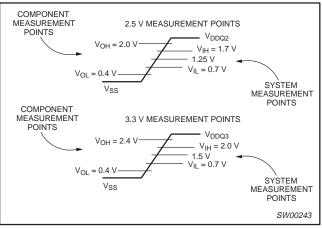

- 5. T<sub>HKH</sub> is measured at 2.0 V for 2.5 V outputs, 2.4 V for 3.3 V outputs as shown in Figure 4.

- 6. T<sub>HKL</sub> is measured at 0.4 V for all outputs as shown in Figure 4.

- 7. The time is specified from when V<sub>DDQ</sub> achieves its nominal operating level (typical condition V<sub>DDQ</sub> = 3.3 V) until the frequency output is stable and operating within specification.

- 8.  $T_{HRISE}$  and  $T_{HFALL}$  are measured as a transition through the threshold region  $V_{OL} = 0.4$  V and  $V_{OH} = 2.4$  V (1 mA) JEDEC specification. 9. The average period over any 1  $\mu$ s period of time must be greater than the minimum specified period.

- The average period over any 1 µs period of time must be greater than the minimum specified period.

Calculated at minimum edge-rate (1V/ns) to guarantee 45/55% duty-cycle. Pulse width is required to be wider at faster edge-rate to ensure duty-cycle specification is met.

- 11. Output (see Figure 5 for measure points).

## Product specification

### PCK2010R

#### SPREAD SPECTRUM FUNCTION TABLE

| SPREAD#      | SEL133/100# | SEL1   | SEL0   | Function                        |            |

|--------------|-------------|--------|--------|---------------------------------|------------|

| pin 34       | pin 28      | pin 33 | pin 32 | Function                        | 48 MHz PLL |

| 0 (active)   | 0 (100 MHz) | 0      | 0      | 3-State to High Impedance       | Inactive   |

| 0 (active)   | 0 (100 MHz) | 0      | 1      | 100 MHz, Center Spread ±0.5%    | Active     |

| 0 (active)   | 0 (100 MHz) | 1      | 0      | 100 MHz, Down Spread – 0.5%     | Inactive   |

| 0 (active)   | 0 (100 MHz) | 1      | 1      | 100 MHz, Down Spread – 0.5%     | Active     |

| 0 (active)   | 1 (133 MHz) | 0      | 0      | Test Mode                       | Active     |

| 0 (active)   | 1 (133 MHz) | 0      | 1      | 133 MHz, Center Spread ±0.5%    | Active     |

| 0 (active)   | 1 (133 MHz) | 1      | 0      | 133 MHz, Down Spread – 0.5%     | Inactive   |

| 0 (active)   | 1 (133 MHz) | 1      | 1      | 133 MHz, Down Spread – 0.5%     | Active     |

| 1 (inactive) | 0 (100 MHz) | 0      | 0      | 3-State to High Impedance       | Inactive   |

| 1 (inactive) | 0 (100 MHz) | 0      | 1      | 100 MHz, No Center Spread ±0.5% | Active     |

| 1 (inactive) | 0 (100 MHz) | 1      | 0      | 100 MHz, No Down Spread – 0.5%  | Inactive   |

| 1 (inactive) | 0 (100 MHz) | 1      | 1      | 100 MHz, No Down Spread – 0.5%  | Active     |

| 1 (inactive) | 1 (133 MHz) | 0      | 0      | Test Mode                       | Active     |

| 1 (inactive) | 1 (133 MHz) | 0      | 1      | 133 MHz, No Center Spread ±0.5% | Active     |

| 1 (inactive) | 1 (133 MHz) | 1      | 0      | 133 MHz, No Down Spread – 0.5%  | Inactive   |

| 1 (inactive) | 1 (133 MHz) | 1      | 1      | 133 MHz, No Down Spread – 0.5%  | Active     |

# PCK2010R

#### AC WAVEFORMS

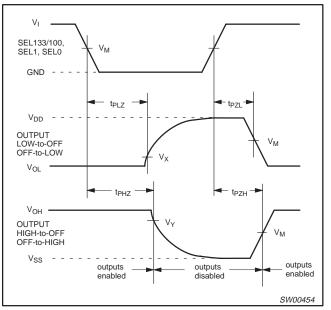

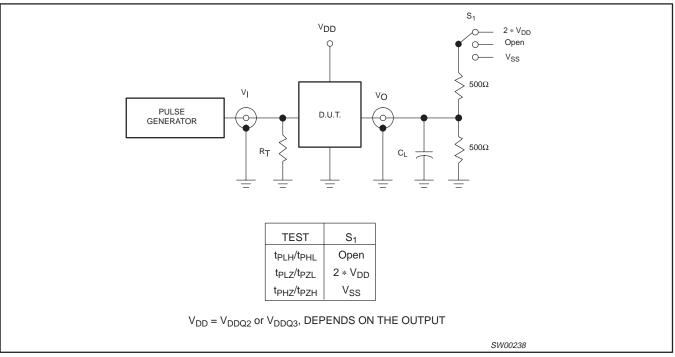

$V_M$  = 1.25 V @  $V_{DDQ2}$  and 1.5 V @  $V_{DDQ3}$   $V_X$  =  $V_{OL}$  + 0.3 V  $V_Y$  =  $V_{OH}$  –0.3 V  $V_{OL}$  and  $V_{OH}$  are the typical output voltage drop that occur with the output load.

Figure 1. CPUCLK to 3V66 offset

Figure 2. 3V66 to PCI offset

Figure 3. CPU to IOAPIC offset

Figure 4. 2.5V/3.3V clock waveforms

Figure 5. Component versus system measure points

Figure 6. 3-State enable and disable times

PCK2010R

Figure 7. Load circuitry for switching times

Figure 8. Power Management

# PCK2010R

Product specification

| OUTLINE  |     | REFERENCES |      |  | EUROPEAN   | ISSUE DATE                       |

|----------|-----|------------|------|--|------------|----------------------------------|

| VERSION  | IEC | JEDEC      | EIAJ |  | PROJECTION | ISSUE DATE                       |

| SOT371-1 |     | MO-118AB   |      |  |            | <del>-93-11-02</del><br>95-02-04 |

Product specification

PCK2010R

NOTES

# PCK2010R

#### Data sheet status

| Data sheet<br>status      | Product<br>status | Definition <sup>[1]</sup>                                                                                                                                                                                                                                        |

|---------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development       | This data sheet contains the design target or goal specifications for product development.<br>Specification may change in any manner without notice.                                                                                                             |

| Preliminary specification | Qualification     | This data sheet contains preliminary data, and supplementary data will be published at a later date.<br>Philips Semiconductors reserves the right to make changes at any time without notice in order to<br>improve design and supply the best possible product. |

| Product specification     | Production        | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                             |

[1] Please consult the most recently issued datasheet before initiating or completing a design.

#### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition - Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information - Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Philips

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

**Philips Semiconductors** 811 East Argues Avenue P.O. Box 3409 Sunnyvale, California 94088-3409 Telephone 800-234-7381

© Copyright Philips Electronics North America Corporation 2000 All rights reserved. Printed in U.S.A.

> Date of release: 05-00 9397-750-07139

Document order number:

Let's make things better.

PHILIPS