### INTEGRATED CIRCUITS

# DATA SHEET

# **PCK2001R**

14.318 – 133 MHz I<sup>2</sup>C 1:6 clock buffer

**Product specification**

### 14.318 - 133 MHz I<sup>2</sup>C 1:6 clock buffer

### **PCK2001R**

#### **FEATURES**

- Typically used to support four registered SDRAM DIMMs

- 16-pin SSOP package

- See PCK2001 for 48-pin 1:18 buffer part

- See PCK2001M for 28-pin 1:10 buffer part

- Optimized for 33 MHz, 66 MHz, 100 MHz and 133 MHz operation

- Part-to-part skew < 500 ps

- 175 ps skew outputs typical

- Individual SDRAM clock output enable/disable via I<sup>2</sup>C

- Multiple V<sub>DD</sub>, V<sub>SS</sub> pins for noise reduction

- 3.3 V operation

- ESD protection exceeds 2000 V per Standard 801.2

### **DESCRIPTION**

The PCK2001R is a 1–6 fanout buffer used for 133/100 MHz CPU, 66/33 MHz PCI, 14.318 MHz REF, or 133/100/66 MHz SDRAM clock distribution. 6 outputs are typically used to support up to 4 registered SDRAM DIMMs commonly found in server applications.

### **QUICK REFERENCE DATA**

| SYMBOL                               | PARAMETER                                        | CONDITIONS                          | TYPICAL    | UNIT |

|--------------------------------------|--------------------------------------------------|-------------------------------------|------------|------|

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay BUF_IN to BUF_OUT <sub>n</sub> | V <sub>CC</sub> = 3.3 V, CL = 30 pF | 2.5<br>2.5 | ns   |

| t <sub>r</sub>                       | Rise time                                        | V <sub>CC</sub> = 3.3 V, CL = 30 pF | 1.0        | ns   |

| t <sub>f</sub>                       | Fall time                                        | V <sub>CC</sub> = 3.3 V, CL = 20 pF | 700        | ps   |

| I <sub>CC</sub>                      | Total supply current                             | V <sub>CC</sub> = 3.465 V           | 50         | μΑ   |

#### ORDERING INFORMATION

|   | PACKAGES            | TEMPERATURE RANGE | ORDER CODE | DRAWING NUMBER |  |

|---|---------------------|-------------------|------------|----------------|--|

| - | 16-Pin Plastic SSOP | 0°C to +70°C      | PCK2001RDB | SOT369-1       |  |

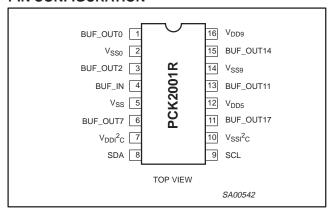

### **PIN CONFIGURATION**

Intel and Pentium are registered trademarks of Intel Corporation.  $I^2C$  is a trademark of Philips Semiconductors Corporation.

### **PIN DESCRIPTION**

| PIN<br>NUMBER | I/O<br>TYPE | SYMBOL                          | FUNCTION                            |

|---------------|-------------|---------------------------------|-------------------------------------|

| 1, 3          | Output      | BUF_OUT<br>(0, 2)               | Buffered clock outputs              |

| 13, 15        | Output      | BUF_OUT<br>(11, 14)             | Buffered clock outputs              |

| 6, 11         | Output      | BUF_OUT<br>(7, 17)              | Buffered clock outputs              |

| 4             | Input       | BUF_IN                          | Buffered clock input                |

| 8             | I/O         | SDA                             | I <sup>2</sup> C serial data        |

| 9             | Input       | SCL                             | I <sup>2</sup> C serial clock       |

| 12, 16        | Input       | V <sub>DD</sub><br>(5, 9)       | 3.3 V power supply                  |

| 2, 14         | Input       | V <sub>SS</sub> (0, 9)          | Ground                              |

| 7             | Input       | V <sub>DDI</sub> <sup>2</sup> C | 3.3 V I <sup>2</sup> C power supply |

| 10            | Input       | V <sub>SSI</sub> <sup>2</sup> C | I <sup>2</sup> C ground             |

### 14.318 - 133 MHz I<sup>2</sup>C 1:6 clock buffer

PCK2001R

### **FUNCTION TABLE**

| BUF_IN | I <sup>2</sup> CEN | BUF_OUTn |

|--------|--------------------|----------|

| L      | X                  | L        |

| Н      | Н                  | Н        |

| Н      | L                  | L        |

### **ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>**

In accordance with the Absolute Maximum Rating System (IEC 134). Voltages are referenced to  $V_{SS}$  ( $V_{SS}$  = 0V).

| SYMBOL           | DADAMETED                                                     | COMPITION                                                                   | T I  |                       |      |

|------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------|------|-----------------------|------|

|                  | PARAMETER                                                     | CONDITION                                                                   | MIN  | MAX                   | UNIT |

| $V_{DD}$         | DC 3.3V supply voltage                                        |                                                                             | -0.5 | +4.6                  | V    |

| I <sub>IK</sub>  | DC input diode current                                        | V <sub>1</sub> < 0                                                          |      | -50                   | mA   |

| VI               | DC input voltage                                              | Note 2                                                                      | -0.5 | 5.5                   | V    |

| lok              | DC output diode current                                       | $V_O > V_{DD}$ or $V_O < 0$                                                 |      | ±50                   | mA   |

| Vo               | DC output voltage                                             | Note 2                                                                      | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Io               | DC output source or sink current                              | $V_O \ge 0$ to $V_{DD}$                                                     |      | ±50                   | mA   |

| T <sub>stg</sub> | Storage temperature range                                     |                                                                             | -65  | +150                  | °C   |

| P <sub>TOT</sub> | Power dissipation per package plastic medium-shrink SO (SSOP) | For temperature range: 0 to +70°C above +55°C derate linearly with 11.3mW/K |      | 850                   | mW   |

### NOTES:

### **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL           | PARAMETER                                       | CONDITIONS | LIM   | UNIT     |      |

|------------------|-------------------------------------------------|------------|-------|----------|------|

| STWBOL           | PARAMETER                                       | CONDITIONS | MIN   | MAX      | UNII |

| $V_{DD}$         | DC 3.3V supply voltage                          |            | 3.135 | 3.465    | V    |

| C <sub>L</sub>   | Capacitive load                                 |            | 20    | 30       | pF   |

| V <sub>I</sub>   | DC input voltage range                          |            | 0     | $V_{DD}$ | V    |

| Vo               | DC output voltage range                         |            | 0     | $V_{DD}$ | V    |

| T <sub>amb</sub> | Operating ambient temperature range in free air |            | 0     | +70      | °C   |

<sup>1.</sup> Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2.</sup> The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

# 14.318 – 133 MHz I<sup>2</sup>C 1:6 clock buffer

### PCK2001R

### **DC CHARACTERISTICS**

|                 | SYMBOL PARAMETER         |                     | TEST CONDITIONS         |                    |                       | LIMITS                          |    |  |

|-----------------|--------------------------|---------------------|-------------------------|--------------------|-----------------------|---------------------------------|----|--|

| SYMBOL          |                          |                     |                         |                    |                       | T <sub>amb</sub> = 0°C to +70°C |    |  |

|                 |                          | V <sub>DD</sub> (V) | OTHER                   |                    | MIN                   | MAX                             |    |  |

| V <sub>IH</sub> | HIGH level input voltage | 3.135 to 3.465      |                         |                    | 2.0                   | V <sub>DD</sub> + 0.3           | V  |  |

| V <sub>IL</sub> | LOW level input voltage  | 3.135 to 3.465      |                         |                    | V <sub>SS</sub> - 0.3 | 0.8                             | V  |  |

| V <sub>OH</sub> | 3.3V output HIGH voltage | 3.135 to 3.465      | $I_{OH} = -1mA$         |                    | 3.1                   | -                               | V  |  |

| V <sub>OL</sub> | 3.3V output LOW voltage  | 3.135 to 3.465      | I <sub>OL</sub> = 1mA   |                    | -                     | 50                              | mV |  |

| I <sub>OH</sub> | Output HIGH current      | 3.135 to 3.465      | V <sub>OUT</sub> = 1.5V |                    | -70                   | -185                            | mA |  |

| I <sub>OL</sub> | Output LOW current       | 3.135 to 3.465      | V <sub>OUT</sub> = 1.5V |                    | 65                    | 160                             | mA |  |

| ±l <sub>1</sub> | Input leakage current    | 3.465               |                         |                    | <b>-</b> 5            | 5                               | μΑ |  |

| Icc             | Quiescent supply current | 3.465               | $V_I = V_{DD}$ or GND   | I <sub>O</sub> = 0 | -                     | 100                             | μА |  |

### 14.318 - 133 MHz I<sup>2</sup>C 1:6 clock buffer

PCK2001R

#### **AC CHARACTERISTICS**

| SYMBOL              | PARAMETER                   | TEST CONDITI     | TEST CONDITIONS |      | LIMITS<br>T <sub>amb</sub> = 0°C to +70°C |      |      |  |

|---------------------|-----------------------------|------------------|-----------------|------|-------------------------------------------|------|------|--|

|                     |                             |                  | NOTES           | MIN  | TYP <sup>9</sup>                          | MAX  | 1    |  |

| T <sub>P</sub>      | CLK period                  |                  | 1, 6            | 29.9 | 30.0                                      | 30.2 |      |  |

| T <sub>H</sub>      | CLK HIGH time               | 33MHz            | 2, 6, 8         | 12.3 | 14.3                                      | 16.3 | ns   |  |

| TL                  | CLK LOW time                | 7                | 3, 6, 8         | 12.1 | 14.1                                      | 16.1 | 1    |  |

| T <sub>P</sub>      | CLK period                  |                  | 1, 6            | 14.9 | 15.0                                      | 15.2 |      |  |

| T <sub>H</sub>      | CLK HIGH time               | 66MHz            | 2, 6, 8         | 5.6  | 6.8                                       | 8.0  | ns   |  |

| T <sub>L</sub>      | CLK LOW time                | 7                | 3, 6, 8         | 5.3  | 6.5                                       | 7.7  | 1    |  |

| T <sub>P</sub>      | CLK period                  |                  | 1,6             | 9.9  | 10.01                                     | 10.2 |      |  |

| T <sub>H</sub>      | CLK HIGH time               | 100MHz           | 2, 6, 8         | 3.3  | 4.2                                       | 5.1  | ns   |  |

| T <sub>L</sub>      | CLK LOW time                | 7                | 3, 6, 8         | 3.2  | 4.1                                       | 5.0  | 1    |  |

| T <sub>P</sub>      | CLK period                  |                  | 1, 6            | 7.4  | 7.5                                       | 7.7  |      |  |

| T <sub>H</sub>      | CLK HIGH time               | 133MHz           | 2, 6, 8         | 2.6  | 3.1                                       | 3.6  | ns   |  |

| T <sub>L</sub>      | CLK LOW time                | 7                | 3, 6, 8         | 2.2  | 2.7                                       | 3.2  | 1    |  |

| T <sub>SDRISE</sub> | Rise time                   |                  | 4, 6, 10        | 1.5  | 2.0                                       | 4.0  | V/ns |  |

| T <sub>SDFALL</sub> | Fall time                   |                  | 4, 6, 11        | 1.5  | 2.5                                       | 4.0  | V/ns |  |

| T <sub>PLH</sub>    | Buffer LH propagation delay |                  | 6, 7            | 1.0  | 2.4                                       | 3.5  | ns   |  |

| T <sub>PHL</sub>    | Buffer HL propagation delay |                  | 6, 7            | 1.0  | 2.6                                       | 3.5  | ns   |  |

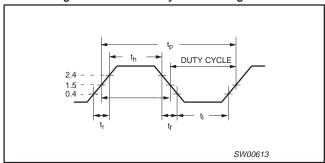

| DUTY CYCLE          | Output Duty Cycle           | Measured at 1.5V | 5, 6, 7         | 45   | 50                                        | 55   | %    |  |

| T <sub>SKW</sub>    | Bus CLK skew                |                  | 1, 6            |      | 150                                       | 250  | ps   |  |

| T <sub>DDSKW</sub>  | Device to device skew       |                  |                 |      |                                           | 500  | ps   |  |

#### NOTES:

- 1. Clock period and skew are measured on the rising edge at 1.5V.

- T<sub>H</sub> is measured at 2.4V as shown in Figure 2.

T<sub>L</sub> is measured at 0.4V as shown in Figure 2.

- T<sub>SDRISE</sub> and T<sub>SDFALL</sub> are measured as a transition through the threshold region V<sub>OL</sub> = 0.4V and V<sub>OH</sub> = 2.4V (1 mA) JEDEC specification.

Duty cycle should be tested with a 50/50% input.

Over MIN (20pF) to MAX (30pF) discrete load, process, voltage, and temperature.

- Input edge rate for these tests must be faster than 1 V/ns.

Calculated at minimum edge rate (1.5ns) to guarantee 45/55% duty cycle at 1.5V. Pulsewidth is required to be wider at the faster edge to ensure duty cycle specification is met.

- 9. All typical values are at  $V_{CC} = 3.3V$  and  $T_{amb} = 25^{\circ}C$ . 10. Typical is measured with MAX (30pF) discrete load.

- 11. Typical is measured with MIN (20pF) discrete load.

### 14.318 - 133 MHz I<sup>2</sup>C 1:6 clock buffer

PCK2001R

### I<sup>2</sup>C CONSIDERATIONS

I<sup>2</sup>C has been chosen as the serial bus interface to control the PCK2001R. I<sup>2</sup>C was chosen to support the JEDEC proposal JC-42.5 168 Pin Unbuffered SDRAM DIMM. All vendors are required to determine the legal issues associated with the manufacture of I<sup>2</sup>C devices.

1) Address assignment: The clock driver in this specification uses the single, 7-bit address shown below. All devices can use the address if only one master clock driver is used in a design. The address can be re-used for the CKBF device if no other conflicting I<sup>2</sup>C clock driver is used in the system.

The following address was confirmed by Philips on 09/04/96.

| A6 | A5 | A4 | А3 | A2 | A1 | A0 | $R/\overline{W}$ |

|----|----|----|----|----|----|----|------------------|

| 1  | 1  | 0  | 1  | 0  | 0  | 1  | 0                |

**NOTE:** The R/ $\overline{\mathbb{W}}$  bit is used by the I<sup>2</sup>C controller as a data direction bit. A 'zero' indicates a transmission (WRITE) to the clock device. A 'one' indicates a request for data (READ) from the clock driver. Since the definition of the clock buffer only allows the controller to WRITE data; the R/ $\overline{\mathbb{W}}$  bit of the address will always be seen as 'zero'. Optimal address decoding of this bit is left to the vendor.

- 2) Options: It is our understanding that metal mask options and other pinouts of this type of clock driver will be allowed to use the same address as the original CKBF device. I<sup>2</sup>C addresses are defined in terms of function (master clock driver) rather than form (pinout, and option).

- 3) Slave/Receiver: The clock driver is assumed to require only slave/receiver functionality. Slave/transmitter functionality is optional.

- 4) Data Transfer Rate: 100 kbits/s (standard mode) is the base functionality required. Fast mode (400 kbits/s) functionality is optional.

- 5) Logic Levels: I<sup>2</sup>C logic levels are based on a percentage of V<sub>DD</sub> for the controller and other devices on the bus. Assume all devices are based on a 3.3 Volt supply.

- 6) Data Byte Format: Byte format is 8 Bits as described in the following appendices.

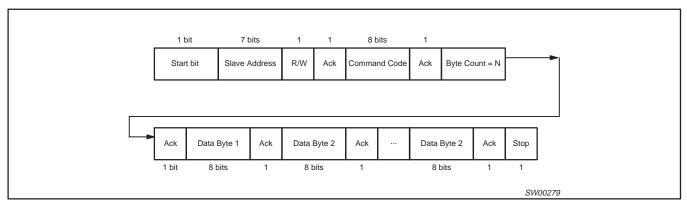

- 7) Data Protocol: To simplify the clock I<sup>2</sup>C interface, the clock driver serial protocol was specified to use only block writes from the controller. The bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte has been transferred. Indexed bytes are not allowed. However, the SMBus controller has a more specific format than the generic I<sup>2</sup>C protocol.

The clock driver must meet this protocol which is more rigorous than previously stated I<sup>2</sup>C protocol. Treat the description from the viewpoint of controller. The controller "writes" to the clock driver and if possible would "read" from the clock driver (the clock driver is a slave/receiver only and is incapable of this transaction.)

"The block write begins with a slave address and a write condition. After the command code the host (controller) issues a byte count which describes how many more bytes will follow in the message. If the host had 20 bytes to send, the first byte would be the number 20 (14h), followed by the 20 bytes of data. The byte count may not be 0. A block write command is allowed to transfer a maximum of 32 data bytes."

NOTE: The acknowledgement bit is returned by the slave/receiver (the clock driver).

Consider the command code and the byte count bytes required as the first two bytes of any transfer. The command code is software programmable via the controller, but will be specified as 0000 0000 in the clock specification. The byte count byte is the number of additional bytes required to transfer, not counting the command code and byte count bytes. Additionally, the byte count byte is required to be a minimum of 1 byte and a maximum of 32 bytes to satisfy the above requirement.

### 14.318 - 133 MHz I<sup>2</sup>C 1:6 clock buffer

PCK2001R

#### For example:

| Byte cou | unt byte | Notes:                                                                       |  |  |  |

|----------|----------|------------------------------------------------------------------------------|--|--|--|

| MSB      | LSB      |                                                                              |  |  |  |

| 0000     | 0000     | Not allowed. Must have at least one byte.                                    |  |  |  |

| 0000     | 0001     | Data for functional and frequency select register (currently byte 0 in spec) |  |  |  |

| 0000     | 0010     | Reads first two bytes of data. (byte 0 then byte 1)                          |  |  |  |

| 0000     | 0011     | Reads first three bytes (byte 0, 1, 2 in order)                              |  |  |  |

| 0000     | 0100     | Reads first four bytes (byte 0, 1, 2, 3 in order)                            |  |  |  |

| 0000     | 0101     | Reads first five bytes (byte 0, 1, 2, 3, 4 in order)                         |  |  |  |

| 0000     | 0110     | Reads first six bytes (byte 0, 1, 2, 3, 4, 5 in order)                       |  |  |  |

| 0000     | 0111     | Reads first seven bytes (byte 0, 1, 2, 3, 4, 5, 6 in order)                  |  |  |  |

| 0010     | 0000     | Max byte count supported = 32                                                |  |  |  |

A transfer is considered valid after the acknowledge bit corresponding to the byte count is read by the controller. The serial controller interface can be simplified by discarding the information in both the command code and the byte count bytes and simply reading all the bytes that are sent to the clock driver after being addressed by the controller. It is expected that the controller will not provide more bytes than the clock driver can handle. A clock vendor may choose to discard any number of bytes that exceed the defined byte count.

- 8) Clock stretching: The clock device must not hold/stretch the SCLOCK or SDATA lines low for more than 10 ms. Clock stretching is discouraged and should only be used as a last resort. Stretching the clock/data lines for longer than this time puts the device in an error/time-out mode and may not be supported in all platforms. It is assumed that all data transfers can be completed as specified without the use of clock/data stretching.

- 9) General Call: It is assumed that the clock driver will not have to respond to the "general call."

- 10) Electrical Characteristics: All electrical characteristics must meet the standard mode specifications found in section 15 of the I<sup>2</sup>C specification.

- a) Pull-Up Resistors: Any internal resistors pull-ups on the SDATA and SCLOCK inputs must be stated in the individual datasheet. The use of internal pull-ups on these pins of below 100 k $\Omega$  is discouraged. Assume that the board designer will use a single external pull-up resistor for each line and that these values are in the 5–6 k $\Omega$  range. Assume one I<sup>2</sup>C device per DIMM (serial presence detect), one I<sup>2</sup>C controller, one clock driver plus one/two more I<sup>2</sup>C devices on the platform for capacitive loading purposes.

- (b) Input Glitch Filters: Only fast mode I<sup>2</sup>C devices require input glitch filters to suppress bus noise. The clock driver is specified as a standard mode device and is not required to support this feature.

- 11) PWR DWN: If a clock driver is placed in PWR DWN mode, the SDATA and SCLK inputs must be 3-Stated and the device must retain all programming information. I<sub>DD</sub> current due to the I<sup>2</sup>C circuitry must be characterized and in the data sheet.

For specific I<sup>2</sup>C information consult the Philips I<sup>2</sup>C Peripherals Data Handbook IC12 (1997).

### 14.318 - 133 MHz I<sup>2</sup>C 1:6 clock buffer

PCK2001R

#### SERIAL CONFIGURATION MAP

The serial bits will be read by the clock buffer in the following order:

Byte 0 - Bits 7, 6, 5, 4, 3, 2, 1, 0

Byte 1 - Bits 7, 6, 5, 4, 3, 2, 1, 0

Byte 2 - Bits 7, 6, 5, 4, 3, 2, 1, 0

All unused register bits (Reserved and N/A) should be desined as "Don't Care". It is expected that the controller will force all of these bits to a "0" level.

All register bits labeled "Initialize to 0" must be written to zero during intialization. Failure to do so may result in a higher than normal operating current. The controller will read back the last written value.

### Byte 0: Active/inactive register

1 = enable; 0 = disable

| BIT | PIN# | NAME     | DESCRIPTION     |

|-----|------|----------|-----------------|

| 7   | 6    | BUF_OUT7 | Active/Inactive |

| 6   | _    |          | _               |

| 5   | _    |          | _               |

| 4   | _    |          | _               |

| 3   | _    | _        | _               |

| 2   | 3    | BUF_OUT2 | Active/Inactive |

| 1   | _    |          | _               |

| 0   | 1    | BUF_OUT0 | Active/Inactive |

#### NOTE:

### Byte 1: Active/inactive register

1 = enable; 0 = disable

| BIT | PIN# | NAME      | DESCRIPTION     |

|-----|------|-----------|-----------------|

| 7   | _    |           |                 |

| 6   | 15   | BUF_OUT14 | Active/Inactive |

| 5   | _    | _         | _               |

| 4   | _    | _         | _               |

| 3   | 13   | BUF_OUT11 | Active/Inactive |

| 2   | _    | _         |                 |

| 1   | _    | _         | -               |

| 0   | _    | _         | <del>-</del>    |

#### NOTE

### Byte 2: Active/inactive register

| BIT | PIN# | NAME      | DESCRIPTION     |

|-----|------|-----------|-----------------|

| 7   | 11   | BUF_OUT17 | Active/Inactive |

| 6   | _    | _         | _               |

| 5   | _    | _         | _               |

| 4   | _    | _         | _               |

| 3   | _    | _         | _               |

| 2   | _    | _         | _               |

| 1   | _    | _         | _               |

| 0   | _    | _         | _               |

### NOTE:

<sup>1.</sup> Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be configured at power-on and are not expected to be configured during the normal modes of operation.

Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be configured at power-on and are not expected to be configured during the normal modes of operation.

<sup>1.</sup> Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be configured at power-on and are not expected to be configured during the normal modes of operation.

### 14.318 - 133 MHz I<sup>2</sup>C 1:6 clock buffer

PCK2001R

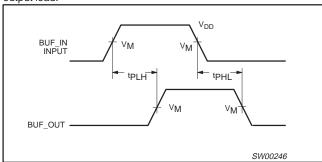

### **AC WAVEFORMS**

$\begin{array}{l} V_M = 1.5 \ V \\ V_X = V_{OL} + 0.3 \ V \\ V_Y = V_{OH} - 0.3 \ V \\ V_{OL} \ and \ V_{OH} \ are the typical output voltage drop that occur with the output load. \end{array}$

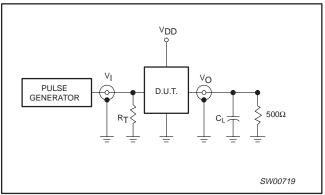

Figure 1. Load circuitry for switching times.

Figure 2. Buffer Output clock

### **TEST CIRCUIT**

Figure 3. Load circuitry for switching times

# 14.318 – 133 MHz I<sup>2</sup>C 1:6 clock buffer

PCK2001R

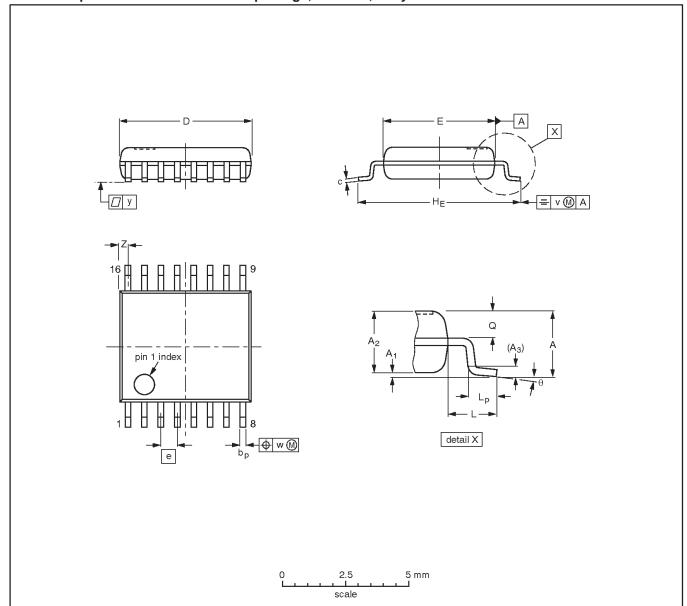

### SSOP16: plastic shrink small outline package; 16 leads; body width 4.4 mm

SOT369-1

### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | HE         | L   | Lp           | Q            | v   | w    | у   | z <sup>(1)</sup> | θ         |

|------|-----------|----------------|----------------|------|--------------|--------------|------------------|------------------|------|------------|-----|--------------|--------------|-----|------|-----|------------------|-----------|

| mm   | 1.5       | 0.15<br>0.00   | 1.4<br>1.2     | 0.25 | 0.32<br>0.20 | 0.25<br>0.13 | 5.30<br>5.10     | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.45 | 0.65<br>0.45 | 0.2 | 0.13 | 0.1 | 0.48<br>0.18     | 10°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.20 mm maximum per side are not included.

| OUTLINE  |     | REFER  | EUROPEAN | ISSUE DATE |            |                                  |

|----------|-----|--------|----------|------------|------------|----------------------------------|

| VERSION  | IEC | JEDEC  | EIAJ     |            | PROJECTION | ISSUE DATE                       |

| SOT369-1 |     | MO-152 |          |            |            | <del>-95-02-04</del><br>99-12-27 |

$14.318 - 133 \text{ MHz } I^2\text{C} 1:6 \text{ clock buffer}$

PCK2001R

**NOTES**

## 14.318 - 133 MHz I<sup>2</sup>C 1:6 clock buffer

PCK2001R

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                             |

|---------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                          |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 2000 All rights reserved. Printed in U.S.A.

Date of release: 07-00

Document order number: 9397 750 07352

Let's make things better.

Philips Semiconductors