Gerstweg 2, 6534 AE Nijmegen The Netherlands

Report no.

: RNR-T45-95-B-341.

Author

: H Mollee.

Date

: 22 - 5 - 1995

Department

: P.G. Transistors & Diodes Development

# Preamplifier for pager applications.

#### Abstract:

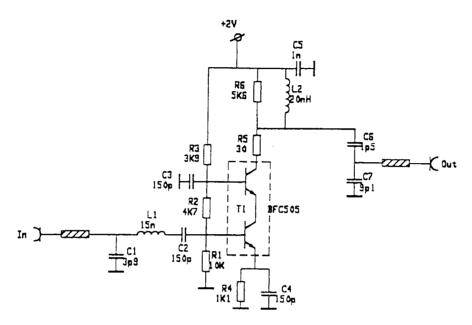

In this report a description is given of a preamplifier for pager applications based upon the BFC505 transistor. This transistor consists of two BFR505 crystals connected in cascade. This preamplifier or cascode features a high gain at a low supply voltage and low supply current. A detailed circuit description, lay-out and a (typical) specification are given.

2

Gerstweg 2, 6534 AE Nijmegen The Netherlands

#### 1 Introduction.

In this report the design of a preamplifier (cascode) for pager applications is described. This preamplifier consists of two BFR505 crystals in a SOT353 encapsulation. This preamplifier has the following features:

- low supply voltage (2 V).

- low power consumption ( ≤ 0.5 mA).

- high gain.

- small size.

In this design we use a BFC505 because this, together with the use of 0402-components, enables us to use a minimum of space on the PCB.

The amplifier has the following (typical) specification:

| Gain.                                               | $G_{P}$         | 15  | dB.  |

|-----------------------------------------------------|-----------------|-----|------|

| Bandwidth                                           | В               | 25  | MHz. |

| return loss at input                                | S <sub>11</sub> | -12 | dB.  |

| return loss at output                               | s <sub>22</sub> | -12 | dB.  |

| 3 <sup>rd</sup> -order intercept point <sup>1</sup> | IP <sub>3</sub> | -14 | dBm. |

| 1 dB compression point <sup>1</sup>                 | P.,             | -24 | dBm. |

| Noise figure                                        | NF              | 3.0 | dB.  |

<sup>1</sup> reffered to output.

Gerstweg 2, 6534 AE Nijmegen The Netherlands

#### 2 Designing the circuit.

Due to the low supply voltage of 2 V it is very difficult to achieve thermal stability. In general, thermal stability is achieved by an emitter-resistor. If the temperature rises, the collector current will increase. As the base-voltage is constant, this means that the baseemitter voltage drops, which means that the collector current drops and stability is achieved. In our case thermal stability is also achieved by an emitter-resistor, but the voltage drop may not be too large because of the low supply voltage. In our case this voltage drop is about 0.3 V. Both in- and output are matched to 50  $\Omega$  by means of passive components. Under normal conditions the input will not necessarily be matched to 50  $\Omega$  but to optimized for a loop antenna. However, for evaluation purposes this is unpractical. With the bias-circuit the collector current is set to ≈0.3 mA. This is done by a ladder-network of three resistors with each node connected to the base of a transistor and a resistor in the emitter. This emitter-resistor is decoupled for AC. The input is matched to 50  $\Omega$  by an inductor of 15 nH and a capacitor of 3.9 pF. To achieve sufficient gain we transform the 50  $\Omega$  load to a higher impedance. This is done by the two capacitors of 9.1 pF and 1.5 pF. Together with an inductor of ≈ 20 nH ( 2.5 turns, Ø 0.5 mm, d = 2 mm) these capacitors form a resonant circuit tuned to 900 MHz. Tuning the circuit to exactly 900 MHz must be done by bending the inductor. The 30  $\Omega$  resistor is used to ensure unconditional AC-stability.

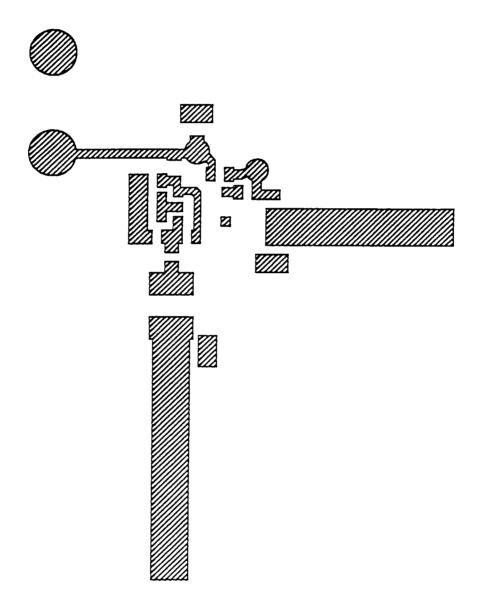

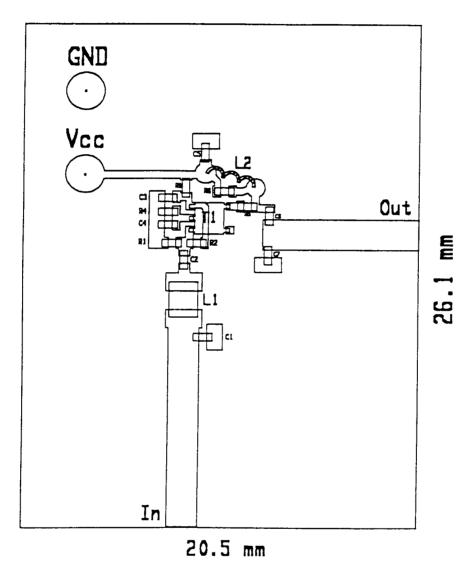

The schematic diagram of the cascode can be seen in figure 1. For this circuit a lay-out has been designed which can be found in figure 2 and 3.

# **PHILIPS**

# Philips Semiconductors

Gerstweg 2, 6534 AE Nijmegen The Netherlands

fig. 1: Schematic diagram of cascode circuit.

Gerstweg 2, 6534 AE Nijmegen The Netherlands

fig. 2: Lay-out of cascode circuit.

# **PHILIPS**

# **Philips Semiconductors**

Gerstweg 2, 6534 AE Nijmegen The Netherlands

fig. 3: Component lay-out cascode.