# Low Voltage 1:9 Clock Distribution Chip

The MPC947 is a 1:9 low voltage clock distribution chip. The device features the capability to select between two LVTTL compatible inputs and fans the signal out to 9 LVCMOS or LVTTL compatible outputs. These 9 outputs were designed and optimized to drive  $50\Omega$  series terminated transmission lines. With output-to-output skews of 500ps, the MPC947 is ideal as a clock distribution chip for synchronous systems which need a tight level of skew at a relatively low cost. For a similar product targeted at a higher price/performance point, consult the MPC948 data sheet.

- Clock Distribution for PowerPC<sup>™</sup> 620 L2 Cache

- 2 Selectable LVCMOS/LVTTL Clock Inputs

- 500ps Maximum Output-to-Output Skew

- Drives Up to 18 Independent Clock Lines

- Maximum Output Frequency of 110MHz

- Synchronous Output Enable

- Tristatable Outputs

- 32-Lead TQFP Packaging

- 3.3V V<sub>CC</sub> Supply Voltage

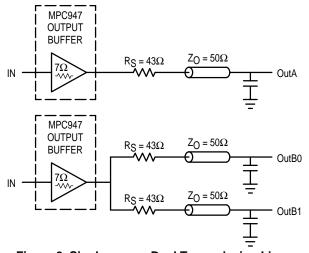

With an output impedance of approximately  $7\Omega$ , in both the HIGH and LOW logic states, the output buffers of the MPC947 are ideal for driving series terminated transmission lines. More specifically, each of the 9 MPC947 outputs can drive two series terminated  $50\Omega$  transmission lines. With this capability, the MPC947 has an effective fanout of 1:18 in applications using point—to—point distribution schemes. With this level of fanout, the MPC947 provides enough copies of low skew clocks for high performance synchronous systems, including use as a clock distribution chip for the L2 cache of a PowerPC 620 based system.

# **MPC947**

LOW VOLTAGE

1:9 CLOCK

DISTRIBUTION CHIP

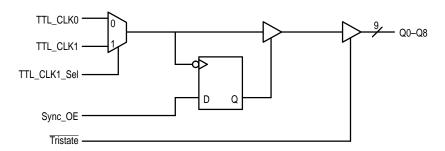

Two independent LVCMOS/LVTTL compatible clock inputs are available. Designers can take advantage of this feature to provide redundant clock sources or the addition of a test clock into the system design. With the select input pulled HIGH, the TTL\_CLK1 input will be selected.

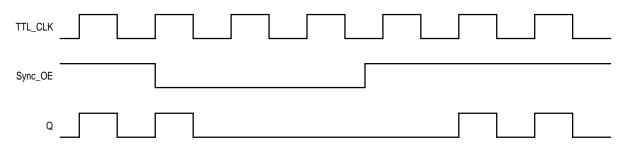

All of the control inputs are LVCMOS/LVTTL compatible. The MPC947 provides a synchronous output enable control to allow for starting and stopping of the output clocks. A logic high on the Sync\_OE pin will enable all of the outputs. Because this control is synchronized to the input clock, potential output glitching or runt pulse generation is eliminated. In addition, for board level test, the outputs can be tristated via the tristate control pin. A logic LOW applied to the Tristate input will force all of the outputs into high impedance. Note that all of the MPC947 inputs have internal pullup resistors.

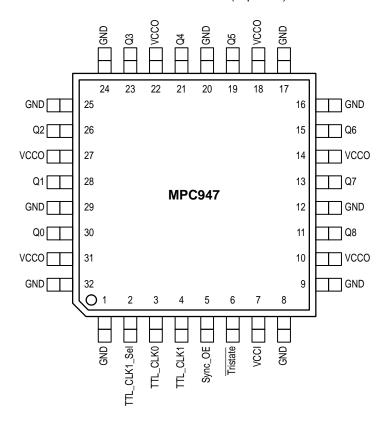

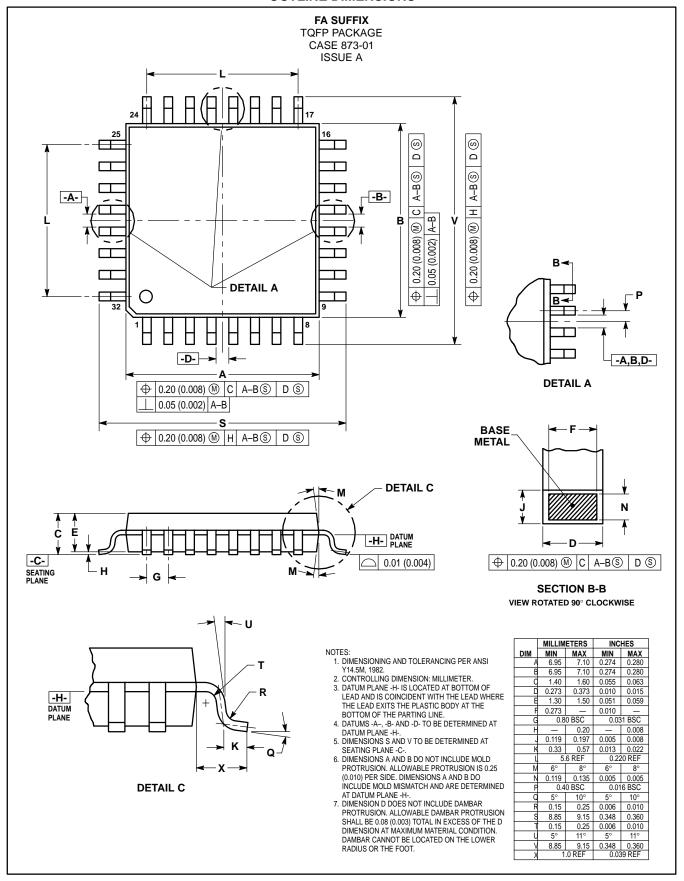

The MPC947 is fully 3.3V compatible. The 32-lead TQFP package was chosen to optimize performance, board space and cost of the device. The 32-lead TQFP has a 7x7mm body size with a conservative 0.8mm pin spacing.

PowerPC is a trademark of International Business Machines Corporation.

## **LOGIC DIAGRAM**

Pinout: 32-Lead TQFP (Top View)

## **FUNCTION TABLES**

| TTL_CLK1_Sel | Input    |  |  |  |

|--------------|----------|--|--|--|

| 0            | TTL_CLK0 |  |  |  |

| 1            | TTL_CLK1 |  |  |  |

| Sync_OE      | Outputs  |  |  |  |

| 0            | Disabled |  |  |  |

| 1            | Enabled  |  |  |  |

| Tristate     | Outputs  |  |  |  |

| 0            | Tristate |  |  |  |

| 1            | Enabled  |  |  |  |

Figure 1. Sync\_OE Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS\***

| Symbol            | Parameter                   | Min  | Max                   | Unit |

|-------------------|-----------------------------|------|-----------------------|------|

| Vcc               | Supply Voltage              | -0.3 | 4.6                   | V    |

| VI                | Input Voltage               | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IN</sub>   | Input Current (CMOS Inputs) | TBD  | TBD                   | mA   |

| T <sub>Stor</sub> | Storage Temperature Range   | -40  | 125                   | °C   |

Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute-maximum-rated conditions is not implied.

## DC CHARACTERISTICS (T<sub>A</sub> = $0^{\circ}$ to $70^{\circ}$ C, $V_{CC}$ = $3.3V \pm 0.3V$ )

| Symbol          | Characteristic                   | Min | Тур | Max  | Unit | Condition                            |

|-----------------|----------------------------------|-----|-----|------|------|--------------------------------------|

| VIH             | Input HIGH Voltage               | 2.0 |     | 3.6  | V    |                                      |

| V <sub>IL</sub> | Input LOW Voltage                |     |     | 0.8  | V    |                                      |

| Vон             | Output HIGH Voltage              | 2.5 |     |      | V    | I <sub>OH</sub> = -20mA <sup>1</sup> |

| V <sub>OL</sub> | Output LOW Voltage               |     |     | 0.4  | V    | I <sub>OL</sub> = 20mA <sup>1</sup>  |

| I <sub>IN</sub> | Input Current                    |     |     | -100 | μΑ   | Note 2                               |

| ICC             | Maximum Quiescent Supply Current |     | 21  | 28   | mA   |                                      |

| C <sub>IN</sub> | Input Capacitance                |     |     | 4    | pF   |                                      |

| C <sub>pd</sub> | Power Dissipation Capacitance    |     |     | TBD  | pF   |                                      |

<sup>1</sup> The MPC947 outputs can drive series or parallel terminated  $50\Omega$  (or  $50\Omega$  to  $V_{CC}/2$ ) transmission lines on the incident edge (see Applications Info section).

## AC CHARACTERISTICS ( $T_A = 0^{\circ}$ to $70^{\circ}$ C, $V_{CC} = 3.3 \text{V} \pm 0.3 \text{V}$ )

| Symbol                          | Characteristic               | Min              | Тур | Max              | Unit | Condition                                 |

|---------------------------------|------------------------------|------------------|-----|------------------|------|-------------------------------------------|

| F <sub>max</sub>                | Maximum Input Frequency      | 110              |     |                  | MHz  | Note 1                                    |

| <sup>t</sup> pd                 | Propagation Delay TCLK t     | to Q 7.5         |     | 12               | ns   | Note 1                                    |

| tsk(o)                          | Output-to-Output Skew        |                  |     | 500              | ps   | Note 1                                    |

| <sup>t</sup> sk(pr)             | Part-to-Part Skew            |                  |     | 2.0              | ns   | Note 2                                    |

| <sup>t</sup> pwo                | Output Pulse Width           | tCYCLE/2-<br>800 |     | tCYCLE/2+<br>800 | ps   | Note 1,<br>Measured at V <sub>CC</sub> /2 |

| t <sub>S</sub>                  | Setup Time Sync_OE to Input  | Clk 0.0          |     |                  | ns   | Note 3                                    |

| t <sub>h</sub>                  | Hold Time Input Clk to Sync_ | _OE 1.0          |     |                  | ns   | Note 3                                    |

| tPZL, tPZH                      | Output Enable Time           |                  |     | 11               | ns   |                                           |

| tPLZ, tPHZ                      | Output Disable Time          |                  |     | 11               | ns   |                                           |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time        | 0.2              |     | 1.0              | ns   | 0.8V to 2.0V                              |

<sup>1.</sup> Driving  $50\Omega$  transmission lines.

<sup>2</sup> I<sub>IN</sub> current is a result of internal pull-up resistors.

<sup>2.</sup> Part-to-part skew at a given temperature and voltage.

<sup>3.</sup> Setup and Hold times are relative to the falling edge of the input clock.

## **APPLICATIONS INFORMATION**

## **Driving Transmission Lines**

The MPC947 clock driver was designed to drive high speed signals in a terminated transmission line environment. To provide the optimum flexibility to the user the output drivers were designed to exhibit the lowest impedance possible. With an output impedance of less than  $10\Omega$  the drivers can drive either parallel or series terminated transmission lines. For more information on transmission lines the reader is referred to application note AN1091 in the Timing Solutions brochure (BR1333/D).

In most high performance clock networks point—to—point distribution of signals is the method of choice. In a point—to—point scheme either series terminated or parallel terminated transmission lines can be used. The parallel technique terminates the signal at the end of the line with a  $50\Omega$  resistance to VCC/2. This technique draws a fairly high level of DC current and thus only a single terminated line can be driven by each output of the MPC947 clock driver. For the series terminated case however there is no DC current draw, thus the outputs can drive multiple series terminated lines. Figure 2 illustrates an output driving a single series terminated line vs two series terminated lines in parallel. When taken to its extreme the fanout of the MPC947 clock driver is effectively doubled due to its capability to drive multiple lines.

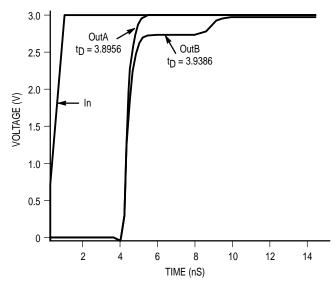

Figure 2. Single versus Dual Transmission Lines

The waveform plots of Figure 3 show the simulation results of an output driving a single line vs two lines. In both cases the drive capability of the MPC947 output buffers is more than sufficient to drive  $50\Omega$  transmission lines on the incident edge. Note from the delay measurements in the simulations a delta of only 43ps exists between the two differently loaded outputs. This suggests that the dual line driving need not be used exclusively to maintain the tight output—to—output skew of the MPC947. The output waveform in Figure 3 shows a step in the waveform, this step is caused by the impedance mismatch seen looking into the driver. The parallel combination of the  $43\Omega$  series resistor plus the output impedance does not match the parallel combination of the

line impedances. The voltage wave launched down the two lines will equal:

$$VL = VS (Zo / Rs + Ro + Zo) = 3.0 (25/53.5) = 1.40V$$

At the load end the voltage will double, due to the near unity reflection coefficient, to 2.8V. It will then increment towards the quiescent 3.0V in steps separated by one round trip delay (in this case 4.0ns).

Figure 3. Single versus Dual Waveforms

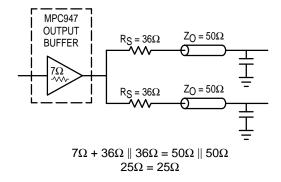

Since this step is well above the threshold region it will not cause any false clock triggering, however designers may be uncomfortable with unwanted reflections on the line. To better match the impedances when driving multiple lines the situation in Figure 4 should be used. In this case the series terminating resistors are reduced such that when the parallel combination is added to the output buffer impedance the line impedance is perfectly matched.

Figure 4. Optimized Dual Line Termination

SPICE level output buffer models are available for engineers who want to simulate their specific interconnect schemes. In addition IV characteristics are in the process of being generated to support the other board level simulators in general use.

## **OUTLINE DIMENSIONS**

### **MPC947**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and

#### Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan.

ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.