# Universal Cordless Telephone Subsystem IC

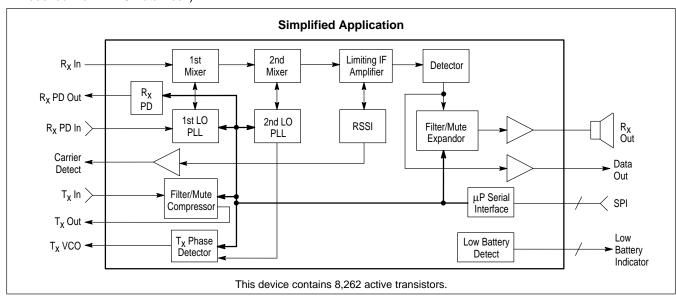

The MC13111 integrates several of the functions required for a cordless telephone into a single integrated circuit. This significantly reduces component count, board space requirements, external adjustments, and lowers overall costs. It is designed for use in both the handset and the base.

- Dual Conversion FM Receiver

- Complete Dual Conversion Receiver Antenna In to Audio Out 80 MHz Maximum Carrier Frequency

- RSSI Output

- Carrier Detect Output with Programmable Threshold

- Comparator for Data Recovery

- Operates with Either a Quad Coil or Ceramic Discriminator

- Compander

- Expandor Includes Mute, Digital Volume Control, Speaker Driver,

3.5 kHz Low Pass Filter, and Programmable Gain Block

- Compressor Includes Mute, 3.5 kHz Low Pass Filter, Limiter, and Programmable Gain Block

- Dual Universal Programmable PLL

- Supports New 25 Channel U.S. Standard with No External Switches

- Universal Design for Domestic and Foreign CT–1 Standards

- Digitally Controlled Via a Serial Interface Port

- Receive Side Includes 1st LO VCO, Phase Detector, and 14–Bit Programmable Counter and 2nd LO with 12–Bit Counter

- Transmit Section Contains Phase Detector and 14-Bit Counter

- MPU Clock Outputs Eliminates Need for MPU Crystal

- Supply Voltage Monitor

- Provides Two Levels of Monitoring with Separate Outputs

- Separate, Adjustable Trip Points

- Programmable Corner Frequency Selection

- MC13111 is Pin-for-Pin Compatible with MC13110

- 2.7 to 5.5 V Operation with One–Third the Power Consumption of Competing Devices

- AN1575: Refer to this Application Note for a List of the "Worldwide Cordless Telephone Frequencies" (List can also be found in Chapter 8 Addendum of DL128 Data Book)

# MC13111

# UNIVERSAL CT-1 SUBSYSTEM INTEGRATED CIRCUIT

SEMICONDUCTOR TECHNICAL DATA

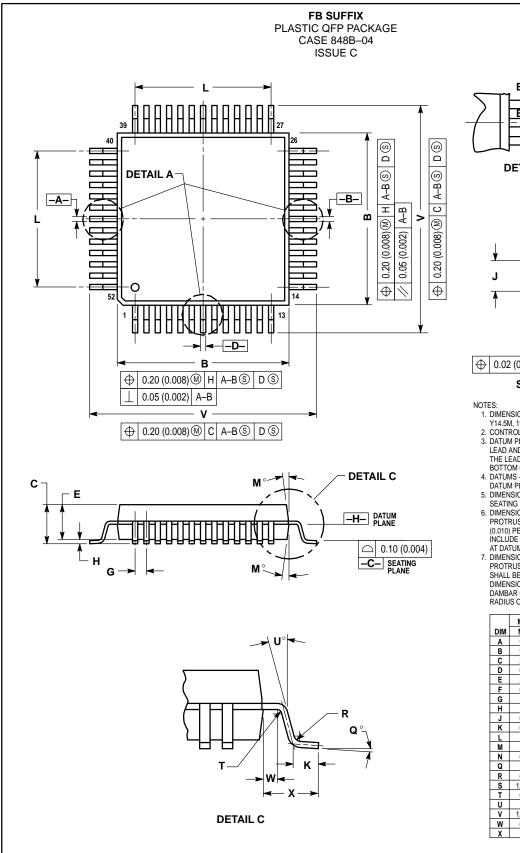

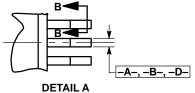

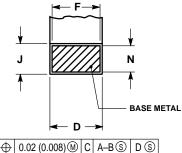

FB SUFFIX

PLASTIC QFP PACKAGE

CASE 848B

#### **ORDERING INFORMATION**

| Device    | Tested Operating<br>Temperature Range               | Package |

|-----------|-----------------------------------------------------|---------|

| MC13111FB | $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$ | QFP-52  |

#### **MAXIMUM RATINGS**

| Characteristic       | Symbol | Value        | Unit |

|----------------------|--------|--------------|------|

| Power Supply Voltage | VCC    | -0.5 to +6.0 | Vdc  |

| Junction Temperature | TJ     | -65 to +150  | °C   |

**NOTES:** 1. Devices should not be operated at these limits. The "Recommended Operating Conditions" provide for actual device operation.

#### **RECOMMENDED OPERATING CONDITIONS**

| Characteristic                                                 | Symbol          | Min      | Тур | Max       | Unit |

|----------------------------------------------------------------|-----------------|----------|-----|-----------|------|

| Supply Voltage                                                 | VCC             | 2.7      | 3.6 | 5.5       | Vdc  |

| Operating Ambient Temperature                                  | TA              | -40      | _   | 85        | °C   |

| Input Voltage Low (Data, Clk, EN)                              | V <sub>IL</sub> | I        | -   | 0.3       | V    |

| Input Voltage High (Data, Clk, EN)                             | VIH             | 2.5      | _   | _         | V    |

| Output Current (R <sub>X</sub> PD, T <sub>X</sub> PD) High Low | I <sub>OH</sub> | -<br>0.7 |     | -0.7<br>- | mA   |

NOTE: All limits are not necessarily functional concurrently.

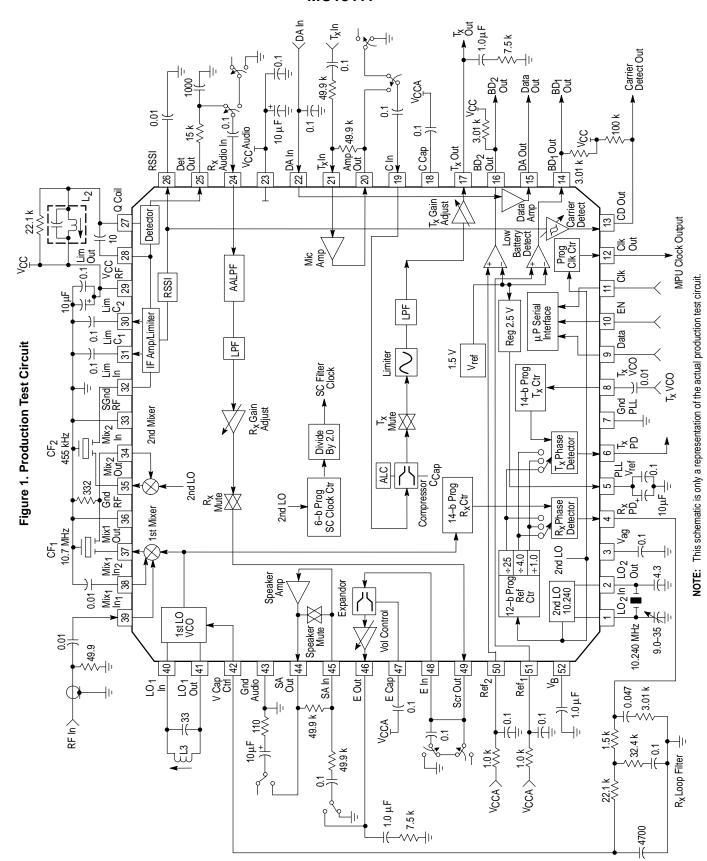

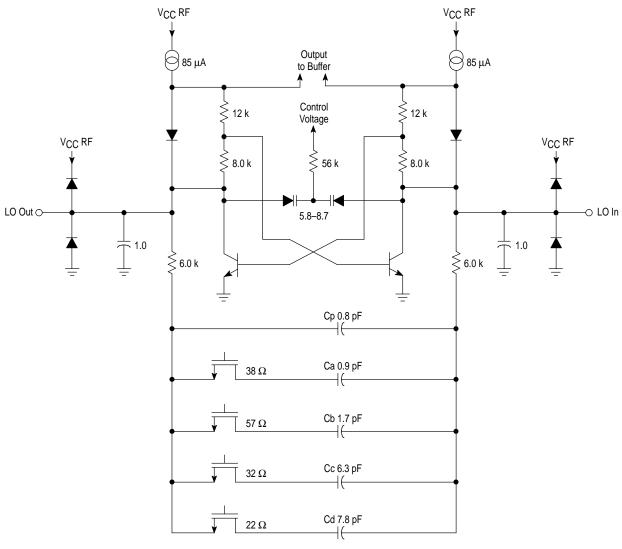

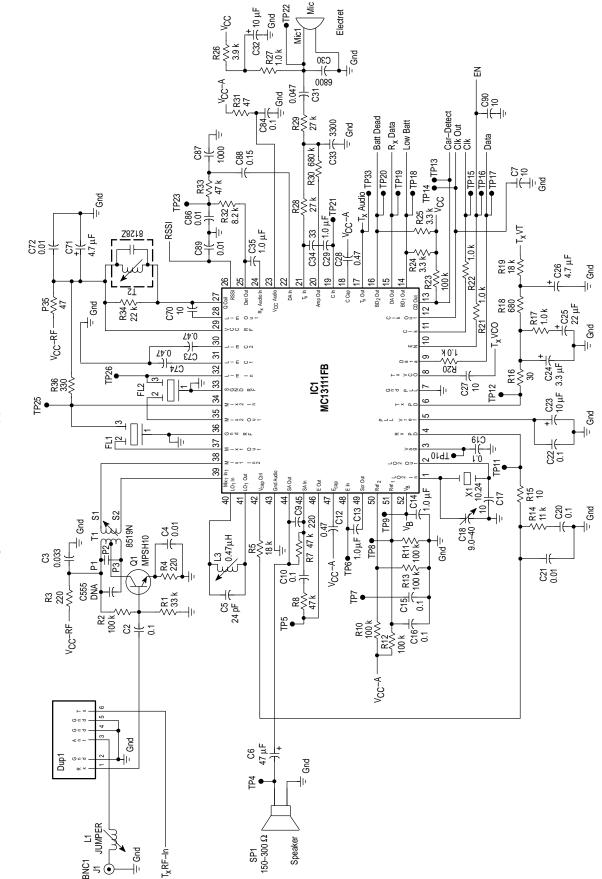

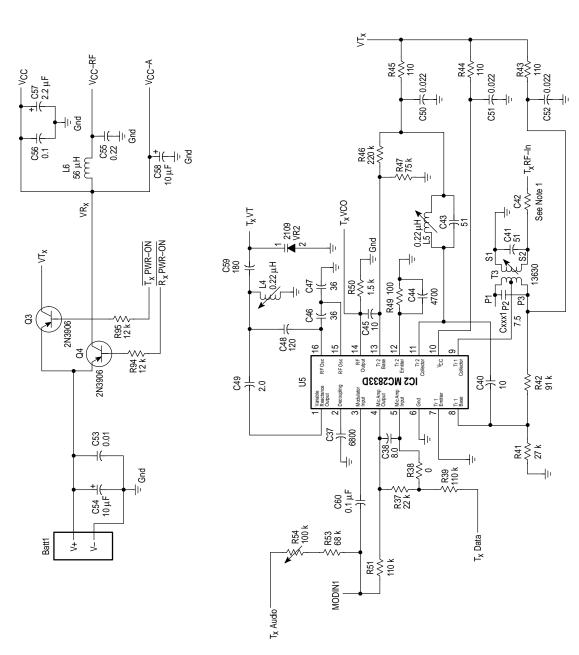

# **DC ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 3.6 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ , unless otherwise specified;

Test Circuit Figure 1.)

| Characteristic      | Symbol                         | Min | Тур | Max | Unit |

|---------------------|--------------------------------|-----|-----|-----|------|

| Static Current      |                                |     |     |     |      |

| Active Mode (2.7 V) | ACT I <sub>CC</sub>            | _   | 8.1 | -   | mA   |

| Active Mode         | ACT ICC                        | _   | 8.6 | 12  | mA   |

| Receive Mode        | R <sub>x</sub> I <sub>CC</sub> | _   | 4.3 | 5.3 | mA   |

| Standby Mode        | STD I <sub>CC</sub>            | _   | 270 | 500 | μΑ   |

| Inactive Mode       | INACT I <sub>CC</sub>          | I   | 35  | 80  | μΑ   |

# **ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 3.6 \text{ V}, V_B = 1.5 \text{ V}, T_A = 25^{\circ}\text{C}$ , Active or $R_X$ Mode, unless otherwise specified; Test Circuit Figure 1.)

| Test Circuit rigure 1.)                                          |                                                                   |                       |                                           |                          |     |      |     |      |  |

|------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------|-------------------------------------------|--------------------------|-----|------|-----|------|--|

| Characteristic Condition                                         |                                                                   | Input<br>Pin          | Measure<br>Pin                            | Symbol                   | Min | Тур  | Max | Unit |  |

| PLL VOLTAGE REGULATOR                                            |                                                                   |                       |                                           |                          |     |      |     |      |  |

| Regulated Output Level                                           | I <sub>L</sub> = 0 mA                                             | _                     | PLL V <sub>ref</sub>                      | ٧o                       | 2.4 | 2.5  | 2.6 | V    |  |

| Line Regulation                                                  | $I_L = 0 \text{ mA},$<br>$V_{CC} = 3.6 \text{ to } 5.5 \text{ V}$ | V <sub>CC</sub> Audio | PLL V <sub>ref</sub>                      | V <sub>Reg</sub><br>Line | -   | -0.6 | 20  | mV   |  |

| Load Regulation V <sub>CC</sub> = 3.6 V, I <sub>L</sub> = 1.0 mA |                                                                   | V <sub>CC</sub> Audio | PLL V <sub>ref</sub>                      | V <sub>Reg</sub><br>Load | _   | -1.1 | 20  | mV   |  |

| PLL LOOP CHARACTERIST                                            | rics                                                              |                       |                                           |                          |     |      |     |      |  |

| 2nd LO Frequency – (No Crystal)                                  |                                                                   | LO <sub>2</sub> In    | -                                         | f <sub>2ext</sub>        | _   | 12   | -   | MHz  |  |

| 2nd LO Frequency –<br>(With Crystal)                             |                                                                   | _                     | LO <sub>2</sub> In<br>LO <sub>2</sub> Out | f <sub>2ext</sub>        | -   | 12   | -   | MHz  |  |

| T <sub>X</sub> VCO (Input Frequency)                             | V <sub>in</sub> = 200 mVpp                                        | -                     | T <sub>X</sub> VCO                        | f <sub>txmax</sub>       | -   | 80   | -   | MHz  |  |

<sup>2.</sup> ESD data available upon request.

**ELECTRICAL CHARACTERISTICS** (continued) ( $V_{CC} = 3.6 \text{ V}$ ,  $V_B = 1.5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , Active or  $R_X$  Mode, unless otherwise specified; Test Circuit Figure 1.)

| Characteristic                          | Condition                                                           | Input<br>Pin                       | Measure<br>Pin                                    | Symbol                             | Min                            | Тур         | Max                            | Unit         |

|-----------------------------------------|---------------------------------------------------------------------|------------------------------------|---------------------------------------------------|------------------------------------|--------------------------------|-------------|--------------------------------|--------------|

| PLL PHASE DETECTOR                      |                                                                     |                                    |                                                   |                                    |                                |             |                                |              |

| Output Voltage Low                      | I <sub>I</sub> L = 0.7 mA                                           | _                                  | R <sub>X</sub> PD<br>T <sub>X</sub> PD            | VOL                                | _                              | -           | (PLL<br>V <sub>ref</sub> ) *.2 | V            |

| Output Voltage High                     | I <sub>IH</sub> = -0.7 mA                                           | _                                  | R <sub>X</sub> PD<br>T <sub>X</sub> PD            | VOL                                | (PLL<br>V <sub>ref</sub> ) *.8 | -           | _                              | V            |

| 3–State Leakage Current                 | V = 1.2 V                                                           | _                                  | R <sub>X</sub> PD<br>T <sub>X</sub> PD            | loz                                | -50                            | -           | 50                             | nA           |

| Output Capacitance                      | -                                                                   | _                                  | R <sub>X</sub> PD<br>T <sub>X</sub> PD            | C <sub>out</sub>                   | _                              | 8.0         | _                              | pF           |

| Output Rise and Fall Time               | C <sub>Load</sub> = 50 pF                                           | _                                  | R <sub>X</sub> PD<br>T <sub>X</sub> PD<br>Clk Out | t <sub>r</sub> , t <sub>f</sub>    | -                              | 250         | -                              | ns           |

| MICROPROCESSOR SERIA                    | L INTERFACE                                                         |                                    |                                                   |                                    |                                |             |                                |              |

| Input Current Low                       | V <sub>in</sub> = 0.3 V<br>Standby Mode                             | _                                  | Data,<br>Clk, EN                                  | IJĽ                                | -5.0                           | 0.3         | _                              | μΑ           |

| Input Current High                      | t Current High $V_{in} = 3.3 \text{ V}$<br>Standby Mode             |                                    | Data,<br>Clk, EN                                  | ΙΗ                                 | _                              | 1.5         | 5.0                            | μΑ           |

| Hysteresis Voltage                      | -                                                                   | -                                  | Data,<br>Clk, EN                                  | V <sub>hys</sub>                   | _                              | 1.0         | _                              | V            |

| Maximum Clock Frequency                 | -                                                                   | Data,<br>EN, Clk                   | -                                                 | -                                  | _                              | 2.0         | _                              | MHz          |

| Input Capacitance                       | -                                                                   | Data,<br>Clk, EN                   | -                                                 | C <sub>in</sub>                    | _                              | 8.0         | _                              | pF           |

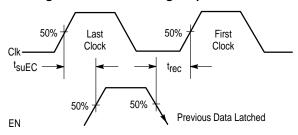

| EN to Clk Setup Time                    | =                                                                   | -                                  | EN, Clk                                           | tsuEC                              | -                              | 200         | -                              | ns           |

| Data to Clk Setup Time                  | =                                                                   | -                                  | Data, Clk                                         | t <sub>suDC</sub>                  | -                              | 100         | _                              | ns           |

| Hold Time                               | =                                                                   | -                                  | Data, Clk                                         | t <sub>h</sub>                     | -                              | 90          | _                              | ns           |

| Recovery Time                           | -                                                                   | -                                  | EN, Clk                                           | t <sub>rec</sub>                   | _                              | 90          | _                              | ns           |

| Input Pulse Width                       | -                                                                   | -                                  | EN, Clk                                           | t <sub>W</sub>                     | _                              | 100         | _                              | ns           |

| Input Rise and Fall Time                | -                                                                   | -                                  | Data,<br>Clk, EN                                  | t <sub>r</sub> , t <sub>f</sub>    | -                              | 9.0         | _                              | μs           |

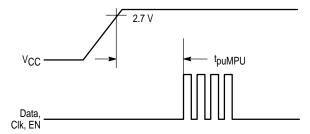

| MPU Interface Power–Up<br>Delay         | 90% of PLL V <sub>ref</sub> to Data,<br>Clk, EN                     | _                                  | -                                                 | <sup>t</sup> puMPU                 | -                              | 100         | _                              | μs           |

| FM RECEIVER (f <sub>RF</sub> = 46.77    | MHz [USA Ch 21], $f_{dev} = \pm 3.0 \text{ kHz}$                    | Hz, f <sub>mod</sub> = 1.0         | kHz)                                              |                                    |                                |             | ı                              | l            |

| Sensitivity (Input for 12 dB SINAD)     | 50 Ω Termination                                                    | Mix <sub>1</sub> In <sub>1/2</sub> | Det Out                                           | VSIN                               | -                              | 2.8<br>-98  | _<br>_                         | μVrms<br>dBm |

|                                         | Single–Ended, Matched Input<br>Generator Referred                   | Mix <sub>1</sub> In <sub>1/2</sub> | Det Out                                           | VSIN                               | -<br>-                         | 1.0<br>–107 | _<br>_                         | μVrms<br>dBm |

|                                         | Differential, Matched Input<br>Generator Referred                   | Mix <sub>1</sub> In <sub>1/2</sub> | Det Out                                           | VSIN                               | _<br>_                         | .56<br>–112 | _<br>_                         | μVrms<br>dBm |

| 1st Mixer Voltage<br>Conversion Gain    | V <sub>in</sub> = 1.0 mVrms, with CF <sub>1</sub><br>Filter as Load | Mix <sub>1</sub> In <sub>1/2</sub> | Mix <sub>1</sub> Out                              | MX <sub>gain1</sub>                | -                              | 12          | _                              | dB           |

| 2nd Mixer Voltage<br>Conversion Gain    | V <sub>in</sub> = 3.0 mVrms, with CF <sub>2</sub><br>Filter as Load | Mix <sub>2</sub> In                | Mix <sub>2</sub> Out                              | MX <sub>gain2</sub>                | -                              | 20          | -                              | dB           |

| 1st and 2nd Mixer Voltage<br>Gain Total | $V_{in} = 1.0 \text{ mVrms, with CF}_1$ and CF <sub>2</sub> Load    | Mix <sub>1</sub> In <sub>1/2</sub> | Mix <sub>2</sub> Out                              | MXgainT                            | 24                             | 28          | -                              | dB           |

| 1st Mixer Input Impedance               | Single–Ended Input                                                  | _                                  | Mix <sub>1</sub> In <sub>1/2</sub>                | R <sub>P1</sub><br>C <sub>P1</sub> | _<br>_                         | 875<br>2.7  | _<br>_                         | Ω<br>pF      |

| 2nd Mixer Input Impedance               | f <sub>in</sub> = 10.7 MHz                                          | -                                  | Mix <sub>2</sub> In                               | Z <sub>in2</sub>                   | _                              | 3.0         | _                              | kΩ           |

**ELECTRICAL CHARACTERISTICS** (continued) ( $V_{CC} = 3.6 \text{ V}$ ,  $V_B = 1.5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , Active or  $R_X$  Mode, unless otherwise specified; Test Circuit Figure 1.)

| Characteristic                                                                                                            | Condition                                                                  | Input<br>Pin                       | Measure<br>Pin       | Symbol                                       | Min                   | Тур  | Max | Unit  |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------|----------------------|----------------------------------------------|-----------------------|------|-----|-------|

| FM RECEIVER (f <sub>RF</sub> = 46.77                                                                                      | MHz [USA Ch 21], f <sub>dev</sub> = ±3.0 kH                                | Hz, f <sub>mod</sub> = 1.0         | kHz)                 |                                              |                       |      |     |       |

| 1st Mixer Output Impedance                                                                                                | -                                                                          | -                                  | Mix <sub>1</sub> Out | Z <sub>out1</sub>                            | -                     | 330  | -   | Ω     |

| 2nd Mixer Output<br>Impedance                                                                                             | -                                                                          | _                                  | Mix <sub>2</sub> Out | Z <sub>out2</sub>                            | -                     | 1.5  | -   | kΩ    |

| IF – 3.0 dB Limiting<br>Sensitivity                                                                                       | f <sub>in</sub> = 455 kHz                                                  | Lim In                             | Det Out              | IF Sens                                      | -                     | 71   | 100 | μVrms |

| Total Harmonic Distortion                                                                                                 | With R <sub>C</sub> = 15 k/1.0 nF Filter at Det Out                        | Mix <sub>1</sub> In <sub>1</sub>   | Det Out              | THD                                          | -                     | 1.3  | 2.0 | %     |

| Recovered Audio                                                                                                           | $V_{in}$ = 3.16 mVrms with R <sub>C</sub> = 15 k/1000 pF Filter at Det Out | Mix <sub>1</sub> In <sub>1</sub>   | Det Out              | AFO                                          | 80                    | 105  | 150 | mVrms |

| Demodulator Bandwidth                                                                                                     | -                                                                          | Lim In                             | Det Out              | BW                                           | _                     | 20   | -   | kHz   |

| Signal to Noise Ratio $V_{in} = 3.16 \text{ mVrms}, \\ R_{C} = 15 \text{ k/1000 pF}$                                      |                                                                            | Mix <sub>1</sub> In <sub>1</sub>   | Det Out              | SN                                           | -                     | 49   | -   | dB    |

| AM Rejection Ratio $V_{in} = 3.16 \text{ mVrms}, \\ 30\% \text{ AM, } @ 1.0 \text{ kHz}, \\ R_{C} = 15 \text{ k/1000 pF}$ |                                                                            | Mix <sub>1</sub> In <sub>1</sub>   | Det Out              | AMR                                          | 30                    | 47   | -   | dB    |

| 1st Mixer, 1.0 dB Voltage<br>Compression (Input Pin<br>Referred)                                                          | -                                                                          | Mix <sub>1</sub> In <sub>1/2</sub> | Mix <sub>1</sub> Out | V <sub>O</sub><br>1.0 dB<br>Mix <sub>1</sub> | _                     | 15   | -   | mVrms |

| 2nd Mixer, 1.0 dB Voltage<br>Compression (Input Pin<br>Referred)                                                          | 50 Ω Input                                                                 | Mix <sub>2</sub> In                | Mix <sub>2</sub> Out | V <sub>O</sub><br>1.0 dB<br>Mix <sub>2</sub> | _                     | 14   | -   | mVrms |

| 1st Mixer 3rd Order<br>Intercept (Input Pin<br>Referred)                                                                  | V <sub>in</sub> = 3.98 mVrms                                               | Mix <sub>1</sub> In <sub>1</sub>   | Mix <sub>1</sub> Out | TOI <sub>mix1</sub>                          | _                     | 56   | -   | mVrms |

| 2nd Mixer 3rd Order<br>Intercept (Input Pin<br>Referred)                                                                  | $V_{in}$ = 3.98 mVrms, 50 $\Omega$ Input                                   | Mix <sub>2</sub> In                | Mix <sub>2</sub> Out | TOI <sub>mix2</sub>                          | -                     | 53   | -   | mVrms |

| Detector Output Impedance                                                                                                 | -                                                                          | -                                  | Det Out              | ZO                                           | _                     | 870  | -   | Ω     |

| RSSI/CARRIER DETECT (R                                                                                                    | L = 100 kΩ)                                                                | •                                  | •                    |                                              |                       |      |     | •     |

| RSSI Output Current<br>Dynamic Range                                                                                      | -                                                                          | Mix <sub>1</sub> In                | RSSI                 | RSSI                                         | -                     | 80   | -   | dB    |

| Carrier Sense Threshold CD Threshold Adjust = (10100)                                                                     |                                                                            | Mix <sub>1</sub> In                | CD Out               | VT                                           | -                     | 33   | -   | μVrms |

| Hysteresis                                                                                                                | -                                                                          |                                    | CD Out               | Hys                                          | -                     | 3.6  | 7.0 | dB    |

| Output High Voltage V <sub>in</sub> = 0 Vrms, CD = (10100)                                                                |                                                                            | Mix <sub>1</sub> In                | CD Out               | Voн                                          | V <sub>CC</sub> - 0.1 | 3.6  | -   | V     |

| Output Low Voltage                                                                                                        | V <sub>in</sub> = -80 dBV, CD = (10100)                                    | Mix <sub>1</sub> In                | CD Out               | V <sub>OL</sub>                              | _                     | 0.02 | 0.4 | V     |

|                                                                                                                           |                                                                            |                                    | l                    |                                              |                       |      |     |       |

**ELECTRICAL CHARACTERISTICS** (continued) ( $V_{CC} = 3.6 \text{ V}$ ,  $V_B = 1.5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , Active or  $R_X$  Mode, unless otherwise specified; Test Circuit Figure 1.)

| Characteristic                                      | Condition                                                                                                          | Input<br>Pin                    | Measure<br>Pin     | Symbol                         | Min                   | Тур                   | Max         | Unit |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|--------------------------------|-----------------------|-----------------------|-------------|------|

| RSSI/CARRIER DETECT (R                              | = 100 kΩ)                                                                                                          | •                               |                    |                                | •                     | •                     |             |      |

| Carrier Sense Threshold<br>Adjustment Range         | Programmable through MPU Interface                                                                                 | _                               | ı                  | VT low<br>range                | -20                   | -                     | ı           | dB   |

|                                                     |                                                                                                                    | _                               | I                  | <sup>V</sup> T hi<br>range     | -                     | _                     | 11          |      |

| Carrier Sense Threshold –<br>Number of Steps        | Programmable through MPU Interface                                                                                 | _                               | -                  | V <sub>Tn</sub>                | -                     | 32                    | -           | _    |

| DATA AMP COMPARATOR                                 |                                                                                                                    |                                 |                    |                                |                       |                       |             |      |

| Hysteresis                                          | -                                                                                                                  | DA In                           | DA Out             | Hys                            | 30                    | 40                    | 50          | mV   |

| Threshold Voltage                                   | -                                                                                                                  | DA In                           | DA Out             | VT                             | 2.7                   | V <sub>CC</sub> - 0.7 | -           | V    |

| Input Impedance                                     | -                                                                                                                  | _                               | DA In              | ZĮ                             | _                     | 11                    | -           | kΩ   |

| Output Impedance                                    | =                                                                                                                  | _                               | DA Out             | ZO                             | _                     | 100                   | _           | kΩ   |

| Output High Voltage                                 | $V_{in} = V_{CC} - 1.0 \text{ V},$<br>$I_{OH} = 0 \text{ mA}$                                                      | DA In                           | DA Out             | Voн                            | V <sub>CC</sub> - 0.1 | 3.6                   | -           | V    |

| Output Low Voltage                                  | $V_{in} = V_{CC} - 0.4 \text{ V},$ $I_{OL} = 0 \text{ mA}$                                                         | DA In                           | DA Out             | VOL                            | -                     | 0.04                  | 0.4         | V    |

| R <sub>X</sub> AUDIO PATH (f <sub>in</sub> = 1.0 kl | Hz)                                                                                                                |                                 |                    |                                |                       | •                     |             |      |

| Absolute Gain                                       | $V_{in} = -20 \text{ dBV}$                                                                                         | E In                            | E Out              | G                              | -3.0                  | 0                     | 3.0         | dB   |

| Gain Tracking                                       |                                                                                                                    |                                 | E Out              | Gt                             | -21<br>-42            | -20<br>-40            | -19<br>-38  | dB   |

| Total Harmonic Distortion                           | $V_{in} = -20 \text{ dBV}$                                                                                         | E In                            | E Out              | THD                            | _                     | 0.5                   | 1.0         | %    |

| Maximum Input Voltage                               | =                                                                                                                  | R <sub>X</sub> Audio In         | _                  | -                              | _                     | -11.5                 | _           | dBV  |

| Maximum Output Voltage                              | Increase input voltage until output voltage THD = 5.0%, then measure output voltage. R <sub>L</sub> = 7.5 k/1.0 µF | E In                            | E Out              | V <sub>Omax</sub>              | _                     | 0                     | -           | dBV  |

| Input Impedance                                     | -                                                                                                                  | R <sub>X</sub> Audio In<br>E In | -                  | z <sub>in</sub>                | -<br>-                | 600<br>7.5            | -           | kΩ   |

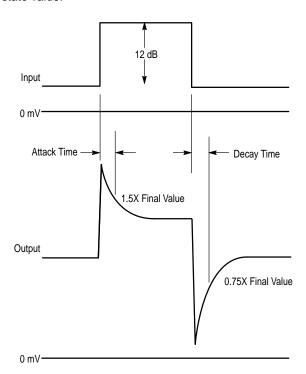

| Attack Time                                         | E <sub>cap</sub> = 0.5 μF, R <sub>filt</sub> = 40 k<br>(See Appendix B)                                            | E In                            | E Out              | t <sub>a</sub>                 | -                     | 3.0                   | -           | ms   |

| Release Time                                        | E <sub>cap</sub> = 0.5 μF, R <sub>filt</sub> = 40 k<br>(See Appendix B)                                            | E In                            | E Out              | t <sub>r</sub>                 | -                     | 13.5                  | -           | ms   |

| Compressor to Expandor<br>Crosstalk                 | $V_{in} = -10 \text{ dBV},$<br>$V_{(E \text{ In})} = AC \text{ Gnd}$                                               | C In                            | E Out              | CT                             | -                     | -90                   | -70         | dB   |

| R <sub>X</sub> Data Muting (∆ Gain)                 | $V_{in} = -20 \text{ dBV},$ $R_X \text{ Gain Adj} = (01111)$                                                       | R <sub>X</sub> Audio In         | E Out              | M <sub>e</sub>                 | -                     | -83                   | -60         | dB   |

| R <sub>X</sub> High Frequency Corner (Note 1)       | R <sub>X</sub> Path,<br>V R <sub>X</sub> Audio In = -20 dBV                                                        | R <sub>X</sub> Audio In         | Scr Out            | R <sub>x</sub> f <sub>ch</sub> | -                     | 3.879                 | -           | kHz  |

| SPEAKER AMP/SP MUTE                                 |                                                                                                                    |                                 |                    |                                |                       |                       |             |      |

| Maximum Output Swing $R_L = 130 \Omega$             |                                                                                                                    | SA In                           | SA Out             | V <sub>Omax</sub>              | 0.8                   | 0.9                   | -           | Vpp  |

| Speaker Amp Muting                                  | $V_{in} = -20 \text{ dBV}$                                                                                         | SA In                           | SA Out             | M <sub>sp</sub>                | -                     | -90                   | -60         | dB   |

| T <sub>X</sub> AUDIO PATH (f <sub>in</sub> = 1.0 kH | Iz, T <sub>X</sub> Gain Adj = (01111), f <sub>in</sub> = 1.                                                        | 0 kHz)                          |                    |                                |                       |                       |             |      |

| Absolute Gain                                       | V <sub>in</sub> = −10 dBV, ALC,<br>Lim Disabled                                                                    | T <sub>X</sub> In               | T <sub>X</sub> Out | G                              | -4.0                  | 0                     | 4.0         | dB   |

| Gain Tracking                                       | $V_{in} = -30 \text{ dBV}$<br>$V_{in} = -40 \text{ dBV}$                                                           | T <sub>X</sub> In               | T <sub>X</sub> Out | Gt                             | -11<br>-17            | -10<br>-20            | -9.0<br>-13 | dB   |

| Total Harmonic Distortion V <sub>in</sub> = -10 dBV |                                                                                                                    | T <sub>X</sub> In               | T <sub>X</sub> Out | THD                            | _                     | 0.6                   | 1.1         | %    |

**ELECTRICAL CHARACTERISTICS** (continued) ( $V_{CC} = 3.6 \text{ V}$ ,  $V_B = 1.5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , Active or  $R_X$  Mode, unless otherwise specified; Test Circuit Figure 1.)

| Characteristic                                               | Condition                                                                                                                                  | Input<br>Pin                         | Measure<br>Pin                             | Symbol                         | Min                   | Тур        | Max          | Unit |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|--------------------------------|-----------------------|------------|--------------|------|

| T <sub>X</sub> AUDIO PATH (f <sub>in</sub> = 1.0 kH          | Hz, T <sub>X</sub> Gain Adj = (01111), f <sub>in</sub> = 1.0                                                                               | ) kHz)                               |                                            |                                |                       | •          |              |      |

| Maximum Output Voltage                                       | Increase input voltage until output voltage THD = $5.0\%$ , then measure output voltage. R <sub>L</sub> = $7.5 \text{ k/} 1.0 \mu\text{F}$ | C In                                 | T <sub>X</sub> Out                         | VOmax                          | _                     | -5.0       | -            | dBV  |

| Input Impedance                                              | _                                                                                                                                          | C In                                 | T <sub>X</sub> Out                         | Z <sub>in</sub>                | _                     | 10         | _            | kΩ   |

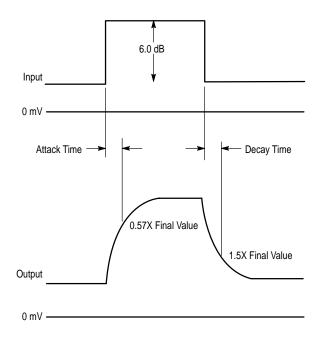

| Attack Time                                                  | C <sub>cap</sub> = 0.5 μF, R <sub>filt</sub> = 40 k<br>(See Appendix B)                                                                    | C In                                 | T <sub>X</sub> Out                         | ta                             | -                     | 3.0        | -            | ms   |

| Release Time                                                 | C <sub>cap</sub> = 0.5 μF, R <sub>filt</sub> = 40 k<br>(See Appendix B)                                                                    | C In                                 | T <sub>X</sub> Out                         | t <sub>r</sub>                 | -                     | 13.5       | -            | ms   |

| Expandor to Compressor<br>Crosstalk                          | $V_{in} = -20$ dBV, Speaker Amp<br>No Load, $V_{(C\ In)} = AC$ Gnd                                                                         | E In                                 | T <sub>X</sub> Out                         | СТ                             | -                     | -60        | -40          | dB   |

| T <sub>X</sub> Muting                                        | V <sub>in</sub> – 10 dBV                                                                                                                   | T <sub>X</sub> In                    | T <sub>X</sub> Out                         | M <sub>C</sub>                 | _                     | -90        | -60          | dB   |

| ALC Output Level                                             | V <sub>in</sub> = -10 dBV<br>V <sub>in</sub> = -2.5 dBV<br>Limiter and Mutes disabled                                                      | T <sub>X</sub> In                    | T <sub>X</sub> Out                         | ALCout                         | -15<br>-13            | -11<br>-10 | -8.0<br>-6.0 | dBV  |

| Limiter Output Level                                         | V <sub>in</sub> = -2.5 dBV,<br>ALC disabled                                                                                                | T <sub>X</sub> In                    | T <sub>X</sub> Out                         | V <sub>lim</sub>               | -10                   | -7.0       | _            | dBV  |

| T <sub>X</sub> High Frequency Corner (Note 1)                | $T_X$ Path, $V T_X$ In = -10 dBV,<br>Mic Amp = Unity Gain                                                                                  | T <sub>X</sub> In                    | T <sub>X</sub> Out                         | T <sub>x</sub> f <sub>ch</sub> | -                     | 3.7        | _            | kHz  |

| MIC AMP (fin = 1.0 kHz, Exte                                 | ernal resistors set to gain of 1)                                                                                                          |                                      |                                            |                                |                       |            |              |      |

| Open Loop Gain                                               | -                                                                                                                                          | T <sub>X</sub> In                    | Amp Out                                    | AVOL                           | _                     | 100,000    | _            | V/V  |

| Gain Bandwidth                                               | _                                                                                                                                          | T <sub>X</sub> In                    | Amp Out                                    | GBW                            | _                     | 100        | _            | kHz  |

| Maximum Output Swing                                         | $R_L = 10 \text{ k}\Omega$                                                                                                                 | T <sub>X</sub> In                    | Amp Out                                    | V <sub>Omax</sub>              | _                     | 2.8        | _            | Vpp  |

| LOW BATTERY DETECT                                           |                                                                                                                                            |                                      |                                            |                                |                       |            |              |      |

| Average Threshold<br>Voltage Before Electronic<br>Adjustment | V <sub>CC</sub> = 3.6 V, V <sub>ref</sub> _Adj = (0111). Take average of rising and falling threshold                                      | Ref <sub>1</sub><br>Ref <sub>2</sub> | BD <sub>1</sub> Out<br>BD <sub>2</sub> Out | VTi                            | 1.36                  | 1.5        | 1.64         | V    |

| Average Threshold<br>Voltage After Electronic<br>Adjustment  | V <sub>CC</sub> = 3.6 V, V <sub>ref</sub> Adj = (adjusted value). Take average of rising and falling threshold                             | Ref <sub>1</sub><br>Ref <sub>2</sub> | BD <sub>1</sub> Out<br>BD <sub>2</sub> Out | VTf                            | 1.475                 | 1.5        | 1.525        | V    |

| Hysteresis –                                                 |                                                                                                                                            | Ref <sub>1</sub><br>Ref <sub>2</sub> | BD <sub>1</sub> Out<br>BD <sub>2</sub> Out | Hys                            | -                     | 4.0        | _            | mV   |

| Input Current                                                | V <sub>in</sub> = 1.0 to 2.0 V                                                                                                             | -                                    | Ref <sub>1</sub><br>Ref <sub>2</sub>       | l <sub>in</sub>                | -50                   | -          | 50           | nA   |

| Output High Voltage                                          | $V_{in}$ = 2.0 V,<br>$R_L$ = 3.9 k $\Omega$ to $V_{CC}$                                                                                    | Ref <sub>1</sub><br>Ref <sub>2</sub> | BD <sub>1</sub> Out<br>BD <sub>2</sub> Out | Voн                            | V <sub>CC</sub> - 0.1 | 3.6        | -            | V    |

| Output Low Voltage                                           | $V_{in}$ = 1.0 V,<br>$R_L$ = 3.9 k $\Omega$ to $V_{CC}$                                                                                    | Ref <sub>1</sub><br>Ref <sub>2</sub> | BD <sub>1</sub> Out<br>BD <sub>2</sub> Out | V <sub>OL</sub>                | -                     | 0.1        | 0.4          | V    |

NOTE: 1. The filter specification is based on a 10.24 MHz 2nd LO, and a switched–capacitor (SC) filter counter divider ratio of 31. If other 2nd LO frequencies and/or SC filter counter divider ratios are used, the filter corner frequency will be proportional to the resulting SC filter clock frequency.

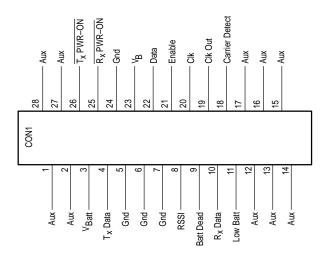

# PIN FUNCTION DESCRIPTION

| Pin           | Symbol                                   | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2           | LO <sub>2</sub> In<br>LO2 Out            | -      | These pins form the PLL reference oscillator when connected to an external parallel–resonant crystal (10.24 MHz typical). The reference oscillator is also the second Local Oscillator (LO <sub>2</sub> ) for the RF receiver. "LO <sub>2</sub> In" may also serve as an input for an externally generated reference signal which is typically ac–coupled.                                                                                                                       |

| 3             | V <sub>ag</sub>                          | _      | Internal reference voltage for switched capacitor filter section.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4             | R <sub>X</sub> PD                        | Output | Three state voltage output of the $R_X$ Phase Detector. This pin is either "high", "low", or "high impedance" depending on the phase difference of the phase detector input signals. During lock, very narrow pulses with a frequency equal to the reference frequency are present. This pin drives the external $R_X$ PLL loop filter. It is important to minimize the line length and parasitic capacitance of this pin.                                                       |

| 5             | PLL V <sub>ref</sub>                     | _      | PLL voltage regulator output pin. An internal voltage regulator provides a stable power supply voltage for the R <sub>X</sub> and T <sub>X</sub> PLL's and can also be used as a regulated supply voltage for other IC's.                                                                                                                                                                                                                                                        |

| 6             | T <sub>X</sub> PD                        | Output | Three state voltage output of the $T_X$ Phase Detector. This pin is either "high", "low", or "high impedance" depending on the phase difference of the phase detector input signals. During lock, very narrow pulses with a frequency equal to the reference frequency are present. This pin drives the external $T_X$ PLL loop filter. It is important to minimize the line length and parasitic capacitance of this pin.                                                       |

| 7             | Gnd PLL                                  | Gnd    | Ground pin for PLL section of IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8             | T <sub>X</sub> VCO                       | Input  | Transmit divide counter input which is driven by an ac–coupled external transmit loop VCO. The minimum signal level is 200 mVpp @ 60.0 MHz. This pin also functions as the test mode input for the counter tests.                                                                                                                                                                                                                                                                |

| 9<br>10<br>11 | Data<br>EN<br>Clk                        | Input  | Microprocessor serial interface input pins for programming various counters and control functions.                                                                                                                                                                                                                                                                                                                                                                               |

| 12            | Clk Out                                  | Output | Microprocessor Clock Output which is derived from the 2nd LO crystal oscillator and a programmable divider. It can be used to drive a microprocessor and thereby reduce the number of crystals required in the system design. The driver has an internal resistor in series with the output which can be combined with an external capacitor to form a low pass filter to reduce radiated noise on the PCB. This output also functions as the output for the counter test modes. |

| 13            | CD Out                                   | I/O    | Dual function pin; 1) Carrier detect output (open collector with external 100 kΩ pull–up resistor. 2) Hardware interrupt input which can be used to "wake–up" from Inactive Mode.                                                                                                                                                                                                                                                                                                |

| 14            | BD <sub>1</sub> Out                      | Output | Low battery detect output #1 (open collector with external pull-up resistor).                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15            | DA Out                                   | Output | Data amplifier output (open collector with internal 100 k $\Omega$ pull–up resistor).                                                                                                                                                                                                                                                                                                                                                                                            |

| 16            | BD <sub>2</sub> Out                      | Output | Low battery detect output #2 (open collector with external pull-up resistor).                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17            | T <sub>X</sub> Out                       | Output | T <sub>X</sub> path audio output.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18            | C Cap                                    | -      | Compressor rectifier filter capacitor pin. Pull pin high through a capacitor.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19            | C In                                     | Input  | Compressor input (ac-coupled).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 20            | Amp Out                                  | Output | Microphone amplifier output.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 21            | T <sub>X</sub> In                        | Input  | T <sub>X</sub> path input to microphone amplifier (Mic Amp) (ac-coupled).                                                                                                                                                                                                                                                                                                                                                                                                        |

| 22            | DA In                                    | Input  | Data amplifier input (ac-coupled).                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 23            | V <sub>CC</sub> Audio                    | Supply | V <sub>CC</sub> supply for audio section.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 24            | R <sub>X</sub> Audio In                  | Input  | R <sub>X</sub> audio input (ac–coupled).                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 25            | Det Out                                  | Output | Audio output from FM detector.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 26            | RSSI                                     | Output | Receive Signal Strength Indicator filter capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 27<br>28      | Q Coil<br>Lim Out                        | _      | A quad coil or ceramic discriminator connected to these pins as part of the FM demodulator circuit.                                                                                                                                                                                                                                                                                                                                                                              |

| 29            | V <sub>CC</sub> RF                       | Supply | V <sub>CC</sub> supply for RF receiver section.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 30<br>31      | Lim C <sub>2</sub><br>Lim C <sub>1</sub> | _      | IF amplifier/limiter capacitor pins.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 32            | Lim In                                   | Input  | Signal input for IF amplifier/limiter.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# PIN FUNCTION DESCRIPTION (continued)

| Pin      | Symbol                                    | Туре   | Description                                                                    |

|----------|-------------------------------------------|--------|--------------------------------------------------------------------------------|

| 33       | SGND RF                                   | Gnd    | Ground pin for RF section of the IC.                                           |

| 34       | Mix <sub>2</sub> In                       | Input  | Second mixer input.                                                            |

| 35       | Mix <sub>2</sub> Out                      | Output | Second mixer output.                                                           |

| 36       | Gnd RF                                    | Gnd    | Ground pin for RF section of the IC.                                           |

| 37       | Mix <sub>1</sub> Out                      | Output | First mixer output.                                                            |

| 38       | Mix <sub>1</sub> In <sub>2</sub>          | Input  | Negative phase first mixer input.                                              |

| 39       | Mix <sub>1</sub> In <sub>1</sub>          | Input  | Positive phase first mixer input.                                              |

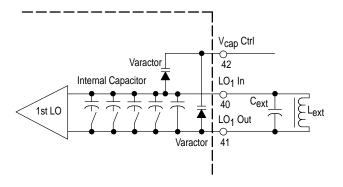

| 40<br>41 | LO <sub>1</sub> In<br>LO <sub>1</sub> Out | _      | Tank Elements for 1st LO Multivibrator Oscillator are connected to these pins. |

| 42       | V <sub>cap</sub> Ctrl                     | -      | 1st LO Varactor Control Pin.                                                   |

| 43       | Gnd Audio                                 | Gnd    | Ground for audio section of the IC.                                            |

| 44       | SA Out                                    | Output | Speaker amplifier output.                                                      |

| 45       | SA In                                     | Input  | Speaker amplifier input (ac–coupled).                                          |

| 46       | E Out                                     | Output | Expandor output.                                                               |

| 47       | E <sub>cap</sub>                          | _      | Expandor rectifier filter capacitor pin. Pull pin high through a capacitor.    |

| 48       | E In                                      | Input  | Expandor Input.                                                                |

| 49       | Scr Out                                   | Output | R <sub>X</sub> Audio Output.                                                   |

| 50       | Ref <sub>2</sub>                          | _      | Reference voltage input for Low Battery Detect #2.                             |

| 51       | Ref <sub>1</sub>                          | _      | Reference voltage input for Low Battery Detect #1.                             |

| 52       | VB                                        | -      | Internal half supply analog ground reference.                                  |

#### **FM Receiver**

The FM receiver can be used with either a quad coil or a ceramic resonator. The FM receiver and 1st LO have been designed to work for all country channels, including 25 channel U.S., without the need for any external switching circuitry (see Figure 32).

#### **RSSI/Carrier Detect**

Connect 0.01  $\mu F$  to Gnd from "RSSI" output pin to form the carrier detect filter. "CD Out" is an open collector output which requires an external 100 k $\Omega$  pull–up resistor to VCC. The carrier detect threshold is programmable through the MPU interface.

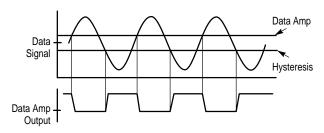

#### **Data Amp Comparator**

The data amp comparator is an inverting hysteresis comparator. Its open collector output has an internal 100  $k\Omega$  pull—up resistor. A band pass filter is connected between the "Det Out" pin and the "DA In" pin with component values as shown in Figure 1 (Test Circuit). The "DA In" input signal is ac—coupled.

Figure 2. Data Amp Operation

#### **Expandor/ Compressor**

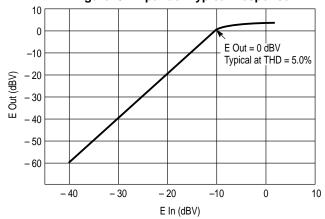

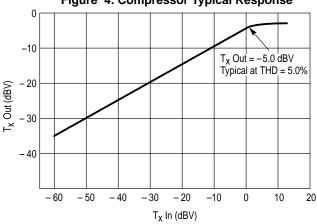

In Appendix B, the EIA/CCITT recommendations for measurement of the attack and decay times are defined. The curves in Figures 3 and 4 show the typical expandor and compressor output versus input responses.

Figure 3. Expandor Typical Response

Figure 4. Compressor Typical Response

#### R<sub>X</sub> Audio Path (LPF/R<sub>X</sub> Gain Adjust/ R<sub>X</sub> Mute/Expandor/Volume Control)

The  $R_X$  Audio signal path goes from " $R_X$  Audio In" (Pin 24) to "E Out" (Pin 46). The " $R_X$  Audio In" input signal is ac coupled. AC couple between "Scr Out" and "E In" (see Figure 3).

#### Speaker Amp/SP Mute

The Speaker Amp is an inverting rail-to-rail operational amplifier. The noninverting input is connected to the internal VB reference. External resistors and capacitors are used to set the gain and frequency response. The "SA In" Input is ac coupled.

#### Mic Amp

The Mic Amp is an inverting rail–to–rail operational amplifier with noninverting input terminal connected to internal  $V_B$  reference. External resistors and capacitors are set to the gain and frequency response. The " $T_X$  In" input is ac coupled.

## T<sub>X</sub> Audio Path (Compressor/ALC/T<sub>X</sub> Mute/ Limiter/LPF/T<sub>X</sub> Gain Adjust)

The  $T_X$  Audio signal path goes from " $T_X$  In" (Pin 19) to " $T_X$  Out" (Pin 17). The "C In" input signal is ac coupled from "Amp Out". The ALC (Automatic Level Control) provides a "soft" limit to the output signal swing as the input voltage increases slowly (i.e., a sine wave is maintained). The Limiter circuit limits rapidly changing signal levels by clipping the signal peaks. The ALC and/or Limiter can be disabled through the MPU serial interface (see Figure 4).

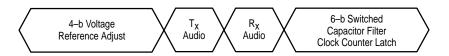

#### T<sub>X</sub> and R<sub>X</sub> Audio

Each audio path contains a low–pass switched capacitor filter (SCF). The control register must be set through the MPU interface (Figure 11) for proper operation ( $T_X$  and  $R_X$  bits must be set to "1"). The SCF corner frequencies are proportional to the SCF Clock. The SCF Clock Divider is programmable through the MPU interface as follows: (SCF) = F(2nd LO) / (SCF Divider Value \* 2). The LPF corner

frequencies can be selected in from the table in Figures 28 and 29 relative to the 2nd LO operating frequency.

#### **PLL Voltage Regulator**

The "PLL V<sub>ref</sub>" pin is the internal supply voltage for the R<sub>X</sub> and T<sub>X</sub> PLL's. It is regulated to a nominal 2.5 V. The "V<sub>CC</sub> Audio" pin is the supply voltage for the internal voltage regulator. Two capacitors with 10  $\mu$ F and 0.1  $\mu$ F values must be connected to the "PLL V<sub>ref</sub>" pin to filter and stabilize this regulated voltage. The "PLL V<sub>ref</sub>" pin may be used to power other IC's as long as the total external load current does not exceed 1.0 mA. The tolerance of the regulated voltage is initially  $\pm 8.0\%$ , but is improved to  $\pm 4.0\%$  after the internal Bandgap voltage reference is adjusted electronically through the MPU serial interface. The voltage regulator is turned off in the Standby and Inactive modes to reduce current drain. In these modes, the "PLL V<sub>ref</sub>" pin is internally connected to the "V<sub>CC</sub> Audio" pin (i.e., the power supply voltage is maintained but is now unregulated).

#### **Low Battery Detect**

Two external precision resistor dividers are used to set independent thresholds for two battery detect hysteresis comparators. The voltages on "Ref1" and "Ref2" are compared to an internally generated 1.5 V reference voltage. The tolerance of the internal reference voltage is initially  $\pm 6.0\%$ . The Low Battery Detect threshold tolerance can be improved by adjusting a trim–pot in the external resistor divider. Alternately, the tolerance of the internal reference voltage can be improved to  $\pm 1.5\%$  through MPU serial interface programming. The internal reference can be measured directly at the "VB" pin. During final test of the telephone, the VB internal reference voltage is measured. Then, the internal reference voltage value is adjusted

electronically through the MPU serial interface to achieve the desired accuracy level. The voltage reference register value should be stored in ROM during final test so that it can be reloaded each time the MC13111 IC is powered up. Low Battery Detect outputs are open collector.

#### **Power Supply Voltage**

This circuit is used in a cordless telephone handset and base unit. The handset is battery powered and can operate on three NiCad cells or on 5.0 V supply.

#### **PLL Frequency Synthesizer General Description**

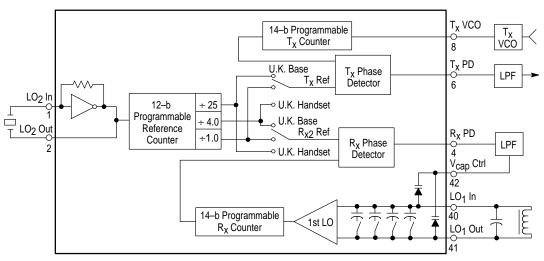

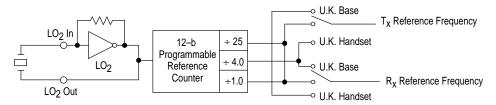

Figure 5 shows a simplified block diagram of the programmable universal dual phase locked loop (PLL). This dual PLL is fully programmable through the MCU serial interface and supports most country channel frequencies including USA (25 ch), Spain, Australia, Korea, New Zealand, U. K., Netherlands, France, and China.

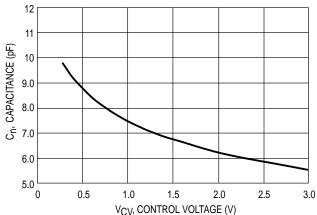

The 2nd local oscillator and reference divider provide the reference frequency for the receive (R<sub>x</sub>) and transmit (T<sub>x</sub>) PLL loops. The programmed divider value for the reference divider is selected based on the crystal frequency and the desired R<sub>x</sub> and T<sub>x</sub> reference frequency values. Additional divide by 25 and divide by 4 blocks are provided to allow for generation of the 1.0 kHz and 6.25 kHz reference frequencies required for the U. K. The 14-bit T<sub>x</sub> counter is programmed for the desired transmit channel frequency. The 14-bit R<sub>x</sub> counter is programmed for the desired first local oscillator frequency. All counters power up in the proper default state for USA channel #21 (channel #6 for FCC 10 channel band) and for a 10.24 MHz reference frequency crystal. Internal fixed capacitors can be connected to the tank circuit of the 1st LO through microprocessor control to extend the sensitivity of the 1st LO for U.S. 25 channel operation.

Figure 5. Dual PLL Simplified Block Diagram

#### PLL I/O Pin Specifications

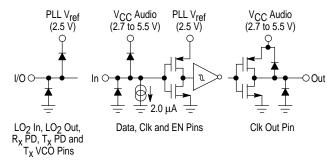

The 2nd LO,  $R_X$  and  $T_X$  PLL's, and MPU serial interface are powered by the internal voltage regulator at the "PLL  $V_{ref}$ " pin. The "PLL  $V_{ref}$ " pin is the output of a voltage regulator which is powered from the " $V_{CC}$  Audio" power supply pin and is regulated by an internal bandgap voltage reference. Therefore, the maximum input and output levels for most PLL I/O pins (LO $_2$  In, LO $_2$  Out,  $R_X$  PD,  $T_X$  PD,  $T_X$  VCO) is the regulated voltage at the "PLL  $V_{ref}$ " pin. The ESD protection diodes on these pins are also connected to "PLL  $V_{ref}$ ". Internal level shift buffers are provided for the pins (Data, Clk, EN, Clk Out) which connect directly to the microprocessor. The maximum input and output levels for these pins is  $V_{CC}$ . Figure 6 shows a simplified schematic of the I/O pins.

Figure 6. PLL I/O Pin Simplified Schematics

#### **Microprocessor Serial Interface**

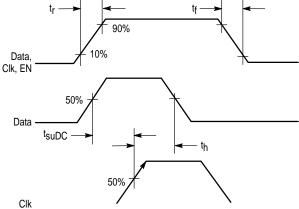

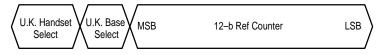

The "Data", "Clk", and "EN" pins provide an MPU serial interface for programming the reference counters, the transmit and receive channel divider counters, the switched capacitor filter clock counter, and various control functions. The "Data" and "Clk" pins are used to load data into the shift register. Figure 7 shows the timing required on the "Data" and "Clk" pins. Data is clocked into the shift register on positive clock transitions.

Figure 7. Data and Clock Timing Requirement

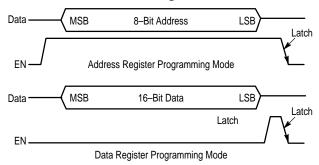

After data is loaded into the shift register, the data is latched into the appropriate latch register using the "EN" pin. This is done in two steps. First, an 8-bit address is loaded into the shift register and latched into the 8-bit address latch register. Then, up to 16-bits of data is loaded into the shift register and latched into the data latch register specified by the address that was previously loaded. Figure 5 shows the timing required on the EN pin. Latching occurs on the negative EN transition.

Figure 8. Enable Timing Requirement

The state of the EN pin when clocking data into the shift register determines whether the data is latched into the address register or a data register. Figure 9 shows the address and data programming diagrams. In the data programming mode, there must not be any clock transitions when "EN" is high. The clock can be in a high state (default high) or a low state (default low) but must not have any transitions during the "EN" high state. The convention in these figures is that latch bits to the left are loaded into the shift register first.

Figure 9. Microprocessor Interface Programming Mode Diagrams

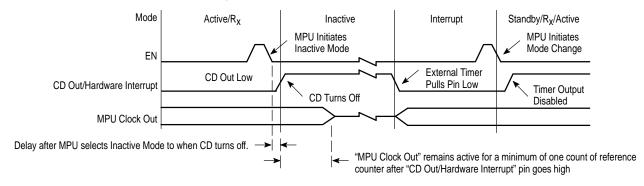

The MPU serial interface is fully operational within 100  $\mu$ s after the power supply has reached its minimum level during power–up (see Figure 10). The MPU Interface shift registers and data latches are operational in all four power saving modes; Inactive, Standby, R<sub>X</sub>, and Active Modes. Data can be loaded into the shift registers and latched into the latch registers in any of the operating modes.

Figure 10. Microprocessor Serial Interface Power-Up Delay

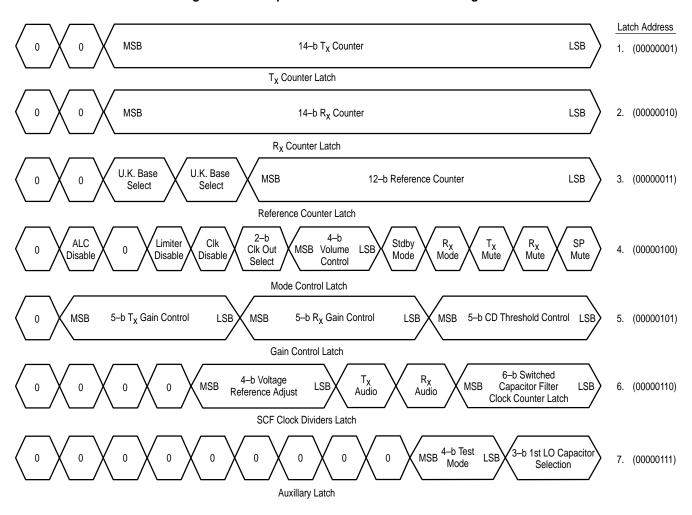

## **Data Registers**

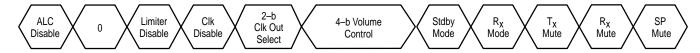

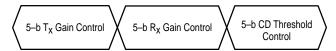

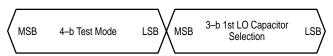

Figure 11 shows shows the data latch registers and addresses which are used to select each of these registers. Latch bits to the left (MSB) are loaded into the shift register first. The LSB bit must always be the last bit loaded into the shift register. Bits preceeding the register must be "0's" as shown in Figure 11.

Figure 11. Microprocessor Interface Data Latch Registers

Figure 12. Reference Frequency and Reference Divider Values

| Crystal<br>Frequency | Reference<br>Divider<br>Value | U.K. Base/<br>Handset<br>Divider | Reference<br>Frequency | SC Filter<br>Clock<br>Divider | SC Filter<br>Clock<br>Frequency |

|----------------------|-------------------------------|----------------------------------|------------------------|-------------------------------|---------------------------------|

| 10.24 MHz            | 2048                          | 1.0                              | 5.0 kHz                | 31                            | 165.16 kHz                      |

| 10.24 MHz            | 1024                          | 4.0                              | 2.5 kHz                | 31                            | 165.16 kHz                      |

| 11.15 MHz            | 2230                          | 1.0                              | 5.0 kHz                | 34                            | 163.97 kHz                      |

| 12.00 MHz            | 2400                          | 1.0                              | 5.0 kHz                | 36                            | 166.67 kHz                      |

| 11.15 MHz            | 1784                          | 1.0                              | 6.25 kHz               | 34                            | 163.97 kHz                      |

| 11.15 MHz            | 446                           | 4.0                              | 6.25 kHz               | 34                            | 163.97 kHz                      |

| 11.15 MHz            | 446                           | 25                               | 1.0 kHz                | 34                            | 163.97 kHz                      |

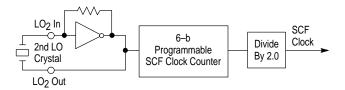

#### **Reference Frequency Selection**

The "LO2 In" and "LO2 Out" pins form a reference oscillator when connected to an external parallel—resonant crystal. The reference oscillator is also the second local oscillator for the RF Receiver. Figure 12 shows the relationship between different crystal frequencies and reference frequencies for cordless phone applications in various countries. "LO2 In" may also serve as an input for an externally generated reference signal which is ac—coupled. The switched capacitor filter 6—bit programmable counter must be programmed for the crystal frequency that is selected since this clock is derived from the crystal frequency and must be held constant regardless of the crystal that is selected. The actual switched capacitor clock divider ratio is twice the programmed divider ratio since there is a fixed divide by 2.0 after the programmable counter.

#### **Reference Counter**

Figure 13 shows how the reference frequencies for the  $R_X$  and  $T_X$  loops are generated. All countries except the U.K. require that the  $T_X$  and  $R_X$  reference frequencies be identical. In this case, set "U.K. Base Select" and "U.K. Handset