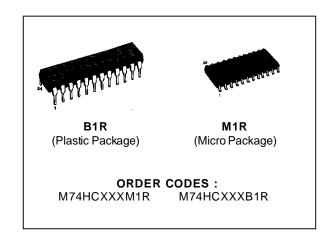

# M74HCT651 M74HCT652

## HCT651 OCTAL BUS TRANSCEIVER/REGISTER (3-STATE, INV.) HCT652 OCTAL BUS TRANSCEIVER/REGISTER (3-STATE)

- HIGH SPEED f<sub>MAX</sub> = 60 MHz (TYP.) AT V<sub>CC</sub> = 5V

- COMPATIBLE WITH TTL OUTPUTS V<sub>IH</sub> = 2 V (MIN.) AT V<sub>IL</sub> = 0.8V (MAX)

- LOW POWER DISSIPATION ICC = 4 µA (MAX) AT T<sub>A</sub> = 25 °C

- OUTPUT DRIVE CAPABILITY

15 LSTTL LOADS

- SYMMETRICAL OUTPUT IMPEDANCE | I<sub>OH</sub> | = I<sub>OL</sub> = 6 mA (mIN.)

- BALANCED PROPAGATION DELAYS tplh = tphl

- PIN AND FUNCTION COMPATIBLE WITH 54/74LS651/652

#### **DESCRIPTION**

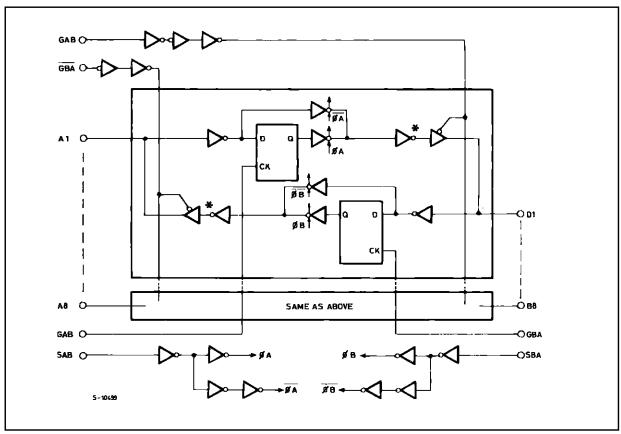

M74HCT651/652 are high speed CMOS OCTAL BUS TRANSCEIVERS AND REGISTERS (3-STATE), fabricated in silicon gate  $C^2MOS$  technology. They have the same high speed performance of LSTTL combined with true CMOS low power consumption. These devices consist of bus transceiver circuits, D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal storage registers. Enable GAB and GBA are provided to control the transceiver functions. Select AB and Select BA control pins are provided to select whether real-time or stored data is transfered. A low input level selects real-time data, and a high selects stored data. Data on the A or B bus, or both, can be stored in the internal D flip-flops by low-to-high transitions at the appropriate clock pins (CLOCK AB or CLOCK BA) regardless of the select or enable control pins. When select AB and select BA are in the real-time transfer mode, it is also possible to store data without using the internal D-type flip-flops by simultaneously enabling GAB and GBA. In this configuration each output reinforces its input. Thus, when all other data sources to the two sets of bus lines are at high impedance, each set of bus lines will remain at its last state. All inputs are equipped with protection circuits against static discharge and transient excess voltage. This integrated circuit has input and output characteristics that are fully compatible with 54/74 LSTTL logic families. M54/74HCT devices are designed to directly interface HSCMOS systems with TTL and NMOS components. They are also plug in replacements for LSTTL devices giving a reduction of power consumption.

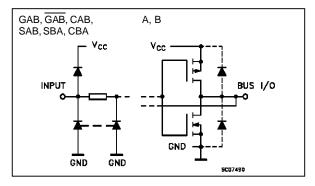

#### INPUT AND OUTPUT EQUIVALENT CIRCUIT

October 1993 1/12

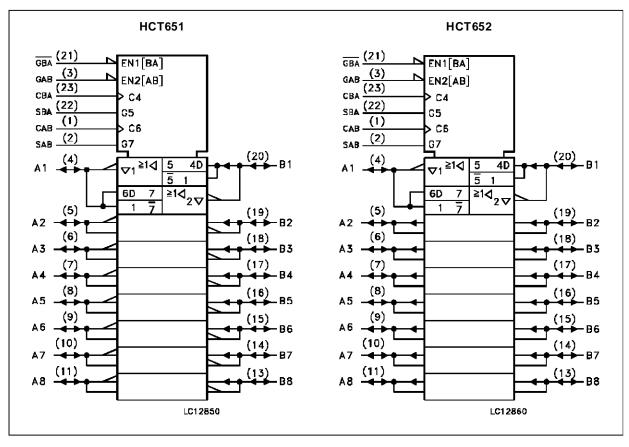

## **LOGIC DIAGRAM** (HCT651)

Note: In case of 74HCT652 output inverter marked \* at A bus and B bus are eliminated.

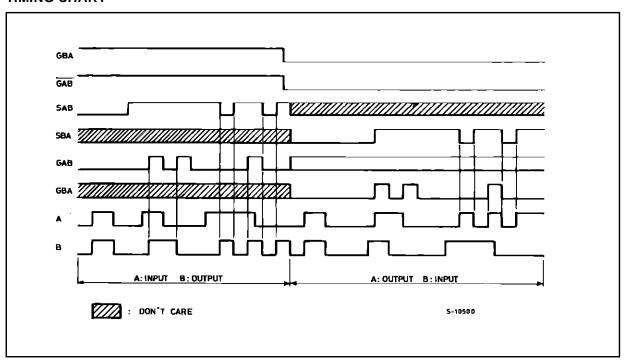

### **TIMING CHART**

**TRUTH TABLE**

HCT652 (The truth table for HCT651 is the same as this, but with the outputs inverted)

| GAB | GBA | CAB     | СВА | SAB | SBA | Α       | В       | FUNCTION                                                                                                                                          |

|-----|-----|---------|-----|-----|-----|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|     |     |         |     |     |     | INPUTS  | INPUTS  | Both the A bus and the B bus are inputs                                                                                                           |

|     | l   | Х       | Χ   | Χ   | Х   | Z       | Z       | The output functions of the A and B bus are disabled                                                                                              |

| L   | H   | $L_{I}$ |     | X   | X   | INPUTS  | INPUTS  | Both the A and B bus are used for inputs to the internal flip-flops. Data at the bus will be stored on low to high transition of the clock inputs |

|     |     |         |     |     |     | OUTPUTS | INPUTS  | The A bus are outputs and the B bus are inputs                                                                                                    |

|     |     | Χ*      | Χ   | Х   | L   | L       | L       | The data at the B bus are displayed at the A bus                                                                                                  |

|     |     |         |     |     |     | Н       | Н       |                                                                                                                                                   |

|     |     | Χ*      |     | Х   | L   | L       | L       | The data at the B bus ar displayed at the A bus.                                                                                                  |

| L   | L   |         |     |     |     | Н       | Н       | The data of the B bus are stored to the internal flip-flop on low to high transition of th clock pulse                                            |

|     |     | X*      | Х   | X   | Н   | Qn      | Х       | The data stored to the internal flip-flop are dispayed at the A bus                                                                               |

|     |     | Χ*      |     | Χ   | I   | L       | L       | The data at the B bus are stored to the internal flip-                                                                                            |

|     |     |         |     |     |     | н       | Н       | flop on low to high transition of the clock pulse. The states of the internal flip-flops output directly to the A bus                             |

|     |     |         |     |     |     | INPUTS  | OUTPUTS | The A bus are inputs and the B bus are outputs                                                                                                    |

|     |     | Х       | X*  | L   | Х   | L       | L       | The data at the A bus are displayed at the B bus                                                                                                  |

|     |     |         |     |     |     | Н       | Н       |                                                                                                                                                   |

|     |     | J       | Χ*  | L   | X   | L       | L       | The data at the A bus are displayed at the B bus.                                                                                                 |

| н   | н   |         |     |     |     | H       | Н       | The data of the A bus are stored to the internal flip-<br>flop on low to high transition of the clock pulse                                       |

|     |     | Х       | X*  | Ι   | Х   | X       | Qn      | The data stored to the internal flip-flops are displayed at the B bus                                                                             |

|     |     |         | Χ*  | Н   | X   | L       | L       | the data at the A bus are stored to the internal flip-                                                                                            |

|     |     |         |     |     |     | Н       | Н       | flop on low to high transition of the clock pulse. The states of the internal flip-flops output directly to the B bus                             |

|     |     |         |     |     |     | OUTPUTS | OUTPUTS | Both the A bus and the B bus are outputs                                                                                                          |

| Н   | L   | Х       | Х   | Н   | Н   | Qn      | Qn      | The data stored to the internal flip-flops are displayed at the A and B bus respactively                                                          |

|     |     | J       | 了   | Н   | Н   | Qn      | Qn      | The output at the A bus are displayed at the B bus, the output at the B bus are displayed at the A bus respectively                               |

<sup>:</sup> DON'T CARE

Z : HIGH IMPEDANCE

Qn : THE DATA STORED TO THE INTERNAL FLIP-FLOPS BY MOST RECENT LOW TO HIGH TRANSITION OF THE CLOCK INPUTS

: THE DATA AT THE A AND B BUS WILL BE STORED TO THE INTERNAL FLIP-FLOPS ON EVERY LOW TO HIGH TRANSITION OF THE CLOCK INPUTS

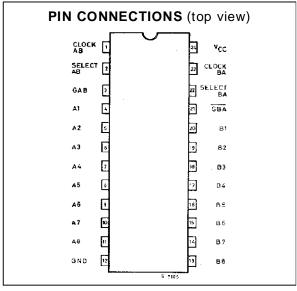

#### PIN DESCRIPTION

| PIN No                         | SYMBOL    | NAME AND FUNCTION                                |

|--------------------------------|-----------|--------------------------------------------------|

| 1                              | CLOCK AB  | A to B Clock Input (LOW to HIGH, Edge-Trigged)   |

| 2                              | SELECT AB | Select A to B Source Input                       |

| 3                              | GAB       | Direction Control Input                          |

| 4, 5, 6, 7, 8, 9, 10, 11       | A1 to A8  | A data Inputs/Outputs                            |

| 20, 19, 18, 17, 16, 15, 14, 13 | B1 to B8  | B Data Inputs/Outputs                            |

| 21                             | GBA       | Output Enable Input (Active LOW)                 |

| 22                             | SELECT BA | Select B to A Source Input                       |

| 23                             | CLOCK BA  | B to A Clock Input (LOW to HIGH, Edge-Triggered) |

| 12                             | GND       | Ground (0V)                                      |

| 24                             | Vcc       | Positive Supply Voltage                          |

#### **IEC LOGIC SYMBOLS**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                  | Parameter                                    | Value                         | Unit |

|-------------------------|----------------------------------------------|-------------------------------|------|

| Vcc                     | Supply Voltage                               | -0.5 to +7                    | V    |

| VI                      | DC Input Voltage                             | -0.5 to V <sub>CC</sub> + 0.5 | ٧    |

| Vo                      | DC Output Voltage                            | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| lıĸ                     | DC Input Diode Current                       | ± 20                          | mA   |

| I <sub>OK</sub>         | DC Output Diode Current                      | ± 20                          | mA   |

| lo                      | DC Output Source Sink Current Per Output Pin | ± 35                          | mA   |

| Icc or I <sub>GND</sub> | DC V <sub>CC</sub> or Ground Current         | ± 70                          | mA   |

| $P_{D}$                 | Power Dissipation                            | 500 (*)                       | mW   |

| T <sub>stg</sub>        | Storage Temperature                          | -65 to +150                   | °C   |

| TL                      | Lead Temperature (10 sec)                    | 300                           | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                          | Parameter                                                | Value                | Unit |

|---------------------------------|----------------------------------------------------------|----------------------|------|

| $V_{CC}$                        | Supply Voltage                                           | 4.5 to 5.5           | V    |

| VI                              | Input Voltage                                            | 0 to V <sub>CC</sub> | V    |

| Vo                              | Output Voltage                                           | 0 to V <sub>CC</sub> | V    |

| T <sub>op</sub>                 | Operating Temperature:                                   | -40 to +85           | °C   |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise and Fall Time (V <sub>CC</sub> = 4.5 to 5.5V) | 0 to 500             | ns   |

## **DC SPECIFICATIONS**

|                 | Parameter                            |                  | est Co                                   | nditions                                                       |                        |      |      |              |      |      |

|-----------------|--------------------------------------|------------------|------------------------------------------|----------------------------------------------------------------|------------------------|------|------|--------------|------|------|

| Symbol          |                                      |                  |                                          |                                                                | T <sub>A</sub> = 25 °C |      |      | -40 to 85 °C |      | Unit |

|                 |                                      | (V)              |                                          |                                                                | Min.                   | Тур. | Max. | Min.         | Max. |      |

| V <sub>IH</sub> | High Level Input Voltage             | 4.5<br>to<br>5.5 |                                          |                                                                | 2.0                    |      |      | 2.0          |      | V    |

| VIL             | Low Level Input<br>Voltage           | 4.5<br>to<br>5.5 |                                          |                                                                |                        |      | 0.8  |              | 0.8  | V    |

| Vон             | High Level Output Voltage            |                  | Vı =                                     | Ιο=-20 μΑ                                                      | 4.4                    | 4.5  |      | 4.4          |      |      |

|                 |                                      | 4.5              | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> =-6.0 mA                                        | 4.18                   | 4.31 |      | 4.13         |      | V    |

| Vol             | Low Level Output Voltage             |                  | Vı =                                     | I <sub>O</sub> = 20 μA                                         |                        | 0.0  | 0.1  |              | 0.1  |      |

|                 |                                      | 4.5              | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 6.0 mA                                        |                        | 0.17 | 0.26 |              | 0.33 | V    |

| II              | Input Leakage Current (*)            | 5.5              | V <sub>I</sub> = \                       | √ <sub>CC</sub> or GND                                         |                        |      | ±0.1 |              | ±1   | μΑ   |

| loz             | 3 State Output Off State Current     | 5.5              | V <sub>I</sub> = \                       | √ <sub>CC</sub> or GND                                         |                        |      | ±0.5 |              | ±5.0 | μΑ   |

| Icc             | Quiescent Supply Current             | 5.5              | V <sub>I</sub> = \                       | √ <sub>CC</sub> or GND                                         |                        |      | 1    |              | 10   | μΑ   |

| Δlcc            | Additional worst case supply current | 5.5              | V <sub>I</sub> :<br>V<br>Othe            | Input pin<br>= 0.5V or<br>1 = 2.4V<br>er Inputs at<br>c or GND |                        |      | 2.0  |              | 2.9  | mA   |

<sup>(\*):</sup> Applicable only to GAB, GBA, CAB, CBA, SAB, SBA input

## AC ELECTRICAL CHARACTERISTICS (Input $t_r = t_f = 6 \text{ ns}$ )

|                                      |                                                | To  | est Co | nditions          |      |                        |      |        |       |     |

|--------------------------------------|------------------------------------------------|-----|--------|-------------------|------|------------------------|------|--------|-------|-----|

| Symbol                               | Parameter                                      | Vcc | CL     |                   | Т    | T <sub>A</sub> = 25 °C |      | -40 to | 85 °C |     |

|                                      |                                                |     | (pF)   |                   | Min. | Тур.                   | Max. | Min.   | Max.  |     |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Output Transition Time                         | 4.5 | 50     |                   |      | 7                      | 12   |        | 15    | ns  |

| t <sub>PLH</sub>                     | Propagation Delay Time                         | 4.5 | 50     |                   |      | 20                     | 30   |        | 38    | ns  |

| t <sub>PHL</sub>                     | (BUS - BUS)                                    | 4.5 | 150    |                   |      | 25                     | 38   |        | 48    | ns  |

| t <sub>PLH</sub>                     | Propagation Delay Time                         | 4.5 | 50     |                   |      | 29                     | 44   |        | 55    | ns  |

| t <sub>PHL</sub>                     | (CLOCK - BUS)                                  | 4.5 | 150    |                   |      | 34                     | 52   |        | 65    | ns  |

| t <sub>PLH</sub>                     | Propagation Delay Time                         |     | 50     |                   |      | 24                     | 34   |        | 43    | ns  |

| t <sub>PHL</sub>                     | (SELECT - BUS)                                 | 4.5 | 150    |                   |      | 29                     | 42   |        | 53    | ns  |

| t <sub>PZL</sub>                     | 3-State Output Enable Time                     | 4.5 | 50     | $R_L = 1 K\Omega$ |      | 22                     | 33   |        | 41    | ns  |

| t <sub>PZH</sub>                     | (GAB, GBA - BUS)                               | 4.5 | 150    | $R_L = 1 K\Omega$ |      | 27                     | 41   |        | 51    | ns  |

| t <sub>PLZ</sub><br>t <sub>PHZ</sub> | Output <u>Disable Time</u><br>(GAB, GBA - BUS) | 4.5 | 50     | $R_L = 1 K\Omega$ |      | 24                     | 35   |        | 44    | ns  |

| f <sub>MAX</sub>                     | Maximum Clock Frequency                        | 4.5 | 50     |                   | 31   | 55                     |      | 25     |       | MHz |

| t <sub>W(H)</sub>                    | Minimum Clock Pulse Width                      | 4.5 | 50     |                   |      | 8                      | 15   |        | 19    | ns  |

| ts                                   | Minimum Set-up Time                            | 4.5 | 50     |                   |      | 3                      | 10   |        | 13    | ns  |

| th                                   | Minimum Hold Time                              | 4.5 | 50     |                   |      |                        | 5    |        | 5     | ns  |

| C <sub>IN</sub>                      | Input Capacitance                              |     |        |                   |      | 5                      | 10   |        | 10    | pF  |

| C <sub>I/O</sub>                     | Bus Terminal Capacitance                       |     |        |                   |      | 13                     |      |        |       | pF  |

| C <sub>PD</sub> (*)                  | Power Dissipation Capacitance                  |     |        | HCT651<br>HCT652  |      | 38<br>39               |      |        |       | pF  |

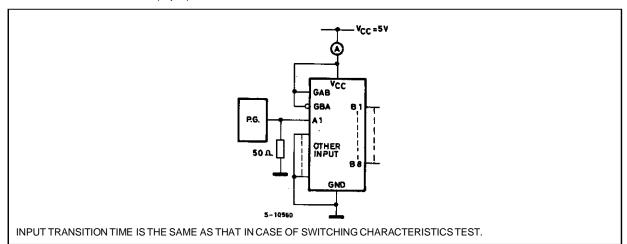

<sup>(\*)</sup>  $C_{PD}$  is defined as the value of the IC's internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation.  $I_{CC}(opr) = C_{PD} \bullet V_{CC} \bullet f_{IN} + I_{CC}/8$  (per Channel)

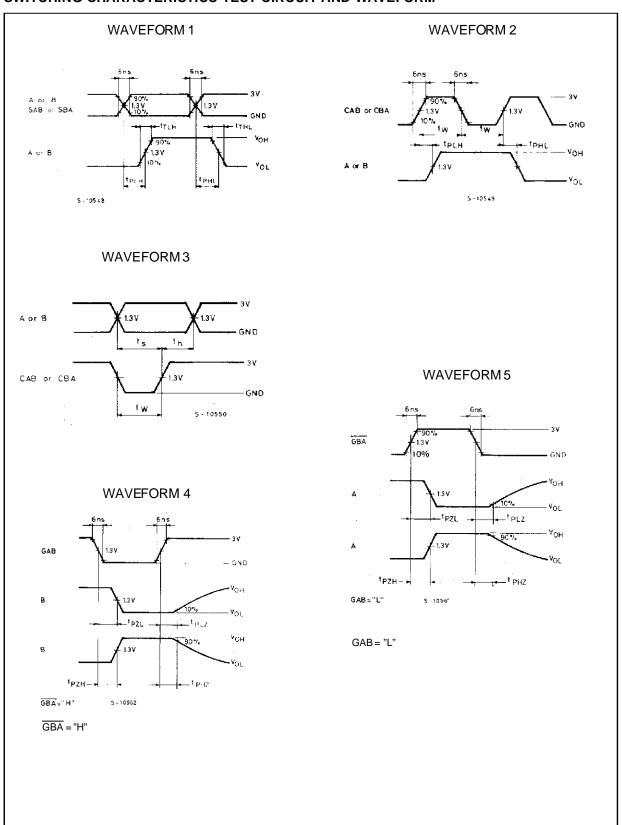

#### SWITCHING CHARACTERISTICS TEST CIRCUIT AND WAVEFORM

## TEST WAVEFORM Icc (Opr.)

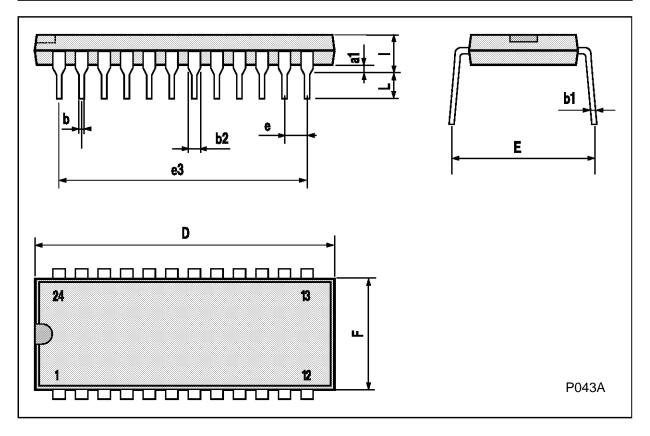

# Plastic DIP24 (0.25) MECHANICAL DATA

| DIM. |      | mm    |       | inch  |       |       |  |  |  |

|------|------|-------|-------|-------|-------|-------|--|--|--|

|      | MIN. | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |  |  |  |

| a1   |      | 0.63  |       |       | 0.025 |       |  |  |  |

| b    |      | 0.45  |       |       | 0.018 |       |  |  |  |

| b1   | 0.23 |       | 0.31  | 0.009 |       | 0.012 |  |  |  |

| b2   |      | 1.27  |       |       | 0.050 |       |  |  |  |

| D    |      |       | 32.2  |       |       | 1.268 |  |  |  |

| E    | 15.2 |       | 16.68 | 0.598 |       | 0.657 |  |  |  |

| е    |      | 2.54  |       |       | 0.100 |       |  |  |  |

| e3   |      | 27.94 |       |       | 1.100 |       |  |  |  |

| F    |      |       | 14.1  |       |       | 0.555 |  |  |  |

| I    |      | 4.445 |       |       | 0.175 |       |  |  |  |

| L    |      | 3.3   |       |       | 0.130 |       |  |  |  |

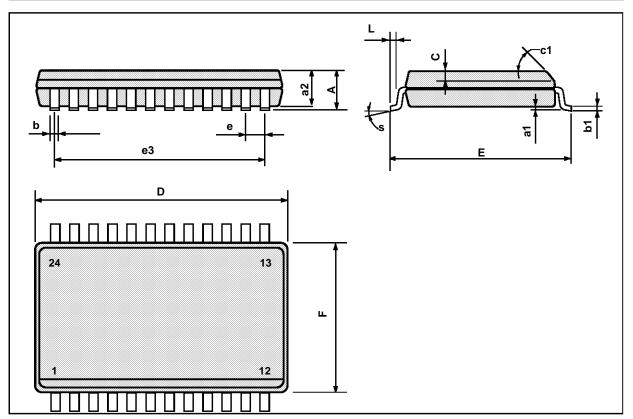

## **SO24 MECHANICAL DATA**

| DIM.   |       | mm        |       | inch   |       |       |  |  |

|--------|-------|-----------|-------|--------|-------|-------|--|--|

| Dilvi. | MIN.  | MIN. TYP. |       | MIN.   | TYP.  | MAX.  |  |  |

| А      |       |           | 2.65  |        |       | 0.104 |  |  |

| a1     | 0.10  |           | 0.20  | 0.004  |       | 0.007 |  |  |

| a2     |       |           | 2.45  |        |       | 0.096 |  |  |

| b      | 0.35  |           | 0.49  | 0.013  |       | 0.019 |  |  |

| b1     | 0.23  |           | 0.32  | 0.009  |       | 0.012 |  |  |

| С      |       | 0.50      |       |        | 0.020 |       |  |  |

| c1     |       | •         | 45° ( | (typ.) | •     |       |  |  |

| D      | 15.20 |           | 15.60 | 0.598  |       | 0.614 |  |  |

| E      | 10.00 |           | 10.65 | 0.393  |       | 0.420 |  |  |

| е      |       | 1.27      |       |        | 0.05  |       |  |  |

| e3     |       | 13.97     |       |        | 0.55  |       |  |  |

| F      | 7.40  |           | 7.60  | 0.291  |       | 0.299 |  |  |

| L      | 0.50  |           | 1.27  | 0.19   |       | 0.050 |  |  |

| S      |       |           | 8° (r | nax.)  |       |       |  |  |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectonics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A