# 3.3V-5V 4 Mbit (512Kb x 8) TIMEKEEPER® SRAM

**DATA BRIEFING**

- INTEGRATED ULTRA LOW POWER SRAM, REAL TIME CLOCK, POWER-FAIL CONTROL CIR CUIT, BATTERY, AND CRYSTAL

- BCD CODED YEAR, MONTH, DAY, DATE, HOURS, MINUTES, and SECONDS

- AUTOMATIC POWER-FAIL CHIP DESELECT and WRITE PROTECTION

- WRITE PROTECT VOLTAGES: (VPFD = Power-fail Deselect Voltage)

- $M48T512Y: 4.10V \le V_{PFD} \le 4.5V$

- M48T512V:  $2.7V \le V_{PFD} \le 3.0V$

- CONVENTIONAL SRAM OPERATION; UNLIMITED WRITE CYCLES

- SOFTWARE CONTROLLED CLOCK CALIBRATION FOR HIGH ACCURACY APPLICATIONS

- 10 YEARS of DATA RETENTION and CLOCK OPERATION in the ABSENCE OF POWER

- PIN and FUNCTION COMPATIBLE with INDUSTRY STANDARD 512K X 8 SRAMS

- SELF-CONTAINED BATTERY and CRYSTAL in DIP PACKAGE

#### **DESCRIPTION**

The M48T512Y/V TIMEKEEPER® RAM is a 512Kb x 8 non-volatile static RAM and real time clock organized as 524,288 words by 8 bits. The special DIP package provides a fully integrated battery back-up memory and real time clock solution.

The M48T512Y/V directly replaces industry standard 512Kb x 8 SRAMs. It also provides the non-volatility of Flash without any requirement for special write timing or limitations on the number of writes that can be performed.

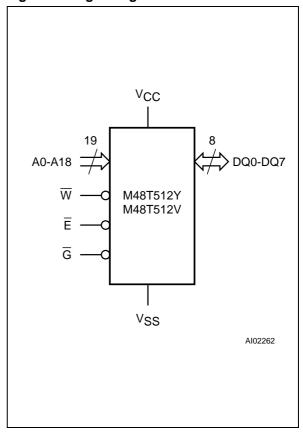

Figure 1. Logic Diagram

B48T512/806 1/2

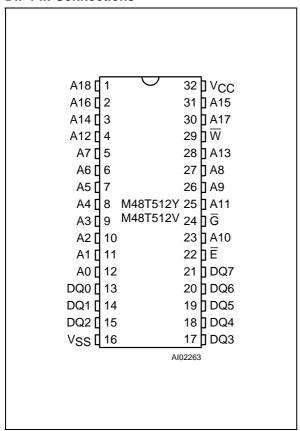

#### **DIP Pin Connections**

Note: NC = Not Connected.

## **Signal Names**

| A0-A18          | Address Inputs        |

|-----------------|-----------------------|

| DQ0-DQ7         | Data Inputs / Outputs |

| Ē               | Chip Enable Input     |

| G               | Output Enable Input   |

| W               | Write Enable Input    |

| V <sub>CC</sub> | Supply Voltage        |

| V <sub>SS</sub> | Ground                |

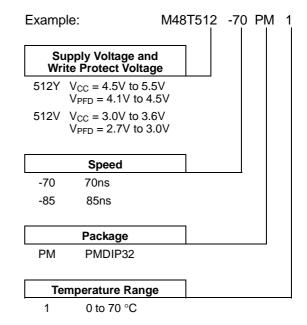

### **Ordering Information Scheme**

For a list of available options or for further information on any aspect of this device, please contact the STMicroelectronics Sales Office nearest to you.

2/2