# REFERENCE

SPEC No. | E L 0 8 Y 0 4 5 ISSUE: Nov. 11 1996

| T | 0 | ; |  |  |  |

|---|---|---|--|--|--|

|   |   |   |  |  |  |

|       | SPEC              | IFICATIONS                                                                                               |    |

|-------|-------------------|----------------------------------------------------------------------------------------------------------|----|

| Prod  | uct Type 16       | M Flash File Memory                                                                                      |    |

|       | LH2               | 8 F 0 1 6 S A T - 7 0                                                                                    |    |

| Mod   | el No             | (LHF16S17)                                                                                               |    |

|       | ou have any objec | contains <u>45</u> pages including the cover and appe<br>ctions, please contact us before issuing purcha |    |

| DATE: |                   | _                                                                                                        |    |

| BY:   |                   | PRESENTED  BY: Sanaba  S. Tanaka  Dept. General Manager                                                  |    |

|       |                   | REVIEWED BY: PREPARED B                                                                                  | Y: |

Engineering Dept. 2

Flash Memory Development Center Tenri Integrated Circuits Group

y Oshiha T- Joshida

SHARP CORPORATION

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- ·Office electronics

- ·Instrumentation and measuring equipment

- · Machine tools

- · Audiovisual equipment

- · Home appliance

- ·Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- ·Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- · Mainframe computers

- ·Traffic control systems

- ·Gas leak detectors and automatic cutoff devices

- ·Rescue and security equipment

- ·Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- · Aerospace equipment

- ·Communications equipment for trunk lines

- ·Control equipment for the nuclear power industry

- · Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- Please direct all queries regarding the products covered herein to a sales representative of the company.

# LH28F016SAT-70 16 Mbit (1 Mbit x 16, 2 Mbit x 8) Flash Memory

| CONTENTS                         | PAGE        | CONTENTS                      | PAGE               |

|----------------------------------|-------------|-------------------------------|--------------------|

| FEATURES                         | 2           | 5.0 ELECTRICAL SPECIFICATIO   | NS 17              |

|                                  |             | 5.1 Absolute Maximum Ratir    | ngs 17             |

| 1.0 INTRODUCTION                 | 3           | 5.2 Capacitance               | 18                 |

| 1.1 Product Overview             | 3           | 5.3 Timing Nomenclature       | 19                 |

|                                  |             | 5.4 DC Characteristics:       |                    |

| 2.0 DEVICE PINOUT                | 5           | Commercial Temperature        | e 22               |

| 2.1 Lead Descriptions            | 7           | 5.5 DC Characteristics:       |                    |

|                                  |             | Commercial Temperatur         | e 24               |

| 3.0 MEMORY MAPS                  | 9           | 5.6 AC Characteristics -Read  | d Only Operations: |

| 3.1 Extended Status Register Men | nory Map 10 | Commercial Temperature        | 26                 |

|                                  |             | 5.7 Power-Up and Reset Tim    | ings 30            |

| 4.0 BUS OPERATIONS, COMMANDS     |             | 5.8 AC Characteristics for W  | E# -Controlled     |

| AND STATUS REGISTER              |             | Command Operations:           |                    |

| DEFINITIONS                      | 11          | Commercial Temperature        | <b>∍</b> 31        |

| 4.1 Bus operations for Word-Wide | Mode        | 5.9 AC Characteristics for C  | E# -Controlled     |

| (Byte#=V <sub>IH</sub> )         | 11          | Command Operations:           |                    |

| 4.2 Bus operations for Byte-Wide | Mode        | Commercial Temperature        | ∍ 34               |

| (Byte#=V <sub>IL</sub> )         |             | 5.10 AC Characteristics for P | age Buffer Write   |

| 4.3 LH28F008SA -Compatible Mod   |             | Operations: Commercial        | Temperature 37     |

| Bus Definitions                  | 12          | 5.11Erase and Word/Byte Wr    | ite performance,   |

| 4.4 LH28F016SUT-10 -Performanc   | e           | Cycling performance           |                    |

| <b>Enhancement Command Bus</b>   |             | and Suspend Latency           | 39                 |

| Definitions                      |             | 6.0 PACKAGE AND PACKING       |                    |

| 4.5 Compatible Status Register   | 14          | SPECIFICATION                 | 40                 |

| 4.6 Global Status Register       | 15          |                               |                    |

| 4.7 Block Status Bogistor        | 16          |                               |                    |

# LH28F016SAT-70 16 MBIT (1 MBIT x 16, 2 MBIT x 8) FLASH MEMORY

#### **FEATURES**

- User-Selectable 3.3V or 5V V<sub>cc</sub>

- User-Configurable x8 or x16 Operation

- 70 ns Maximum Access Time

- 0.43 MB/sec Write Transfer Rate

- 100 Thousand Erase Cycles per Block

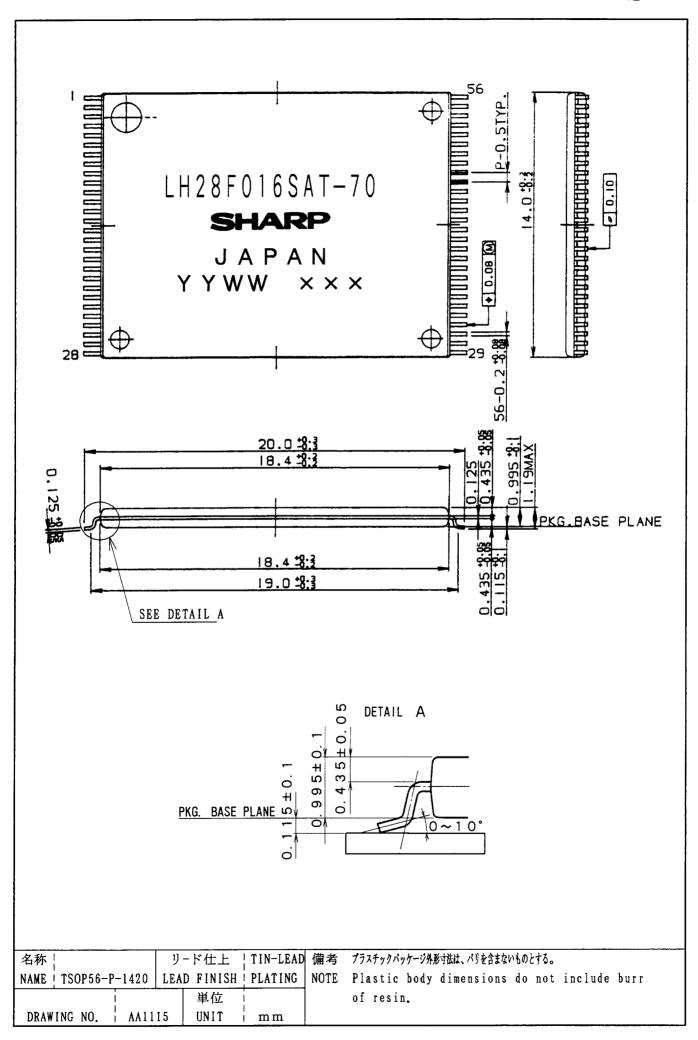

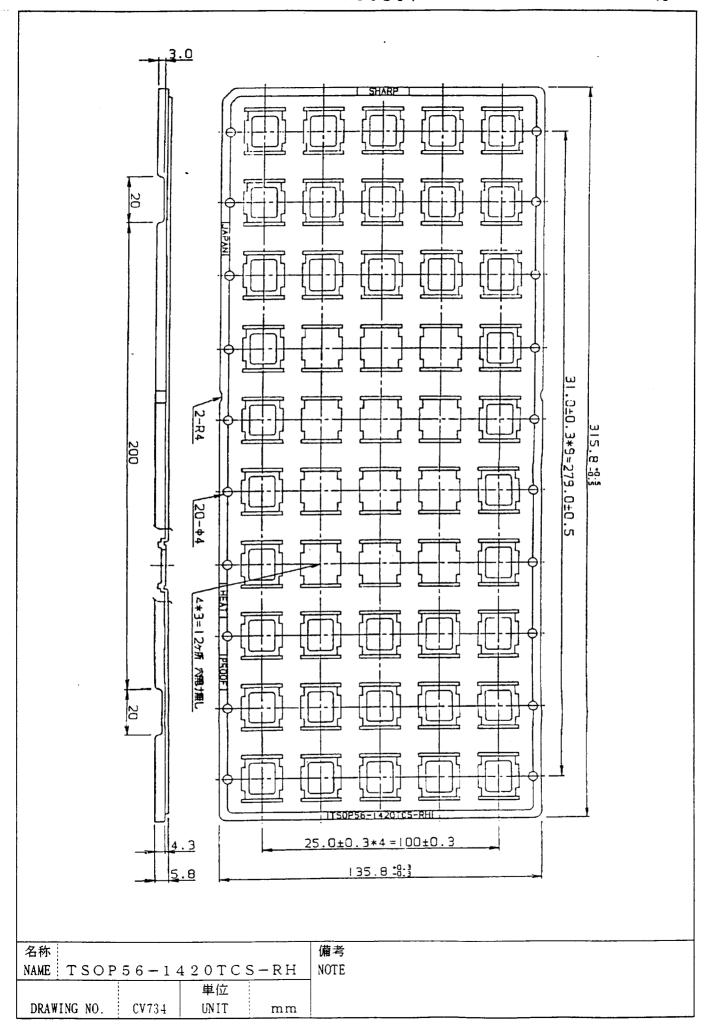

- 56-Lead, 1.2mm x 14mm x 20mm TSOP Package (STANDARD PINOUT)

- Revolutionary Architecture

- Pipelined Command Execution

- Write During Erase

- Command Superset of Sharp LH28F008SA

- 50 μA (TYP.) I<sub>cc</sub> in CMOS Standby

- 1 µA (TYP.) Deep Power-Down

- 32 Independently Lockable Blocks

- State-of-the-Art 0.55 μm ETOX<sup>™\*</sup> Flash Technology

- · Not designed or rated as radiation hardened

Sharp's LH28F016SAT-70 16-Mbit Flash Memory is a revolutionary architecture which enables the design of truly mobile, high performance, personal computing and communication products. With innovative capabilities and very high read/write performance, the LH28F016SAT-70 is also the ideal choice for designing embedded mass storage flash memory systems.

The LH28F016SAT-70 is a very high density, highest performance non-volatile read/write solution for solid-state storage applications. Its symmetrically blocked architecture (100% compatible with the LH28F008SA 8-Mbit Flash memory), extended cycling, low power 3.3V operation, very fast write and read performance and selective block locking provide a highly flexible memory component suitable for high density memory cards, Resident Flash Arrays and PCMCIA-ATA Flash Drives. The LH28F016SAT-70's dual read voltage enables the design of memory cards which can interchangeably be read/written in 3.3V and 5.0V systems. Its x8/x16 architecture allows the optimization of memory to processor interface. The flexible block locking option enables bundling of executable application software in a Resident Flash Array or memory card. Manufactured on Sharp's 0.55 μm ETOX<sup>™</sup> process technology, the LH28F016SAT-70 is the most cost-effective, high-density flash memory.

| * ETOX is a trademark of Intel corporation. |  |  |

|---------------------------------------------|--|--|

|                                             |  |  |

|                                             |  |  |

# 1.0 INTRODUCTION

The specifications intended to give an overview of the chip feature-set and of the operating AC/DC specifications. Please refer to User's Manual also, to learn detail usage.

#### 1.1 Product Overview

The LH28F016SAT-70 is a high performance 16 Mbit (16,777,216 bit) block erasable non-volatile random access memory organized as either 1 Mword x 16 or 2 Mbyte x 8. The LH28F016SAT-70 includes sixteen 64 KB (65,536) blocks or sixteen 32-KW (32,768) blocks. A chip memory map is shown in Figure 3.

The implementation of a new architecture, with many enhanced features, will improve the device operating characteristics and results in greater product reliability and ease of use.

Among the significant enhancements of the LH28F016SAT-70:

- · 3.3V Low Power Capability

- Improved Write Performance

- Dedicated Block Write/Erase Protection

A 3/5# input pin reconfigures the device internally for optimized 3.3V or 5.0V read/write operation.

The LH28F016SAT-70 will be available in a 56-lead, 1.2mm thick, 14mm x 20mm TSOP type I package (STANDARD PINOUT). This form factor and pinout allow for very high board layout densities.

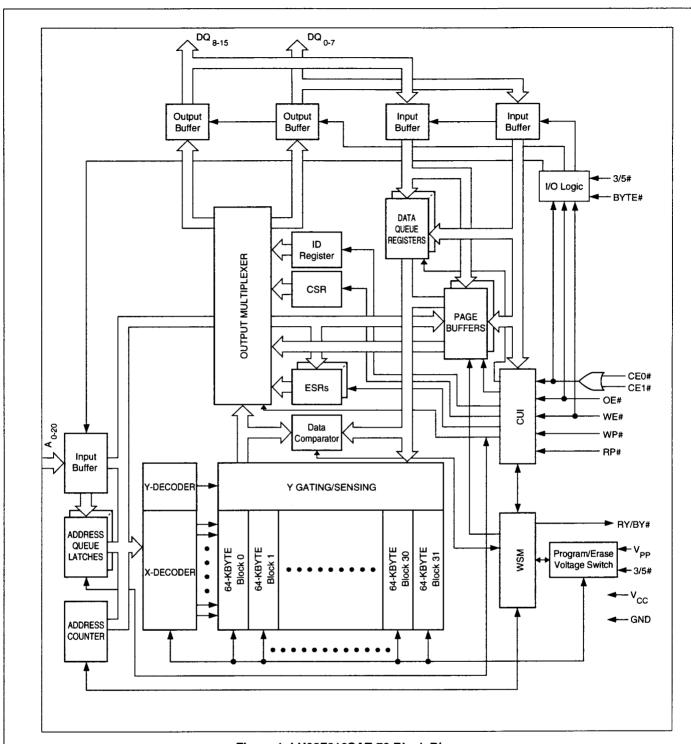

A Command User Interface (CUI) serves as the system interface between the microprocessor or microcontroller and the internal memory operation.

Internal Algorithm Automation allows Byte/Word Writes and Block Erase operations to be executed using a Two-Write command sequence to the CUI in the same way as the LH28F008SA 8-Mbit Flash memory.

A Superset of commands have been added to the basic LH28F008SA command-set to achieve higher write performance and provide additional capabilities. These new commands and features include:

- · Page Buffer Writes to Flash

- · Command Queuing Capability

- · Automatic Data Writes During Erase

- Software Locking of Memory Blocks

- Two-Byte Successive Writes in 8-bit Systems

- · Erase All Unlocked Blocks

Writing of memory data is performed in either byte or word increments typically within 6  $\mu$ sec, a 33% improvement over the LH28F008SA. A Block Erase operation erases one of the 32 blocks in typically 0.6 sec, independent of the other blocks, which is about 65% improvement over the LH28F008SA.

The LH28F016SAT-70 incorporates two Page Buffers of 256 Bytes (128 Words) each to allow page data writes. This feature can improve a system write performance over previous flash memory devices.

All operations are started by a sequence of Write commands to the device. Three Status Registers (described in detail later) and a RY/BY# output pin provide information on the progress of the requested operation.

While the LH28F008SA requires an operation to complete before the next operation can be requested, the LH28F016SAT-70 allows queuing of the next operation while the memory executes the current operation. This eliminates system overhead when writing several bytes in a row to the array or erasing several blocks at the same time. The LH28F016SAT-70 can also perform write operations to one block of memory while performing erase of another block.

The LH28F016SAT-70 provides user-selectable block locking to protect code or data such as Device Drivers, PCMCIA card information, ROM-Executable O/S or Application Code. Each block has an associated non-volatile lock-bit which determines the lock status of the block. In addition, the LH28F016SAT-70 incorporates Master Write Protection Pin(WP#). When WP# turns  $V_{\rm IL}$  after Block Lock command was issued, the device realizes Block Lock capability. When WP# is  $V_{\rm IH}$ , any Write or Erase operation can be performed in spite of Block Lock status. When WP# is  $V_{\rm IL}$ , please note following points.

- 1.When WP# is  $V_{\rm IL}$ , any execution for Block Lock command. It is accomplished by keeping WP#  $V_{\rm IH}$  to execute Block Lock command.

- 2. When WP# is V<sub>IL</sub> and also if power off occurs or Reset, Abort command is issued during executing Erase operation, there is a possibility that the Block in which Erase operation is in progress turns to protected Block and succeeding Erase/Write operation in that Block can not be executed. In this case, turn WP# to V<sub>IH</sub> and also execute Block Erase operation for that Block or execute Full chip Erase operation.

The LH28F016SAT-70 contains three types of Status Registers to accomplish various functions:

- A Compatible Status Register (CSR) which is 100% compatible with the LH28F008SA Flash memory's Status Register. This register, when used alone, provides a straightforward upgrade capability to the LH28F016SAT-70 from a LH28F008SA-based design.

- A Global Status Register (GSR) which informs the system of command Queue status, Page Buffer status, and overall Write State Machine (WSM) status.

- 32 Block Status Registers (BSRs) which provide block-specific status information such as the block lock-bit status.

The GSR and BSR memory maps for Byte-Wide and Word-Wide modes are shown in Figures 4.1 and 4.2.

The LH28F016SAT-70 incorporates an open drain RY/BY# output pin. This feature allows the user to OR-tie many RY/BY# pins together in a multiple memory configuration such as a Resident Flash Array.

The LH28F016SAT-70 also incorporates a dual chipenable function with two input pins, CE<sub>0</sub># and CE<sub>1</sub>#. These pins have exactly the same functionality as the regular chip-enable pin CE# on the LH28F008SA. For minimum chip designs, CE<sub>1</sub># may be tied to ground and use CE<sub>0</sub># as the chip enable input. The LH28F016SAT-70 uses the logical combination of these two signals to enable or disable the entire chip. Both CE<sub>0</sub># and CE<sub>1</sub># must be active low to enable the device and if either one becomes inactive, the chip will be disabled. This feature, along with the open drain RY/BY# pin, allows the system designer to reduce the number of control pins used in a large array of 8-Mbit devices.

The BYTE# pin allows either x8 or x16 read/writes to the LH28F016SAT-70. BYTE# at logic low selects 8-bit mode with address  $A_0$  selecting between low byte and high byte. On the other hand, BYTE# at logic high enables 16-bit operation with address  $A_1$  becoming the lowest order address and address  $A_0$  is not used (don't care). A device diagram is shown in Figure 1.

The LH28F016SAT-70 is specified for a maximum access time of each version, as follows:

#### LH28F016SAT-70

| <b>Operating Temperature</b> | Vcc Suply     | Max. Access (tacc) |

|------------------------------|---------------|--------------------|

| 0 - 70 °C                    | 4.75 - 5.25 V | 70 ns              |

| 0 - 70 °C                    | 4.5 - 5.5 V   | 80 ns              |

| 0 - 70 °C                    | 3.0 - 3.6 V   | 120 ns             |

The LH28F016SAT-70 incorporates an Automatic Power Saving (APS) feature which substantially reduces the active current when the device is in static mode of operation (addresses not switching).

In APS mode, the typical  $I_{cc}$  current is 2 mA at 5.0V (1 mA at 3.3V).

A Deep Power-Down mode of operation is invoked when the RP# (called PWD# on the LH28F008SA) pin transitions low, any current operation is aborted and the device is put into the deep power-down mode. This mode brings the device power consumption to less than 5 μA, typically, and provides additional write protection by acting as a device reset pin during power transitions. When the power is turned on, RP# pin turned to low order to return the device to default configuration. When the 3/5# pin is switched, or when the power transition is occurred, or at the power on/off, RP# is required to stay low in order to protect data from noise. A recovery time of 400ns (Vcc=5.0V±0.25V) is required from RP# switching high until outputs are again valid. In the Deep Power-Down state, the WSM is reset (any current operation will abort) and the CSR, GSR and BSR registers are cleared.

A CMOS Standby mode of operation is enabled when either  $CE_0\#$  or  $CE_1\#$  transitions high and RP# stays high with all input control pins at CMOS levels. In this mode, the device typically draws an  $I_{cc}$  standby current of 10  $\mu$ A.

Please do not execute reprogramming "0" for the bit which has already been programed "0". Overwrite operation may generate unerasable bit. In case of reprogramming "0" to the data which has been programed "1".

- •Program "0" for the bit in which you want to change data from "1" to "0".

- Program "1" for the bit which has already been programmed "0".

For example, changing data from "10111101" to "10111100" requires "11111110" programming.

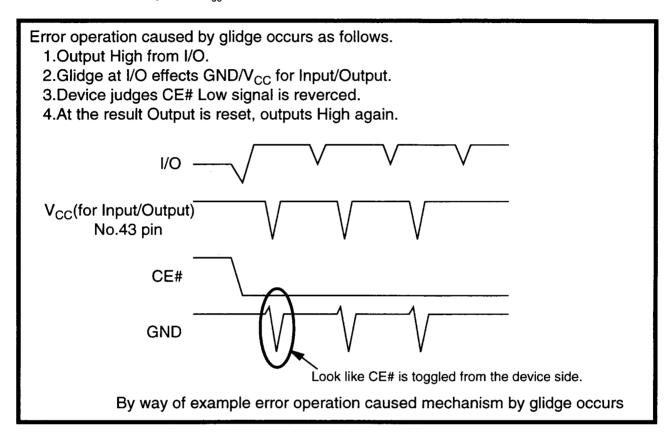

When you use LH28F016SAT-70, please note following points related to output buffer. When the device is in the reading mode, High-Low-High glidge may occurs (It is whithin the access time, not operation error.) In case of the device is used for application in which the GND/ $V_{\rm cc}$  from system is tied by high-inductance connector or flat cable such as memory card,  $V_{\rm cc}$  current which is

generated by the glidge induces voltage difference at  $\mathrm{GND/V_{cc}}$  between system and device. The detail mechanism is showed in following chart. In these kinds application,  $\mathrm{GND/V_{cc}}$  pin (No.42, No.43) should be connected to a single line from outside.  $\mathrm{GND/V_{cc}}$  lines from other devices should not be mixed.

#### 2.0 DEVICE PINOUT

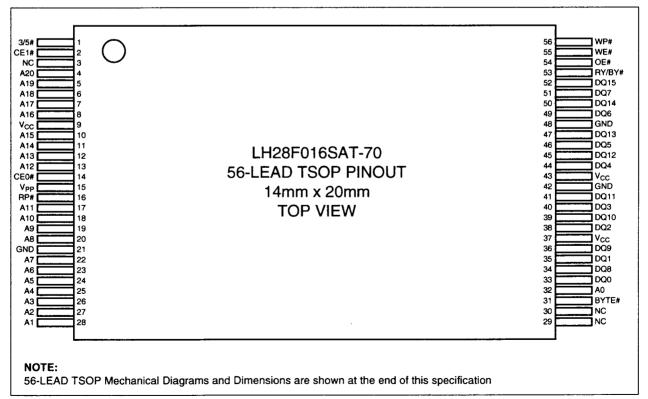

The LH28F016SAT-70 56L-TSOP Type I pinout configuration is shown in Figure 2.

Figure 1. LH28F016SAT-70 Block Diagram

Architectural Evolution Includes Page Buffers, Queue Registers and Extended Status Registers.

# 2.1 Lead Descriptions

| Symbol                               | Туре                 | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub>                       | INPUT                | BYTE-SELECT ADDRESS: Selects between high and low byte when device is in x8 mode. This address is latched in x8 Data Writes. Not used in x16 mode (i.e., the A <sub>0</sub> input buffer is turned off when BYTE# is high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A <sub>1</sub> -A <sub>15</sub>      | INPUT                | WORD-SELECT ADDRESSES: Select a word within one 64-Kbyte block. A <sub>6-15</sub> selects 1 of 1024 rows, and A <sub>1-5</sub> selects 16 of 512 columns. These addresses are latched during Data Writes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A <sub>16</sub> -A <sub>20</sub>     | INPUT                | BLOCK-SELECT ADDRESSES: Select 1 of 32 Erase blocks. These addresses are latched during Data Writes, Erase and Lock-Block operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DQ <sub>0</sub> -DQ <sub>7</sub>     | INPUT/OUTPUT         | LOW-BYTE DATA BUS: Inputs data and commands during CUI write cycles. Outputs array, buffer, identifier or status data in the appropriate Read mode. Floated when the chip is de-selected or the outputs are disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DQ <sub>8</sub> -DQ <sub>15</sub>    | INPUT/OUTPUT         | HIGH-BYTE DATA BUS: Inputs data during x16 Data-Write operations. Outputs array, buffer or identifier data in the appropriate Read mode; not used for Status register reads. Floated when the chip is de-selected or the outputs are disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CE <sub>0</sub> #, CE <sub>1</sub> # | INPUT                | CHIP ENABLE INPUTS: Activate the device's control logic, input buffers, decoders and sense amplifiers. With either CE <sub>0</sub> # or CE <sub>1</sub> # high, the device is de-selected and power consumption reduces to Standby levels upon completion of any current Data-Write or Erase operations. Both CE <sub>0</sub> #, CE <sub>1</sub> # must be low to select the device.  All timing specifications are the same for both signals. Device Selection occurs with the latter falling edge of CE <sub>0</sub> # or CE <sub>1</sub> #. The first rising edge of CE <sub>0</sub> # or CE <sub>1</sub> # disables the device.                                                                                                                                                              |

| RP#                                  | INPUT                | <b>RESET/POWER-DOWN:</b> With RP# low, the device is reset, any current operation is aborted and device is put into the deep power down mode. When the power is turned on, RP# pin is turned to low in order to return the device to default configuration. When the 3/5# pin is switched, or when the power transition is occurred, or at the power on/off, RP# is required to stay low in order to protect data from noise. When returning from Deep Power-Down, a recovery time of 400ns (Vcc=5.0V $\pm$ 0.25V) is required to allow these circuits to power-up. When RP# goes low, any current or pending WSM operation(s) are terminated, and the device is reset. All Status registers return to ready (with all status flags cleared). After returning, the device is in read array mode. |

| OE#                                  | INPUT                | OUTPUT ENABLE: Gates device data through the output buffers when low. The outputs float to tri-state off when OE# is high.  NOTE: CE <sub>X</sub> # overrides OE#, and OE# overrides WE#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WE#                                  | INPUT                | WRITE ENABLE: Controls access to the CUI, Page Buffers, Data Queue Registers and Address Queue Latches. WE# is active low, and latches both address and data (command or array) on its rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RY/BY#                               | OPEN DRAIN<br>OUTPUT | <b>READY/BUSY:</b> Indicates status of the internal WSM. When low, it indicates that the WSM is busy performing an operation. RY/BY# high indicates that the WSM is ready for new operations (or WSM has completed all pending operations), or Erase is Suspended, or the device is in deep power-down mode. This output is always active (i.e., not floated to tri-state off when OE# or CE <sub>0</sub> #, CE <sub>1</sub> # are high), except if a RY/BY# Pin Disable command is issued.                                                                                                                                                                                                                                                                                                      |

# 2.1 Lead Descriptions (Continued)

| Symbol          | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WP#             | INPUT  | WRITE PROTECT: Erase blocks can be locked by writing a non-volatile lock-bit for each block. When WP# is low, those locked blocks as reflected by the Block-Lock Status bits (BSR.6), are protected from inadvertent Data Writes or Erases. When WP# is high, all blocks can be Written or Erased regardless of the state of the lock-bits. The WP# input buffer is disabled when RP# transitions low (deep power-down mode). |

| BYTE#           | INPUT  | <b>BYTE ENABLE:</b> BYTE# low places device in x8 mode. All data is then input or output on DQ <sub>0-7</sub> , and DQ <sub>8-15</sub> float. Address Ao selects between the high and low byte. BYTE# high places the device in x16 mode, and turns off the $A_0$ input buffer. Address $A_1$ , then becomes the lowest order address.                                                                                        |

| 3/5#            | INPUT  | 3.3/5.0 VOLT SELECT: 3/5# high configures internal circuits for 3.3V operation. 3/5# low configures internal circuits for 5.0V operation. NOTES: Reading the array with 3/5# high in a 5.0V system could damage the device. There is a significant delay from 3/5# switching to valid data.                                                                                                                                   |

| V <sub>PP</sub> | SUPPLY | ERASE/WRITE POWER SUPPLY: For erasing memory array blocks or writing words/bytes/pages into the flash array.                                                                                                                                                                                                                                                                                                                  |

| Vcc             | SUPPLY | DEVICE POWER SUPPLY (3.3V $\pm$ 0.3V, 5.0V $\pm$ 0.5V): Do not leave any power pins floating.                                                                                                                                                                                                                                                                                                                                 |

| GND             | SUPPLY | GROUND FOR ALL INTERNAL CIRCUITRY: Do not leave any ground pins floating.                                                                                                                                                                                                                                                                                                                                                     |

| NC              |        | NO CONNECT: No internal connection to die, lead may be driven or left floating.                                                                                                                                                                                                                                                                                                                                               |

Figure 2. TSOP Configuration

#### 3.0 MEMORY MAPS 1FFFFFH 64 KByte Block 31 1F0000H 1EFFFFH 30 64 KByte Block 1E0000H 1DFFFFH 64 KByte Block 29 1D0000H 1CFFFFH 64 KByte Block 28 1C0000H 1BFFFFH 27 64 KByte Block 1B0000H 1AFFFFH 64 KByte Block 26 1A0000H 19FFFFH 64 KByte Block 25 190000H 18FFFFH 64 KByte Block 24 180000H 17FFFFH 64 KByte Block 23 170000H 16FFFFH 64 KByte Block 22 160000H 15FFFFH 64 KByte Block 21 150000H 14FFFFH 20 64 KByte Block 140000H 13FFFFH 64 KByte Block 19 130000H 12FFFFH 18 64 KByte Block 120000H 11FFFFH 17 64 KByte Block 110000H 10FFFFH 16 64 KByte Block 100000H 0FFFFH 64 KByte Block 15 OFOOOOH OEFFFFH 14 64 KByte Block 0E0000H 0DFFFFH 64 KByte Block 13 ODOOOOH OCFFFFH 12 64 KByte Block OCOOOOH OBFFFFH 64 KByte Block 11 0B0000H 0AFFFFH 10 64 KByte Block 0A0000H 09FFFFH 9 64 KByte Block 090000H 08FFFFH 8 64 KByte Block 080000H 07FFFFH 7 64 KByte Block 070000H 06FFFFH 6 64 KByte Block 060000H 05FFFFH 5 64 KByte Block 050000H 04FFFFH 4 64 KByte Block 040000H 03FFFFH 3 64 KByte Block 030000H 02FFFFH 2 64 KByte Block 020000H 01FFFFH 1 64 KByte Block 010000H 00FFFFH 0 64 KByte Block 000000H

Figure 3. LH28F016SAT-70 Memory Map (Byte-wide mode)

X16 MODE

A[20:1]\*

# 3.1 Extended Status Registers Memory Map

| RESERVED GSR RESERVED BSR31 RESERVED RESERVED     | A[20:0]<br>1F0006H<br>1F0005H<br>1F0004H<br>1F0003H<br>1F0002H<br>1F0001H<br>1F0000H |

|---------------------------------------------------|--------------------------------------------------------------------------------------|

| e<br>•<br>•<br>•<br>•<br>RESERVED                 | 010002H                                                                              |

| RESERVED  GSR  RESERVED  BSR0  RESERVED  RESERVED | 000006H<br>000005H<br>000004H<br>000003H<br>000002H<br>000001H                       |

F8003H **RESERVED** GSR F8002H **RESERVED BSR31** F8001H **RESERVED RESERVED** F8000H 08001H **RESERVED** 00003H **RESERVED** GSR 00002H **RESERVED** BSR0 00001H **RESERVED RESERVED** H00000

Figure 4.1 Extended Status Register Memory Map (Byte-wide mode)

Figure 4.2 Extended Status Register Memory Map (Word-wide mode)

<sup>\*</sup> In Word-wide mode  $A_0$  don't care, address values are ignored  $A_0$

# 4.0 BUS OPERATIONS, COMMANDS AND STATUS REGISTER DEFINITIONS

# 4.1 Bus Operations for Word-Wide Mode (BYTE# = V,u)

| Mode            | Notes | RP#             | CE <sub>1</sub> #                                     | CE <sub>0</sub> #                                     | OE#             | WE#             | A <sub>1</sub>  | DQ <sub>0-15</sub> | RY/BY#          |

|-----------------|-------|-----------------|-------------------------------------------------------|-------------------------------------------------------|-----------------|-----------------|-----------------|--------------------|-----------------|

| Read            | 1,2,7 | $V_{IH}$        | V <sub>IL</sub>                                       | V <sub>IL</sub>                                       | VIL             | V <sub>IH</sub> | Х               | D <sub>OUT</sub>   | Х               |

| Output Disable  | 1,6,7 | V <sub>IH</sub> | VIL                                                   | VIL                                                   | VIH             | V <sub>IH</sub> | Х               | High Z             | X               |

| Standby         | 1,6,7 | V <sub>IH</sub> | V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>IH</sub> | V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>IH</sub> | x               | х               | x               | High Z             | x               |

| Deep Power-Down | 1,3   | V <sub>IL</sub> | ×                                                     | х                                                     | ×               | ×               | х               | High Z             | V <sub>OH</sub> |

| Manufacturer ID | 4     | $V_{iH}$        | VIL                                                   | V <sub>IL</sub>                                       | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | 0089H              | V <sub>OH</sub> |

| Device ID       | 4     | V <sub>IH</sub> | V <sub>IL</sub>                                       | ViL                                                   | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | 66A0H              | V <sub>OH</sub> |

| Write           | 1,5,6 | V <sub>IH</sub> | V <sub>IL</sub>                                       | V <sub>IL</sub>                                       | V <sub>IH</sub> | V <sub>IL</sub> | X               | D <sub>IN</sub>    | X               |

# 4.2 Bus Operations For Byte-Wide Mode (BYTE# =V<sub>11</sub>)

| Mode            | Notes | RP#             | CE <sub>1</sub> #                                     | CE <sub>0</sub> #                                     | OE#             | WE#             | A <sub>0</sub>  | DQ <sub>0-7</sub> | RY/BY#          |

|-----------------|-------|-----------------|-------------------------------------------------------|-------------------------------------------------------|-----------------|-----------------|-----------------|-------------------|-----------------|

| Read            | 1,2,7 | V <sub>IH</sub> | VIL                                                   | VIL                                                   | V <sub>IL</sub> | V <sub>IH</sub> | Х               | D <sub>OUT</sub>  | Х               |

| Output Disable  | 1,6,7 | V <sub>IH</sub> | VIL                                                   | V <sub>IL</sub>                                       | V <sub>IH</sub> | V <sub>IH</sub> | Х               | High Z            | Х               |

| Standby         | 1,6,7 | VIH             | V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>IH</sub> | V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>IH</sub> | х               | x               | x               | High Z            | X               |

| Deep Power-Down | 1,3   | V <sub>IL</sub> | Х                                                     | Х                                                     | X               | Х               | Х               | High Z            | V <sub>OH</sub> |

| Manufacturer ID | 4     | V <sub>IH</sub> | V <sub>IL</sub>                                       | V <sub>IL</sub>                                       | VıL             | V <sub>IH</sub> | V <sub>IL</sub> | 89H               | V <sub>OH</sub> |

| Device ID       | 4     | V <sub>IH</sub> | VIL                                                   | V <sub>IL</sub>                                       | VIL             | V <sub>IH</sub> | V <sub>IH</sub> | A0H               | V <sub>OH</sub> |

| Write           | 1,5,6 | V <sub>IH</sub> | V <sub>IL</sub>                                       | V <sub>IL</sub>                                       | V <sub>IH</sub> | VIL             | Х               | D <sub>IN</sub>   | Х               |

### NOTES:

- 1. X can be  $V_{IH}$  or  $V_{IL}$  for address or control pins except for RY/BY#, which is either  $V_{OL}$  or  $V_{OH}$ .

- 2. RY/BY# output is open drain. When the WSM is ready, Erase is suspended or the device is in deep power-down mode, RY/BY# will be at V<sub>OH</sub> if it is tied to V<sub>CC</sub> through a resistor. When the RY/BY# at V<sub>OH</sub> is independent of OE# while a WSM operation is in progress.

- 3. RP# at GND  $\pm$  0.2V ensures the lowest deep power-down current.

- 4.  $A_0$  and  $A_1$  at  $V_{II}$  provide manufacturer ID codes in x8 and x16 modes respectively.

- A<sub>0</sub> and A<sub>1</sub> at V<sub>IH</sub> provide device ID codes in x8 and x16 modes respectively. All other addresses are set to zero.

- 5. Commands for different Erase operations, Data Write operations of Lock-Block operations can only be successfully completed when  $V_{pp} = V_{pph}$ .

- 6. While the WSM is running, RY/BY# in Level-Mode (default) stays at  $V_{OL}$  until all operations are complete. RY/BY# goes to  $V_{OH}$  when the WSM is not busy or in erase suspend mode.

- 7. RY/BY# may be at V<sub>OL</sub> while the WSM is busy performing various operations. For example, a status register read during a write operation.

# 4.3 LH28F008SA-Compatible Mode Command Bus Definitions

| 2                               | N-4   | Fir   | st Bus Cy | cle  | Second Bus Cycle |      |      |  |

|---------------------------------|-------|-------|-----------|------|------------------|------|------|--|

| Command                         | Notes | Oper  | Addr      | Data | Oper             | Addr | Data |  |

| Read Array                      |       | Write | Х         | FFH  | Read             | AA   | AD   |  |

| Intelligent Identifier          | 1     | Write | Х         | 90H  | Read             | IA   | ID   |  |

| Read Compatible Status Register | 2     | Write | Х         | 70H  | Read             | Х    | CSRD |  |

| Clear Status Register           | 3     | Write | х         | 50H  |                  |      |      |  |

| Word/Byte Write                 |       | Write | Х         | 40H  | Write            | WA   | WD   |  |

| Alternate Word/Byte Write       |       | Write | Х         | 10H  | Write            | WA   | WD   |  |

| Block Erase/Confirm             | 4     | Write | Х         | 20H  | Write            | ВА   | DOH  |  |

| Erase Suspend/Resume            | 4     | Write | ×         | вон  | Write            | Х    | D0H  |  |

**ADDRESS**

DATA

AA = Array Address BA = Block Address IA = Identifier Address WA = Write Address AD = Array Data CSRD = CSR Data ID = Identifier Data WD = Write Data

X = Don't Care

#### NOTES:

- 1. Following the intelligent identifier command, two Read operations access the manufacturer and device signature codes.

- 2. The CSR is automatically available after device enters Data Write, Erase, or Suspend operations.

- 3. Clears CSR.3, CSR.4 and CSR.5. Also clears GSR.5 and all BSR.5 and BSR.2 bits.

See Status register definitions.

4. While device performs Block Erase, if you issue Erase Suspend Command (B0H), be sure to confirm ESS (Erase-Suspend-Status) is set to 1 on compatible status register. In the case, ESS bit was not set to 1, also completed the Erase (ESS=0, WSMS=1), be sure to issue Resume command (D0H) after completed next Erase command. Beside, when the Erase Suspend command is issued, while the device is not in Erase, be sure to issue Resume command (D0H) after the next erase completed. When you use Erase-Suspend /Resume command, we recommend to issue serial Block Erase command (20H, D0H) and Resume command (D0H). (Refer to 4.4 Performance Enhancement Command Bus Definitions.)

# 4.4 LH28F016SAT-70 -Performance Enhancement Command Bus Definitions

| Command                              | Mode | Notes    | Firs  | t Bus C | ycle | Seco  | nd Bu      | s Cycle      | Thi   | rd Bus | Cycle   |

|--------------------------------------|------|----------|-------|---------|------|-------|------------|--------------|-------|--------|---------|

| Command                              | Wode | Notes    | Oper  | Addr    | Data | Oper  | Addr       | Data         | Oper  | Addr   | Data    |

| Read Extended<br>Status Register     |      | 1        | Write | х       | 71H  | Read  | RA         | GSRD<br>BSRD |       |        |         |

| Page Buffer Swap                     |      | 7        | Write | Х       | 72H  |       |            |              |       |        |         |

| Read Page Buffer                     |      |          | Write | x       | 75H  | Read  | PA         | PD           |       |        |         |

| Single Load to<br>Page Buffer        |      |          | Write | х       | 74H  | Write | PA         | PD           |       |        |         |

| Sequential Load to                   | x8   | 4,6,10   | Write | ×       | E0H  | Write | х          | BCL          | Write | Х      | всн     |

| Page Buffer                          | x16  | 4,5,6,10 | Write | х       | E0H  | Write | х          | WCL          | Write | х      | WCH     |

| Page Buffer Write                    | x8   | 3,4,9,10 | Write | Х       | 0CH  | Write | <b>A</b> 0 | BC(L,H)      | Write | WA     | BC(H,L) |

| to Flash                             | x16  | 4,5,10   | Write | х       | 0CH  | Write | х          | WCL          | Write | WA     | WCH     |

| Two-Byte Write                       | x8   | 3        | Write | х       | FBH  | Write | <b>A</b> 0 | WD(L,H)      | Write | WA     | WD(H,L) |

| Block Erase<br>/Confirm              |      | 11       | Write | Х       | 20H  | Write | ВА         | DOH          | Write | Х      | DOH     |

| Lock Block<br>/Confirm               |      |          | Write | x       | 77H  | Write | ВА         | DOH          |       |        |         |

| Upload Status Bits<br>/Confirm       |      | 2        | Write | х       | 97H  | Write | Х          | DOH          |       |        |         |

| Upload Device<br>Information         |      |          | Write | х       | 99H  | Write | Х          | DOH          |       |        |         |

| Erase All Unlocked<br>Blocks/Confirm |      | 11       | Write | Х       | A7H  | Write | Х          | DOH          | Write | Х      | DOH     |

| RY/BY# Enable to<br>Level-Mode       |      | 8        | Write | х       | 96H  | Write | Х          | 01H          |       |        |         |

| RY/BY# Pulse-On-<br>Write            |      | 8        | Write | Х       | 96H  | Write | Х          | 02H          |       |        |         |

| RY/BY# Pulse-On-<br>Erase            |      | 8        | Write | Х       | 96H  | Write | Х          | 03H          |       |        |         |

| RY/BY# Disable                       |      | 8        | Write | Х       | 96H  | Write | Х          | 04H          |       |        |         |

| Sleep                                |      |          | Write | х       | F0H  |       |            |              |       |        |         |

| Abort                                |      |          | Write | х       | 80H  |       |            |              |       |        |         |

### **ADDRESS**

BA = Block Address

PA = Page Buffer Address

RA = Extended Register Address

WA = Write Address

X = Don't Care

### DATA

AD = Array Data

PD = Page Buffer Data

PSPD = PSP Data

BSRD = BSR Data

GSRD = GSR Data

WC (L.H) = Word Count (Low, High) BC (L.H) = Byte Count (Low, High)

WD (L.H) = Write Data (Low, High)

#### NOTES:

- 1. RA can be the GSR address or any BSR address. See Figure 4.1 and 4.2 for Extended Status Register Memory Maps.

- 2. Upon device power-up, all BSR lock-bits come up locked. The Upload Status Bits command must be written to reflect the actual lock-bit status.

- 3.  $A_n$  is automatically complemented to load second byte of data. BYTE# must be at  $V_{it}$ .

- $A_0$  value determines which WD/BC is supplied first:  $A_0 = 0$  looks at the WDL/BCL,  $A_0 = 1$  looks at the WDH/BCH.

- 4. BCH/WCH must be at 00H for this product because of the 256-Byte (128 Word) Page Buffer size and to avoid writing the Page Buffer contents into more than one 256-Byte segment within an array block. They are simply shown for future Page Buffer expandability.

- 5. In x16 mode, only the lower byte DQ<sub>0.7</sub> is used for WCL and WCH. The upper byte DQ<sub>8.15</sub> is a don't care.

- 6. PA and PD (Whose count is given in cycles 2 and 3) are supplied starting in the 4th cycle which is not shown.

- 7. This command allows the user to swap between available Page Buffers (0 or 1).

- 8. These commands reconfigure RY/BY# output to one of two pulse-modes or enable and disable the RY/BY# function.

- 9. Write address. WA, is the Destination address in the flash array which must match the Source address in the Page Buffer. Refer to the LH28F800SU User's Manual.

- 10. BCL = 00H corresponds to a Byte count of 1. Similarly, WCL = 00H corresponds to a Word count of 1.

- 11. Unless you issue Erase-Suspend command, It is no necessary to input DOH on third bus cycle.

4.5 Compatible Status Register

| WSMS | ESS | ES | DWS | VPPS | R | R | R |

|------|-----|----|-----|------|---|---|---|

| 7    | 6   | 5  | 4   | 3    | 2 | 1 | 0 |

#### CSR.7 = WRITE STATE MACHINE STATUS (WSMS)

1 = Ready

0 = Busy

RY/BY# output or WSMS bit must be checked to determine completion of an operation (Erase Suspend, Erase or Data Write) before the appropriate Status bit (ESS, ES or DWS) is checked for success.

NOTES:

### CSR.6 = ERASE-SUSPEND STATUS (ESS)

1 = Erase Suspended

0 = Erase in Progress/Completed

# CSR.5 = ERASE STATUS (ES)

1 = Error in Block Erasure

0 = Successful Block Erase

If DWS and ES are set to "1" during an erase attempt, an improper command sequence was entered. Clear the CSR and attempt the operation again.

#### CSR.4 = DATA-WRITE STATUS (DWS)

1 = Error in Data Write

0 = Data Write Successful

# CSR.3 = $V_{pp}$ STATUS (VPPS)

$1 = V_{pp}$  Low Detect, Operation Abort

$0 = V_{pp} OK$

The VPPS bit, unlike an A/D converter, does not provide continuous indication of Vpp level. The WSM interrogates V<sub>pp</sub>'s level only after the Data-Write or Erase command sequences have been entered, and informs the system if V<sub>pp</sub> has not been switched on. VPPS is not guaranteed to report accurate feedback between  $V_{PPL}$  and  $V_{PPH}$ .

# CSR.2-0 = RESERVED FOR FUTURE ENHANCEMENTS

These bits are reserved for future use: mask them out when polling the CSR.

SHARP

# 4.6 Global Status Register

| WSMS | oss | DOS | DSS | QS | PBAS | PBS | PBSS |

|------|-----|-----|-----|----|------|-----|------|

| 7    | 6   | 5   | 4   | 3  | 2    | 1   | 0    |

#### NOTES:

GSR.7 = WRITE STATE MACHINE STATUS (WSMS)

1 = Ready

0 = Busy

[1] RY/BY# output or WSMS bit must be checked to determine completion of an operation (Block Lock, Suspend, any RY/BY# reconfiguration, Upload Status Bits, Erase or Data Write) before the appropriate Status bit (OSS or DOS) is checked for success.

GSR.6 = OPERATION SUSPEND STATUS (OSS)

1 = Operation Suspended

0 = Operation in Progress/Completed

GSR.5 = DEVICE OPERATION STATUS (DOS)

1 = Operation Unsuccessful

0 = Operation Successful or Currently Running

GSR.4 = DEVICE SLEEP STATUS (DSS)

1 = Device in Sleep

0 = Device Not in Sleep

MATRIX 5/4

00 = Operation Successful or Currently

Running

01 = Device in Sleep Mode or Pending Sleep

10 = Operation Unsuccessful

11 = Operation Unsuccessful or Aborted

If operation currently running, then GSR.7 = 0.

If device pending sleep, then GSR.7 = 0.

Operation aborted: Unsuccessful due to Abort

GSR.3 = QUEUE STATUS (QS)

1 = Queue Full

0 = Queue Available

GSR.2 = PAGE BUFFER AVAILABLE STATUS (PBAS)

1 = One or Two Page Buffers Available

0 = No Page Buffer Available

The device contains two Page Buffers.

GSR.1 = PAGE BUFFER STATUS (PBS)

1 = Selected Page Buffer Ready

0 = Selected Page Buffer Busy

Selected Page Buffer is currently busy with WSM

operation.

command.

GSR.0 = PAGE BUFFER SELECT STATUS (PBSS)

1 = Page Buffer 1 Selected

0 = Page Buffer 0 Selected

#### NOTE:

1. When multiple operations are queued, checking BSR.7 only provides indication of completion for that particular block. GSR.7 provides indication when all queued operations are completed.

SHARP

# 4.7 Block Status Register

| BS | BLS | BOS | BOAS | QS | VPPS | R | R |

|----|-----|-----|------|----|------|---|---|

| 7  | 6   | 5   | 4    | 3  | 2    | 1 | 0 |

#### NOTES:

BSR.7 = BLOCK STATUS (BS)

1 = Ready 0 = Busy [1] RY/BY# output or BS bit must be checked to determine completion of an operation (Block Lock, Suspend, Erase or Data Write) before the appropriate Status bits (BOS, BLS) is checked for success.

BSR.6 = BLOCK-LOCK STATUS (BLS)

1 = Block Unlocked for Write/Erase0 = Block Locked for Write/Erase

BSR.5 = BLOCK OPERATION STATUS (BOS)

1 = Operation Unsuccessful0 = Operation Successful or Currently Running

BSR.4 = BLOCK OPERATION ABORT STATUS

(BOAS)

1 = Operation Aborted0 = Operation Not Aborted

The BOAS bit will not be set until BSR.7 = 1.

MATRIX 5/4

00 = Operation Successful or Currently Running01 = Not a valid Combination

10 = Operation Unsuccessful

11 = Operation Aborted Operation halted via Abort command.

BSR.3 = QUEUE STATUS (QS)

1 = Queue Full

0 = Queue Available

BSR.2 =  $V_{pp}$  STATUS (VPPS)

$1 = V_{pp}$  Low Detect, Operation Abort

$0 = V_{pp} OK$

### NOTES:

BSR.1-0 = RESERVED FOR FUTURE ENHANCEMENTS

These bits are reserved for future use; mask them out when polling the BSRs.

1. When multiple operations are queued, checking BSR.7 only provides indication of completion for that particular block. GSR.7 provides indication when all queued operations are completed.

#### 5.0 **ELECTRICAL SPECIFICATIONS**

#### 5.1 **Absolute Maximum Ratings\***

Temperature Under Bias ...... 0°C to + 80°C Storage Temperature ..... - 65°C to + 125°C

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

# $V_{cc}$ = 3.3V $\pm$ 0.3V Systems<sup>(4)</sup>

| Symbol          | Parameter                                                                          | Notes | Min   | Max                      | Units | Test Conditions     |

|-----------------|------------------------------------------------------------------------------------|-------|-------|--------------------------|-------|---------------------|

| TA              | Operating Temperature, Commercial                                                  | 1     | 0     | 70                       | .c    | Ambient Temperature |

| V <sub>CC</sub> | V <sub>CC</sub> with Respect to GND                                                | 2     | - 0.2 | 7.0                      | V     |                     |

| V <sub>PP</sub> | V <sub>PP</sub> Supply Voltage with Respect to GND                                 | 2     | - 0.2 | 14.0                     | ٧     |                     |

| V               | Voltage on any Pin (except V <sub>CC</sub> , V <sub>PP</sub> ) with Respect to GND | 2     | - 0.5 | V <sub>CC</sub><br>+ 0.5 | ٧     |                     |

| 1               | Current into any Non-Supply Pin                                                    |       |       | ± 30                     | mA    |                     |

| lout            | Output Short Circuit Current                                                       | 3     |       | 100                      | mA    |                     |

# $V_{cc} = 5.0V \pm 0.5V \text{ Systems}^{(4)}$

| Symbol          | Parameter                                                                          | Notes | Min   | Max  | Units | Test Conditions     |

|-----------------|------------------------------------------------------------------------------------|-------|-------|------|-------|---------------------|

| TA              | Operating Temperature, Commercial                                                  | 1     | 0     | 70   | .c    | Ambient Temperature |

| V <sub>CC</sub> | V <sub>CC</sub> with Respect to GND                                                | 2     | - 0.2 | 7.0  | ٧     |                     |

| V <sub>PP</sub> | V <sub>PP</sub> Supply Voltage with Respect to GND                                 | 2     | - 0.2 | 14.0 | ٧     |                     |

| V               | Voltage on any Pin (except V <sub>CC</sub> , V <sub>PP</sub> ) with Respect to GND | 2     | - 0.5 | 7.0  | ٧     |                     |

| ı               | Current into any Non-Supply Pin                                                    |       |       | ± 30 | mA    |                     |

| lout            | Output Short Circuit Current                                                       | 3     |       | 100  | mA    |                     |

#### **NOTES:**

- 1. Operating temperature is for commercial product defined by this specification.

- 2. Minimum DC voltage is 0.5V on input/output pins. During transitions, this level may undershoot to 2.0V for periods < 20 ns. Maximum DC voltage on input/output pins is  $V_{cc} + 0.5V$  which, during transitions, may overshoot to  $V_{cc} + 2.0V$  for periods < 20 ns. 3. Output shorted for no more than one second. No more than one output shorted at a time.

- 4. AC specifications are valid at both voltage ranges. See DC Characteristics tables for voltage range-specific specifications.

# 5.2 Capacitance

# For a 3.3V System:

| Symbol            | Parameter                                                    | Note | Тур | Max | Units | Test Conditions                    |

|-------------------|--------------------------------------------------------------|------|-----|-----|-------|------------------------------------|

| C <sub>IN</sub>   | Capacitance Looking into an Address/Control Pin              | 1    | 6   | 8   | pF    | $T_A = 25$ °C, f = 1.0 MHz         |

| C <sub>OUT</sub>  | Capacitance Looking into an Output Pin                       | 1    | 8   | 12  | рF    | T <sub>A</sub> = 25°C, f = 1.0 MHz |

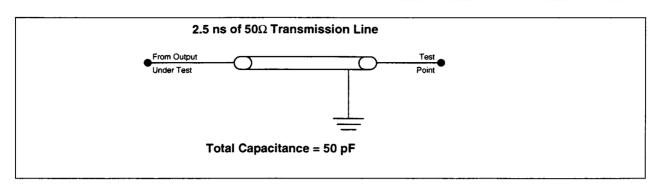

| C <sub>LOAD</sub> | Load Capacitance Driven by Outputs for Timing Specifications | 1    |     | 50  | pF    | For $V_{CC} = 3.3V \pm 0.3V$       |

|                   | Equivalent Testing Load Circuit                              |      |     | 2.5 | ns    | 50Ω transmission line delay        |

# For a 5.0V System:

| Symbol | Parameter                                                    | Note | Тур | Max | Units | Test Conditions                    |

|--------|--------------------------------------------------------------|------|-----|-----|-------|------------------------------------|

| CiN    | Capacitance Looking into an Address/Control Pin              | 1    | 6   | 8   | рF    | T <sub>A</sub> = 25°C, f = 1.0 MHz |

| Cout   | Capacitance Looking into an Output Pin                       | 1    | 8   | 12  | pF    | T <sub>A</sub> = 25°C, f = 1.0 MHz |

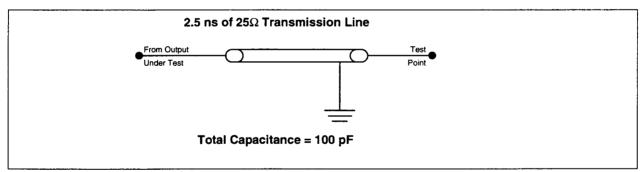

| CLOAD  | Load Capacitance Driven by Outputs for Timing Specifications |      |     | 100 | pF    | For $V_{CC} = 5.0V \pm 0.5V$       |

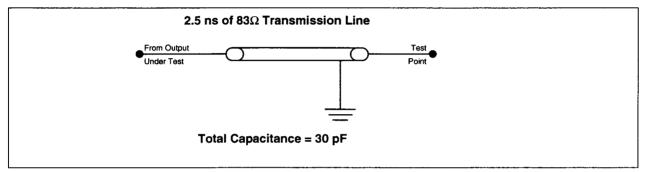

| - LOND |                                                              |      |     | 30  | pF    | For $V_{CC} = 5.0V \pm 0.25V$      |

|        | Equivalent Testing Load Circuit V <sub>CC</sub> ±10%         |      |     | 2.5 | ns    | 25Ω transmission line delay        |

|        | Equivalent Testing Load Circuit V <sub>CC</sub> ±5%          |      |     | 2.5 | ns    | $83\Omega$ transmission line delay |

# NOTE:

1. Sampled, not 100% tested.

# 5.3 Timing Nomenclature

All 3.3V system timings are measured from where signals cross 1.5V.

For 5.0V systems use the standard JEDEC cross point definitions.

Each timing parameter consists of 5 characters. Some common examples are defined below:

$t_{ce}$   $t_{elov}$  time(t) from CE# (E) going low (L) to the outputs (Q) becoming valid (V)

$t_{\text{OE}}$   $t_{\text{GLOV}}$  time(t) from OE# (G) going low (L) to the outputs (Q) becoming valid (V)

$t_{ACC}$   $t_{AVOV}$  time(t) from address (A) valid (V) to the outputs (Q) becoming valid (V)

$t_{AS}$   $t_{AVWH}$  time(t) from address (A) valid (V) to WE# (W) going high (H)

$t_{_{DH}}$   $t_{_{WHOX}}$  time(t) from WE# (W) going high (H) to when the data (D) can become undefined (X)

|    | Pin Characters                  |   | Pin States                        |

|----|---------------------------------|---|-----------------------------------|

| Α  | Address Inputs                  | Н | High                              |

| D  | Data Inputs                     | L | Low                               |

| Q  | Data Outputs                    | ٧ | Valid                             |

| Е  | CE# (Chip Enable)               | Х | Driven, but not necessarily valid |

| G  | OE# (Output Enable)             | Z | High Impedance                    |

| W  | WE# (Write Enable)              |   |                                   |

| Р  | RP# (Deep Power-Down Pin)       |   |                                   |

| R  | RY/BY# (Ready/Busy#)            |   |                                   |

| ٧  | Any Voltage Level               |   |                                   |

| Υ  | 3/5# Pin                        |   |                                   |

| 5V | V <sub>CC</sub> at 4.5V Minimum |   |                                   |

| 3V | V <sub>CC</sub> at 3.0V Minimum |   |                                   |

AC test inputs are driven at  $V_{OH}$  (2.4  $V_{TTL}$ ) for a Logic "1" and  $V_{OL}$  (0.45  $V_{TTL}$ ) for a Logic "0." Input timing begins at  $V_{IH}$  (2.0  $V_{TTL}$ ) and  $V_{IL}$  (0.8  $V_{TTL}$ ). Output timing ends at  $V_{IH}$  and  $V_{IL}$ . Input rise and fall times (10% to 90%) < 10 ns.

Figure 5. Transient Input/Output Reference Waveform ( $V_{cc} = 5.0V$ )

AC test inputs are driven at 3.0V for a Logic "1" and 0.0V for a Logic "0." Input timing begins, and output timing ends, at 1.5V. Input rise and fall times (10% to 90%) < 10 ns.

Figure 6. Transient Input/Output Reference Waveform ( $V_{cc} = 3.3V$ )

Figure 7. Transient Equivalent Testing Load Circuit ( $V_{cc} = 3.3V$ )

Figure 8(1). Transient Equivalent Testing Load Circuit (V  $_{\rm cc}$  = 5.0V  $\pm$  0.25V)

Figure 8(2). Transient Equivalent Testing Load Circuit (V  $_{\rm cc}$  = 5.0V  $\pm$  0.5V)

# **5.4 DC Characteristics**

$V_{cc} = 3.3V \pm 0.3V$ ,  $T_A = 0^{\circ}C$  to + 70 $^{\circ}C$ 3/5# = Pin Set High for 3.3V Operations

| Symbol           | Parameter                                  | Notes | Min | Тур | Max  | Units | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|--------------------------------------------|-------|-----|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l <sub>IL</sub>  | Input Load Current                         | 1     |     |     | ± 1  | μΑ    | V <sub>CC</sub> = V <sub>CC</sub> Max, V <sub>IN</sub> = V <sub>CC</sub> or GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| l <sub>LO</sub>  | Output Leakage<br>Current                  | 1     |     |     | ± 10 | μА    | V <sub>CC</sub> = V <sub>CC</sub> Max, V <sub>IN</sub> = V <sub>CC</sub> or GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Iccs             | V <sub>CC</sub> Standby Current            | 1,4   |     | 50  | 100  | μА    | $V_{CC} = V_{CC}$ Max,<br>$CE_0$ #, $CE_1$ #, $RP$ # = $V_{CC} \pm 0.2V$<br>BYTE#, $WP$ #, $3/5$ # = $V_{CC} \pm 0.2V$ or<br>$GND \pm 0.2V$                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                  |                                            |       |     | 1   | 4    | mA    | $V_{CC} = V_{CC}$ Max,<br>$CE_0$ #, $CE_1$ #, $RP$ # = $V_{IH}$<br>BYTE#, $WP$ #, $3/5$ # = $V_{IH}$ or $V_{IL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ICCD             | V <sub>CC</sub> Deep Power-Down<br>Current | 1     |     | 1   | 5    | μА    | RP# = GND ± 0.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ICCR1            | V <sub>CC</sub> Read Current               | 1,3,4 |     | 30  | 35   | mA    | $\begin{split} &V_{CC} = V_{CC} \text{ Max,} \\ &C\text{MOS: } CE_0\#,  CE_1\# = \text{GND} \pm 0.2\text{V} \\ &\text{BYTE\#} = \text{GND} \pm 0.2\text{V or } V_{CC} \pm 0.2\text{V} \\ &\text{Inputs} = \text{GND} \pm 0.2\text{V or } V_{CC} \pm 0.2\text{V,} \\ &\text{TTL: } CE_0\#,  CE_1\# = \text{V}_{\text{IL}}, \\ &\text{BYTE\#} = \text{V}_{\text{IL}} \text{ or } \text{V}_{\text{IH}}, \\ &\text{Inputs} = \text{V}_{\text{IL}} \text{ or } \text{V}_{\text{IH}}, \\ &\text{f} = 8 \text{ MHz, } \text{I}_{\text{OUT}} = 0 \text{ mA} \end{split}$ |

| ICCR2            | V <sub>CC</sub> Read Current               | 1,3,4 |     | 15  | 20   | mA    | $\begin{split} &V_{CC} = V_{CC} \text{ Max}, \\ &C\text{MOS: } CE_0\#, CE_1\# = \text{GND} \pm 0.2\text{V}, \\ &\text{BYTE}\# = V_{CC} \pm 0.2\text{V or } \text{GND} \pm 0.2\text{V} \\ &\text{Inputs} = \text{GND} \pm 0.2\text{V or } V_{CC} \pm 0.2\text{V}, \\ &\text{TTL: } CE_0\#, CE_1\# = \text{V}_{IL} \\ &\text{BYTE}\# = \text{V}_{IH} \text{ or } \text{V}_{IL} \\ &\text{Inputs} = \text{V}_{IL} \text{ or } \text{V}_{IH}, \\ &\text{f} = 4 \text{ MHz}, I_{OUT} = 0 \text{ mA} \end{split}$                                                      |

| Iccw             | V <sub>CC</sub> Write Current              | 1     |     | 8   | 12   | mA    | Word/Byte Write in<br>Progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ICCE             | V <sub>CC</sub> Block Erase<br>Current     | 1     |     | 6   | 12   | mA    | Block Erase in Progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Icces            | V <sub>CC</sub> Erase Suspend<br>Current   | 1,2   |     | 3   | 6    | mA    | CE <sub>0</sub> #, CE <sub>1</sub> # =V <sub>IH</sub><br>Block Erase Suspended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IPPS             | V <sub>PP</sub> Standby Current            | 1     |     | ± 1 | ± 10 | μА    | V <sub>PP</sub> ≤ V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I <sub>PPD</sub> | V <sub>PP</sub> Deep Power-Down<br>Current | 1     |     | 0.2 | 5    | μА    | RP# = GND ± 0.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **DC Characteristics** (Continued)

$V_{cc}$  = 3.3V ± 0.3V,  $T_A$  = 0°C to + 70°C 3/5# = Pin Set High for 3.3V Operations

| Symbol            | Parameter                                         | Notes | Min                   | Тур  | Max                   | Units | Test Conditions                                                     |

|-------------------|---------------------------------------------------|-------|-----------------------|------|-----------------------|-------|---------------------------------------------------------------------|

| IPPR              | V <sub>PP</sub> Read Current                      | 1     |                       |      | 200                   | μΑ    | V <sub>PP</sub> > V <sub>CC</sub>                                   |

| I <sub>PPW</sub>  | V <sub>PP</sub> Write Current                     | 1     |                       | 10   | 15                    | mA    | V <sub>PP</sub> = V <sub>PPH</sub> ,<br>Word/Byte Write in Progress |

| IPPE              | V <sub>PP</sub> Erase Current                     | 1     |                       | 4    | 10                    | mA    | V <sub>PP</sub> = V <sub>PPH</sub> ,<br>Block Erase in Progress     |

| IPPES             | V <sub>PP</sub> Erase Suspend<br>Current          | 1     |                       |      | 200                   | μA    | V <sub>PP</sub> = V <sub>PPH</sub> ,<br>Block Erase Suspended       |

| VIL               | Input Low Voltage                                 |       | - 0.3                 |      | 0.8                   | ٧     |                                                                     |

| V <sub>IH</sub>   | Input High Voltage                                |       | 2.0                   |      | V <sub>CC</sub> + 0.3 | ٧     |                                                                     |

| V <sub>OL</sub>   | Output Low Voltage                                |       |                       |      | 0.4                   | ٧     | V <sub>CC</sub> = V <sub>CC</sub> Min and I <sub>OL</sub> = 4 mA    |

| V <sub>OH</sub> 1 | Output High Voltage                               |       | 2.4                   |      |                       | ٧     | I <sub>OH</sub> = - 2.0 mA<br>V <sub>CC</sub> = V <sub>CC</sub> Min |

| V <sub>OH</sub> 2 |                                                   |       | V <sub>CC</sub> - 0.2 |      |                       | ٧     | I <sub>OH</sub> = - 100 μA<br>V <sub>CC</sub> = V <sub>CC</sub> Min |

| V <sub>PPL</sub>  | V <sub>PP</sub> during Normal                     | 5     | 0.0                   |      | 0.2                   | V     |                                                                     |

|                   | Operations                                        | 5     | V <sub>CC</sub> - 0.2 |      | 6.5                   | V     |                                                                     |

| V <sub>PPH</sub>  | V <sub>PP</sub> during Write/<br>Erase Operations |       | 11.4                  | 12.0 | 12.6                  | ٧     |                                                                     |

| V <sub>LKO</sub>  | V <sub>CC</sub> Erase/Write<br>Lock Voltage       |       | 2.0                   |      |                       | ٧     |                                                                     |

#### NOTES:

- 1. All currents are in RMS unless otherwise noted. Typical values at  $V_{cc} = 3.3V$ ,  $V_{pp} = 5.0V$ , T = 25°C. These currents are valid for all product versions (package and speeds).

- 2.  $I_{cces}$  is specified with the device de-selected. If the device is read while in erase suspend mode, current draw is the sum of  $I_{cces}$  and  $I_{cce}$ .

- 3. Automatic Power Saving (APS) reduces  $I_{CCR}$  to less than 1 mA in static operation. 4. CMOS Inputs are either  $V_{CC} \pm 0.2V$  or GND  $\pm 0.2V$ . TTL Inputs are either  $V_{IL}$  or  $V_{IH}$ . 5.  $V_{PPL}$  in read is  $V_{CC}$  0.2V <  $V_{PPL}$  < 5.5V or GND <  $V_{PPL}$  < GND + 0.2V.

# **5.5 DC Characteristics**

$V_{cc} = 5.0V \pm 0.5V$ ,  $T_A = 0^{\circ}C$  to + 70 $^{\circ}C$  3/5# Pin Set Low for 5V Operations

| Symbol          | Parameter                                  | Notes | Min | Тур | Max  | Units | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

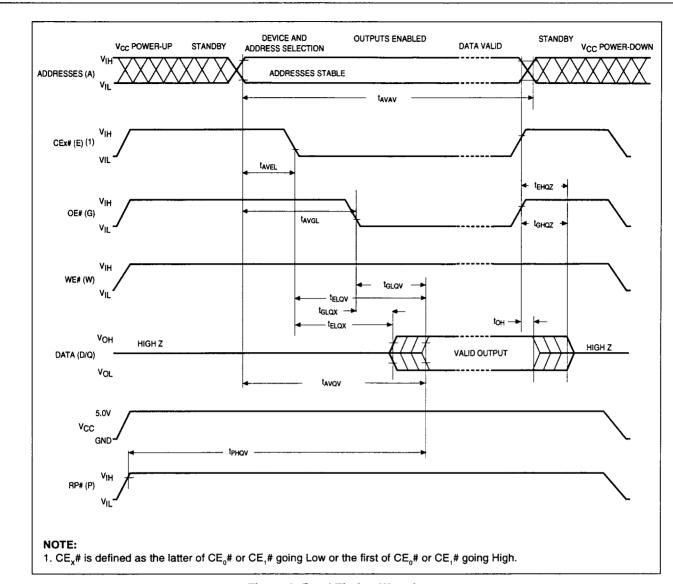

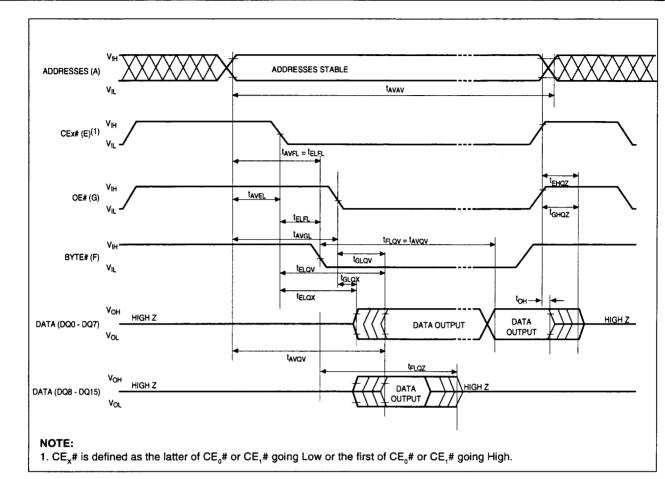

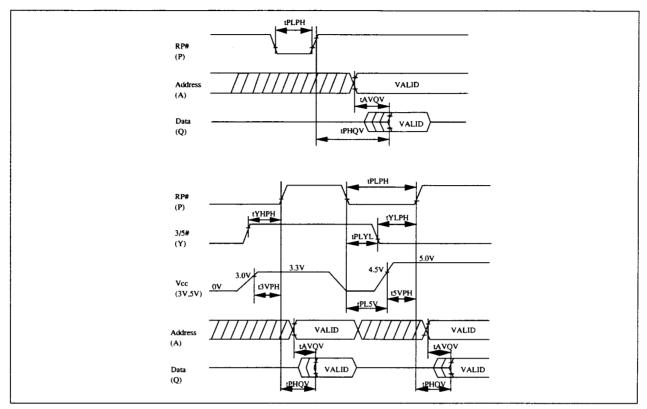

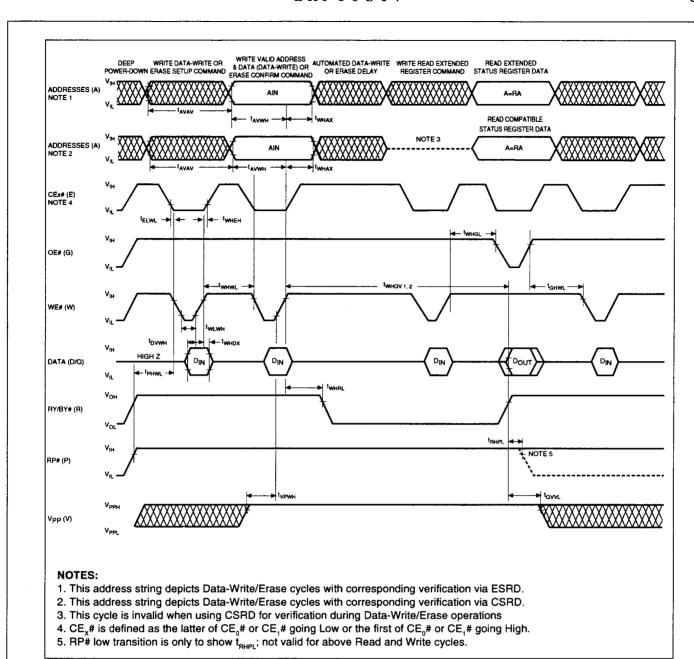

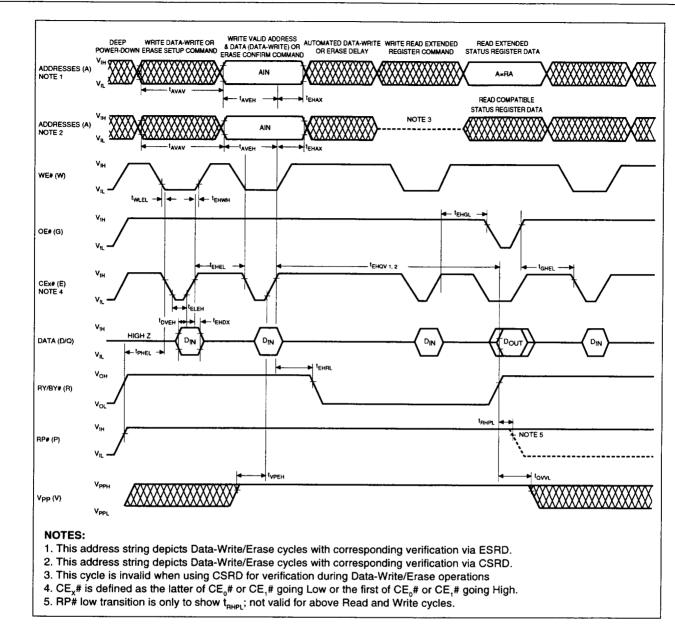

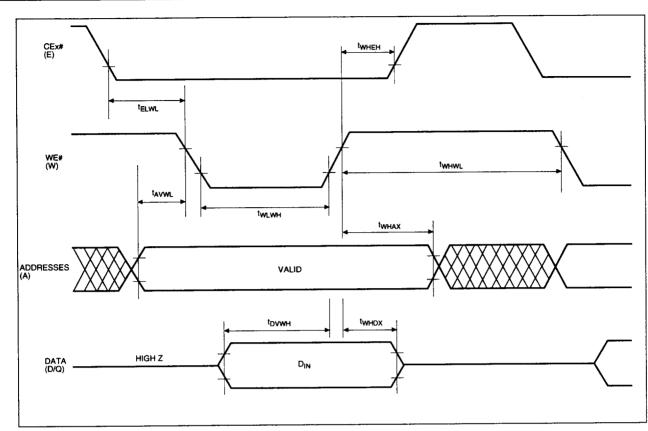

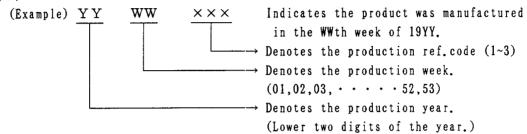

|-----------------|--------------------------------------------|-------|-----|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|