| SPEC No. | EL086125      |

|----------|---------------|

| ISSUE:   | Jun. 19. 1996 |

To;

| SPE                                   | CIFICATIONS                                                                                                                              |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Product Type                          | 256k SRAM                                                                                                                                |

| LH                                    | 5 2 2 5 6 C T - 1 0 L L                                                                                                                  |

| Model No.                             | ( LH525C9T )                                                                                                                             |

| · · · · · · · · · · · · · · · · · · · | is contains 15 pages including the cover and appendix. jections, please contact us before issuing purchasing order.  5.06'97.  MAIL DATE |

| BAY:                                  | PRSENTED GRO  BY: T. KUZUMOTO Dept. General Manager                                                                                      |

|                                       | REVIEWED BY: PREPARED BY:                                                                                                                |

|                                       | Dr. Johilashi H. Magar                                                                                                                   |

$\hbox{\tt Engineering Dept.}\, 2$

Memory IC Engineering Center Tenri Integrated Circuits Group

SHARP CORPORATION

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- · Office electronics

- · Instrumentation and measuring equipment

- · Machine tools

- · Audiovisual equipment

- · Home appliances

- $\cdot$  Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail sale operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- · Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- · Mainframe computers

- · Traffic control systems

- · Gas leak detectors and automatic cutoff devices

- · Rescue and security equipment

- · Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- · Aerospace equipment

- · Communications equipment for trunk lines

- · Control equipment for the nuclear power industry

- · Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- Please direct all queries regarding the products covered herein to a sales representative of the company.

### Contents

| 1.  | Description                                                             | 2  |

|-----|-------------------------------------------------------------------------|----|

| 2.  | Pin Configuration · · · · · · · · · · · · · · · · · · ·                 | 2  |

| 3.  | Truth Table                                                             | 3  |

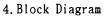

| 4.  | Block Diagram                                                           | 3  |

| 5.  | Absolute Maximum Ratings                                                | 4  |

| 6.  | Recommended DC Operating Conditions                                     | 4  |

| 7.  | DC Electrical Characteristics                                           | 4  |

| 8.  | AC Electrical Characteristics · · · · · · · · · · · · · · · · · · ·     | 5  |

| 9.  | Data Retention Characteristics                                          | 6  |

| 10. | Pin Capacitance                                                         | 6  |

| 11. | Timing Chart                                                            | 7  |

| 12. | Package and Packing Specification · · · · · · · · · · · · · · · · · · · | .( |

## 1. Decription

The LH52256CT-10LL is a static RAM organized as 32,  $768\times8$  bit with provides low-power standby mode.

It is fabricated using silicon gate CMOS process technology.

#### Features

| OAccess Time                  |       | 1 0 0 n s (Max. )                         |

|-------------------------------|-------|-------------------------------------------|

| Operating current             |       | 4 0 m A (Max. )                           |

|                               |       | 10 mA (Max. trc. twc=1 $\mu$ s)           |

| OStandby current              |       | <b>4</b> 0 μ A (Max. )                    |

| OData retention current       | • • • | 1.0 $\mu$ A (Max. Vccpr = 3 V, Ta = 25°C) |

| ○Wide operating voltage range |       | 4.5 V to 5.5 V                            |

| Operating temperature         |       | 0 ℃ to + 7 0 ℃                            |

| 07.11                         |       |                                           |

OFully static operation

$\bigcirc$ Three-state output

ONot designed or rated as radiation hardened

$\bigcirc$  2 8 pin TSOP ( TSOP 28-P-0813) plastic package

ON-type bulk silicon

### 2. Pin Configuration

|               |    |            |    | _ |            |

|---------------|----|------------|----|---|------------|

| OE $\Box$     | 10 |            | 28 |   | A 10       |

| A 11          | 2  |            | 27 |   | CE         |

| A 9           | 3  |            | 26 |   | I/O 8      |

| A s           | 4  |            | 25 |   | I/O 7      |

| A 13          | 5  |            | 24 |   | I/O 6      |

| WE $\Box$     | 6  |            | 23 |   | I/O 5      |

| Vcc $\square$ | 7  |            | 22 |   | I/O 4      |

| A 14          | 8  | (Top View) | 21 |   | GND        |

| A 12          | 9  |            | 20 |   | I/O 3      |

| A 7           | 10 |            | 19 |   | I/O 2      |

| $A_6 \square$ | 11 |            | 18 |   | I/O 1      |

| A 5           | 12 |            | 17 |   | Αo         |

| A 4 $\Box$    | 13 |            | 16 |   | <b>A</b> 1 |

| A 3 $\square$ | 14 |            | 15 | F | A 2        |

| A             |    |            |    |   |            |

| Pin Name    | Function            |  |  |

|-------------|---------------------|--|--|

| A 0 to A 14 | Address inputs      |  |  |

| CE          | Chip enable         |  |  |

| WE          | Write enable        |  |  |

| ŌE          | Output enable       |  |  |

| I/O1toI/Os  | Data inputs/outputs |  |  |

| Vcc         | Power supply        |  |  |

| GND         | Ground              |  |  |

3. Truth Table

| CE | WE | ΟE | Mode           | I /O 1 to I /O s | Supply current |

|----|----|----|----------------|------------------|----------------|

| Н  | *  | *  | Standby        | High impedance   | Standby (IsB)  |

| L  | Н  | L  | Read           | Data output      | Active (Icc)   |

| L  | Н  | Н  | Output disable | High impedance   | Active (Icc)   |

| L  | L  | *  | Write          | Data Input       | Active (Icc)   |

(\*=Don't Care, L=Low, H=High)

5. Absolute Maximum Ratings

| Parameter             | Symbol | Ratings              | Unit |

|-----------------------|--------|----------------------|------|

| Supply voltage (*1)   | Vcc    | -0.5 to $+7.0$       | V    |

| Input voltage (*1)    | VIN    | -0.5 (*2) to Vcc+0.5 | V    |

| Operating temperature | Торг   | 0 to +70             | r    |

| Storage temperature   | Tstg   | -65 to +150          | r    |

Note)  $\star$ 1. The maximum applicable voltage on any pin with respect to GND.

\*2. Undershoot of -3.0V is allowed width of pluse bellow 50ns.

## 6. Recommended DC Operating Conditions

(Ta= 0 % to + 7 0 %)

| Parameter      | Symbol | Min.      | Typ. | Max.    | Unit |

|----------------|--------|-----------|------|---------|------|

| Supply voltage | Vcc    | 4.5       | 5.0  | 5.5     | V    |

| Input voltage  | VIH    | 2.2       |      | Vcc+0.5 | V    |

|                | Vil    | -0.5 (*3) |      | 0.8     | V    |

Note) \*3. Undershoot of -3.0V is allowed width of pluse below 50ns.

#### 7. DC Electrical Characteristics

$(T_a = 0 \, \text{°C to} + 7 \, 0 \, \text{°C} , \text{Vcc} = 4.5 \, \text{V to} \, 5.5 \, \text{V})$

|                |        | (1a = 0 C to + 7)                                                          | 0 0 , vee | = 4.J V   | 10 5. | <del> </del> |

|----------------|--------|----------------------------------------------------------------------------|-----------|-----------|-------|--------------|

| Parameter      | Symbol | Conditions                                                                 | Min.      | Typ. (*4) | Max.  | Unit         |

| Input leakage  | Ili    | V <sub>IN</sub> = OV to Vcc                                                |           |           |       |              |

| current        |        |                                                                            | -1.0      |           | 1.0   | μΑ           |

| Output leakage | ILO    | CE =Vih or OE =Vih                                                         |           |           |       |              |

| current        |        | V <sub>1/0</sub> =0V to Vcc                                                | -1.0      |           | 1.0   | μΑ           |

| Operating      | Icc    | Minimum cycle                                                              |           |           |       |              |

| supply         |        | $V_{IN} = V_{IL}$ or $V_{IH}$ , $I_{I/0} = OmA$ , $\overline{CE} = V_{IL}$ |           | 2 0       | 4 0   | m A          |

| current        | Iccı   | trc, two =1 $\mu$ s                                                        |           |           |       |              |

|                |        | VIN =VIL or VIII, II/O =OmA, CE =VIL                                       |           |           | 1 0   | m A          |

| Standby        | Іѕв    | CE ≥V <sub>cc</sub> - 0. 2V                                                |           | 0.6       | 4 0   | μΑ           |

| current        | Isbi   | CE =VIH                                                                    |           |           | 3     | m A          |

| Output         | Vol    | IoL= 2.1mA                                                                 |           |           | 0.4   | V            |

| voltage        | Vон    | I <sub>OH</sub> =-1. OmA                                                   | 2.4       |           |       | V            |

Note) \*4. Typical values at Vcc=5.0V, Ta=25 $^{\circ}$ C.

### 8. AC Electrical Characteristics

## AC Test Conditions

| Input pulse level                  | 0.6 V to 2.4 V                   |

|------------------------------------|----------------------------------|

| Input rise and fall time           | 1 0 n s                          |

| Input and Output timing Ref. level | 1.5 V                            |

| Output load                        | 1TTL+C <sub>L</sub> (100pF) (*5) |

Note) \*5. Including scope and jig capacitance.

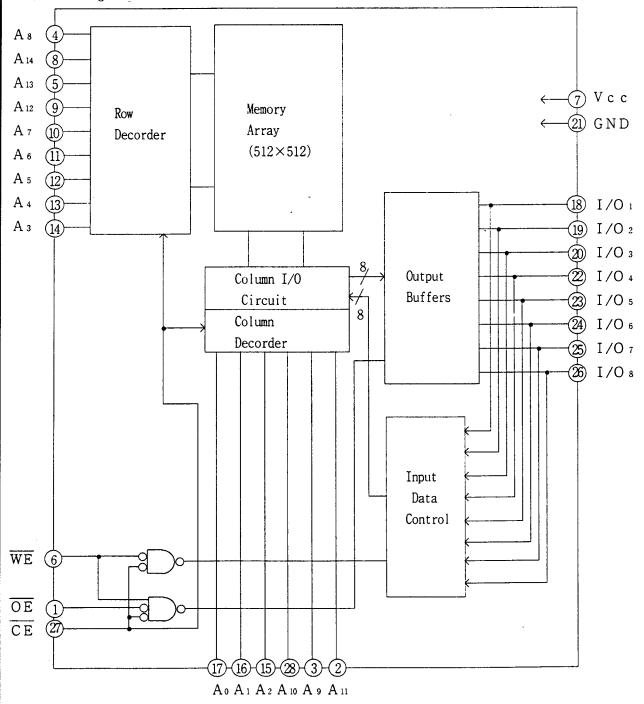

## Read cycle

$(Ta = 0 \ C to + 7 0 \ C , Vcc = 4.5 \ V to 5.5 \ V)$

| Parameter                           | Symbol | Min. | Max.  | Unit |   |

|-------------------------------------|--------|------|-------|------|---|

| Read cycle time                     | trc    | 100  |       | ns   |   |

| Address access time                 | t AA   |      | 1 0 0 | ns   |   |

| CE access time                      | t ACE  |      | 100   | ns   |   |

| Output enable to output valid       | t o e  |      | 5 0   | ns   |   |

| Output hold from address change     | tон    | 1 0  |       | ns   |   |

| CE Low to output active             | tız    | 1 0  |       | ns   | * |

| OE Low to output active .           | tolz   | 5    |       | ns   | * |

| CE High to output in High impedance | tнz    | 0    | 4 0   | ns   | * |

| OE High to output in High impedance | t onz  | 0    | 4 0   | ns   | * |

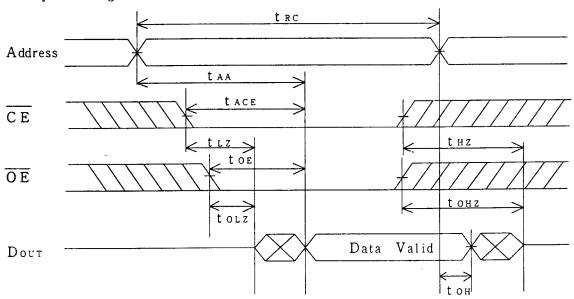

## Write cycle

(Ta = 0 % to + 7 0 % , Vcc = 4.5 V to 5.5 V)

| Parameter                           | Symbol | Min. | Max. | Unit |     |

|-------------------------------------|--------|------|------|------|-----|

| Write cycle time                    | twc    | 100  |      | ns   |     |

| CE Low to end of write              | tcw    | 8 0  |      | ns   |     |

| Address valid to end of write       | taw    | 8 0  |      | ns   |     |

| Address setup time                  | tas    | 0    |      | ns   |     |

| Write pluse width                   | t wp   | 7 5  |      | ns   |     |

| Write recovery time                 | t wr   | 0    |      | ns   |     |

| Input data setup time               | t ow   | 4 0  |      | ns   |     |

| Input data hold time                | tон    | 0    |      | ns   |     |

| WE High to output active            | tow    | 5    |      | ns   | * ( |

| WE Low to output in High impedance  | t wz   | 0    | 4 0  | ns   | * ( |

| OE High to output in High impedance | tонz   | 0    | 4 0  | ns   | * ( |

Note) \*6. Active output to High impedance and High impedance to output active tests specified for a  $\pm 200 \text{mV}$  transition from steady state levels into the test load.

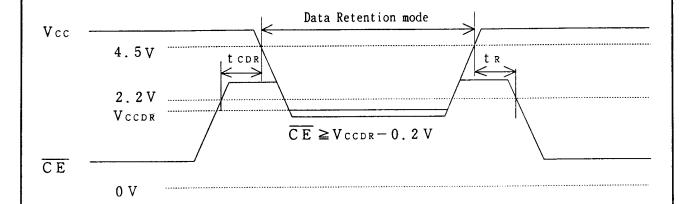

## 9. Data Retention Characteristics

| (Ta= | O°C | to | + | 7 | 0 | $\mathbb{C}$ | ) |

|------|-----|----|---|---|---|--------------|---|

| (14  | 0   | LU | • | • | v | $\sim$       | , |

| Paramenter                    | Symbol | Conditions                       |             | Min.         | Typ. (*7) | Max. | Unit |

|-------------------------------|--------|----------------------------------|-------------|--------------|-----------|------|------|

| Data Retention supply voltage | VCCDR  | CE≥ Vccdr-0                      | . 2 V       | 2.0          |           | 5.5  | V    |

| Data Retention                | ICCDR  | Vccdr=3 V                        | T a = 2 5 ℃ | 2.0          | 0.3       | 1.0  | μΑ   |

| supply current                |        |                                  | T a = 4 0 ℃ |              | Ü. Ü      | 3.0  | μΑ   |

|                               |        | $\overline{CE} \ge V_{CCDR} - 0$ | . 2 V       |              |           | 1 5  | μΑ   |

| Chip enable                   | t CDR  |                                  |             |              |           |      |      |

| setup time                    |        |                                  |             | 0            |           |      | n s  |

| Chip enable                   | tr     |                                  |             | <b>(*</b> 8) |           |      |      |

| hold time                     |        |                                  |             | trc          |           |      | n s  |

Note) \*7. Typical values at Ta=25 $^{\circ}$ C

∗8. Read Cycle

## 10.Pin Capacitance

$(Ta = 25 \, \text{°C}, f = 1 \, \text{MHz})$

| Parameter         | Symbol | Conditions      | Min. | Typ. | Max. | Unit |            |

|-------------------|--------|-----------------|------|------|------|------|------------|

| Input capacitance | CIN    | $V_{IN} = 0 V$  |      |      | 7    | рF   | <b>*</b> 9 |

| I/O capacitance   | C1/0   | $V_{I/O} = 0 V$ |      |      | 1 0  | рF   | <b>*</b> 9 |

Note) \*9. This parameter is sampled and not production tested.

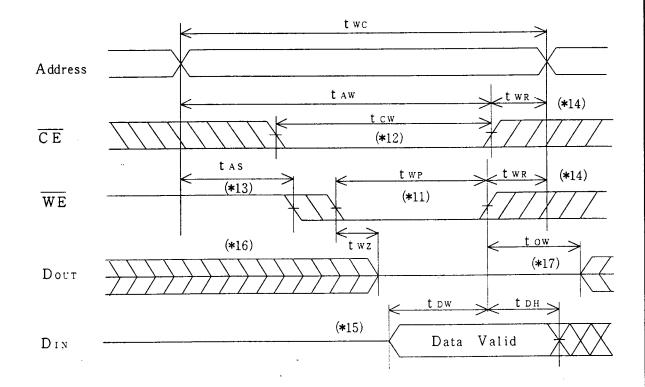

## 11. Timing Chart

Read cycle timing chart— (\*10)

Note) \*10. WE is high for Read cycle.

Write cycle timing chart— (OE Controlled)

Write cycle timing chart—  $\overline{(OE)}$  Low fixed)

- Note) \* 11. A write occurs during the overlap of a low  $\overline{\text{CE}}$ , and a low  $\overline{\text{WE}}$ ,

A write begins at the latest transition among  $\overline{\text{CE}}$  going low, and  $\overline{\text{WE}}$  going low.

A write ends at the earliest transition among  $\overline{\text{CE}}$  going high, and  $\overline{\text{WE}}$  going high.

two is measured from the beginning of write to the end of write.

- \* 12. tem is measured from the later of  $\overline{\text{CE}}$  going low to the end of write.

- \* 13. tas is measured from the address valid to the beginning of write.

- \* 14. twm is measured from the end of write to the address change.

- $\star$  15. During this period, I/O pins are in the output state, therefore the input signals of opposite phase to the outputs must not be applied.

- \* 16. If  $\overline{\text{CE}}$  goes low simultaneously with  $\overline{\text{WE}}$  going low or after  $\overline{\text{WE}}$  going low, the outputs remain in high impedance state.

- \* 17. If  $\overline{\text{CE}}$  goes high simultaneously with  $\overline{\text{WE}}$  going high or before  $\overline{\text{WE}}$  going high, the outputs remain in high impedance state.

Data Retention timing chart -  $\overline{\text{(CE Controlled)}}$

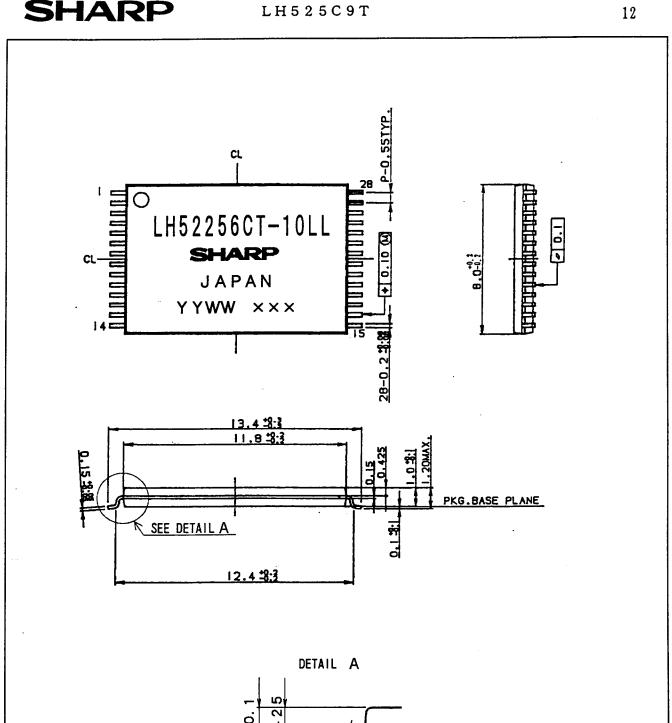

12 Package and packing specification

1. Package Outline Specification

Refer to drawing No.AA1068

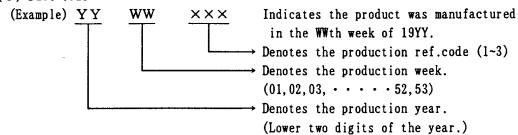

### 2. Markings

2-1. Marking contents

(1) Product name : LH52256CT-10LL

(2) Company name : SHARP

(3) Date code

(4) The marking of "JAPAN" indicates the country of origin.

### 2-2. Marking layout

Refer drawing No. AA1068

(This layout do not define the dimensions of marking character and marking position.)

3. Packing Specification (Dry packing for surface mount packages)

Dry packing is used for the purpose of maintaining IC quality after mounting packages on the PCB (Printed Circuit Board).

When the epoxy resin which is used for plastic packages is stored at high humidity, it may absorb 0.15% or more of its weight in moisture. If the surface mount type package for a relatively large chip absorbs a large amount of moisture between the epoxy resin and insert material (e.g. chip, lead frame) this moisture may suddenly vaporize into steam when the entire package is heated during the soldering process (e.g. VPS). This causes expansion and results in separation between the resin and insert material, and sometimes cracking of the package. This dry packing is designed to prevent the above problem from occurring in surface mount packages.

#### 3-1. Packing Materials

| Material Name          | Material Specificaiton              | Purpose                         |

|------------------------|-------------------------------------|---------------------------------|

| Tray                   | Conductive plastic (80devices/tray) | Fixing of device                |

| Upper cover tray       | Conductive plastic (ltray/case)     | Fixing of device                |

| Laminated aluminum bag | Aluminum polyethylene (1bag/case)   | Drying of device                |

| Des iccant             | Silica gel                          | Drying of device                |

| P P band               | Polypropylene (3pcs/case)           | Fixing of tray                  |

| Inner case             | Card board (800devices/case)        | Packaging of device             |

| Label                  | Paper                               | Indicates part number, quantity |

|                        |                                     | and date of manufacture         |

| Outer case             | Card board                          | Outer packing of tray           |

(Devices shall be placed into a tray in the same direction.)

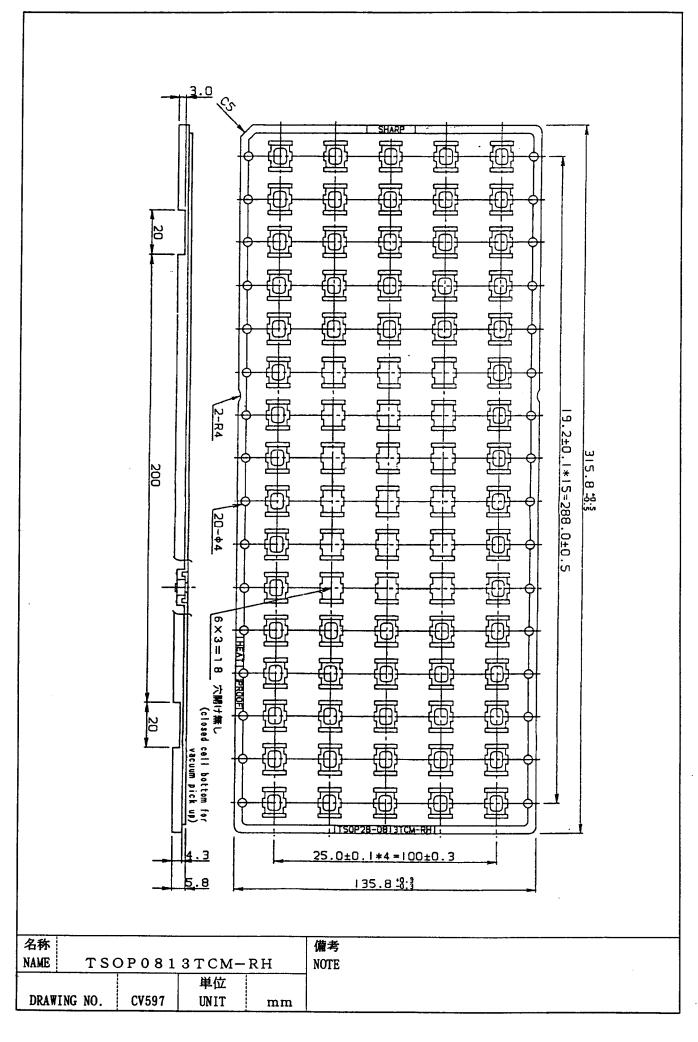

- 3-2. Outline dimension of tray Refer to attached drawing

- 4. Storage and Opening of Dry Packing

- 4-1. Store under conditions shown below before opening the dry packing

(1) Temperature range : 5~40℃

(2) Humidity : 80% RH or less

- 4-2. Notes on opening the dry packing

- (1) Before opening the dry packing, prepare a working table which is grounded against ESD and use a grounding strap.

- (2) The tray has been treated to be conductive or anti-static. If the device is transferred to another tray, use a equivalent tray.

- 4-3. Storage after opening the dry packing

Perform the following to prevent absorption of moisture after opening.

(1) After opening the dry packing, store the ICs in an environment with a temperature of 5~25℃ and a relative humidity of 60% or less and mount ICs within 3 days after opening dry packing.

- 4-4. Baking (drying) before mounting

- (1) Baking is necessary

- (A) If the humidity indicator in the desiccant becomes pink

- (B) If the procedure in section 4-3 could not be performed

- (2) Recommended baking conditions

If the above conditions (A) and (B) are applicable, bake it before mounting. The recommended conditions are 16~24 hours at 120°C.

Heat resistance tray is used for shipping tray.

- 5. Surface Mount Conditions

Please perform the following conditions when mounting ICs not to deteriorate IC quality.

5-1. Soldering conditions (The following conditions are valid only for one time soldering.)

| Mounting Method  | Temperature and Duration                         | Measurement Point |

|------------------|--------------------------------------------------|-------------------|

| Reflow soldering | Peak temperature of 230°C or less,               | IC surface        |

| (air)            | duration less than 15 seconds.                   |                   |

|                  | 200℃ or over, duration less than 40 seconds.     |                   |

|                  | Temperature increase rate of $1\sim4\%$ /second. |                   |

| Manual soldering | 260℃ or less, duration less                      | IC outer lead     |

| (soldering iron) | than 10 seconds.                                 | surface           |

5-2. Conditions for removal of residual flux

(1) Ultrasonic washing power

25 Watts/liter or less

(2) Washing time

Total 1 minute maximum

(3) Solvent temperature :  $15\sim40^{\circ}$

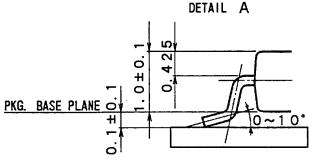

| 名称   |          |       | リード仕上       | TIN-LEAD | 備考   | プラスチックパッケージ外形寸法は、パリを含まないものとする。              |

|------|----------|-------|-------------|----------|------|---------------------------------------------|

| NAME | TSOP28-P | -0813 | LEAD FINISH | PLATING  | NOTE | Plastic body dimensions do not include burr |

|      | •        |       | 単位          |          |      | of resin.                                   |

| DRAW | ING NO.  | AA106 | S8 UNIT     | mm       |      |                                             |

STATIC SRAM RAM Random Access Memory LH52256CT-10LL 256K (32Kx8) (100 ns) (TSOP)