## **FEATURES**

- 512K x 8 Bit Configuration

- 5 V Write/Erase Operation (5 V V<sub>PP</sub>, 3.3 V<sub>CC</sub>)

V<sub>CC</sub> for Write/Erase at as low as 2.9 V

- VCC for Write/Erase at as low as 2

- Min. 2.7 V Read Capability

- 190 ns Maximum Access Time (V<sub>CC</sub> = 2.7 V)

- 2 Banks Enable the Simultaneous Read/Write/Erase Operation

- 32 Independently Lockable Blocks (16K)

- 100,000 Erase Cycles per Block

- Automated Byte Write/Block Erase

- Command User Interface

- Status Register

- System Performance Enhancement

- Erase Suspend for Read

- Two-Byte Write

- Bank Erase

- Data Protection

- Hardware Erase/Write Lockout during Power Transitions

- Software Erase/Write Lockout

- Independently Lockable for Write/Erase on Each Block (Lock Block and Protect Set/Reset)

- 20  $\mu$ A (Maximum) I<sub>CC</sub> in CMOS Standby

- State-of-the-Art 0.55 µm ETOX™ Flash Technology

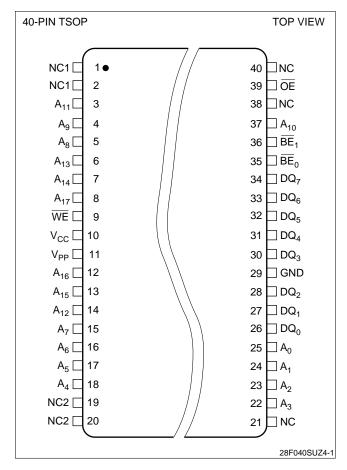

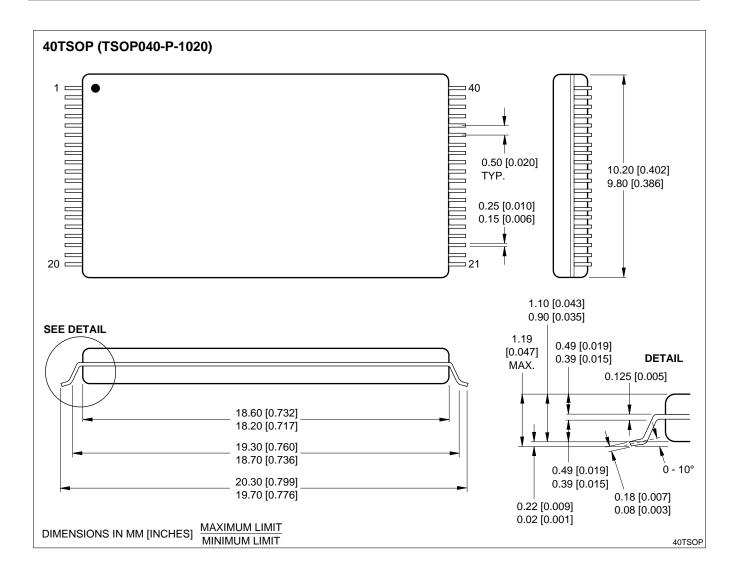

- 40-Pin, 1.2 mm x 10 mm x 20 mm TSOP (Type I) Package

Figure 1. TSOP Configuration

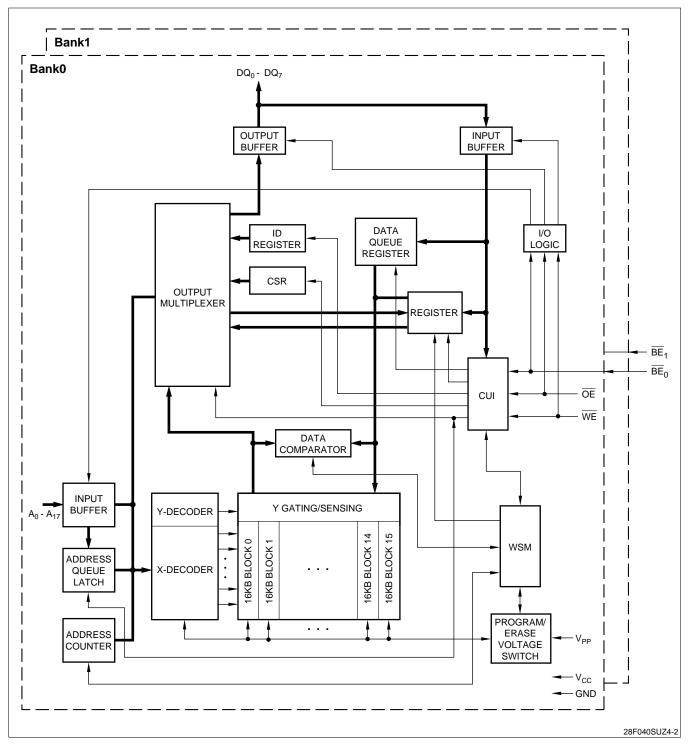

Figure 2. LH28F040SUTD-Z4 Block Diagram

## PIN DESCRIPTION

| SYMBOL                            | TYPE         | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> - A <sub>13</sub>  | INPUT        | BYTE-SELECT ADDRESSES: Select a byte within one 16K block. These addresses are latched during Data Writes.                                                                                                                                                                                                                                      |

| A <sub>14</sub> - A <sub>17</sub> | INPUT        | BLOCK-SELECT ADDRESSES: Select 1 of 16K Erase blocks. These addresses are latched during Data Writes, Erase and Lock-Block operations.                                                                                                                                                                                                          |

| DQ <sub>0</sub> - DQ <sub>7</sub> | INPUT/OUTPUT | DATA INPUT/OUTPUT: Inputs data and commands during CUI write cycles. Outputs array, buffer, identifier or status data in the appropriate Read mode. Floated when the chip is de-selected or the outputs are disabled.                                                                                                                           |

| BE <sub>0</sub> , BE <sub>1</sub> | INPUT        | <b>BANK ENABLE INPUTS</b> : Activate the device's control logic, input buffers, decoders and sense amplifiers. $\overline{CE}$ must be low to select the device. When $\overline{BE}_0$ is low, bank0 is active. When $\overline{BE}_1$ is low, bank1 is active. Both $\overline{BE}_0$ and $\overline{BE}_1$ must not be low at the same time. |

| ŌĒ                                | INPUT        | <b>OUTPUT ENABLE:</b> Gates device data through the output buffers when low. The outputs float to tri-state off when $\overline{\text{OE}}$ is high.                                                                                                                                                                                            |

| WE                                | INPUT        | WRITE ENABLE: Controls access to the CUI, Page Buffers, Data Queue Registers and Address Queue Latches. WE is active low, and latches both address and data (command or array) on its rising edge.                                                                                                                                              |

| V <sub>PP</sub>                   | SUPPLY       | <b>ERASE/WRITE POWER SUPPLY (5.0 V ±0.5 V):</b> For erasing memory array blocks or writing bytes into the flash array.                                                                                                                                                                                                                          |

| V <sub>CC</sub>                   | SUPPLY       | <b>DEVICE POWER SUPPLY (3.3 V ±0.3 V):</b> Do not leave any power pins floating.                                                                                                                                                                                                                                                                |

| GND                               | SUPPLY       | GROUND FOR ALL INTERNAL CIRCUITRY: Do not leave any ground pins floating.                                                                                                                                                                                                                                                                       |

| NC                                |              | NO CONNECTION                                                                                                                                                                                                                                                                                                                                   |

| NC1, NC2                          |              | <b>OPEN PIN:</b> But NC1 (between pin1 and pin2) and also NC2 (pin19 and pin20) are connected inside package.                                                                                                                                                                                                                                   |

### INTRODUCTION

Sharp's LH28F040SUTD-Z4 4M Flash Memory is a revolutionary architecture which enables the design of truly mobile, high performance, personal computing and communication products. With innovative capabilities, 3.3V low power operation and very high read/write performance, the LH28040SU-Z4 is also the ideal choice for designing embedded mass storage flash memory systems.

The LH28F040SUTD-Z4 is a very high density, highest performance non-volatile read/write solution for solid-state storage applications. Its independently lockable 32 symmetrical blocked architecture (16K each) extended cycling, low power operation, very fast write and read performance and selective block locking provide a highly flexible memory component suitable for high density memory cards, Resident Flash Arrays and

PCMCIA-ATA Flash Drives. The LH28F040SUTD-Z4's 5.0 V/3.3 V power supply operation enables the design of memory cards which can be read in 3.3 V system and written in 5.0 V/3.3 V systems. Its x8 architecture allows the optimization of memory to processor interface. The flexible block locking option enables bundling of executable application software in a Resident Flash Array or memory card. Manufactured on Sharp's 0.55 µm ETOX<sup>TM</sup> process technology, the LH28F040SUTD-Z4 is the most cost-effective, high-density 3.3 V flash memory.

LH28F040SUTD-Z4 divides 4M into two areas. Each area can read/write/erase independently. For example, while you write and erase on one area, you can simultaneously read the data from the other area. This enables users to reduce the number of components in their system.

## **DESCRIPTION**

The LH28F040SUTD-Z4 is a high performance 4M (4,194,304 bit) block erasable non-volatile random access memory organized as  $256K \times 8 \times 2$  banks. The LH28F040SUTD-Z4 includes thirty-two 16K (16,384) blocks. A chip memory map is shown in Figure 3.

The two banks, the one selected by  $\overline{BE}_0$  (bank0) and the other selected by  $\overline{BE}_1$  (bank1) can be controlled independently. For example, while erase the data in bank0, the data in bank1 can be read out.

The implementation of a new architecture, with many enhanced features, will improve the device operating characteristics and results in greater product reliability and ease of use.

Among the significant enhancements of the LH28F040SUTD-Z4:

- 3 V Read, 5 V Write/Erase Operation (5 V V<sub>PP</sub>, 3 V V<sub>CC</sub>)

- Low Power Capability (2.7 V V<sub>CC</sub> Read)

- Improved Write/Erase Performance (Two-Byte Serial Write, Bank Erase)

- · Dedicated Block Write/Erase Protection

- Command-Controlled Memory Protection Set/Reset Capability

The LH28F040SUTD-Z4 will be available in a 40-pin, 1.2 mm thick  $\times$  10 mm  $\times$  20 mm TSOP (Type I) package. This form factor and pinout allow for very high board layout densities.

A Command User Interface (CUI) serves as the system interface between the microprocessor or microcontroller and the internal memory operation.

Internal Algorithm Automation allows Byte Writes and Block Erase operations to be executed using a Two-Write command sequence to the CUI in the same way as the LH28F008SA 8M Flash memory.

A Superset of commands have been added to the basic LH28F008SA command-set to achieve higher write performance and provide additional capabilities. These new commands and features include:

- Software Locking of Memory Blocks

- Memory Protection Set/Reset Capability

- · Two-Byte Serial Writes in 8-bit Systems

- Bank Erase All Unlocked Blocks

Writing of memory data is performed typically within 20  $\mu$ s. A Block Erase operation erases one of the 32 blocks in typically 1.5 seconds, independent of the other blocks.

LH28F040SUTD-Z4 allows to erase all unlocked blocks for each bank selected by  $\overline{BE}_0$  or  $\overline{BE}_1$ . It is desirable in case of which you have to implement Erase operation maximum 32 times.

LH28F040SUTD-Z4 enables Two-Byte serial Write which is operated by three times command input. This feature can improve system write performance by up to typically 17  $\mu$ s per byte.

All operations are started by a sequence of Write commands to the device. Status Register (described in detail later) provide information on the progress of the requested operation.

Same as the LH28F008SA, LH28F040SUTD-Z4 requires an operation to complete before the next operation can be requested, also it allows to suspend block erase to read data from any other block, and allow to resume erase operation.

The LH28F040SUTD-Z4 provides user-selectable block locking to protect code or data such as Device Drivers, PCMCIA card information, ROM-Executable OS or Application Code. Each block has an associated non-volatile lock-bit which determines the lock status of the block. In addition, the LH28F040SUTD-Z4 has a software controlled master Write Protect circuit which prevents any modifications to memory blocks whose lock-bits are set.

When the device power-up, Write Protect Set/Confirm command must be written both in bank0 and bank1. Otherwise, all lock bits in the device remain being locked, can't perform the Write to each block and single Block Erase. Write Protect Set/Confirm command must be written to reflect the actual lock status. However, when the device power-on, Erase All Unlocked Blocks can be used. If used, Erase is performed with reflecting actual lock status, and after that Write and Block Erase can be used.

The LH28F040SUTD-Z4 contains Status Register to accomplish various functions:

A Compatible Status Register (CSR) which is 100% compatible with the LH28F008SA Flash memory's Status Register. This register, when used alone, provides a straightforward upgrade capability to the LH28F040SUTD-Z4 from a LH28F008SA based design.

The LH28F040SUTD-Z4 is specified for a maximum access time of 150 ns ( $t_{ACC}$ ) at 3.3 V operation (3.0 to 3.6 V) over the commercial temperature range (-20 to +70°C). A corresponding maximum access time of 190 ns ( $t_{ACC}$ ) at 2.7 V (-20 to +70°C) is achieved for reduced power consumption applications.

The LH28F040SUTD-Z4 incorporates an Automatic Power Saving (APS) feature which substantially reduces the active current when the device is in static mode of operation (addresses not switching).

In APS mode, the typical I<sub>CC</sub> current is 2 mA at 3.3 V.

A bank reset mode of operation is enabled when whole  $\overline{BE}_0$  (or  $\overline{BE}_1$ ),  $\overline{WE}$  and  $\overline{OE}$  hold low more than 5 µs. In this mode, all operations are aborted, the internal control circuit is reset and CSR register is cleared. When the device power up, this bank reset operation must be executed for each bank to initialize the control circuit. If  $\overline{BE}_X$  (either  $\overline{BE}_0$  or  $\overline{BE}_1$  which is in low state) and or  $\overline{WE}$  and or  $\overline{OE}$  and or goes high, chip reset mode will be finished. It needs more than 750 ns from one of the  $\overline{BE}_X$ ,  $\overline{WE}$  or  $\overline{OE}$  goes high until output data are valid. It is impossible to reset the whole chip at once, the bank reset must be executed separately for bank0 and bank1.

A CMOS Standby mode of operation is enabled when  $\overline{\text{BE}}_X$  transitions high with all input control pins at CMOS levels. In this mode, the device draws an I<sub>CC</sub> standby current of 20  $\mu$ A.

Please do not execute reprogramming 0 for the bit which has already been programmed 0. Overwrite operation may generate unerasable bit. In case of reprogramming 0 to the data which has been programmed 1.

- Program 0 for the bit in which you want to change data from 1 to 0.

- Program 1 for the bit which has already been programmed 0.

For example, changing data from 10111101 to 10111100 requires 11111110 programming.

## **MEMORY MAP**

| Bank(            | ) (BE <sub>0</sub> = Low) |    | Bank1 (BE <sub>1</sub> = Low) |    |

|------------------|---------------------------|----|-------------------------------|----|

| BFFFFH<br>BC000H | 16KB BLOCK                | 15 | 3FFFFH 16KB BLOCK             | 15 |

| BFFFH<br>38000H  | 16KB BLOCK                | 14 | 3BFFFH<br>38000H 16KB BLOCK   | 14 |

| 37FFFH<br>34000H | 16KB BLOCK                | 13 | 37FFFH<br>34000H 16KB BLOCK   | 13 |

| 33FFFH<br>30000H | 16KB BLOCK                | 12 | 33FFFH<br>30000H 16KB BLOCK   | 12 |

| PFFFH<br>PC000H  | 16KB BLOCK                | 11 | 2FFFFH<br>2C000H 16KB BLOCK   | 11 |

| BFFFH<br>28000H  | 16KB BLOCK                | 10 | 2BFFFH<br>28000H 16KB BLOCK   | 10 |

| 27FFFH<br>24000H | 16KB BLOCK                | 9  | 27FFFH<br>24000H 16KB BLOCK   | 9  |

| 23FFFH<br>20000H | 16KB BLOCK                | 8  | 23FFFH<br>20000H 16KB BLOCK   | 8  |

| FFFFH<br>C000H   | 16KB BLOCK                | 7  | 1FFFFH<br>1C000H 16KB BLOCK   | 7  |

| BFFFH<br>18000H  | 16KB BLOCK                | 6  | 18FFFH<br>18000H 16KB BLOCK   | 6  |

| 17FFFH<br>14000H | 16KB BLOCK                | 5  | 17FFFH<br>14000H 16KB BLOCK   |    |

| 10000H           | 16KB BLOCK                | 4  | 13FFFH<br>10000H 16KB BLOCK   | 4  |

| DEFFEH<br>DC000H | 16KB BLOCK                | 3  | 0FFFFH 0C000H 16KB BLOCK      | 3  |

| DBFFFH<br>D8000H | 16KB BLOCK                | 2  | 08FFFH 08000H 16KB BLOCK      | 2  |

| 07FFFH<br>04000H | 16KB BLOCK                | 1  | 07FFFH<br>04000H 16KB BLOCK   |    |

| 00000H           | 16KB BLOCK                | 0  | 03FFFH<br>00000H 16KB BLOCK   | (  |

Figure 3. Memory Map

# **BUS OPERATIONS, COMMANDS AND STATUS REGISTER DEFINITIONS**

# **Bus Operations**

| MODE               |        | BE <sub>0</sub> | BE <sub>1</sub> | ŌĒ              | WE              | A <sub>0</sub>  | DQ <sub>0</sub> _DQ <sub>7</sub> | NOTE |

|--------------------|--------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------------------------|------|

| Read               | Bank 0 | $V_{IL}$        | V <sub>IH</sub> | V               | W               | X               | 2                                | 1    |

| Reau               | Bank 1 | $V_{IH}$        | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | ^               | D <sub>OUT</sub>                 | I    |

| Output Disable     |        | X               | Х               | V <sub>IH</sub> | V <sub>IH</sub> | X               | High-Z                           | 1    |

| Standby            |        | $V_{IH}$        | V <sub>IH</sub> | Х               | Х               | Х               | High-Z                           | 1    |

| Manufacturer ID    | Bank 0 | $V_{IL}$        | V <sub>IH</sub> | V               | W               | V <sub>IL</sub> | ВОН                              | 2    |

| iviaridiacidiei 1D | Bank 1 | $V_{IH}$        | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> |                 |                                  | 2    |

| Device ID          | Bank 0 | $V_{IL}$        | V <sub>IH</sub> | V               | W               | \/              | 31H                              | 2    |

| Device ID          | Bank 1 | $V_{IH}$        | $V_{IL}$        | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> |                                  | 2    |

| Write              | Bank 0 | $V_{IL}$        | V <sub>IH</sub> | \/              | \/              | , v             | D <sub>IN</sub>                  | 1 2  |

| vviile             | Bank1  | $V_{IH}$        | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Х               |                                  | 1, 3 |

- 1. X can be  $V_{IH}$  or  $V_{IL}$  for address or control pins, which is either  $V_{OL}$  or  $V_{OH}$ .

2.  $A_0$  at  $V_{IL}$  provide manufacturer ID codes.  $A_0$  at  $V_{IH}$  provide device ID codes. All other addresses are set to zero.

- 3. Commands for different Erase operations, Data Write operations, and Lock-Block operations can only be successfully completed when  $V_{PP} = V_{PPH}$ .

- 4. Both  $\overline{BE}_0$  and  $\overline{BE}_1$  must not be low at the same time.

# LH28F008SA-Compatible Mode Command Bus Definitions

Following is the commands to be applied to each bank.

| COMMAND                         | FIR   | ST BUS CYCI | _E   | SECOND BUS CYCLE |         |      | NOTE |

|---------------------------------|-------|-------------|------|------------------|---------|------|------|

| COMMAND                         | OPER. | ADDRESS     | DATA | OPER.            | ADDRESS | DATA | NOTE |

| Read Array                      | Write | Х           | FFH  | Read             | AA      | AD   |      |

| Intelligent Identifier          | Write | Х           | 90H  | Read             | IA      | ID   | 1    |

| Read Compatible Status Register | Write | Х           | 70H  | Read             | Х       | CSRD | 2    |

| Clear Status Register           | Write | Х           | 50H  |                  |         |      | 3    |

| Byte Write                      | Write | Х           | 40H  | Write            | WA      | WD   |      |

| Alternate Byte Write            | Write | Х           | 10H  | Write            | WA      | WD   |      |

| Block Erase/Confirm             | Write | Х           | 20H  | Write            | BA      | D0H  | 4    |

| Erase Suspend/Resume            | Write | Х           | ВОН  | Write            | Х       | D0H  | 4    |

ADDRESS DATA

AA = Array Address

BA = Block Address

IA = Identifier Address

WA = Write Address

AD = Array Data

CSRD = CSR Data

ID = Identifier Data

WD = Write Data

X = Don't Care

#### NOTES:

- 1. Following the intelligent identifier command, two Read operations access the manufacturer and device signature codes.

- 2. The CSR is automatically available after device enters Data Write, Erase or Suspend operations.

- 3. Clears CSR.3, CSR.4, and CSR.5. See Status register definitions.

- 4. While device performs Block Erase, if you issue Erase Suspend command (B0H), be sure to confirm ESS (Erase-Suspend-Status) is set to 1 on compatible status register. In the case, ESS bit was not set to 1, also completed the Erase (ESS = 0, WSMS = 1), be sure to issue Resume command (D0H) after completed next Erase command. Beside, when the Erase Suspend command is issued, while the device is not in Erase, be sure to issue Resume command (D0H) after the next erase complete.

7

## LH28F040SUTD-Z4 Performance Enhancement Command Bus Definitions

Following is the commands to be applied to each bank.

| COMMAND                        | FIRST | BUS C | YCLE | SECO  | ND BU | S CYCLE   | THIE  | RD BUS | CYCLE     | NOTE    |

|--------------------------------|-------|-------|------|-------|-------|-----------|-------|--------|-----------|---------|

| COMMAND                        | OPER. | ADD.  | DATA | OPER. | ADD.  | DATA      | OPER. | ADD.   | DATA      | NOIL    |

| Protect Set/Confirm            | Write | Х     | 57H  | Write | 0FFH  | D0H       |       |        |           | 1, 2, 6 |

| Protect Reset/Confirm          | Write | Х     | 47H  | Write | 0FFH  | D0H       |       |        |           | 3, 6    |

| Lock Block/Confirm             | Write | Х     | 77H  | Write | BA    | D0H       |       |        |           | 1, 2, 4 |

| Bank Erase All Unlocked Blocks | Write | Х     | A7H  | Write | Х     | D0H       |       |        |           | 1, 2    |

| Two-Byte Write                 | Write | Х     | FBH  | Write | A10   | WD (L, H) | Write | WA     | WD (H, L) | 1, 2, 5 |

ADDRESS DATA

BA = Block Address AD = Array Data

$WA = Write \ Address$   $WD (L, H) = Write \ Data (Low, High)$  $X = Don't \ Care$   $WD (H, L) = Write \ Data (High, Low)$

#### NOTES:

- 1. After initial device power-up, or reset is completed, the block lock status bit default to the locked state independent of the data in the corresponding lock bits. In order to upload the lock bit status, it requires to write Protect Set/Confirm command.

- 2. To reflect the actual lock-bit status, the Protect Set/Confirm command must be written after Lock Block/Confirm command.

- 3. When Protect Reset/Confirm command is written, all blocks can be written and erased regardless of the state of the lock-bits.

- 4. The Lock Block/Confirm command must be written after Protect Reset/Confirm command was written.

- 5. A<sub>0</sub> is automatically complemented to load second byte of data A<sub>0</sub> value determines which WD is supplied first: A<sub>0</sub> = 0 looks at the WDL, A<sub>0</sub> = 1 looks at the WDH.

- Second bus cycle address of Protect Set/Confirm and Protect Reset/Confirm command is 0FFH. Specifically A<sub>9</sub> A<sub>8</sub> = 0, A<sub>7</sub> A<sub>0</sub> = 1, others are don't care.

# Compatible Status Register

Following is the commands to be applied to each bank.

| WSMS | ESS | ES | DWS | VPPS | R | R | R |

|------|-----|----|-----|------|---|---|---|

| 7    | 6   | 5  | 4   | 3    | 2 | 1 | 0 |

CSR.7 = WRITE STATE MACHINE STATUS (WSMS)

1 = Ready

2 = Busy

CSR.6 = ERASE-SUSPEND STATUS (ESS)

1 = Erase Suspended

0 = Erase in Progress/Completed

CSR.5 = ERASE STATUS (ES)

1 = Error in Block Erasure

0 = Successful Block Erase

CSR.4 = DATA-WRITE STATUS (DWS)

1 = Error in Data Write

0 = Data Write Successful

CSR.3 =  $V_{PP}$  STATUS (VPPS)

1 = V<sub>PP</sub> Low Detect, Operation Abort

$0 = V_{PP} OK$

#### NOTES:

- RY/BY output or WSMS bit must be checked to determine completion of an operation (Erase Suspend, Erase or Data Write) before the appropriate Status bit (ESS, ES or DWS) is checked for success.

- If DWS and ES are set to '1' during an erase attempt, an improper command sequence was entered. Clear the CSR and attempt the operation again.

- The VPPS bit, unlike an A/D converter, does not provide continuous indication of V<sub>PP</sub> level. The WSM interrogates V<sub>PP</sub>'s level only after the Data-Write or Erase command sequences have been entered, and informs the system if V<sub>PP</sub> has not been switched on. VPPS is not guaranteed to report accurate feedback between V<sub>PPL</sub> and V<sub>PPH</sub>.

- CSR.2 CSR.0 = Reserved for further enhancements. These bits are reserved for future use and should be masked out when polling the CSR.

# 4M DUAL WORK FLASH MEMORY SOFTWARE ALGORITHMS

#### Overview

With the advanced Command User Interface, its Performance Enhancement commands and Status Registers, the software code required to perform a given operation may become more intensive but it will result in much higher write/erase performance compared with current flash memory architectures.

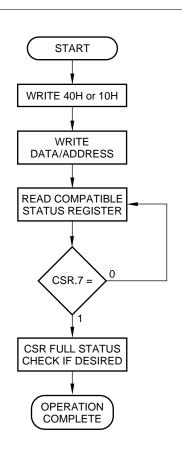

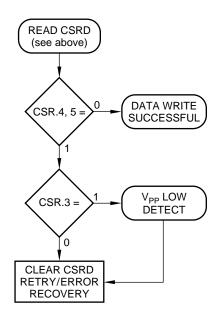

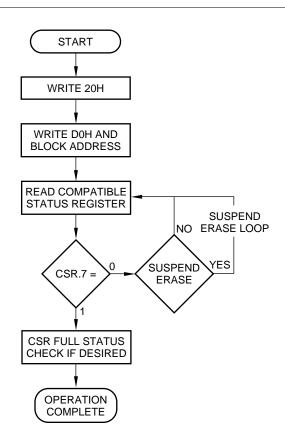

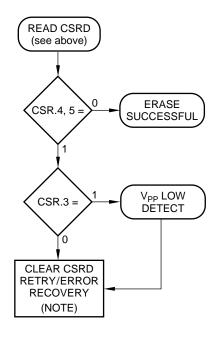

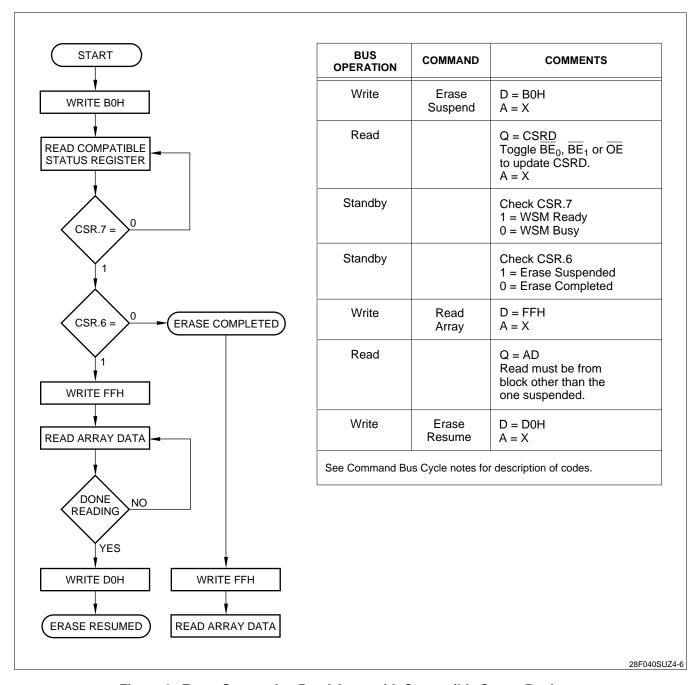

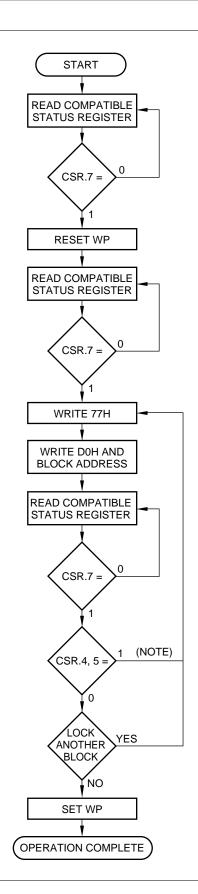

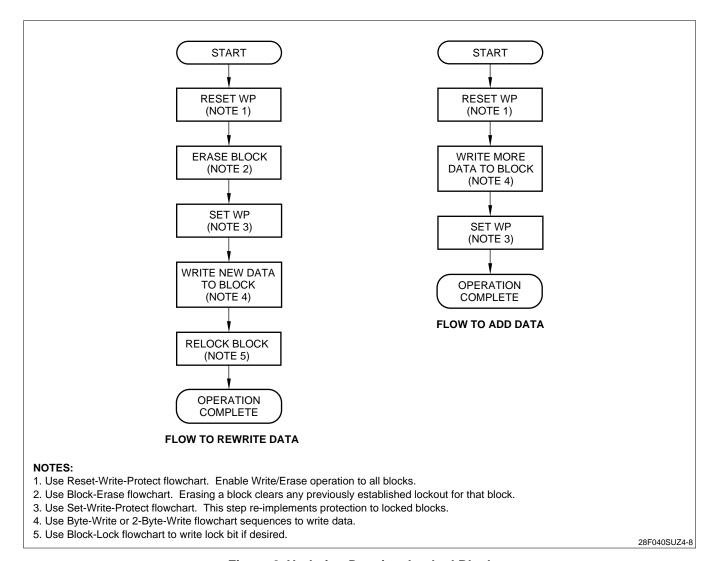

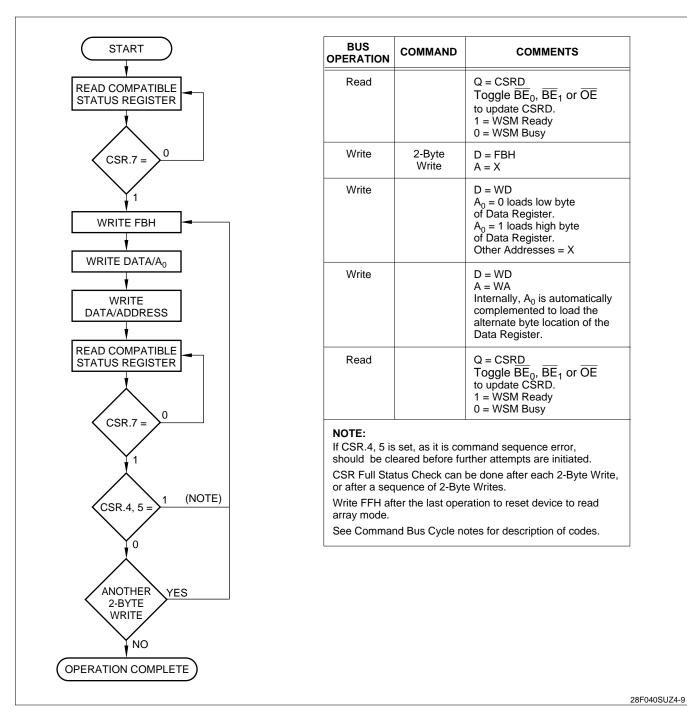

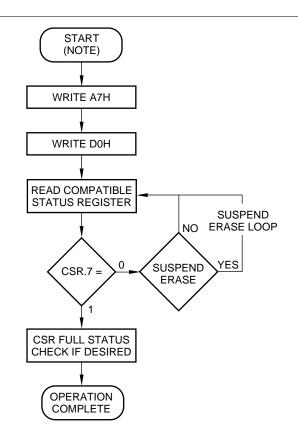

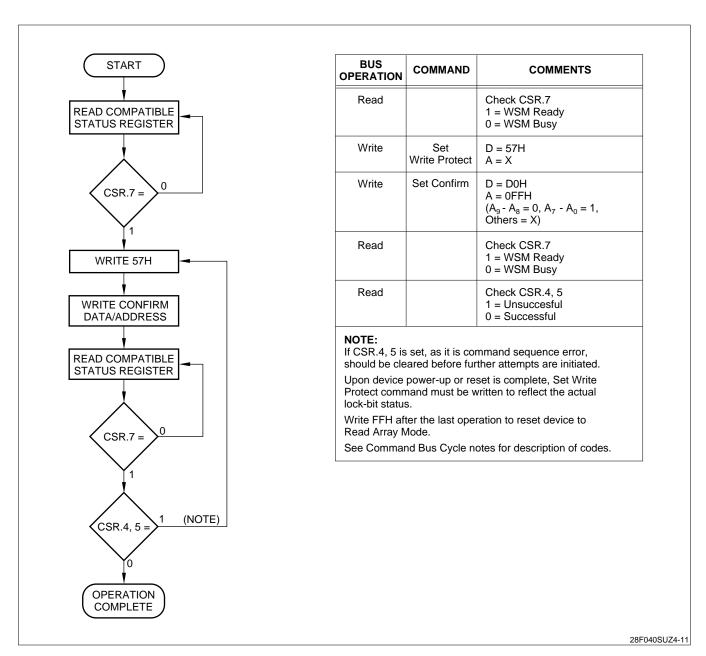

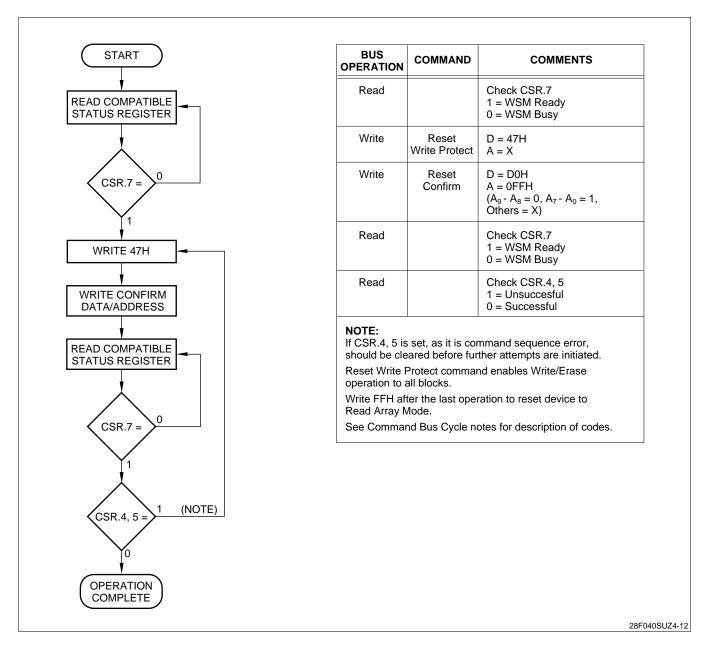

The software flowcharts describing how a given operation proceeds are shown here. Figures 4 through 6 depict flowcharts using the 2nd generation flash device in the LH28F008SA-compatible mode. Figures 7 through 12 depict flowcharts using the 2nd generation flash device's performance enhancement commands mode.

When the device power-up or reset is completed, Set Write Protect command must be written to both the bank selected by  $\overline{BE}_0$  and  $\overline{BE}_1$  in order to reflect actual block lock status.

When the device power-up or reset is completed, all blocks come up locked. Therefore, Byte Write, Two Byte Serial Write and Block Erase can not be performed in each block. However, at that time, Erase All Unlocked Block is performed normally, if used, and reflect actual

lock status, also the unlocked block data is erased. When the device power-up or reset is completed, Set Write Protect command must be written to reflect actual block lock status.

Reset Write Protect command must be written before Write Block Lock command. To reflect actual block lock status, Set Write Protect command is succeeded.

The Compatible Status Register (CSR) used to determine which blocks are locked. In order to see Lock Status of certain block, a Byte Write command (WA = Block Address, WD = FHH) is written to the CUI, after issuing Set Write Protect command. If CSR.7, CSR.5 and CSR.4 (WSMS, ES and DWS) are set to '1's, the block is locked. If CSR.7 is set to '1', the block is not locked.

Reset Write Protect command enables Write/Erase operation to each block.

In the case of Block Erase is performed, the block lock information is also erased. Block Lock command and Set Write Protect command must be written to prohibit Write/Erase operation to each block.

There are unassigned commands. It is not recommended that the customer use any command other than the valid commands specified in "Command Bus Definitions". Sharp reserved the right to redefine these codes for future functions.

9

| BUS<br>OPERATION | COMMAND    | COMMENTS                                                                                                         |

|------------------|------------|------------------------------------------------------------------------------------------------------------------|

| Write            | Byte Write | D = 40H or 10H<br>A = X                                                                                          |

| Write            |            | D = WD<br>A = WA                                                                                                 |

| Read             |            | $ Q = CSRD \\ Toggle \ \overline{BE}_0, \ \overline{BE}_1 \ or \ \overline{OE} \\ to \ update \ CSRD. \\ A = X $ |

| Standby          |            | Check CSR.7<br>1 = WSM Ready<br>0 = WSM Busy                                                                     |

Repeat for subsequent Byte Writes.

CSR Full Status Check can be done after each Byte Write, or after a sequence of Byte Writes.

Write FFH after the last operation to reset device to read array mode.

See Command Bus Cycle notes for description of codes.

## **CSR FULL STATUS CHECK PROCEDURE**

| BUS<br>OPERATION | COMMAND | COMMENTS                                                                |

|------------------|---------|-------------------------------------------------------------------------|

| Standby          |         | Check CSR.4, 5 1 = Data Write Unsuccessful 0 = Data Write Successful    |

| Standby          |         | Check CSR.3<br>1 = V <sub>PP</sub> Low Detect<br>0 = V <sub>PP</sub> OK |

$\ensuremath{\mathsf{CSR.3}}, 4, 5$  should be cleared, if set, before further attempts are initiated.

Figure 4. Byte Writes with Compatible Status Register

| BUS<br>OPERATION | COMMAND     | COMMENTS                                                                                                   |

|------------------|-------------|------------------------------------------------------------------------------------------------------------|

| Write            | Block Erase | D = 20H<br>A = X                                                                                           |

| Write            | Confirm     | D = D0H<br>A = BA                                                                                          |

| Read             |             | $ Q = CSRD \\ Toggle \ \overline{BE}_0, \ \overline{BE}_1 \ \text{or OE} \\ to \ update \ CSRD. \\ A = X $ |

| Standby          |             | Check CSR.7<br>1 = WSM Ready<br>0 = WSM Busy                                                               |

Repeat for subsequent Block Erasures.

CSR Full Status Check can be done after each Block Erase, or after a sequence of Block Erasures.

Write FFH after the last operation to reset device to read array mode.

See Command Bus Cycle notes for description of codes.

#### **CSR FULL STATUS CHECK PROCEDURE**

| BUS<br>OPERATION | COMMAND | COMMENTS                                                                            |

|------------------|---------|-------------------------------------------------------------------------------------|

| Standby          |         | Check CSR.4, 5 1 = Erase Error 0 = Erase Successful Both 1 = Command Sequence Error |

| Standby          |         | Check CSR.3<br>1 = V <sub>PP</sub> Low Detect<br>0 = V <sub>PP</sub> OK             |

$\ensuremath{\mathsf{CSR.3}}, 4, 5$  should be cleared, if set, before further attempts are initiated.

#### NOTE:

If CSR.3 (VPPS) is set to '1', after clearing CSR.3/4/5,

- 1. Issue Reset WP command.

- 2. Retry Single Block Erase command.

- 3. Set WP command is issued, if necessary.

If CSR.3 (VPPS) is set to '0', after clearing CSR.3/4/5,

1. Retry Single Block Erase command.

Where power off or chip reset during erase operation,

- 1. Clear CSR.3/4/5 and issue Reset WP command,

- 2. Retry Single Block Erase command.

- 3. Set WP command is issued, if necessary.

Figure 5. Block Erase with Compatible Status Register

Figure 6. Erase Suspend to Read Array with Compatible Status Register

| BUS<br>OPERATION | COMMAND                | COMMENTS                                                                                                                                     |

|------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Read             |                        | $Q = CSR\underline{D}$ $Toggle \ BE_0, \ \overline{BE}_1 \ or \ \overline{OE}$ to update CSRD. $1 = WSM \ Ready$ $0 = WSM \ Busy$            |

| Write            | Reset<br>Write Protect | After Write D = 47H A = X,<br>Write D = D0H A = 0FFH                                                                                         |

| Read             |                        | $Q = CSR\underline{D}$ $Toggle \ \overline{BE}_0, \ \overline{BE}_1 \ or \ \overline{OE}$ to update CSRD. $1 = WSM \ Ready$ $0 = WSM \ Busy$ |

| Write            | Lock Block             | D = 77H<br>A = X                                                                                                                             |

| Write            | Confirm                | D = D0H<br>A = BA                                                                                                                            |

| Read             |                        | Q = CSRD<br>Toggle BE <sub>0</sub> , BE <sub>1</sub> , or OE<br>to update CSRD.<br>1 = WSM Ready<br>0 = WSM Busy                             |

| Write            | Set<br>Write Protect   | After Write D = 57H A = X,<br>Write D = D0H A = 0FFH                                                                                         |

### NOTE:

See CSR Full Status Check for Data-Write operation. If CSR.4, 5 is set, as it is command sequence error, should be cleared before further attempts are initiated.

Write FFH after the last operation to reset device to read array mode.

See Command Bus Definitions for description of codes.

Figure 7. Block Locking Scheme

SHARP 13

Figure 8. Updating Data in a Locked Block

Figure 9. Two-Byte Serial Writes with Compatible Status Registers

| BUS<br>OPERATION | COMMAND                         | COMMENTS                                                                                                |

|------------------|---------------------------------|---------------------------------------------------------------------------------------------------------|

| Write            | Erase All<br>Unlocked<br>Blocks | D = A7H<br>A = X                                                                                        |

| Write            | Confirm                         | D = D0H<br>A = X                                                                                        |

| Read             |                                 | Q = CSRD<br>Toggle $\overline{BE}_0$ , $\overline{BE}_1$ or $\overline{OE}$<br>to update CSRD.<br>A = X |

| Standby          |                                 | Check CSR.7<br>1 = WSM Ready<br>0 = WSM Busy                                                            |

CSR Full Status Check can be done after Erase All Unlocked Block, or after a sequence of Erasures.

Write FFH after the last operation to reset device to read array mode.

See Command Bus Cycle notes for description of codes.

#### NOTE:

Where power off or reset during erase operation,

- 1. Clear CSR.3/4/5 and issue Reset WP command,

- Retry Erase All Unlocked Block Erase command to erase all blocks, or issue Single Block Erase to erase all of the unlocked blocks in sequence.

- 3. Set WP command is issued, if necessary.

### **CSR FULL STATUS CHECK PROCEDURE**

| BUS<br>OPERATION | COMMAND | COMMENTS                                                                            |

|------------------|---------|-------------------------------------------------------------------------------------|

| Standby          |         | Check CSR.4, 5 1 = Erase Error 0 = Erase Successful Both 1 = Command Sequence Error |

| Standby          |         | Check CSR.3<br>1 = V <sub>PP</sub> Low Detect<br>0 = V <sub>PP</sub> OK             |

$\ensuremath{\mathsf{CSR.3}}, 4, 5$  should be cleared, if set, before further attempts are initiated.

#### NOTE:

If CSR.3 (VPPS) is set to '1', after clearing CSR.3/4/5,

- 1. Issue Reset WP command,

- Retry Erase All Unlocked Block Erase command to erase all blocks, or issue Single Block Erase to erase all of the unlocked blocks in sequence.

- 3. Set WP command is issued, if necessary.

If CSR.3 (VPPS) is set to '0', after clearing CSR.3/4/5,

1. Retry Erase All Unlocked Block Erase command.

Figure 10. Bank Erase All Unlocked Blocks with Compatible Status Registers

Figure 11. Set Write Protect

Figure 12. Reset Write Protect

# **ELECTRICAL SPECIFICATIONS**

# **Absolute Maximum Ratings\***

Temperature under bias .....-20°C to +80°C Storage temperature ....-65°C to +125°C \*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

| SYMBOL           | PARAMETER                                                            | MIN. | MAX.                  | UNITS | TEST CONDITIONS     | NOTE |

|------------------|----------------------------------------------------------------------|------|-----------------------|-------|---------------------|------|

| T <sub>A</sub>   | Operating Temperature, Commercial                                    | 0    | 70.0                  | °C    | Ambient Temperature | 1    |

| V <sub>CC</sub>  | V <sub>CC</sub> with Respect to GND                                  | -0.2 | 7.0                   | ٧     |                     | 2    |

| V <sub>PP</sub>  | V <sub>PP</sub> Supply Voltage with Respect to GND                   | -0.2 | 7.0                   | ٧     |                     | 2    |

| V                | Voltage on any Pin (Except $V_{CC}$ , $V_{PP}$ ) with Respect to GND | -0.5 | V <sub>CC</sub> + 0.5 | V     |                     | 2    |

| I                | Current into any Non-Supply Pin                                      |      | ±30                   | mA    |                     |      |

| I <sub>OUT</sub> | Output Short Circuit Current                                         |      | 100.0                 | mA    |                     | 3    |

### NOTES:

- 1. Operating temperature is for commercial product defined by this specification.

- 2. Minimum DC voltage is -0.5 V on input/output pins. During transitions, this level may undershoot to -2.0 V for periods < 20 ns. Maximum DC voltage on input/output pins is  $V_{CC}$  + 0.5 V which, during transitions, may overshoot to  $V_{CC}$  + 2.0 V for periods < 20 ns.

- 3. Output shorted for no more than one second. No more than one output shorted at a time.

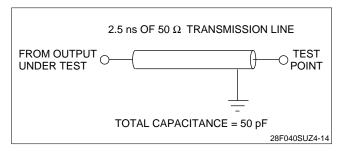

# **Capacitance**

| SYMBOL            | PARAMETER                                                    | TYP. | MAX. | UNITS | TEST CONDITIONS                     | NOTE |

|-------------------|--------------------------------------------------------------|------|------|-------|-------------------------------------|------|

| C <sub>IN</sub>   | Capacitance Looking into an Address/Control Pin              | 14   | 20   | pF    | T <sub>A</sub> = 25°C, f = 1.0 MHz  | 1, 2 |

| C <sub>OUT</sub>  | Capacitance Looking into an Output Pin                       | 18   | 24   | pF    | T <sub>A</sub> = 25°C, f = 1.0 MHz  | 1    |

| C <sub>LOAD</sub> | Load Capacitance Driven by Outputs for Timing Specifications |      | 50   | pF    | For V <sub>CC</sub> = 3.3 V ±0.3 V  | 1    |

|                   | Equivalent Testing Load Circuit V <sub>CC</sub> ± 10%        |      | 2.5  | ns    | 50 $\Omega$ transmission line delay |      |

#### NOTE

- 1. Sampled, not 100% tested.

- 2.  $\overline{BE}_0$  and  $\overline{BE}_1$  have half the value of this.

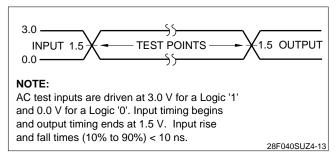

# **Timing Nomenclature**

For 3.3 V systems use 1.5 V cross point definitions.

Each timing parameter consists of 5 characters. Some common examples are defined below:

$t_{CE}$   $t_{ELQV}$  time (t) from  $\overline{BE}$  (E) going low (L) to the outputs (Q) becoming valid (V)

$t_{OE}$   $t_{GLQV}$  time (t) from  $\overline{OE}$  (G) going low (L) to the outputs (Q) becoming valid (V)

$t_{ACC}$   $t_{AVQV}$  time (t) from address (A) valid (V) to the outputs (Q) becoming valid (V)

$t_{AS}$   $t_{AVWH}$  time (t) from address (A) valid (V) to  $\overline{WE}$  (W) going high (H)

$t_{DH}$   $t_{WHDX}$  time (t) from  $\overline{WE}$  (W) going high (H) to when the data (D) can become undefined (X)

|     | PIN CHARACTERS                |   | PIN STATES                        |

|-----|-------------------------------|---|-----------------------------------|

| Α   | Address Inputs                | Н | High                              |

| D   | Data Inputs                   | L | Low                               |

| Q   | Data Outputs                  | V | Valid                             |

| Е   | BE (Byte Enable) <sup>1</sup> | Х | Driven, but not necessarily valid |

| G   | OE (Output Enable)            | Z | High Impedance                    |

| W   | WE (Write Enable)             |   |                                   |

| V   | Any Voltage Level             |   |                                   |

| 3 V | V <sub>CC</sub> at 3.0 V Min. |   |                                   |

## NOTE:

1.  $\overline{BE}_X$  means either  $\overline{BE}_0$  or  $\overline{BE}_1$ .

Figure 13. Transient Input/Output Reference Waveform (V<sub>CC</sub> = 3.3 V)

Figure 14. Transient Equivalent Testing Load Circuit (V<sub>CC</sub> = 3.3 V)

# **DC Characteristics**

$V_{CC} = 3.3 \, V \pm 0.3 \, V$ ,  $T_A = -20 \, ^{\circ}C$  to  $+70 \, ^{\circ}C$

Following is the current consumption of one bank. For the current consumption of one device total, please refer to Note 5.

| SYMBOL                        | PARAMETER                                          | TYP. | MIN. | MAX. | UNITS | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                              | NOTE          |

|-------------------------------|----------------------------------------------------|------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| I <sub>IL</sub>               | Input Load Current                                 |      |      | ±2   | μA    | $V_{CC} = V_{CC} MAX., V_{IN} = V_{CC} or GND$                                                                                                                                                                                                                                                                                                                                                                                                               | 1             |

| I <sub>LO</sub>               | Output Leakage<br>Current                          |      |      | ±20  | μΑ    | $V_{CC} = V_{CC}$ MAX., $V_{IN} = V_{CC}$ or GND                                                                                                                                                                                                                                                                                                                                                                                                             | 1             |

|                               | V <sub>CC</sub> Standby Current                    | 5    |      | 10   | μA    | $\frac{V_{CC} = V_{CC} \text{ MAX.,}}{\overline{BE}_0, \overline{BE}_1 = V_{CC} \pm 0.2 \text{ V}}$                                                                                                                                                                                                                                                                                                                                                          | 1, 4, 5       |

| Iccs                          | V <sub>CC</sub> Standby Gunerit                    | 0.3  |      | 4    | mA    | $\frac{V_{CC}}{\overline{BE}_0} = V_{CC} \text{ MAX.},$ $\overline{BE}_0 = V_{IH}$                                                                                                                                                                                                                                                                                                                                                                           | 1, 4, 3       |

| I <sub>CCR</sub> 1            | V <sub>CC</sub> Read Current<br>(10 MHz Operation) |      |      | 35   | mA    | $\begin{split} & V_{CC} = V_{CC} \text{ MAX.}, \\ & \text{CMOS: } \overline{\text{BE}}_0, \overline{\text{BE}}_1 = \text{GND } \pm 0.2 \text{ V} \\ & \text{Inputs} = \text{GND } \pm 0.2 \text{ V or } V_{CC} \pm 0.2 \text{ V}, \\ & \text{TTL: } \overline{\text{BE}}_0, \overline{\text{BE}}_1 = V_{\text{IL},} \\ & \text{Inputs} = V_{\text{IL}} \text{ or } V_{\text{IH}}, \\ & \text{f} = 10 \text{ MHz}, I_{\text{OUT}} = 0 \text{ mA} \end{split}$ | 1, 3,<br>4, 5 |

| I <sub>CCR</sub> <sup>2</sup> | V <sub>CC</sub> Read Current<br>(5 MHz Operation)  | 10   |      | 20   | mA    | $\begin{split} & V_{CC} = V_{CC} \text{ MAX.}, \\ & \text{CMOS: } \overline{\text{BE}}_0, \overline{\text{BE}}_1 = \text{GND } \pm 0.2 \text{ V} \\ & \text{Inputs} = \text{GND } \pm 0.2 \text{ V or } V_{CC} \pm 0.2 \text{ V}, \\ & \text{TTL: } \overline{\text{BE}}_0, \overline{\text{BE}}_1 = V_{\text{IL},} \\ & \text{Inputs} = V_{\text{IL}} \text{ or } V_{\text{IH}}, \\ & \text{f = 5 MHz, } I_{\text{OUT}} = 0 \text{ mA} \end{split}$         | 1, 3,<br>4, 5 |

| I <sub>CCW</sub>              | V <sub>CC</sub> Write Current                      | 8    |      | 12   | mA    | Byte/Two-Byte Serial Write in Progress                                                                                                                                                                                                                                                                                                                                                                                                                       | 1, 5          |

| I <sub>CCE</sub>              | V <sub>CC</sub> Block Erase<br>Current             | 6    |      | 12   | mA    | Block Erase in Progress                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1, 5          |

| I <sub>CCES</sub>             | V <sub>CC</sub> Erase Suspend<br>Current           | 3    |      | 6    | mA    | $\overline{BE}_0$ , $\overline{BE}_1 = V_{IH}$ Block Erase Suspended                                                                                                                                                                                                                                                                                                                                                                                         | 1, 2, 5       |

| I <sub>PPS</sub>              | V <sub>PP</sub> Standby Current                    | ±1   |      | ±10  | μΑ    | $V_{PP} \leq V_{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1, 5          |

# **DC Characteristics (Continued)**

$V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, T_A = -20 ^{\circ}\text{C} \text{ to } +70 ^{\circ}\text{C}$

| SYMBOL                       | PARAMETER                                        | TYPE | MIN.                  | MAX.                  | UNITS    | TEST CONDITIONS                                                | NOTE |

|------------------------------|--------------------------------------------------|------|-----------------------|-----------------------|----------|----------------------------------------------------------------|------|

| I <sub>PPR</sub>             | V <sub>PP</sub> Read Current                     | 65   |                       | 200                   | μA       | $V_{PP} > V_{CC}$                                              | 1, 5 |

| I <sub>PPW</sub>             | V <sub>PP</sub> Write Current                    | 15   |                       | 35                    | mA       | $V_{PP} = V_{PPH}$ , Byte/Two-Byte<br>Serial Write in Progress | 1, 5 |

| I <sub>PPE</sub>             | V <sub>PP</sub> Erase Current                    | 20   |                       | 40                    | mA       | $V_{PP} = V_{PPH}$ ,<br>Block Erase in Progress                | 1, 5 |

| I <sub>PPES</sub>            | V <sub>PP</sub> Erase Suspend<br>Current         | 65   |                       | 200                   | μΑ       | $V_{PP} = V_{PPH}$ ,<br>Block Erase Suspended                  | 1, 5 |

| V <sub>IL</sub>              | Input Low Voltage                                |      | -0.3                  | 0.8                   | ٧        |                                                                |      |

| V <sub>IH</sub>              | Input High Voltage                               |      | 2.0                   | V <sub>CC</sub> + 0.3 | V        |                                                                |      |

| V <sub>OL</sub>              | Output Low Voltage                               |      |                       | 0.4                   | ٧        | $V_{CC} = V_{CC}$ MIN. and $I_{OL} = 4$ mA                     |      |

| V <sub>OH</sub> <sup>1</sup> | Output High Voltage                              |      | 2.4                   |                       | <b>V</b> | $I_{OH}$ = -2 mA<br>$V_{CC}$ = $V_{CC}$ MIN.                   |      |

| V <sub>OH</sub> <sup>2</sup> | Output High Voltage                              |      | V <sub>CC</sub> - 0.2 |                       | >        | $I_{OH}$ = 100 $\mu$ A<br>$V_{CC}$ = $V_{CC}$ MIN.             |      |

| V <sub>PPL</sub>             | V <sub>PP</sub> during Normal<br>Operations      |      | 0.0                   | 5.5                   | <b>V</b> |                                                                |      |

| V <sub>PPH</sub>             | V <sub>PP</sub> during Write/Erase<br>Operations | 5.0  | 4.5                   | 5.5                   | V        |                                                                |      |

| V <sub>LKO</sub>             | V <sub>CC</sub> Erase/Write<br>Lock Voltage      |      | 1.4                   |                       | V        |                                                                |      |

- 1. All currents are in RMS unless otherwise noted. Typical values at  $V_{CC} = 3.3 \text{ V}$ ,  $V_{PP} = 5.0 \text{ V}$ ,  $T = 25^{\circ}\text{C}$ .

2.  $I_{CCES}$  is specified with the device de-selected. If the device is read while in erase suspend mode, current draw is the sum of I<sub>CCES</sub> and I<sub>CCR</sub>.

- Automatic Power Saving (APS) reduces I<sub>CCR</sub> to less than 2 mA in Static operation.

CMOS inputs are either V<sub>CC</sub> ± 0.2 V or GND ± 0.2 V. TTL Inputs are either V<sub>IL</sub> or V<sub>IH</sub>.

These are the values of the current which is consumed within one bank area. The value for the bank0 and bank1 should be added in order to calculate the value for the whole chip. If the bank0 is in write state and bank1 is in read state, the  $I_{CC} = I_{CCW} + I_{CCR}$ . If both banks are in standby mode, the value for the device is 2 times the value in the above table.

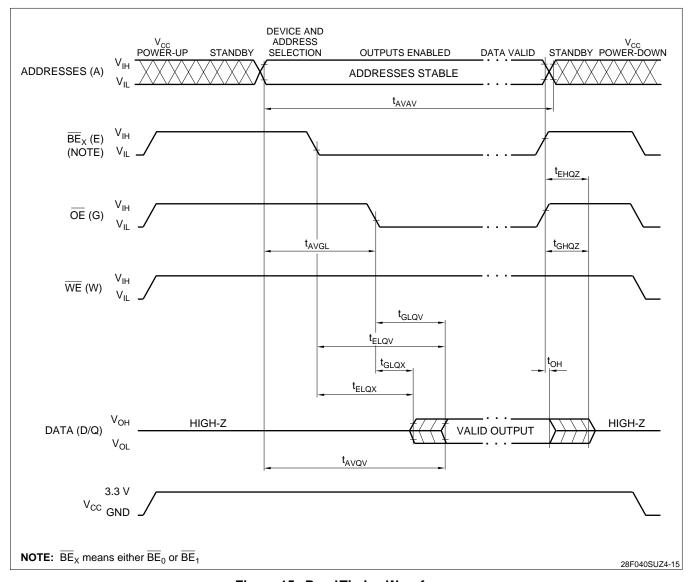

# AC Characteristics - Read Only Operations<sup>1</sup>

$V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, T_A = -20 ^{\circ}\text{C} \text{ to } +70 ^{\circ}\text{C}$

| SYMBOL            | PARAMETER                                                                                                         | MIN. | MAX. | UNITS | NOTE |

|-------------------|-------------------------------------------------------------------------------------------------------------------|------|------|-------|------|

| t <sub>AVAV</sub> | Read Cycle Time                                                                                                   | 150  |      | ns    |      |

| t <sub>AVGL</sub> | Address Setup to OE Going Low                                                                                     | 0    |      | ns    | 3    |

| t <sub>AVQV</sub> | Address to Output Delay                                                                                           |      | 150  | ns    |      |

| t <sub>ELQV</sub> | $\overline{\rm BE}_0$ , $\overline{\rm BE}_1$ to Output Delay                                                     |      | 150  | ns    | 2    |

| t <sub>GLQV</sub> | OE to Output Delay                                                                                                |      | 50   | ns    | 2    |

| t <sub>ELQX</sub> | $\overline{\rm BE}_0$ , $\overline{\rm BE}_1$ to Output in Low Z                                                  | 0    |      | ns    | 3    |

| t <sub>EHQZ</sub> | $\overline{\rm BE}_0$ , $\overline{\rm BE}_1$ to Output in High Z                                                 |      | 55   | ns    | 3    |

| t <sub>GLQX</sub> | OE to Output in Low Z                                                                                             | 0    |      | ns    | 3    |

| t <sub>GHQZ</sub> | OE to Output in High Z                                                                                            |      | 40   | ns    | 3    |

| t <sub>OH</sub>   | Output Hold from Address, $\overline{BE}_0$ , $\overline{BE}_1$ or $\overline{OE}$ change, whichever occurs first | 0    |      | ns    | 3    |

# AC Characteristics - Read Only Operations<sup>1</sup> (Continuted)

$V_{CC} = 2.85 \text{ V} \pm 0.15 \text{ V}, T_A = -20 ^{\circ}\text{C} \text{ to } +70 ^{\circ}\text{C}$

| SYMBOL            | PARAMETER                                                                                                         | MIN. | MAX. | UNITS | NOTE |

|-------------------|-------------------------------------------------------------------------------------------------------------------|------|------|-------|------|

| t <sub>AVAV</sub> | Read Cycle Time                                                                                                   | 190  |      | ns    |      |

| t <sub>AVGL</sub> | Address Setup to OE Going Low                                                                                     | 0    |      | ns    | 3    |

| t <sub>AVQV</sub> | Address to Output Delay                                                                                           |      | 190  | ns    |      |

| t <sub>ELQV</sub> | $\overline{\rm BE}_0$ , $\overline{\rm BE}_1$ to Output Delay                                                     |      | 190  | ns    | 2    |

| t <sub>GLQV</sub> | OE to Output Delay                                                                                                |      | 65   | ns    | 2    |

| t <sub>ELQX</sub> | $\overline{\rm BE}_0$ , $\overline{\rm BE}_1$ to Output in Low Z                                                  | 0    |      | ns    | 3    |

| t <sub>EHQZ</sub> | $\overline{\rm BE}_0$ , $\overline{\rm BE}_1$ to Output in High Z                                                 |      | 70   | ns    | 3    |

| t <sub>GLQX</sub> | OE to Output in Low Z                                                                                             | 0    |      | ns    | 3    |

| t <sub>GHQZ</sub> | OE to Output in High Z                                                                                            | _    | 55   | ns    | 3    |

| t <sub>OH</sub>   | Output Hold from Address, $\overline{BE}_0$ , $\overline{BE}_1$ or $\overline{OE}$ change, whichever occurs first | 0    |      | ns    | 3    |

- 1. See AC Input/Output Reference Waveforms for timing measurements, Figure 4.

- OE may be delayed up to t<sub>ELQV</sub> t<sub>GLQV</sub> after the falling edge of BE<sub>0</sub>, BE<sub>1</sub> without impact on t<sub>ELQV</sub>.

Sampled, not 100% tested.

Figure 15. Read Timing Waveforms

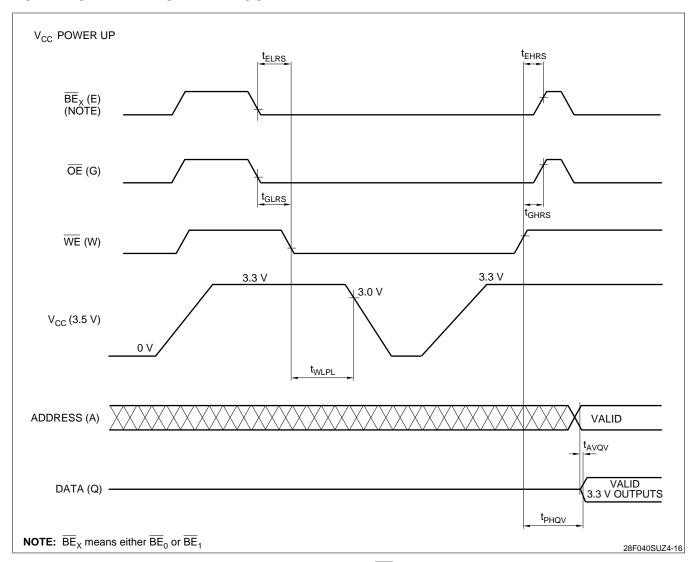

## POWER-UP AND RESETTIMINGS

Figure 16.  $V_{CC}$  Power-Up and  $\overline{RP}$  Reset Waveforms

| SYMBOL            | PARAMETER                                                                                               | MIN. | MAX. | UNITS | NOTE |

|-------------------|---------------------------------------------------------------------------------------------------------|------|------|-------|------|

| t <sub>WLPL</sub> | WE Low to V <sub>CC</sub> at 3.0 V MIN.                                                                 | 5    |      | μs    | 1    |

| t <sub>AVQV</sub> | Address Valid to Data Valid for $V_{CC}$ = 3.3 V $\pm$ 0.3 V                                            |      | 150  | ns    | 2    |

| t <sub>PHQV</sub> | $\overline{\text{WE}}$ High to Data Valid for $V_{\text{CC}}$ = 3.3 V ± 0.3 V                           |      | 500  | ns    | 2    |

| t <sub>ELRS</sub> | $\overline{\mathrm{BE}}_0$ and $\overline{\mathrm{BE}}_1$ Setup to WE Going Low                         | 100  |      | ns    |      |

| t <sub>GLRS</sub> | OE Setup to WE Going Low                                                                                | 100  |      | ns    |      |

| t <sub>EHRS</sub> | $\overline{\mathrm{BE}}_0$ and $\overline{\mathrm{BE}}_1$ Hold from $\overline{\mathrm{WE}}$ Going High | 100  |      | ns    |      |

| t <sub>GHRS</sub> | OE Hold from WE Going High                                                                              | 100  |      | ns    |      |

- BE <sub>0</sub>, BE <sub>1</sub> and OE must be set high once after power-up. BE <sub>0</sub> and BE <sub>1</sub> must not be set low at the same time.

1. Chip reset is enabled when the low state of all BE <sub>0</sub> (or BE <sub>1</sub>), OE and WE exceeds 5 μs. Especially when you will power on the chip, execute an above chip reset sequence for a protection from noise. All  $\overline{BE}_0$  (or  $\overline{BE}_1$ ),  $\overline{OE}$  and  $\overline{WE}$ must not be low, except for the purpose of chip reset.

- 2. These values are shown for 3.3 V  $V_{CC}$  operation. Refer to the AC Characteristics Read Only Operations also.

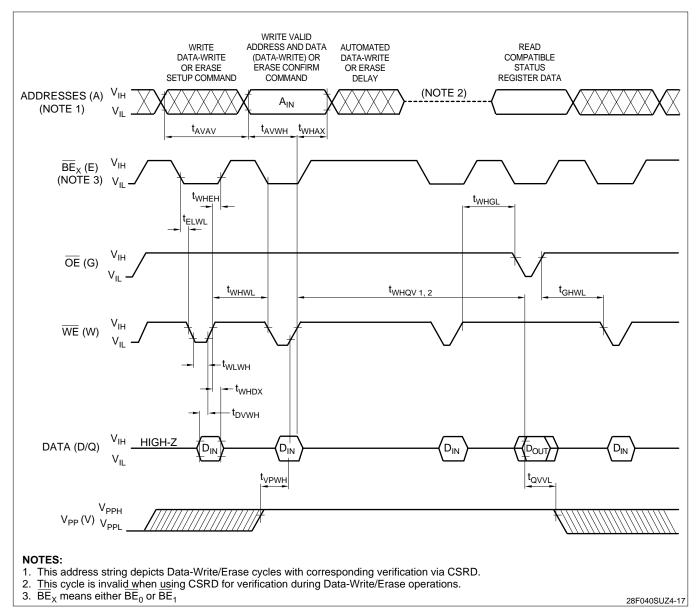

# AC Characteristics for WE - Controlled Command Write Operations<sup>1</sup>

$V_{CC} = 3.25 \text{ V} \pm 0.35 \text{ V}, T_A = -20 ^{\circ}\text{C} \text{ to } +70 ^{\circ}\text{C}$

| SYMBOL                         | PARAMETER                                                                                  | TYP. | MIN. | MAX. | UNITS | NOTE    |

|--------------------------------|--------------------------------------------------------------------------------------------|------|------|------|-------|---------|

| t <sub>AVAV</sub>              | Write Cycle Time                                                                           |      | 150  |      | ns    |         |

| t <sub>VPWH</sub>              | V <sub>PP</sub> Set up to WE Going High                                                    |      | 100  |      | ns    | 3       |

| t <sub>ELWL</sub>              | $\overline{\rm BE}_{0}$ and $\overline{\rm BE}_{1}$ Setup to $\overline{\rm WE}$ Going Low |      | 0    |      | ns    |         |

| t <sub>AVWH</sub>              | Address Setup to WE Going High                                                             |      | 110  |      | ns    | 2, 6    |

| t <sub>DVWH</sub>              | Data Setup to WE Going High                                                                |      | 110  |      | ns    | 2, 6    |

| t <sub>WLWH</sub>              | WE Pulse Width                                                                             |      | 110  |      | ns    |         |

| t <sub>WHDX</sub>              | Data Hold from WE High                                                                     |      | 10   |      | ns    | 2       |

| t <sub>WHAX</sub>              | Address Hold from WE High                                                                  |      | 10   |      | ns    | 2       |

| t <sub>WHEH</sub>              | $\overline{\rm BE}_{0}$ and $\overline{\rm BE}_{1}$ Hold from $\overline{\rm WE}$ High     |      | 10   |      | ns    |         |

| t <sub>WHWL</sub>              | WE Pulse Width High                                                                        |      | 75   |      | ns    |         |

| t <sub>GHWL</sub>              | Read Recovery before Write                                                                 |      | 0    |      | ns    |         |

| t <sub>WHGL</sub>              | Write Recovery before Read                                                                 |      | 120  |      | ns    |         |

| t <sub>QVVL</sub>              | V <sub>PP</sub> Hold from Valid Status Register Data                                       |      | 0    |      | μs    |         |

| t <sub>WHQV</sub> 1            | Duration of Byte Write Operation                                                           | 20   | 8    | 250  | μs    | 4, 5, 7 |

| t <sub>WHQV</sub> <sup>2</sup> | Duration of Block Erase Operation                                                          |      | 0.3  |      | S     | 4       |

### NOTES:

- 1. Read timing during write and erase are the same as for normal read.

- 2. Refer to command definition tables for valid address and data values.

- 3. Sampled, but not 100% tested.

- 4. Write/Erase durations are measured to valid Status Register (CSR) Data.

- 5. Byte write operations are typically performed with 1 Programming Pulse.

- 6. Address and Data are latched on the rising edge of  $\overline{\text{WE}}$  for all Command Write operations.

- The maximum value of byte write time is the maximum write time inside the chip. It is not the time until the whole

writing procedure is completed properly. It is necessary to check CSR to see if the writing procedure is properly

completed.

Figure 17. Waveforms for Command Write Operations

27

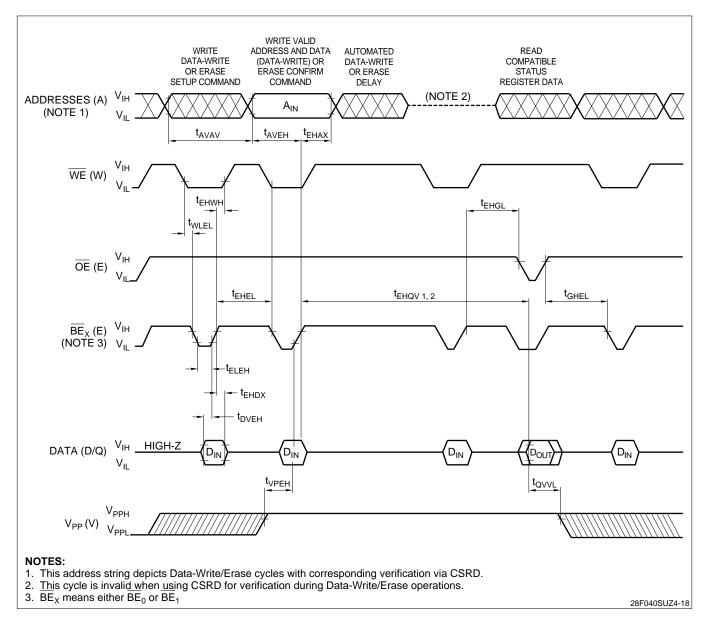

# AC Characteristics for $\overline{\mbox{BE}}$ - Controlled Command Write Operations $^2$

$V_{CC} = 3.25 V \pm 0.35 V$ ,  $T_A = -20 ^{\circ}C$  to  $+70 ^{\circ}C$

| SYMBOL              | PARAMETER                                                                                      | TYP. | MIN. | MAX. | UNITS | NOTE    |

|---------------------|------------------------------------------------------------------------------------------------|------|------|------|-------|---------|

| t <sub>AVAV</sub>   | Write Cycle Time                                                                               |      | 150  |      | ns    |         |

| t <sub>VPEH</sub>   | $V_{PP}$ Set up to $\overline{BE}_0$ or $\overline{BE}_1$ Going High                           |      | 100  |      | ns    | 3       |

| t <sub>WLEL</sub>   | $\overline{\text{WE}}$ Setup to $\overline{\text{BE}}_0$ or $\overline{\text{BE}}_1$ Going Low |      | 0    |      | ns    |         |

| t <sub>AVEH</sub>   | Address Setup to $\overline{\rm BE}_0$ or $\overline{\rm BE}_1$ Going High                     |      | 110  |      | ns    | 2, 6    |

| t <sub>DVEH</sub>   | Data Setup to $\overline{BE}_0$ or $\overline{BE}_1$ Going High                                |      | 110  |      | ns    | 2, 6    |

| t <sub>ELEH</sub>   | $\overline{\rm BE}_{0}$ or $\overline{\rm BE}_{1}$ Pulse Width                                 |      | 110  |      | ns    |         |

| t <sub>EHDX</sub>   | Data Hold from $\overline{\rm BE}_0$ or $\overline{\rm BE}_1$ High                             |      | 10   |      | ns    | 2       |

| t <sub>EHAX</sub>   | Address Hold from $\overline{\rm BE}_0$ or $\overline{\rm BE}_1$ High                          |      | 10   |      | ns    | 2       |

| t <sub>EHWH</sub>   | $\overline{\text{WE}}$ Hold from $\overline{\text{BE}}_0$ or $\overline{\text{BE}}_1$ High     |      | 10   |      | ns    |         |

| t <sub>EHEL</sub>   | $\overline{\rm BE}_{0}$ or $\overline{\rm BE}_{1}$ Pulse Width High                            |      | 75   |      | ns    |         |

| t <sub>GHEL</sub>   | Read Recovery before Write                                                                     |      | 0    |      | ns    |         |

| t <sub>EHGL</sub>   | Write Recovery before Read                                                                     |      | 120  |      | ns    |         |

| t <sub>QVVL</sub>   | V <sub>PP</sub> Hold from Valid Status Register Data                                           |      | 0    |      | μs    |         |

| t <sub>EHQV</sub> 1 | Duration of Byte Write Operation                                                               | 20   | 8    | 250  | μs    | 4, 5, 7 |

| t <sub>EHQV</sub> 2 | Duration of Block Erase Operation                                                              |      | 0.3  |      | S     | 4       |

#### NOTES:

- 1. Read timing during write and erase are the same as for normal read.

- 2. Refer to command definition tables for valid address and data values.

- 3. Sampled, but not 100% tested.

- 4. Write/Erase durations are measured to valid Status Register (CSR) Data.

- 5. Byte Write operations are typically performed with 1 Programming Pulse.

- 6. Address and Data are latched on the rising edge of  $\overline{BE}_0$  or  $\overline{BE}_1$  for all Command Write operations.

- 7. The MAX. value of byte write time is the maximum wrtie time inside the chip. It is not the time until the whole writing procedure is completed properly. It is necessary to check CSR to see if the writing procedure is properly completed.

Figure 18. Alternate AC Waveforms for Command Write Operations

29

# **Erase and Byte Write Performance**

$V_{CC} = 3.25 \text{ V} \pm 0.35 \text{ V}, T_A = -20 ^{\circ}\text{C} \text{ to } +70 ^{\circ}\text{C}$

| SYMBOL                         | PARAMETER                  | TYP. <sup>(1)</sup> | MIN. | MAX. | UNITS | TEST CONDITIONS            | NOTE |

|--------------------------------|----------------------------|---------------------|------|------|-------|----------------------------|------|

| t <sub>WHRH</sub> 1            | Byte Write Time            | 20                  |      | 250  | μs    |                            | 2, 3 |

| t <sub>WHRH</sub> <sup>2</sup> | Two-Byte Serial Write Time | 34                  |      |      | μs    |                            | 2    |

| t <sub>WHRH</sub> 3            | 16KB Block Write Time      | 0.33                |      | 1.0  | S     | Byte Write Mode            | 2    |

| t <sub>WHRH</sub> 4            | 16KB Block Write Time      | 0.28                |      | 1.0  | S     | Two-Byte Serial Write Mode | 2    |

|                                | Block Erase Time (16KB)    | 0.8                 |      | 10   | s     |                            | 2    |

|                                | 2M Bit Bank Erase Time     | 9 - 15              |      |      | S     |                            | 2, 4 |

# NOTES:

- 1.  $25^{\circ}$ C,  $V_{PP} = 5.0 \text{ V}$

- 2. Excludes System-Level Overhead. It actually indicates the time from input write/erase command until bit7 of status register becomes ready (WSMS = 0).

- 3. The MAX. value of byte write time is the maximum write time inside the chip. It is not the time until the whole writing procedure is completed properly. It is necessary to check CSR to see if the writing procedure is properly completed.

- 4. Depends on the number of protected blocks.

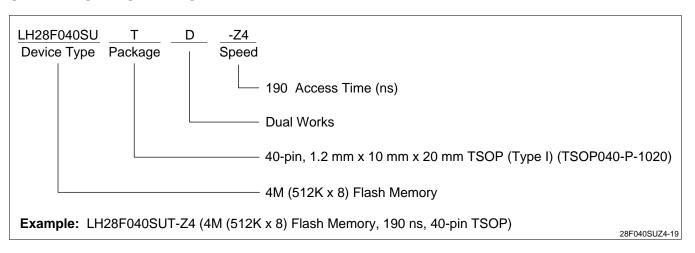

## ORDERING INFORMATION

#### LIFE SUPPORT POLICY

SHARP components should not be used in medical devices with life support functions or in safety equipment (or similiar applications where component failure would result in loss of life or physical harm) without the written approval of an officer of the SHARP Corporation.

# WARRANTY

SHARP warrants to Customer that the Products will be free from defects in material and workmanship under normal use and service for a period of one year from the date of invoice. Customer's exclusive remedy for breach of this warranty is that SHARP will either (i) repair or replace, at its option, any Product which fails during the warranty period because of such defect (if Customer promptly reported the failure to SHARP in writing) or, (ii) if SHARP is unable to repair or replace, SHARP will refund the purchase price of the Product upon its return to SHARP. This warranty does not apply to any Product which has been subjected to misuse, abnormal service or handling, or which has been altered or modified in design or construction, or which has been serviced or repaired by anyone other than SHARP. The warranties set forth herein are in lieu of, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE ARE SPECIFICALLY EXCLUDED.

SHARP reserves the right to make changes in specifications at any time and without notice. SHARP does not assume any responsibility for the use of any circuitry described; no circuit patent licenses are implied.

# SHARP

#### **NORTH AMERICA**

SHARP Electronics Corporation Microelectronics Group 5700 NW Pacific Rim Blvd., M/S 20 Camas, WA 98607, U.S.A. Phone: (360) 834-2500 Telex: 49608472 (SHARPCAM)

Facsimile: (360) 834-8903 http://www.sharpmeg.com

#### **EUROPE**

SHARP Electronics (Europe) GmbH Microelectronics Division Sonninstraße 3 20097 Hamburg, Germany Phone: (49) 40 2376-2286 Telex: 2161867 (HEEG D)

Facsimile: (49) 40 2376-2232

# ASIA

SHARP Corporation Integrated Circuits Group 2613-1 Ichinomoto-Cho Tenri-City, Nara, 632, Japan Phone: (07436) 5-1321 Telex: LABOMETA-B J63428 Facsimile: (07436) 5-1532

©1997 by SHARP Corporation Issued July 1996