# Overview

The LC85632 is a multi-function digital clock IC that in addition to providing current time display supports a wide range of functions, including an alarm function, a sleep function, a calendar function, and a function to turn connected equipment on and off. Furthermore, the LC85632 provides a simpler user interface than that of earlier Sanyo products.

# **Applications**

- · Alarm clocks

- · Clock radios

## **Functions**

- · Current time display

- Two independent alarm functions with snooze function

- Sleep timer function (up to 90 minutes)

- Calendar function

One year calendar (January 1 to December 31)

that can display leap year's day (February 29).

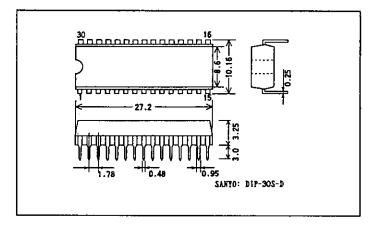

# **Package Dimensions**

unit: mm

DIP-30S-D

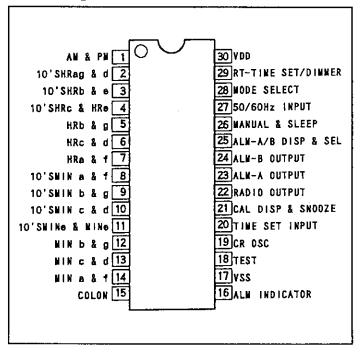

# Pin Assignment

# **Pin Functions**

| No. | Pin             | 1/0   | Internal equivalent circuit | Pin function                                                                                                                                                                                                                                                                                                                                                          | Handling when unused |

|-----|-----------------|-------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1   | AM & PM         | 0     |                             | LED output pins                                                                                                                                                                                                                                                                                                                                                       | Open                 |

| 2   | 10'SHRag & d    | ا ہ ا |                             | No. Pin Drive phase 1 Drive phase 2                                                                                                                                                                                                                                                                                                                                   | ,                    |

| 3   | 10'SHRb & e     | اما   | ∱ VDD                       | 1 AM & PM AM PM                                                                                                                                                                                                                                                                                                                                                       |                      |

|     |                 | -     | ן עטי                       | 2 10'SHR ag & d 10'SHR ad 10'SHR g                                                                                                                                                                                                                                                                                                                                    |                      |

| 4   | 10'SHRc & HRe   | ^     |                             | 3 10'SHRb & e 10'SHR e 10'SHR b                                                                                                                                                                                                                                                                                                                                       |                      |

| 5   | HRb & g         | 0     |                             | 4 10'SHRc & HRe HR e 10'SHR c                                                                                                                                                                                                                                                                                                                                         |                      |

| 6   | HRc & d         | 0     |                             | 5 HRb&g HRg HRb                                                                                                                                                                                                                                                                                                                                                       |                      |

| 7   | HRa & f         | l٥l   |                             | 6 HRc&d HRd HRc                                                                                                                                                                                                                                                                                                                                                       |                      |

| 8   | 10'SMIN a & f   | ا ہ ا | <u> </u>                    | 7 HRa&f HRf HRa                                                                                                                                                                                                                                                                                                                                                       |                      |

| 9   |                 | -     |                             | 8 10'SMIN a & f 10'SMIN a 10'SMIN f                                                                                                                                                                                                                                                                                                                                   |                      |

|     | 10'SMIN b & g   |       |                             | 9 10'SMIN b & g 10'SMIN b 10'SMIN g                                                                                                                                                                                                                                                                                                                                   |                      |

| 10  | 10'SMIN c & d   | 0     |                             | 10 10'SMIN c & d 10'SMIN c 10'SMIN d                                                                                                                                                                                                                                                                                                                                  |                      |

| 11  | 10'SMINe & MINe |       |                             | 11 10'SMINe & MINe MINe 10'SMINe                                                                                                                                                                                                                                                                                                                                      |                      |

| 12  | MIN b & g       | 0     |                             | 12 MIN b & g MIN b                                                                                                                                                                                                                                                                                                                                                    |                      |

| 13  | MIN c & d       | ا ہ ا |                             | 13 MIN c & d MIN d MIN c                                                                                                                                                                                                                                                                                                                                              |                      |

| 14  | MIN a & f       | اها   |                             | 14 MIN a & f MIN f MIN a<br>15 COLON COLON —                                                                                                                                                                                                                                                                                                                          | ,                    |

|     |                 | -     |                             | 16 ALM INDICATOR ALM-A ALM-B                                                                                                                                                                                                                                                                                                                                          |                      |

| 15  | COLON           | 0     |                             | TO ALMINDICATOR MALINIA ALIMIB                                                                                                                                                                                                                                                                                                                                        |                      |

| 16  | ALM INDICATOR   | 0     |                             | (VDD – 15 V breakdown voltage)                                                                                                                                                                                                                                                                                                                                        |                      |

| 22  | ALM-A OUTPUT    | 0     | VDD                         | Outputs a DC voltage. This pin is controlled by the inputs to the MANUAL & SLEEP pin (pin 26). It operates as a toggle. During normal operation it outputs a low level (high impedance).  MANUAL & SLEEP pin input level  VDD  OPEN  VSS  RADIO OUT pin output level (when pulled down to VSS)  VDD  VSS  (Normal breakdown voltage)                                  | Open                 |

| 24  | ALM-B OUTPUT    | 0     | VDD                         | Output alarm signals  ALM-A OUTPUT: Alarm A  ALM-B OUTPUT: Alarm B  The output waveform is shown below.  During normal operation these pins output a low level (high impedance).  ALM-A OUTPUT and ALM-B OUTPUT pin output levels (summary diagram)  * ALM-A OUTPUT (2400 Hz)  VDD  VSS  * ALM-B OUTPUT (1200 Hz)  VDD  VSS  Output start  (Normal breakdown voltage) | Open                 |

Continued on next page.

# Continued from preceding page.

| No. | Pin                | 1/0 | Internal equivalent<br>circuit                       | Pin function                                                                                                                                                                                                                                                                                                                                                                                         | Handling when unused |

|-----|--------------------|-----|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 20  | TIME SET INPUT     | 31  | WDD  H: High threshold input  L: Low threshold input | Input pin that starts the setting/update of the current time, the alarm time, or the calendar date. Normally left open (NOP).  The application of a high level is taken as a + input, which increases the value of the setting, and a low is taken as a - input, which decreases the value of the setting.                                                                                           | Open                 |

| 21  | CAL DISP & SNOOZE  | 31  | VDD  H: High threshold input                         | Input pin for calendar display and snooze.  Normally left open. When a high level is applied the calendar displays the day and month, and when a low level is applied the calendar displays the month and day.  However, if an alarm signal is being output from either ALM-A OUTPUT or ALM-B OUTPUT (pin 23 or 24) the calendar is not displayed, but rather a snooze operation is started.         | Open                 |

| 25  | ALM-A/B DISP & SEL | 31  | │ │ │ │ L: Lōw threshold □ input                     | Input pin for switching between alarm mode and current time mode. Normally left open. When a high level is applied, the current time setting for alarm A is displayed, and when a low level is applied, the current time setting for alarm B is displayed. In either case, the time setting and the operation enable/disable state can be changed.                                                   | Open                 |

| 26  | MANUAL & SLEEP     | 31  |                                                      | Input pin for setting the RADIO OUTPUT pin (pin 22) output control and the sleep function time. Normally left open. When a high level is applied the RADIO OUTPUT goes high. This pin can also be used for setting the sleep function time. When a low level is applied the RADIO OUTPUT goes low. When either a low level or a high level is applied, any alarm output in progress will be stopped. | Open                 |

Continued on next page.

## Continued from preceding page.

| No. | Pin                   | 1/0 | Internal equivalent<br>circuit                 | Pin function                                                                                                                                                                                                                                                     | Handling when unused                                        |

|-----|-----------------------|-----|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 28  | MODE SELECT           | 31  | VDD H                                          | Input pin for switching the operating mode. Switches the display mode and the clock input to the 50/60 Hz INPUT pin (pin 27). High: 50 Hz/24 hour display Open: 60 Hz/12 hour display Low: 50 Hz/12 hour display                                                 | Either left open, connected to VDD, or connected to ground. |

| 29  | RT-TIME<br>SET/DIMMER | 31  | H: High threshold input L: Low threshold input | Input pin for switching the enabled/disabled state for setting the time.  Normally left open.  High: Current time display/current time setting mode  Open: Current time display/current time setting disabled  Low: Dimmed display/current time setting disabled | Open                                                        |

| 19  | CR OSC                | 1/0 | External RC. constant about                    | Connection pin for external RC circuit. An oscillator circuit with a frequency of 4800 Hz can be formed using the following R and C values. $R=68~k\Omega$ $C=4700~pF$                                                                                           | Connected to VDD                                            |

| 17  | VSS                   | 1   | <del>-</del>                                   | Power supply pins.                                                                                                                                                                                                                                               | _                                                           |

| 30  | VDD                   | 1   | :                                              | VSS = 0 V<br>VDD = +5 V (standard)                                                                                                                                                                                                                               |                                                             |

| 18  | TEST                  | 31  | VDD  H. High threshold input                   | LSI test pin.<br>Normally left open.                                                                                                                                                                                                                             | Open                                                        |

| 27  | 50/60 Hz INPUT        | 1   |                                                | Input pin for the 50/60 Hz input for the clock. (Schmitt input)                                                                                                                                                                                                  |                                                             |

Note: • "31" is an abbreviation for "three value input pin." The inputs to these pins can be either high, open, or low. These pins are left open during normal use.

• NOP: "No operation"

# Three Value Input Circuits: H: High level, M: Open, L: Low level, NOP: No operation

# MODE SELECT

| înput level | Mode                  |

|-------------|-----------------------|

| Н           | 50 Hz/24 hour display |

| М           | 60 Hz/12 hour display |

| L           | 50 Hz/12 hour display |

# • TIME SET INPUT

| Input level | Mode |  |

|-------------|------|--|

| Н           | Up   |  |

| M           | NOP  |  |

| L           | Down |  |

# • RE-TIME SET/DIMMER

| Input level | Mode                                           |  |

|-------------|------------------------------------------------|--|

| н           | Current time display/current time setting mode |  |

| M           | Current time display/NOP                       |  |

| L           | Dimmed display/NOP                             |  |

# • CAL DISP & SNOOZE

| Input level | Mode                                                    |  |  |

|-------------|---------------------------------------------------------|--|--|

| Н           | Calendar display (day month)/calendar setting/snooze on |  |  |

| M           | Current time display/NOP                                |  |  |

| L           | Calendar display (month-day)/calendar setting/snooze on |  |  |

## • ALM-A/B DISP & SEL

| Input level | Mode                            |

|-------------|---------------------------------|

| Н           | Atarm A setting display/setting |

| М           | Current time display/NOP        |

| L           | Alarm B setting display/setting |

# • MANUAL & SLEEP

| Input level | Mode                     |

|-------------|--------------------------|

| Н           | ON input/sleep-in        |

| M           | Current time display/NOP |

| L           | OFF input                |

# • TEST

| Input level | Mode             |

|-------------|------------------|

| Н           | Illegal setting  |

| M           | Normal operation |

| Ļ           | LED test         |

# **Specifications**

# Absolute Maximum Ratings at Ta = 25°C, VSS = 0 V

| Parameter                      | Symbol  | Applicable pin                                             | Condition                                                                                                              | Rating                | Unit |

|--------------------------------|---------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------|------|

| Maximum power supply voltage   | VDDmax  |                                                            |                                                                                                                        | -0.3 to +7.0          | V    |

| Input voltage                  | VIN(1)  | All input pins other than the 50/60 Hz INPUT pin           |                                                                                                                        | -0.3 to VDD + 0.3     | V    |

|                                | VIN(2)  | 50/60 Hz INPUT                                             | Pin voltage                                                                                                            | -0.3 to VDD + 0.3     | 1    |

|                                |         |                                                            | With a 100 k $\Omega$ currentlimiting resistor inserted in the input, at that resistor's terminal.                     | VDD - 12 to VDD + 12  |      |

| Input clamping current         | liN     | 50/60 Hz INPUT                                             | With a 100 kΩ limiting resistor inserted in the input.                                                                 | -0.4 to +0.4          | mA   |

| Output voltage                 | VOUT(1) | CR OSC                                                     | 1                                                                                                                      | -0.3 to VDD + 0.3     | l v  |

| Output voltage                 | VOUT(2) | RADIO OUTPUT<br>ALM-A OUTPUT<br>ALM-B OUTPUT               |                                                                                                                        | -0.3 to VDD + 0.3     | V    |

| Output voltage                 | VOUT(3) | LED SEGMENT output pins (pins 1 to 16)                     |                                                                                                                        | VDD - 15 to VDD + 0.3 | V    |

| Total output current           | ΣILED   | Total for the LED<br>SEGMENT output pins<br>(pins 1 to 16) | The average value of the effective current value within a single display cycle according to the 50 or 60 Hz frequency. | -280 to 0             | mA   |

| Maximum power dissipation      | Pdmax   |                                                            | Ta = -30 to +70°C                                                                                                      | 700                   | mW   |

| Ambient temperature: operating | Topr    |                                                            |                                                                                                                        | -30 to +70            | °C   |

| Ambient temperature: storage   | Tstg    |                                                            |                                                                                                                        | -55 to +125           | °C   |

# Allowable Operating Ranges at $Ta = -30 \text{ to } +70^{\circ}\text{C}$ , VSS = 0 V

| Parameter                        | Symbol | Applicable sie                                      | On a distant                                               | Rating        |     |               |      |

|----------------------------------|--------|-----------------------------------------------------|------------------------------------------------------------|---------------|-----|---------------|------|

| raidilletei                      | Symbol | Applicable pin                                      | Condition                                                  | min           | typ | max           | Unit |

| Operating power supply voltage   | VDD    |                                                     |                                                            | 4.0           | 5.0 | 6.0           | v    |

| Input high level voltage         | VIH(1) | CR OSC                                              |                                                            | 0.75 VDD      |     | VDD           | V    |

| Input low level voltage          | VIL(1) |                                                     |                                                            | VSS           | *** | 0.25 VDD      | V    |

| Input high level voltage         | VIH(2) | TIME SET INPUT<br>CAL DISP & SNOOZE                 | The intermediate is the open pin state.                    | VDD - 0.5     |     | VDD           | ٧    |

| Input intermediate level voltage | VIM(2) | ALM-A/B DISP & SEL<br>MANUAL & SLEEP<br>MODE SELECT | The rated values apply when an external signal is applied. | 1/2 VDD - 0.5 |     | 1/2 VDD + 0.5 | V    |

| Input low level voltage          | VIL(2) | RT-TIME SET/DIMMER TEST                             | зарряец.                                                   | VSS           |     | VSS + 0.5     | ٧    |

| Input high level voltage         | VIH(3) | 50/60 Hz INPUT                                      |                                                            | VDD - 0.5     |     | VDD + 0.3     | v    |

| Input low level voltage          | VIL(3) |                                                     |                                                            | vss           |     | VDD - 3.0     | v    |

| Operating frequency              | fOP    | 50/60 Hz INPUT                                      |                                                            | 1             |     | 2000          | Hz   |

| Input level hold time            | tH     | All three value input pins                          |                                                            | 10            |     |               | msec |

| Input chattering time            | tC     | All three value input pins                          |                                                            | 10            |     | <u> </u>      | msec |

# Electrical Characteristics at $Ta = 25^{\circ}C$ , VDD = 5 V, VSS = 0 V

| Parameter                          | Symbol | Applicable pin                                                                                                                        | Condition                                                     | Rating   |      |                                       | Unit |

|------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------|------|---------------------------------------|------|

|                                    | ·      |                                                                                                                                       | Condition                                                     | min      | lyp  | max                                   | Onit |

| Output high level current          | IOH(1) | 10' SHRag & d                                                                                                                         | Output on,<br>VOUT = VDD - 2.0 V                              | (Note 1) |      | -32                                   | mA   |

| Output off leakage current         | (OF(1) |                                                                                                                                       | Output off,<br>VOUT = VDD ~ 12 V                              | -20      |      | · · · · · · · · · · · · · · · · · · · | μА   |

| Output high level current          | IOH(2) | AM & PM 10'SHRb & e 10'SHRc & HRe HRb & g HRc & d HRa & f 10'SMIN a & f 10'SMIN b & g 10'SMIN c & d 10'SMIN b & g MIN b & g MIN c & d | Output on,<br>VOUT = VDD - 2.0 V                              | (Note 2) |      | -16                                   | mA   |

| Output off leakage current         | IOF(2) | COLON<br>ALM INDICATOR                                                                                                                | Output off,<br>VOUT = VDD - 12 V                              | -20      |      |                                       | μÀ   |

| Output high level current          | IOH(3) | RADIO OUTPUT<br>ALM-A OUTPUT                                                                                                          | Output on,<br>VOUT = VDD - 2.0 V                              |          |      | -2                                    | mA   |

| Output off leakage current         | IOF(3) | ALM-B OUTPUT                                                                                                                          | Output off,<br>VOUT = VSS                                     | -10      |      |                                       | Ац   |

| Input high level current           | IIH(2) | CR OSC                                                                                                                                | VIN = VDD                                                     |          |      | 10                                    | μA   |

| Input low level current            | IIL(2) |                                                                                                                                       | VIN = VSS                                                     |          | -2   |                                       | mA   |

| Input high level current           | IIH(3) | TIME SET INPUT CAL DISP & SNOOZE ALM-A/B DISP & SEL                                                                                   | VIN = VDD                                                     | 10       |      | 100                                   | μА   |

| Input low level current            | IIL(3) | MANUAL & SLEEP MODE SELECT RT-TIME SET/DIMMER TEST                                                                                    | VIN = VSS                                                     | 100      |      | -10                                   | μΑ   |

| Pull-up resistance                 | RPU    | TIME SET INPUT<br>CAL DISP & SNOOZE<br>ALM-A/B DISP & SEL                                                                             | VIN = 1/2 VDD                                                 |          | 1.0  | <del></del>                           | MΩ   |

| Pull-down resistance               | RPD    | MANUAL & SLEEP MODE SELECT RT-TIME SET/DIMMER TEST                                                                                    |                                                               |          | 0.8  | -                                     | ΜΩ   |

| Oscillator stability               | fS     | CR OSC (Note 2)                                                                                                                       | VDD = 5.0 V                                                   | -10      |      | +10                                   | %    |

| Oscillator precision               | fA     | CR OSC (Note 2)                                                                                                                       | VDD = 5.0 V                                                   | -10      |      | +10                                   | %    |

| Oscillator frequency               | fOSC   | CR OSC                                                                                                                                | R = 91 kΩ ±1%<br>C = 3300 pF ±5%                              |          | 4800 | · .                                   | Hz   |

| Initial reset power supply voltage | VDET   | VDD<br>VSS                                                                                                                            | Power supply voltage<br>range when initial reset<br>operates. |          | 2.5  | 4.0                                   | ٧    |

| Current dissipation (operating)    | IDD    |                                                                                                                                       | With no output load                                           |          |      | 2                                     | mA   |

Note: 1. In addition to not exceeding the total output current <code>SILED</code> (from the absolute maximum ratings table), the segment output currents are allowed the following values within a 700 mW total power dissipation range.

10'SHRag & d: Up to -78 mA Others: Up to -39 mA

Current flowing out of the IC is expressed with negative values, and current flowing into the IC is expressed with positive values.

2. The total variation in the oscillator frequency will be the sum of the precision and the stability. That is, the limiting values for the oscillator frequency variation fall within the range from losc - 19% to fosc + 21%.

# **Functional Description**

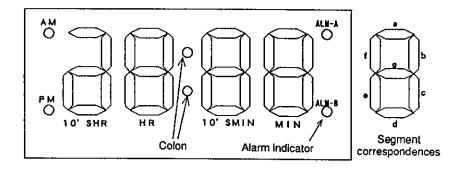

## **Segment Output**

This IC can directly drive with its 16 segment pins duplex type LED panels that include colon and alarm indicators. However, since the total value of the LED drive current ( $\Sigma$ ILED) flowing into the LED panel is limited to its absolute maximum value, caution is required in design.

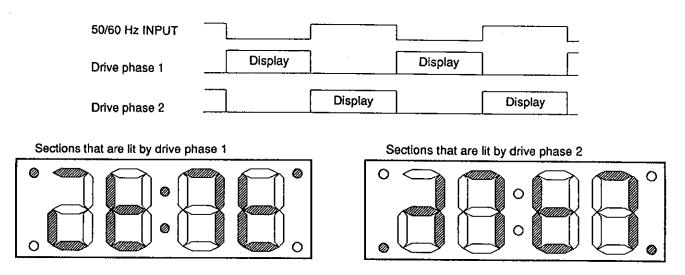

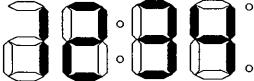

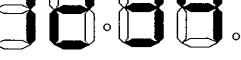

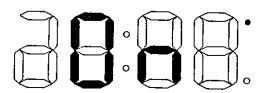

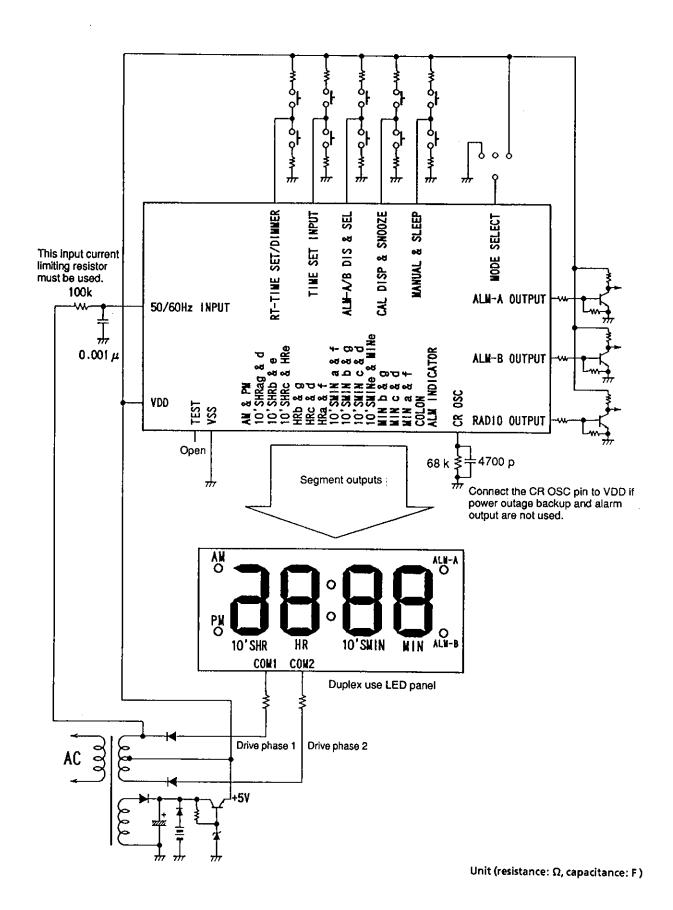

Figure 1 shows the correspondence between the LC85632 segment outputs and the LED panel. For example, pin 2 (the 10'SHRag & d pin) drives the segments 'a', 'g', and 'd' in the 10'SHR digit. Table 1 shows the correspondence between the drive phases and the segments that light.

Note that figure 1 is a generalized LED panel and not an exact representation of any particular product.

Figure 1 LED Panel and LED Segments

Table 1 Segment Lighting Correspondences for the Drive Phases

| No. | Pin             | Drive phase 1 | Drive phase 2 |

|-----|-----------------|---------------|---------------|

| . 1 | AM & PM         | AM            | PM            |

| 2   | 10'SHRag & d    | 10'SHR ad     | 10'SHR g      |

| 3   | 10'SHRb & e     | 10'SHR e      | 10'SHR b      |

| 4   | 10'SHRc & HRe   | HRe           | 10'SHR c      |

| 5   | HRb & g         | HRg           | HR b          |

| 6   | HRc & d         | HR d          | HR c          |

| 7   | HRa & f         | HRI           | HR a          |

| 8   | 10'SMIN a & f   | 10'SMIN a     | 10'SMIN f     |

| 9   | 10'SMIN b & g   | 10'SMIN b     | 10'SMIN g     |

| 10  | 10'SMIN c & d   | 10'SMIN c     | 10'SMIN d     |

| 11  | 10'SMINe & MINe | MIN e         | 10'SMIN e     |

| 12  | MIN b & g       | MIN g         | MIN b         |

| 13  | MIN c & d       | MiN d         | MIN c         |

| 14  | MIN a & f       | MIN f         | MINa          |

| 15  | COLON           | COLON         |               |

| 16  | ALM INDICATOR   | ALM-A         | ALM-B         |

Figure 2 shows the sections where LEDs are lit for each drive phase. This figure is based on the generalized drawing shown in figure 1, and the shaded sections show the segments that are lit by the corresponding phase.

Figure 2 LED Sections Lit by the Drive Phases

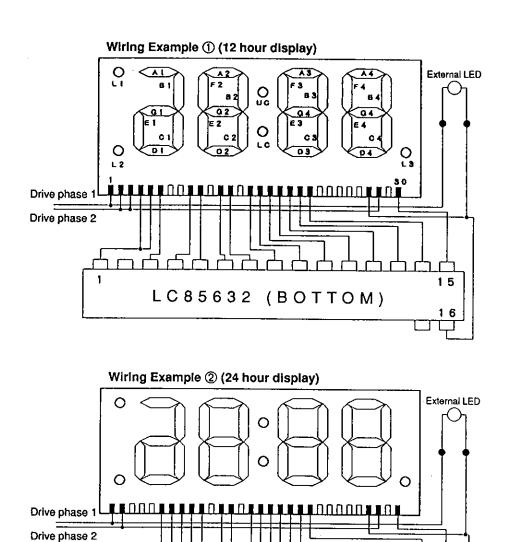

Figure 3 shows actual wiring examples for 12 hour and 24 hour displays for the Tottori Sanyo, Ltd., SL-1042-30T LED panel. However, since the SL-1042-30T LED panel does not have an alarm A display LED, an external LED is used for alarm A display. Also, the calendar day/month display cannot be used with this circuit.

Figure 3 LED Panel Wiring Examples

LC85632 (BOTTOM)

16

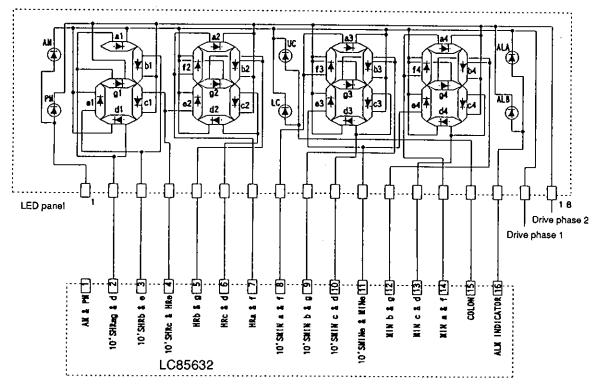

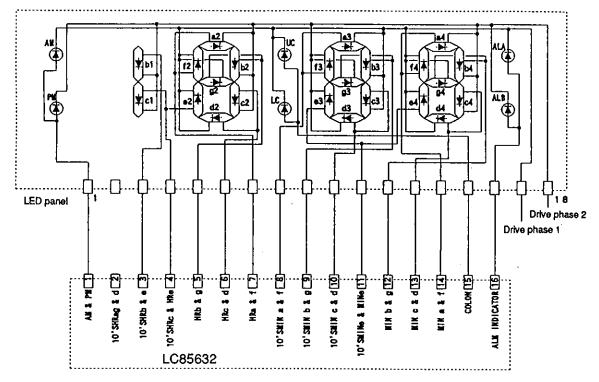

The following figures show the circuit diagrams for LED panels that can also display the alarm and calendar functions. These panels are the SL-1994-54T (for 12 hour display) and the SL-1994-55T (for 24 hour display), and are both made by Tottori Sanyo, Ltd.

The calendar day/month cannot be used with this circuit.

Figure 4 Wiring and Connection Example Using the SL-1994-54T LED Panel (12 hour display)

Figure 5 Wiring and Connection Example Using the SL-1994-55T LED Panel (24 hour display)

#### **Oscillator Circuit**

A 4800 Hz oscillator can be constructed by connecting a resistor and a capacitor to the CR OSC pin (pin 19). This oscillator is used as the internal clock for detecting the loss of external power, for alarm tones, and for the dimmer duty cycle. Therefore, it operates continuously during normal operation. In this section, we describe the operation when the AC input to the 50/60 Hz INPUT pin falls below 1 Hz.

During a power outage, LED segment output from pins 1 to 16 is stopped. Also when power is restored and the AC input becomes over 1 Hz, the whole LED display (except for the alarm indicator) flashes. The period of this flashing is 1 Hz. This period is created by dividing the period of the AC input from the 50/60 Hz either by 50 when the clock is operated at 50 Hz, i.e., when either a low or high level is applied to the MODE SELECT pin, or by 60 when the clock is operated at 60 Hz, i.e., when the MODE SELECT pin is left open. Apply either a high level or a low level to the TIME SET INPUT pin to stop the flashing. In either case the flashing will stop and the chip will return to normal operation, i.e., current time display.

Tie the CR OSC pin high if the oscillator circuit is not used. In this case the IC will not detect power loss. Also, the alarm function will not operate correctly, but will output either no signal or an irregular signal. Furthermore, no segment signals will be output in dimmer mode.

Note that if an oscillator circuit is not used, the high level applied to the CR OSC pin must be applied before power is applied. If the oscillator is forcibly stopped by applying a high level in the state where the CR oscillator is operating after power has been applied the alarm DC output may operate incorrectly.

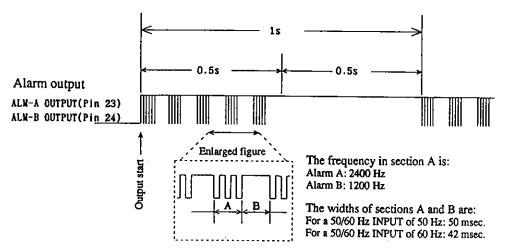

#### **Dual Alarms**

This IC provides two 24-hour alarms systems, each of which can be set in 1 minute increments. Alarm A outputs a 2400 Hz alarm tone, and alarm B a 1200 Hz tone. (See the "Alarm" section for details on the alarm waveforms.) The alarm tones are output continuously for 59 minutes, but can be interrupted for 6 to 7 minutes by the snooze function.

### Calendar

This IC includes an on-chip full-year month and day display calendar function. The display can be switched to be either a month/day or a day/month format. The calendar function can be set to display leap year's day (February 29) on what would have been March 1 by applying a low level to the TIME SET INPUT pin.

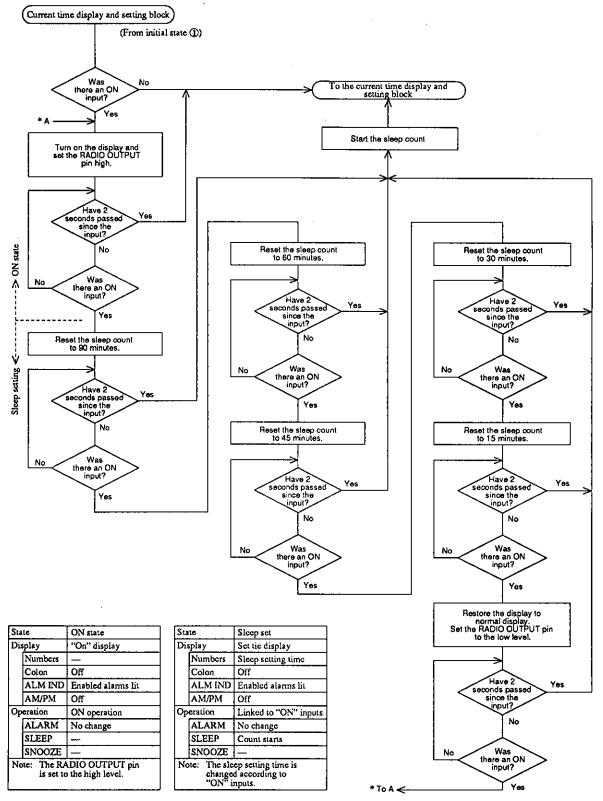

### Sleep Function

This IC includes a 90 minute sleep circuit (off timer) that can be set easily. The sleep function time setting can be set to be 90, 60, 45, 30, or 15 minutes in an "easy set" format.

# **Operating State Transition Diagram**

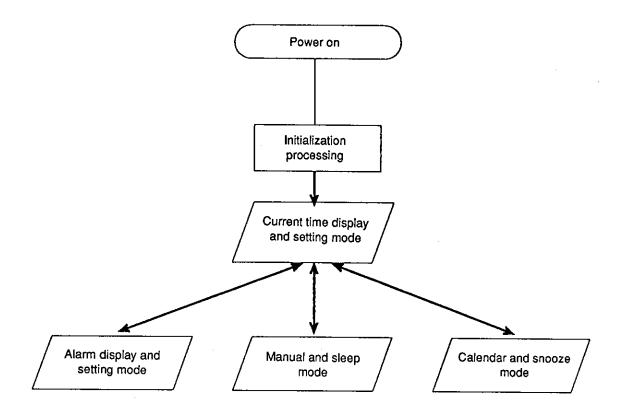

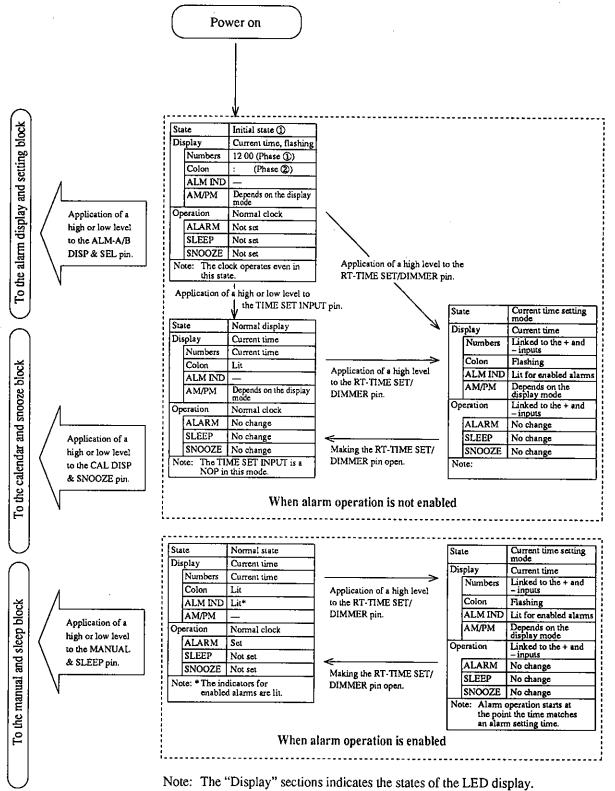

Figure 6 Operating State Transitions 1: Overall

Abbreviations: ALM IND. → Alarm indicator, AM/PM → AM, PM

Figure 7 Operating State Transitions 2: Current Time Display and Setting Block

The following are the alarm stop conditions during output.

- An OFF input (pin 22 = VSS)

- An ON input (pin 22 = VDD)

- · Arrival at the point 59 minutes following start of alarm output.

- A snooze input (pin 21 = VDD or VSS) (Alarm output restarts after the completion of the snooze operation.)

- The start of another alarm operation during alarm operation.

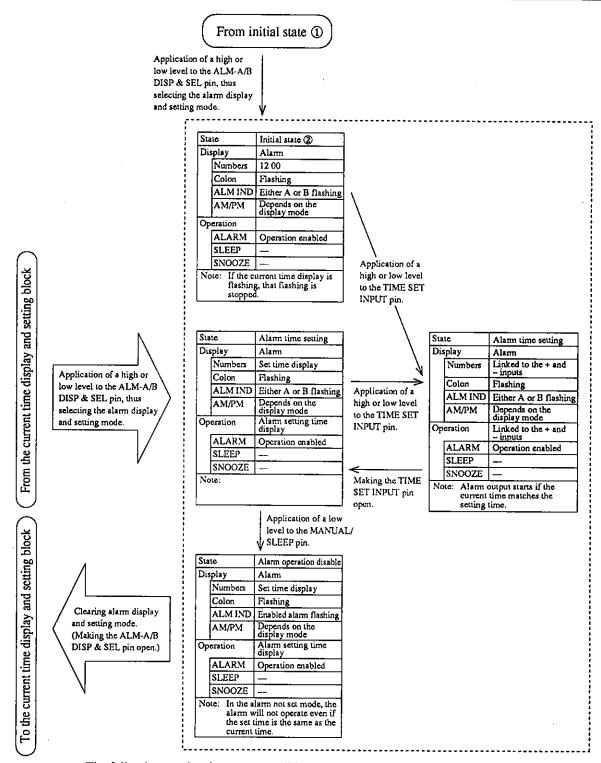

Figure 8 Operating State Transitions 3: Alarm Display and Setting Block

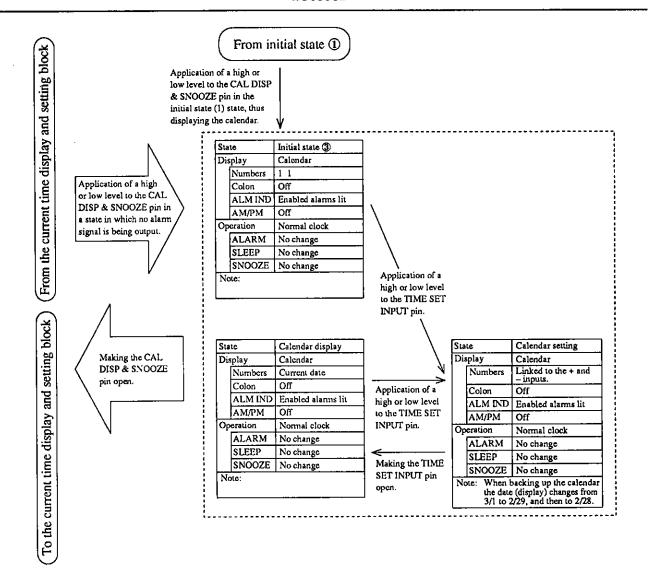

Figure 9 Operating State Transitions 4: Calendar Display and Setting Block

- \* "ON input": The application of a high level to the MANUAL & SLEEP pin.

- When the RADIO OUTPUT pin output is at the high level, the OFF input

(application of a low level to the MANUAL & SLEEP pin) will always be valid.

(If the RADIO OUTPUT pin is at the low level, the sleep counter will be reset

and the count stopped.)

Figure 10 Operating State Transitions 5: Manual and Sleep Block

# Operation

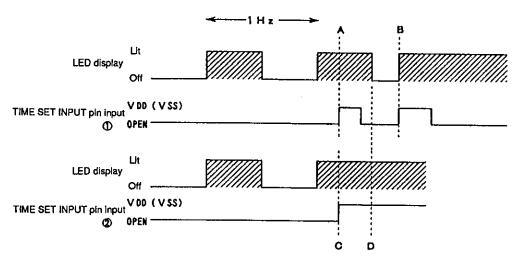

### Clearing the Initial Reset State

In the initial state when power is first applied, the display reads 12:00 (or 0:00 for 24 hour display) and the numbers and the colon flash alternately. This is called the "initial reset state". The period of the flashing is 1 Hz.

To clear the flashing state, apply a high or low level to the TIME SET INPUT pin when the colon is lit.

Figure 11 Clearing the Initial Input State Flashing

In figure 11, the shaded areas under the LED display line are times when the numbers are lit. At these times the colon will be off.

Here, the application of an input to the TIME SET INPUT input ① in the figure when the numbers are lit, i.e., the timing indicated by "A", will be invalid. Since the colon is off at that point, the flashing state will not be cleared. However, such an input is valid at a point when the numbers are off, i.e., the timing indicated by "B". Since the colon will be lit in this state, the flashing state will be cleared and the clock will enter normal display mode.

Alternatively, an input signal such as the TIME SET INPUT input ② in the figure can be applied. Here, the low (or high) level is held until the flashing is cleared at the timing indicated by "D" in the figure.

When the flashing state is cleared, the colon also will stop flashing, and remain lit.

### Setting the Time

### \* RT-TIME SET/DIMMER [Pin 29]

| VSS        | OPEN                   | VDD                       |

|------------|------------------------|---------------------------|

| DIMMÉR     | NOP                    | Current time setting mode |

| (1/4 DUTY) | (Current time display) |                           |

#### \* TIME SET INPUT [Pin 20]

| VSS    | OPEN                   | VDD       |

|--------|------------------------|-----------|

| DOWN   | NOP                    | UP        |

| (Back) | (Current time display) | (Forward) |

### (1) Normal operation (current time display mode)

RT-TIME SET/DIMMER pin: Open TIME SET INPUT pin: Open

In this state the current time is displayed and inputs to the TIME SET INPUT pin (pin 20) for setting the time will be ignored.

#### (2) Current time setting mode

The IC can be switched to the current time setting mode by applying a high level to the RT-TIME SET/DIMMER pin (pin 29). The current time can only be changed in this mode, and is changed by inputs to the TIME SET INPUT pin (pin 20). The current time setting mode and the current time display mode can be distinguished by the state of the colon. If the colon is lit steadily then the IC is in display mode, and if the colon is flashing with a 1 Hz period then the IC is in setting mode. Normally, the clock continues to operate in setting mode.

If a high level is applied to the TIME SET INPUT pin in setting mode, the second counter is reset to zero and the time is advanced by one minute. Inversely, if a low level is applied, the second counter is reset to zero and the time is backed up by one minute. In either case, clock operation is interrupted at the point that the input is applied to the TIME SET INPUT pin. Furthermore, if the input is held for over 0.5 to 1.0 seconds, the IC switches to quick forward (or quick reverse) mode. In these modes, counting speed will be 20 msec/count for a 50 Hz input to the 50/60 Hz INPUT pin, and 17 msec/count for a 60 Hz input to that pin.

When the time has been set, normal clock operation can be restarted by making the TIME SET INPUT pin open.

### (3) Dimmer display

# RT-TIME SET/DIMMER pin: Low level

If an RC circuit is connected to the CR OSC pin (pin 19) this input can be used to set the LED lit time to 1/4 of that in normal operation, thus reducing the effective LED brightness. This sets the LED display to a 1/4 duty cycle. In this mode, the LED on time will 1/4 of that in normal operation, with no influence on any other operation.

If an RC circuit is not provided the LED output will go to zero, i.e., this input can be used to turn off LED display.

This operation is a toggle operation. The first time a low level is applied to the RT-TIME SET/DIMMER pin dimmed display is setup, and the next time a low level is applied the display will return to normal.

#### Alarm

### \* ALM-A/B DISP & SEL. [Pin 25]

| VSS                      | OPEN                   | VDD                      |

|--------------------------|------------------------|--------------------------|

| Alarm B set time display | NOP                    | Alarm A set time display |

| (Setting enabled)        | (Current time display) | (Setting enabled)        |

# (1) Entering alarm mode

Alarm A set time display (setting enabled): High level Alarm B set time display (setting enabled): Low level

This pin should be left open in normal operation.

Applying a high or low level to this pin displays the set time for alarm A (high level) or alarm B (low level) and enables the alarm time to be set. The display switches to set time display (with an initial value of 12:00 or 0:00) and the colon and the corresponding alarm indicator (ALM INDICATOR) flash in synchronization.

### (2) Adjusting the set time

The alarm time settings are adjusted by displaying the alarm whose setting is to be changed, and then inputting a high or low level to the TIME SET INPUT pin (pin 20). We will refer to these latter operations as "+ input" and "- input" in the remainder of this section.

The initial value of the display will be 12:00 (or 0:00) unless there was a previous setting, in which case that value is displayed. The alarms are set in 1 minute increments, and the setting is changed by one minute each time a + input or a - input is applied. Furthermore, if the + or - input is applied for more than 0.5 to 1.0 seconds the setting changes at a speed of 20 msec per increment when 60 Hz is input to the 50/60 Hz INPUT pin, and at 17 msec per increment for a 50 Hz input. Note that alarm output will start if the set time and the current time match during alarm setting.

### (3) Enabling and disabling alarms

Use the following methods to enable and disable the alarms.

· Enabling an alarm

At the point that the set time for the alarm to be operated is displayed, that alarm is enabled, and the alarm indicator (ALM INDICATOR) for that alarm is displayed.

· Disabling an alarm

When an alarms time setting is displayed, that alarm can be disabled by applying a low level to the MANUAL pin. At this point the colon will blink continuously and the alarm indicator for the corresponding alarm will go out. Note that the set time is maintained, i.e., is not reset.

### (4) Alarm operating conditions

The alarm operates under either of the following conditions:

- If the alarm set time and the current time agree when alarm operation is enabled.

- If the alarm set time and the current time agree while setting the alarm time, i.e., while advancing or backing up the alarm time setting.

#### (5) Alarm operation termination conditions

Alarm output stops if any of the following conditions are met.

- If a high or low level is applied to the MANUAL & SLEEP pin (pin 26).

- If there was a snooze input, i.e., if either a high or low level was applied to the CAL DISP & SNOOZE pin). Note that alarm output will resume once the snooze setting period has elapsed.

- If a total time of 59 minutes (excluding the snooze interrupt periods) has passed since the start of the alarm output.

- If the other alarm starts operation during alarm output. (See item (7), "Output,")

- If the other alarm starts operation during an interruption of alarm output due to the snooze function. (See item (7), "Output.")

- (6) Restart of and alarm interrupted by the snooze function

- · A snooze operation completes 6 to 7 minutes after its start.

- If the current time is changed during a snooze operation, the snooze period will be shortened by the amount the time is changed, regardless of whether the time was advanced or moved backwards. For example, if directly following the start of a snooze operation the current time is set back by 3 minutes, the alarm interruption period due to the snooze function will be reduced by 3 minutes to be between 3 and 4 minutes.

#### (7) Output

• The alarm A and B outputs have the following form.

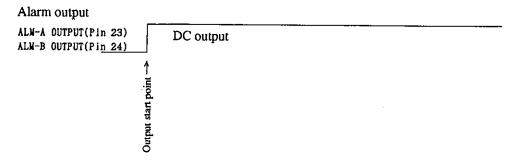

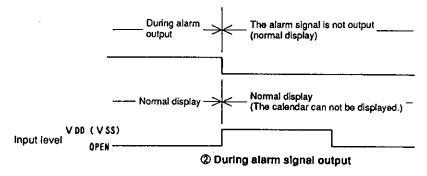

Figure 12 Alarm Output Waveforms

However, if no oscillator circuit is attached at the CR OSC pin (pin 19) the output will be a DC signal unmodulated by any tone.

Note that if an oscillator circuit is not used, the high level applied to the CR OSC pin must be applied before power is applied. If the oscillator is forcibly stopped by applying a high level in the state where the CR oscillator is operating after power has been applied the alarm DC output may operate incorrectly.

Figure 13 Alarm Output Waveform Overview (for the case where the output is a DC signal unmodulated by any tone)

- The conditions concerning alarm output are as follows:

- In principle, the later occurring alarm is given priority.

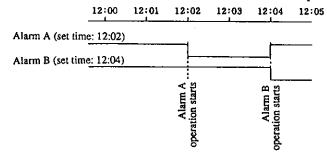

Example: The alarms will operate as follows if alarm A is set for 12:02 and alarm B is set for 12:04.

- Alarm A begins to operate at 12:02

- At 12:04 alarm B begins to operate. At the same time alarm A stops.

Figure 14 Alarm Operation Priority

Exceptions to later arrival priority: Although in principle the later occurring alarm take priority, in the following case alarm A takes priority and alarm B does not operate.

Assume that the alarm A set time is 12:30 and the alarm B set time is 12:00 and the alarms are enabled at

Now, time progress and 12:30 arrives and alarm B operates. At this point, while the current time is still 12:30, alarm B will not operate even if the alarm B set time is advanced to 12:30. Here, alarm A will take priority and alarm B will not operate.

- If both alarms are set to the same time, alarm A takes priority and alarm B does not operate.

- If the other alarm operates during a snooze interruption of one alarm, the interrupted alarm is stopped.

Example: Assume alarm A has been interrupted by the snooze function and alarm B operates. At this point only the ALM-B OUTPUT pin outputs an alarm signal, and no signal is output from the ALM-A OUTPUT pin when the snooze period for alarm A completes.

### (8) Other points

Notes on the alarm indicators (ALM INDICATOR)

This output is used to display the alarm state on the LED display. Its display states are as follows.

- Normal operation (No alarm times set and no operations enabled): Off

- Normal operation (Alarm time set and alarm enabled) : On

- Alarm setting mode

- Initial state flashing mode

- Flashing mode following a power loss

- : Flashing (1 Hz) : Lit (not flashing)

- : Lit (not flashing)

Not set (No alarm signals will be output)

Set (Alarm signals will be output)

Figure 15 Alarm Indicators

## · Radio output

If the radio output is in the on state, i.e., the RADIO OUTPUT pin is high, and either alarm A or alarm B output goes on, the radio output will go off, i.e., the RADIO OUTPUT pin will go low.

#### Calendar

### (1) Overview

This IC includes a one year calendar on-chip. It only supports month and date displays, and does not provide a day of the week display. The following calendar table is included on-chip.

| Month | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|

| Days  | 31 | 28 | 31 | 30 | 31 | 30 | 31 | 31 | 30 | 31 | 30 | 31 |

This calendar function can display February 29 to handle leap year's day.

- · During calendar display the AM/PM indicator and the colon are turned off.

- · Alarm indicators for enabled alarms (ALM INDICATOR) are lit.

- The display format can be switched to be either month-day or day-month.

### (2) Functions

#### \* CAL. DISP & SNOOZE [Pin 21]

| VSS                                                          | OPEN                          | VDD                                                          |

|--------------------------------------------------------------|-------------------------------|--------------------------------------------------------------|

| Calendar display and set<br>(Month-day display)<br>Snooze√in | NOP<br>(Current time display) | Calendar display and set<br>(Day-month display)<br>Snooze-in |

- When a high level is applied to the CAL DISP & SNOOZE pin (pin 21) the calendar is displayed in the day-month format, and when a low level is applied it is displayed in the month-day format.

- The calendar is set using either a high level or a low level input to the TIME SET INPUT pin (pin 20) while the calendar is displayed.

### (3) Operation

### Display

The calendar is displayed when either a high or a low level is applied to the CAL DISP & SNOOZE pin (pin 21). Only numbers and the alarm indicators for alarms that are enabled are displayed; the other segments (AM/PM and the colon) are turned off.

However, note that the CAL DISP & SNOOZE pin operates as snooze function input during alarm signal output and periods when the alarm output is interrupted by the snooze function. During those times the calender is not displayed.

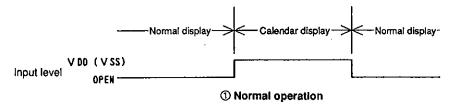

Figure 16 Caléndar Display Setting

- · Operating conditions

- Normal operation

When the time advances from 23:59 to 0:00 (0:00 a.m.), the date is advanced by 1 day.

- Current time setting mode

The clock time setting is advanced or set back in current time setting mode. If the time setting passes through 0:00 a.m. during that operation, the calendar is advanced or set back by one day.

During calendar display

If a high level is applied to the TIME SET INPUT pin during calendar display, the date is advanced by one day, and if a low level is applied, it is set back by one day.

### Setting

— The calendar can be set during calendar display

The calendar display following initial reset, i.e., the initial value, will be January 1. the TIME SET INPUT pin is used for setting the date.

If a high level is applied to the TIME SET INPUT pin during calendar display, the date is advanced by one day, and if a low level is applied, it is set back by one day. In either case, if the input is applied for more than 0.5 to 1.0 seconds the setting changes at a speed of 20 msec per increment when 60 Hz is input to the 50/60 Hz INPUT pin, and at 17 msec per increment for a 50 Hz input.

- Only the day can be changed directly using the TIME SET INPUT pin. To change the month, count either up or down through the days of the month. For example,  $1/30 \rightarrow 1/31 \rightarrow 2/1$ , or  $2/2 \rightarrow 2/1 \rightarrow 1/31$ .

- Displaying leap year's day (2/29)

To display leap year's day, with the calender display set to 3/1, apply a low level to the TIME SET INPUT pin for more than 20 msec and less than 0.5 seconds, i.e., back up the date one day. In normal operation, the date advances from 2/28 to 3/1, but in date backup, the date changes from 3/1 to 2/29 and then to 2/28.

$2/27 \rightarrow 2/28 \rightarrow 3/1 \rightarrow 3/2...$ : Normal calendar display

$3/2 \rightarrow 3/1 \rightarrow 2/29 \rightarrow 2/28...$ : Display when setting the calendar in the reverse direction

#### Manual and Sleep

### \* MANUAL & SLEEP [Pin 26]

| VSS       | OPEN                          | VDD                  |

|-----------|-------------------------------|----------------------|

| OFF input | NOP<br>(Current time display) | ON input<br>Sleep-in |

#### (1) Function

This pin has the following functions.

- RADIO OUTPUT pin (pin 22) output control

- · Alarm output stop control

- Sleep operation setting (including setting the operating time)

### (2) Operation

• RADIO OUTPUT pin output control

The output of the RADIO OUTPUT pin can be controlled by applying a high or low level to the MANUAL & SLEEP pin. The operations of applying a high or low level to this pin for over 20 msec and under 0.5 seconds are abbreviated as "an ON input" and "an OFF input" in the remainder of this section.

The operations performed on an ON input are as follows:

- The RADIO OUTPUT pin output is made active, i.e., the pin 22 output goes to the high level.

- Any alarm operation either in progress or interrupted by the snooze function is stopped.

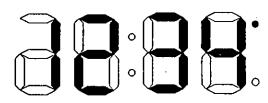

- "On" is displayed in the LEDs.

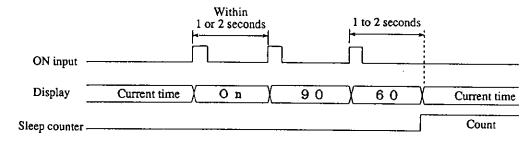

Figure 17 Radio Output "On" Display

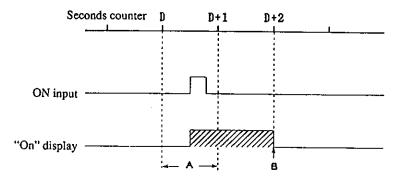

At the same time the sleep counter is reset to 90 minutes, and the sleep counter begins to count. The "On" display is displayed for 1 or 2 seconds following the ON input, and then the display returns to current time display.

Example: If an ON input occurs in the interval A in figure 18, then the display returns to current time display at point B. (Shaded section: "On" display)

Figure 18 "On" Display Timing

The operations performed on an ON input are as follows:

- Any alarm operation in progress is stopped.

- The RADIO OUTPUT pin output is set to the low level (high impedance).

- The LED display is restored to current time display.

- The sleep counter is reset to 90 minutes, and the count operation is stopped.

• If another ON input is applied during "On" display, the IC enters sleep mode.

The following operations are performed in sleep mode.

— The display is changed from "On" to "90".

Figure 19 Sleep Setting Time Display

— The display is held in that form for a 1 to 2 second period, and if another ON input is applied during this display, the display changes to 60. Thereafter, each display is held for 1 to 2 seconds, and if another ON input is applied, the display changes from "60" to "45" to "15" to the current time display, and then to "On" again.

If no ON input is applied during one of these 1 to 2 second waiting periods, the display returns to current time display and the sleep counter is started.

However, note that when the sleep display changes from "15" to current time display, the RADIO OUTPUT pin (pin 22) output goes off, i.e., to a low level output.

- If a snooze input (the application of a high or low level to the CAL DISP & SNOOZE pin) occurs during sleep operation sleep operation is terminated and the RADIO OUTPUT pin (pin 22) is turned off, i.e., set to a low level output.

- During display of the "On", 90, 60, 45, 30, and 15 sleep displays, only the alarm indicators for the enabled alarms are displayed, and the colon and AM/PM displays are turned off.

Figure 20 Sleep Setting Timing

• If the current time is changed (set) after setting the sleep interval, the length of the set sleep interval up to the point the radio goes off may change. Therefore, if the current time is changed (set) after setting the sleep interval it will be necessary to reset the desired sleep interval.

Example: Set the sleep interval to 60 minutes. Then, either quick advance or quick return the current time by 25 minutes using the current time setting mode. At this point, the sleep counter will have been advanced by the amount the current time was advanced or set back, and the actual sleep time will be 35 minutes.

# **AC Input**

## \* 50/60 Hz INPUT [Pin 27]

| Input                      |  |

|----------------------------|--|

| AC input (f = 50 Hz/60 Hz) |  |

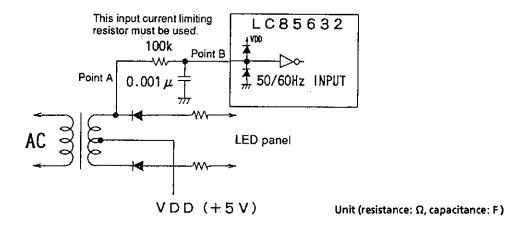

- (1) The AC input should be 50 or 60 Hz. This input uses the 50/60 Hz INPUT pin. This input is used as the reference clock during normal operation.

- (2) AC input to the 50/60 Hz INPUT pin

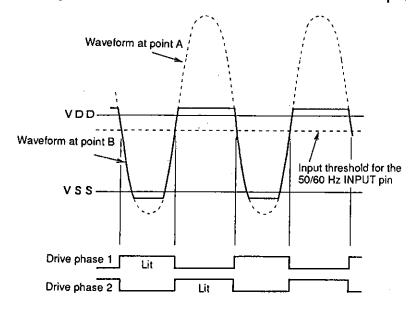

We recommend the circuit shown as an example in figure 21. Figure 22 shows the input waveform when this circuit is used.

The input threshold voltage for the 50/60 Hz INPUT pin is set to a voltage close to the VDD voltage. Since the display drive phase is generated from the AC waveform input to the 50/60 Hz INPUT pin, it is important to input the AC waveform centered around the VDD voltage to prevent creating an unbalanced display duty.

Note that the overdrive portion of the input waveform that exceeds the VDD and VSS voltages (indicated by a broken line in figure 22) is clipped by clamping diodes built into the 50/60 Hz INPUT pin, and the actual waveform becomes that shown in figure 22.

Figure 21 Recommended Circuit for AC Waveform Input

Figure 22 AC Input Waveform

- (3) The IC determines whether power has been lost based on whether there is an AC input to the 50/60 Hz INPUT pin.

- · Determining that power has been lost

When the AC input falls under 1 Hz, the IC determines that power has been lost and stops display output. However, this determination is performed by comparing that input with the frequency from the RC oscillator on the CR OSC pin. If the CR OSC pin is not used, the IC will not check for power outages.

Note that a high level should be applied to the CR OSC pin if it is not used.

### · Power outage operation

If a backup oscillator is connected to the CR OSC pin, at the point that a power outage is detected LED segment output and RADIO OUTPUT pin output are stopped. Also, if an alarm has been interrupted by the snooze function, the snooze function is cleared and the alarm output restarted. At this point the clock operation will continue using the backup oscillator.

During a power outage, only the OFF input (a low level to the MANUAL & SLEEP pin) is valid, and all other operation inputs are disabled.

During the backup state following a power outage detection, at the point that the AC input is restored to a frequency over 1 Hz the IC switches from operation based on the RC oscillator to operation based on AC input. The display indicates a power outage by displaying the current time flashing at 1 Hz. However, alarm indicators for enabled alarms will be lit and not flashing. Apply a high or low level to the TIME SET INPUT pin to stop the flashing and return to normal display.

Note that if the conditions for an alarm are fulfilled, that alarm will be output even during a power outage.

If a backup oscillator is not connected to the CR OSC pin, all operations will halt. That is, power outage detection and backup operation are not performed. Also, the following operations will be performed after recovery from a power outage.

- If the rated power supply voltage (4.0 to 6.0 V) was maintained:

- Clock operation restarts from the point power was lost.

- If the power supply voltage fell below the rated voltage:

The IC returns to the initial start state.

### · Current time during a power outage

The current time is maintained during a power outage using a clock signal generated by dividing the oscillation frequency of the RC oscillator circuit. The standard oscillation frequency of the RC oscillator circuit is 4800 Hz. When the mode is set to 50 Hz mode, the 4800 Hz signal is divided by 96 to form a 50 Hz signal, and when set to 60 Hz mode, the 4800 Hz signal is divided by 80 to form a 60 Hz signal.

#### Colon

- Remains lit during normal operation.

- (2) Flashes at 1 Hz following a initial reset, following recovery from a power outage, and during time setting modes for the current time, alarm A, and alarm B.

- (3) Turns off during calendar display and the "On" and sleep time displays.

#### Self Test Mode

#### \* TEST [Pin 18]

| VSS                | OPEN             | VDD                      |  |  |

|--------------------|------------------|--------------------------|--|--|

| LED self test mode | Normal operation | IC test, illegal setting |  |  |

This IC provides a self-test mode for testing the LED display and the three value input pins. It supports the following tests.

The LEDs can be tested for failure to light and for unbalanced intensity.

This test mode is entered when a low level is applied to the TEST pin (pin 18), and all LED segments are lit. In this state, the LED segments can be turned off individually by applying high or low levels to the three value input pins. The correspondence between the applied inputs and the segments that are turned off is shown in the table below.

| Input pin          | Input level | Corresponding LED segment*1 |  |

|--------------------|-------------|-----------------------------|--|

| RT-TIME SET        | High level  | a segment*2                 |  |

| TIME SET INPUT     | High level  | b segment                   |  |

| TIME SET INPUT     | Low level   | c segment                   |  |

| ALM-A/B DISP & SEL | High level  | d segment*2                 |  |

| ALM-A/B DISP & SEL | Low level   | e segment                   |  |

| MANUAL & SLEEP     | High level  | f segment                   |  |

| MANUAL & SLEEP     | Low level   | g segment                   |  |

| CAL DISP & SNOOZE  | Both*3      | COLON                       |  |

| RT-TIME SET        | Low level   | AM, PM, ALM-A, ALM-B        |  |

- Note: 1. The LED segments are lit or turned off at the same time for all digits. For example, after setting the IC to LED test mode, if a high level is applied to the TIME SET INPUT pin, then all 4 a segments (one LED in each 4 digits) are turned off.

- 2. Due to details of the output pins only the 10'SHR d segment is not linked to rest of the d segment, but is turned off an on along with the a segment.

- 3. Operates identically for both high and low level signals.

- 4. Since the operations in the above table are toggle operations, repeated application of signals to the three value inputs will repeatedly turn each segment on and off.

- 5. When the IC is in the LED test mode, the MODE SELECT pin must be held at either the high, open, or low level. Operation of the IC is not guaranteed if the signal on the MODE SELECT pin changes while the IC is in the LED test mode.

- 6. The TEST pin must be left open during normal operation.

- 7. Do not change the setting on the MODE SELECT pin (pin 28) when the IC in self test mode. System operation is not guaranteed if this setting is changed.

### **Display Priority Ordering**

The priority order for display when inputs are applied to two or more of the following pins at the same time is shown in the box below.

- CAL DISP & SNOOZE (pin 21)

- ALM-A/B DISP & SEL (pin 25)

- MANUAL & SLEEP (pin 26)

- RT-TIME SET/DIMMER (pin 29)

Current time display < Sleep ON display < Alarm setting time display < calender and snooze displays

Example: If a high level is applied at the same time to both the ALM-A/B DISP & SEL and the CAL DISP & SNOOZE pins in current time display (setting) mode, then the display will switch to calendar display.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

Note: T .....Three value input circuit

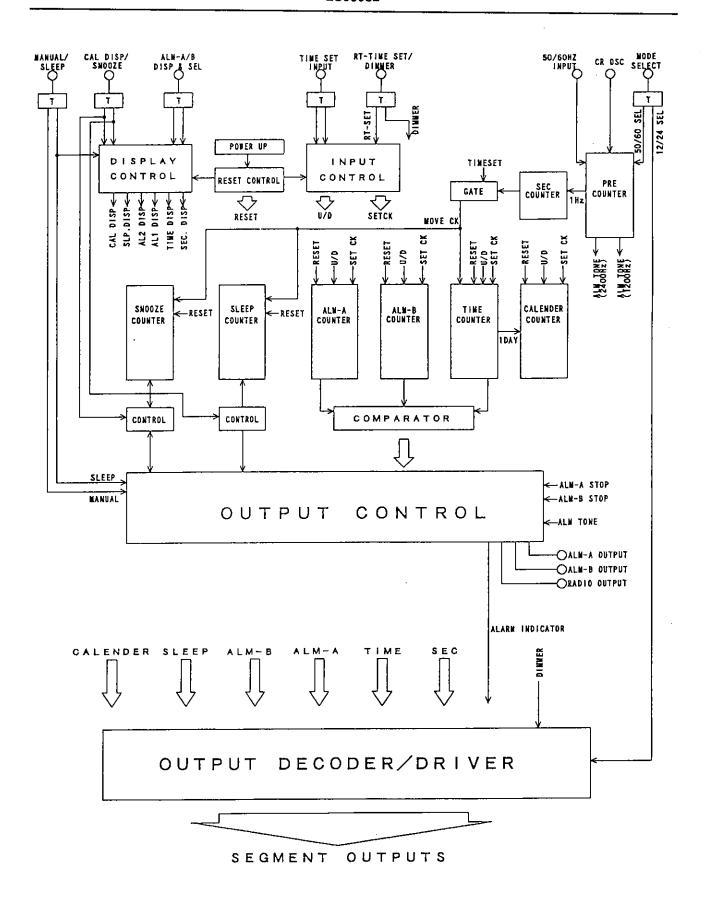

Figure 23 LC85632 Block Diagram

Figure 24 LC85632 Application Circuit