# **DSP for Compact Disk Players**

# Overview

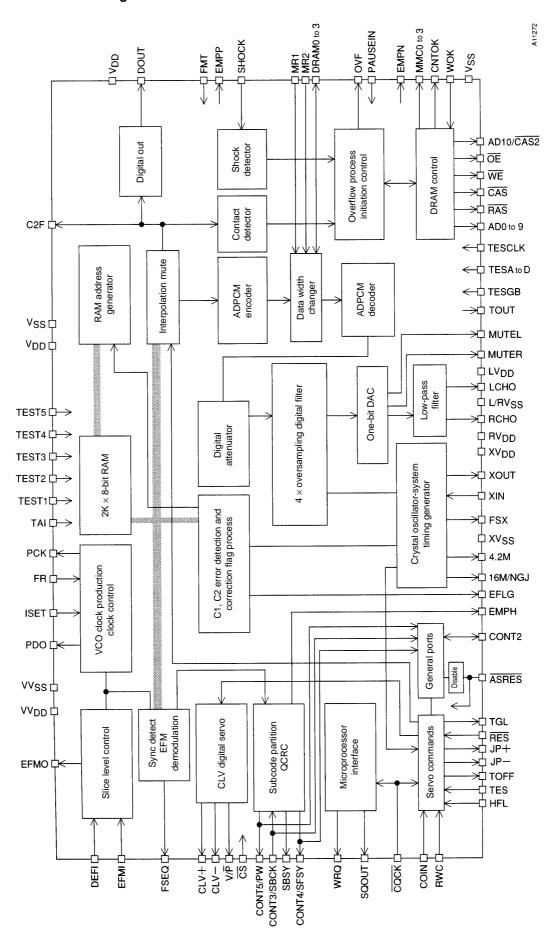

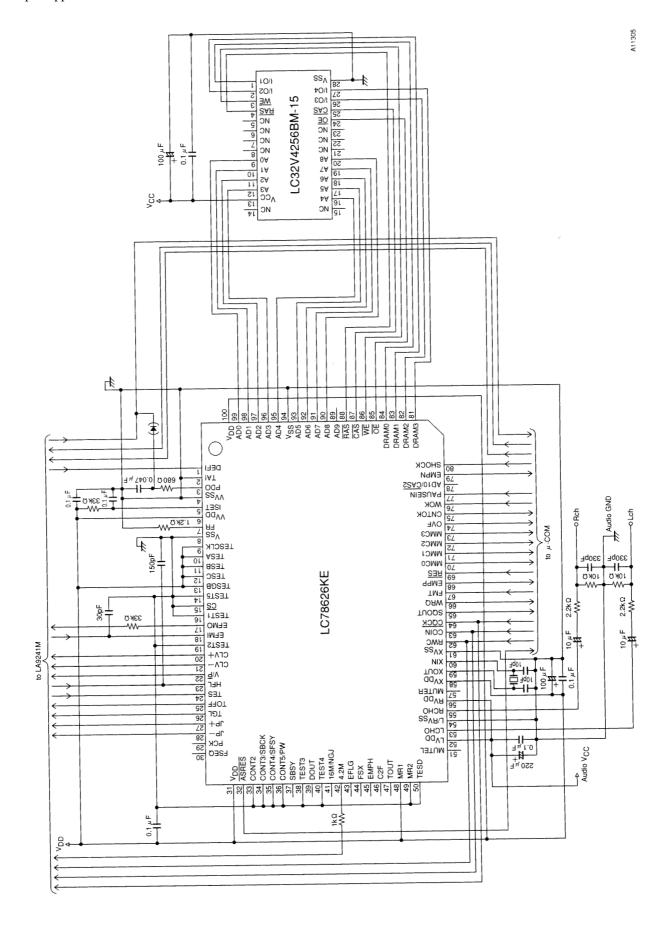

The LC78626KE is a monolithic compact disk player signal processing and servo control CMOS IC equipped with an internal anti-shock control function. Designed for total functionality including support for EFM-PLL, and one-bit D/A converter, and containing analog low-pass filter, the LC78626KE provides optimal cost-performance for low-end CD players that provide anti-shock systems by eliminating as many unnecessary features as possible. The basic functions provided by this IC include modulation of the EFM signal from the optical pick-up, deinterleaving, detection and correction of signal errors, prevention of a maximum of approximately 38 seconds of skipping, signal processing such as digital filtering (which is useful in reducing the cost of the player), and processing of a variety of servo-related commands from the microprocessor. The LC78626KE is an improved version of the LC78626E. It provides 8× oversampling digital filters and supports up to 16M of DRAM.

#### **Functions**

- When an HF signal is input, it is sliced to precise levels and converted to an EFM signal. The phase is compared with the internal VCO and a PLL clock is reproduced at an average frequency of 4.3218 MHz.

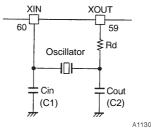

- Precise timing for a variety of required internal timing needs (including the generation of the reference clock) is produced by the attachment of an external 16.9344 MHz crystal oscillator.

- The speed of revolution of the disk motor is controlled by the frame phase difference signal generated by the playback clock and the reference clock.

- The frame synchronizing signal is detected, stored, and interpolated to insure stable data read back.

- The EFM signal is demodulated and converted to 8-bit symbolic data.

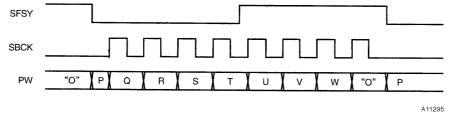

- The demodulated EFM signal is divided into subcodes and output to the external microprocessor. (Three general I/O ports are shared [exclusively] for this purpose.)

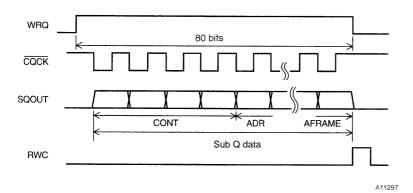

- After the subcode Q signal passes the CRC check, it is output to the microprocessor through a serial transmission (LSB first).

- The demodulated EFM signal is buffered in the internal RAM, which is able to absorb ±4 frame's worth of jitter resulting from variations in the disk rotation speed.

- The demodulated EFM signal is unscrambled to a specific sequence, and deinterleaving is performed.

Continued on next page.

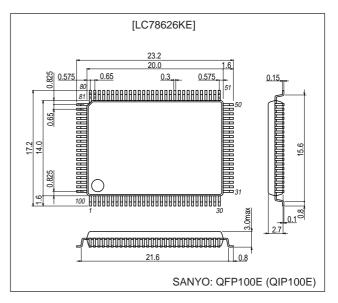

# **Package Dimensions**

unit: mm

# 3151-QFP100E

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

Continued from preceding page.

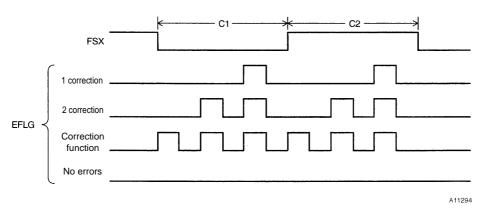

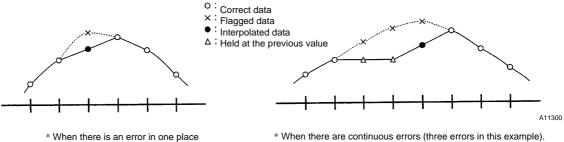

- Error detection and correction is performed, as is a flag process. (C1: two error/C2: two error correction method.)

- The C2 flag is set after referencing the C1 flag and the results of the C2 check, where the signal from the C2 flag is interpolated or held at its previous level. The interpolation circuit uses double interpolation. When there are two or more C2 flags in a row, the previous value is held.

- Command (such as track jump, start focus, disk motor start/stop, muting on/off, track count, etc.) is are executed after they are entered from the microprocessor. (An 8-bit serial input is used.)

- The digital output is equipped internally.

- High speed access is supported through discretionary track counting.

- Using the 8x oversampling digital filter, D/A converter signals with improved continuity of output data are produced.

- A ΔΣ-type D/A converter using a 3-order noise shaper is equipped internally. (An analog low-pass filter is equipped internally.)

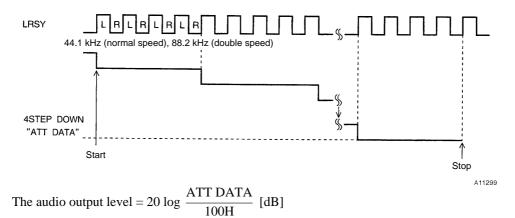

- Internal digital attenuator (8-bit-α; 239 steps.)

- Internal digital deemphasis

- Uses 0 cross mute.

- · Bilingual compatibility

- General I/O ports: 4. (Three of these are shared, exclusively, with the subcode output function.)

- Up to 38 seconds of skip prevention (when using 16M of DRAM) through 5-bit ADPCM compression/ expansion processing. 1M/4M/4M × 2/16M bits DRAM can be selected.

- · Memory overflow detection output

- Free memory output

# **Features**

- 100-pin QIP

- A single 3.2 V power supply

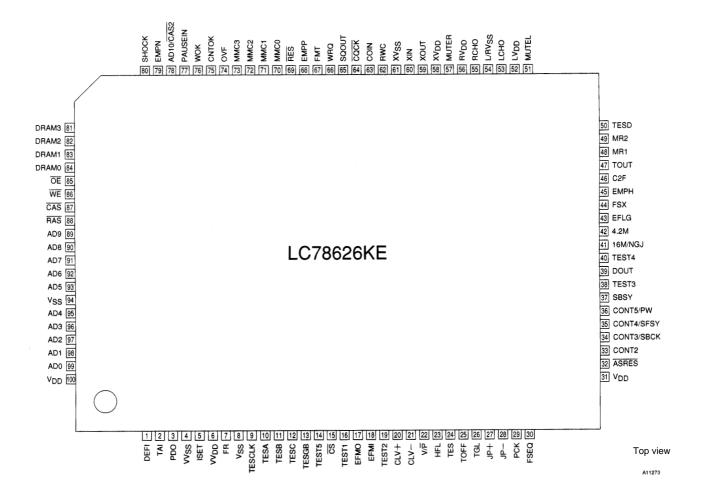

### **Pin Assignment**

# **Equivalent Circuit Block Diagram**

# Specifications Absolute Maximum Ratings at $Ta=25^{\circ}C,\,V_{SS}=0V$

| Parameter                    | Symbol              | Conditions | Ratings                          | Unit |

|------------------------------|---------------------|------------|----------------------------------|------|

| Maximum power supply voltage | V <sub>DD</sub> max |            | $V_{SS} - 0.3$ to $V_{SS} + 4.0$ | V    |

| Input voltage                | V <sub>IN</sub>     |            | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Output voltage               | V <sub>OUT</sub>    |            | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Allowable power dissipation  | Pd max              |            | 400                              | mW   |

| Operating temperature range  | Topr                |            | -20 to +75                       | °C   |

| Storage temperature range    | Tstg                |            | -40 to +125                      | °C   |

# Allowable Operating Range at $Ta=25^{\circ}C,\,V_{SS}=0V$

| Parameter                      | Symbol            | Conditions                                                                                                                            |                      | Ratings |                     | Unit  |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|---------------------|-------|

| Falanetei                      | Symbol            | Conditions                                                                                                                            | min                  | typ     | max                 | Offic |

|                                | V <sub>DD</sub> 1 | V <sub>DD</sub> , XV <sub>DD</sub> , LV <sub>DD</sub> , RV <sub>DD</sub> , VV <sub>DD</sub> :<br>ATT/DF/DAC to the normal speed       | 3.0                  |         | 3.6                 | V     |

| Power supply voltage           | V <sub>DD</sub> 2 | V <sub>DD</sub> , XV <sub>DD</sub> , LV <sub>DD</sub> , RV <sub>DD</sub> , VV <sub>DD</sub> :<br>All functions guaranteed to 2× speed | 3.6                  |         | 3.6                 | V     |

|                                | V <sub>IH</sub> 1 | I/O and input pins with the exception of EFMI and DRAM0 to DRAM3                                                                      | 0.7 V <sub>DD</sub>  |         | V <sub>DD</sub>     | V     |

| Input high-level voltage       | V <sub>IH</sub> 2 | EFMI                                                                                                                                  | 0.6 V <sub>DD</sub>  |         | $V_{DD}$            | V     |

|                                | V <sub>IH</sub> 3 | DRAM0 to DRAM3                                                                                                                        | 0.45 V <sub>DD</sub> |         | $V_{DD}$            | V     |

|                                | V <sub>IL</sub> 1 | I/O and input pins with the exception of EFMI and DRAM0 to DRAM3                                                                      | 0                    |         | 0.3 V <sub>DD</sub> | V     |

| Input low-level voltage        | V <sub>IL</sub> 2 | EFMI                                                                                                                                  | 0                    |         | 0.4 V <sub>DD</sub> | V     |

|                                | V <sub>IL</sub> 2 | DRAM0 to DRAM3                                                                                                                        | 0                    |         | 0.2 V <sub>DD</sub> | V     |

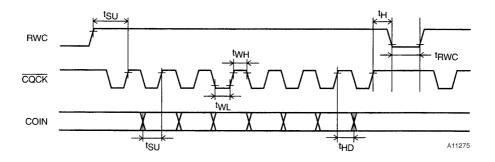

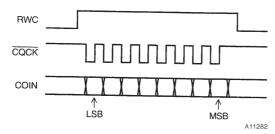

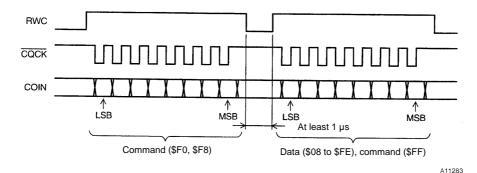

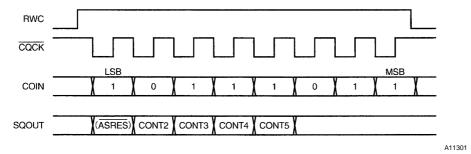

| Data setup time                | t <sub>SU</sub>   | COIN, RWC: Figure 1                                                                                                                   | 400                  |         |                     | ns    |

| Data hold time                 | t <sub>HD</sub>   | COIN, RWC: Figure 1                                                                                                                   | 400                  |         |                     | ns    |

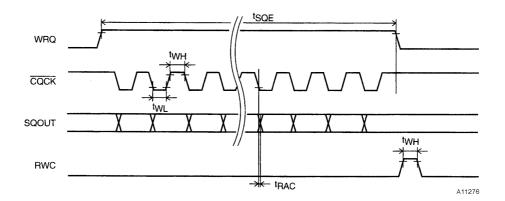

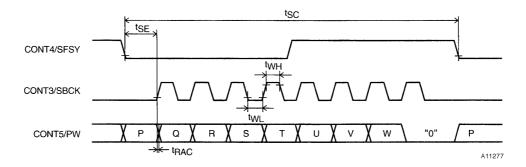

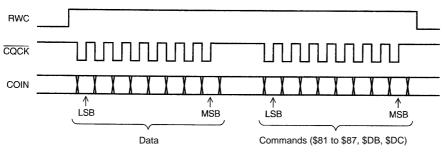

| High level clock pulse width   | t <sub>WH</sub>   | SBCK, CQCK: Figures 1 to 3                                                                                                            | 400                  |         |                     | ns    |

| Low level clock pulse width    | t <sub>WL</sub>   | SBCK, CQCK: Figures 1 to 3                                                                                                            | 400                  |         |                     | ns    |

| Data read access time          | t <sub>RAC</sub>  | SQOUT, PW: Figures 2 and 3                                                                                                            | 0                    |         | 400                 | ns    |

| Command transfer time          | t <sub>RWC</sub>  | RWC: Figure 1                                                                                                                         | 1000                 |         |                     | ns    |

| Subcode Q read enable time     | t <sub>SQE</sub>  | WRQ: Figure 2, no RWC signal                                                                                                          |                      | 11.2    |                     | ms    |

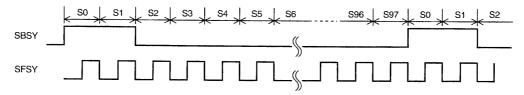

| Subcode ready cycle time       | t <sub>SC</sub>   | SFSY: Figure 3                                                                                                                        |                      | 136     |                     | μs    |

| Subcode read enable time       | t <sub>SE</sub>   | SFSY: Figure 3                                                                                                                        | 400                  |         |                     | ns    |

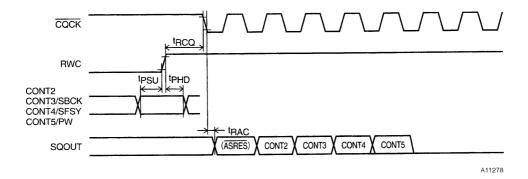

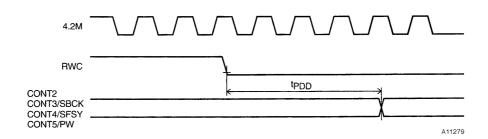

| Port input data setup time     | t <sub>CSU</sub>  | CONT2 to CONT5, RWC: Figure 4                                                                                                         | 400                  |         |                     | ns    |

| Port input data hold time      | t <sub>CHD</sub>  | CONT2 to CONT5, RWC: Figure 4                                                                                                         | 400                  |         |                     | ns    |

| Port input clock setup time    | t <sub>RCQ</sub>  | RWC, CQCK: Figure 4                                                                                                                   | 100                  |         |                     | ns    |

| Port output data delay time    | t <sub>CDD</sub>  | CONT2 to CONT5, RWC: Figure 5                                                                                                         |                      |         | 1200                | ns    |

| In most Invest                 | V <sub>IN</sub> 1 | EFMI: slice level control, V <sub>DD</sub> = 3.0 V                                                                                    | 0.8                  |         |                     | Vp-p  |

| Input level                    | V <sub>IN</sub> 2 | XIN: C coupling input                                                                                                                 | 1.0                  |         |                     | Vp-p  |

| Range of operating frequencies | f <sub>OP</sub>   | EFMI                                                                                                                                  |                      |         | 10                  | MHz   |

| Crystal oscillator frequency   | f <sub>X</sub>    | XIN, XOUT                                                                                                                             |                      | 16.9344 |                     | MHz   |

# Electrical Characteristics at $Ta=25^{\circ}C,\,V_{DD}=3.2\;V,\,V_{SS}=0V$

| Parameter                | Symbol            | Conditions                                                                                                                                                       | Ratings |     |     | - Unit |

|--------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|--------|

| Faianetei                | Symbol            | Conditions                                                                                                                                                       | min     | typ | max | Onit   |

| Current drain            | I <sub>DD</sub>   | $V_{DD}$ , $XV_{DD}$ , $LV_{DD}$ , $RV_{DD}$ , $VV_{DD}$ :<br>$V_{DD} = 3.0$ to 3.4 V with normal playback                                                       |         | 14  | 20  | mA     |

| Input high-level current | I <sub>IH</sub> 1 | DEFI, EFMI, HFL, TES, RWC, COIN, CQCK, FMT, MR1, MR2, RES, TESD, WOK, PAUSE IN, SHOCK, TESCLK, TESA, TESB, TESC, TESGB, TEST1: V <sub>IN</sub> = V <sub>DD</sub> |         |     | 5   | μA     |

|                          | I <sub>IH</sub> 2 | TAI, TEST2 to TEST5, $\overline{\text{CS}}$<br>V <sub>IN</sub> = V <sub>DD</sub> = 3.6 V                                                                         | 15      |     | 55  | μΑ     |

Continued on next page.

Continued from preceding page.

| Parameter                    | Symbol             | Conditions                                                                                                                                                                                                                 |            | Ratings |      | Unit |

|------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|------|------|

| Faranielei                   | Symbol             | Conditions                                                                                                                                                                                                                 | min        | typ     | max  | Onic |

| Input low-level current      | I <sub>IL</sub>    | DEFI, EFMI, HFL, TES, RWC, COIN, CQCK, FMT, MR1, MR2, RES, TESD, WOK, PAUSE IN, SHOCK, TESCLK, TESA, TESB, TESC, TESGB, TAI, TEST1 to TEST5, CS:                                                                           | <b>–</b> 5 |         |      | μА   |

|                              | V <sub>OH</sub> 1  | EFMO, CLV <sup>+</sup> , CLV <sup>-</sup> , V/\overline{P}, TOFF, TGL, JP <sup>+</sup> , JP <sup>-</sup> , PCK, FSEQ, EFLG, FSX, EMPH: I <sub>OH</sub> = -1 mA                                                             | 2.56       |         |      | V    |

| Output high-level current    | V <sub>OH</sub> 2  | CONT2 to CONT5, SBSY, MUTEL, MUTER, C2F, WRQ, SQOUT, 16M/NGJ, 4.2M, EMPP, OVF, CNTOK, NGJ: I <sub>OH</sub> = -0.5 mA                                                                                                       | 2.56       |         |      | V    |

|                              | V <sub>OH</sub> 3  | DOUT : I <sub>OH</sub> = -12 mA                                                                                                                                                                                            | 2.72       |         |      | V    |

|                              | V <sub>OH</sub> 4  | $\overline{OE}$ , $\overline{WE}$ , $\overline{CAS}$ , $\overline{RAS}$ , $\overline{AD10}/\overline{CAS}2$ , $\overline{AD9}$ to $\overline{AD0}$ , $\overline{DRAM3}$ to $\overline{DRAM0}$ : $\overline{IOH} = -0.5$ mA | 2.56       |         |      | V    |

|                              | V <sub>OH</sub> 5  | MMC0 to MMC3 : I <sub>OH</sub> = -2 mA                                                                                                                                                                                     | 2.24       |         |      | V    |

|                              | V <sub>OL</sub> 1  | EFMO, CLV <sup>+</sup> , CLV <sup>-</sup> , V/P, TOFF, JP <sup>+</sup> , JP <sup>-</sup> , PCK, FSEQ, EFLG, FSX, EMPH: I <sub>OL</sub> = 1 mA                                                                              |            |         | 0.64 | V    |

| Output law laval aureast     | V <sub>OL</sub> 2  | CONT2 to CONT5, SBSY, MUTEL, MUTER, C2F, WRQ, SQOUT, 16M/NGJ, 4.2M, EMPP, OVF, CNTOK: I <sub>OL</sub> = 2 mA                                                                                                               |            |         | 0.32 | V    |

| Output low-level current     | V <sub>OL</sub> 3  | DOUT : I <sub>OL</sub> = 12 mA                                                                                                                                                                                             |            |         | 0.48 | V    |

|                              | V <sub>OL</sub> 4  | OE, WE, CAS, RAS, AD10/CAS2, AD9 to AD0, DRAM3 to DRAM0 : I <sub>OL</sub> = 0.5 mA                                                                                                                                         |            |         | 0.44 | V    |

|                              | V <sub>OL</sub> 5  | MMC0 to MMC3 : I <sub>OL</sub> = 2 mA                                                                                                                                                                                      |            |         | 0.96 | V    |

| Output off leakage current   | I <sub>OFF</sub> 1 | PDO, CLV+, CLV-, JP+, JP-,<br>CONT2 to CONT5, DRAM0 to DRAM3,<br>ASRES: V <sub>OUT</sub> = V <sub>DD</sub>                                                                                                                 |            |         | 5    | μΑ   |

| Output on leanage current    | I <sub>OFF</sub> 2 | PDO, CLV <sup>+</sup> , CLV <sup>-</sup> , JP <sup>+</sup> , JP <sup>-</sup> ,<br>CONT2 to CONT5, DRAM0 to DRAM3,<br>ASRES: V <sub>OUT</sub> = 0 V                                                                         | <b>-</b> 5 |         |      | μА   |

| Charge pump output current   | I <sub>PDOH</sub>  | PDO : R <sub>ISET</sub> = 68 kΩ                                                                                                                                                                                            | 30         | 42      | 54   | μΑ   |

| Charge partip output current | I <sub>PDOL</sub>  | PDO : R <sub>ISET</sub> = 68 kΩ                                                                                                                                                                                            | -54        | -42     | -30  | μA   |

# One-bit D/A Converter Analog Characteristics at Ta = $25^{\circ}$ C, $V_{DD}$ = $LV_{DD}$ = $RV_{DD}$ = 3.2 V, $V_{SS}$ = $L/RV_{SS}$ = 0 V

| Parameter                      | Symbol | Conditions                                                                                      |     | Llmit |       |      |

|--------------------------------|--------|-------------------------------------------------------------------------------------------------|-----|-------|-------|------|

| raianietei                     | Symbol | Conditions                                                                                      | min | typ   | max   | Unit |

| Total harmonic distortion rate | TRD+N  | LCHO, RCHO; 1 kHz: Uses the 0 dB data input and the 20 kHz-LPF (in the AD725D)                  |     | 0.035 | 0.038 | %    |

| Dynamic range                  | DR     | LCHO, RCHO; 1 kHz: Uses the –60 dB data input, the 20 kHz-LPF (in the AD725D), and the A filter | 81  | 84    |       | dB   |

| Signal to noise ratio          | S/N    | LCHO, RCHO; 1 kHz: Uses the 0 dB data input, the 20 kHz-LPF (in the AD725D), and the A filter   | 87  | 92    |       | dB   |

| Cross talk                     | СТ     | LCHO, RCHO; 1 kHz: Uses the 0 dB data input and the 20 kHz-LPF (in the AD725D)                  | 79  | 82    |       | dB   |

Note: Measured with the normal-speed playback mode in the Sanyo one-bit D/A converter block reference digital attenuator circuit.

A11274

Figure 1 Command Input

Figure 2 Subcode Q Output

Figure 3 Subcode Output

Figure 4 General Port Input Timing

Figure 5 General Port Output Timing

# **Description of Pins**

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16                        | DEFI TAI PDO VV <sub>SS</sub> ISET VV <sub>DD</sub> FR V <sub>SS</sub> | I I O P AI P | Defect detect                                      | on signal (DEF) input. When not used, must be connected to 0 V.  Test input. Equipped with internal pull-down resistor. Must be connected to 0V.  Internal VCO control phase comparator output                                                                                                                                                                                                                                                                                       | _<br>_<br>_       |  |  |

|---------------------------------------------------------------|------------------------------------------------------------------------|--------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

| 3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | PDO VV <sub>SS</sub> ISET VV <sub>DD</sub> FR V <sub>SS</sub>          | O<br>P<br>Al | For the PLL                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |  |  |

| 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14      | VV <sub>SS</sub> ISET VV <sub>DD</sub> FR V <sub>SS</sub>              | P<br>Al      | For the PLL                                        | Internal VCO control phase comparator output                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                 |  |  |

| 5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14           | ISET VV <sub>DD</sub> FR V <sub>SS</sub>                               | AI           | For the PLL                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                 |  |  |

| 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15          | VV <sub>DD</sub><br>FR<br>V <sub>SS</sub>                              |              | IOI IIIE F LL                                      | Internal VCO ground. Must be connected to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                 |  |  |

| 7<br>8<br>9<br>10<br>11<br>12<br>13<br>14                     | FR<br>V <sub>SS</sub>                                                  | Р            |                                                    | PDO output current adjustment resistor connection                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                 |  |  |

| 8<br>9<br>10<br>11<br>12<br>13<br>14<br>15                    | V <sub>SS</sub>                                                        |              |                                                    | Internal VCO power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                 |  |  |

| 9<br>10<br>11<br>12<br>13<br>14<br>15                         |                                                                        | Al           |                                                    | VCO frequency range adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                 |  |  |

| 10<br>11<br>12<br>13<br>14<br>15                              | TECOLIA                                                                | Р            | Digital system                                     | ground. Must be connected to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                 |  |  |

| 11<br>12<br>13<br>14<br>15                                    | TESCLK                                                                 | ı            | Test clock inp                                     | ut. Must be connected to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                 |  |  |

| 12<br>13<br>14<br>15                                          | TESA                                                                   | 1            | Test operation                                     | n mode control input. Must be connected to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                         | _                 |  |  |

| 13<br>14<br>15                                                | TESB                                                                   | 1            | Test operation                                     | n mode control input. Must be connected to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                         | _                 |  |  |

| 14<br>15                                                      | TESC                                                                   | 1            | Test operation                                     | n mode control input. Must be connected to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                         | _                 |  |  |

| 15                                                            | TESGB                                                                  | 1            | Test operation                                     | n mode control input. Must be connected to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                         | _                 |  |  |

|                                                               | TEST5                                                                  | ı            | Test input. Ed                                     | uipped with internal pull-down resistor. Must be connected to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                   | _                 |  |  |

| 16                                                            | CS                                                                     | ı            | Chip select in                                     | put. Equipped with internal pull-down resistor. When not controlled, must be connected to 0 V.                                                                                                                                                                                                                                                                                                                                                                                       | _                 |  |  |

|                                                               | TEST1                                                                  | 1            | Test input. Mu                                     | ust be connected to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                 |  |  |

| 17                                                            | EFMO                                                                   | 0            | For slice                                          | EFM signal output                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Undefined         |  |  |

| 18                                                            | EFMI                                                                   | ı            | level control                                      | EFM signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                 |  |  |

| 19                                                            | TEST2                                                                  | 1            | Test input. Ec                                     | uipped with internal pull-down resistor. Must be connected to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                   | _                 |  |  |

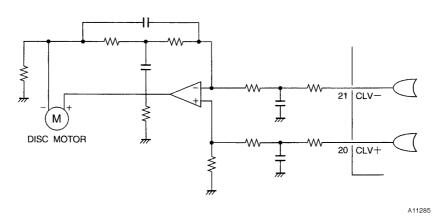

| 20                                                            | CLV <sup>+</sup>                                                       | 0            |                                                    | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |  |  |

| 21                                                            | CLV <sup>-</sup>                                                       | 0            | Disk motor co                                      | ntrol output. Can have a 3-state output depending on the command.                                                                                                                                                                                                                                                                                                                                                                                                                    | Low-level output  |  |  |

| 22                                                            | V/P                                                                    | 0            | "                                                  | ough servo/phase control automatic switching monitor output. If a high level then rough servo mode.  a low level then phase control mode.                                                                                                                                                                                                                                                                                                                                            |                   |  |  |

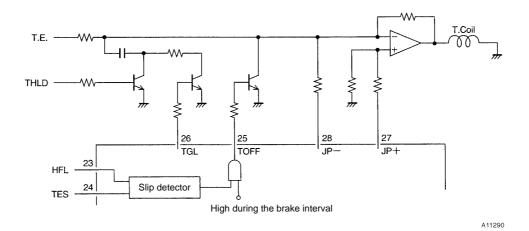

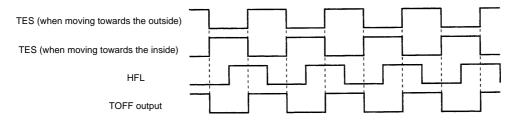

| 23                                                            | HFL                                                                    | 1            | Track detect s                                     | signal input. Schmidt input.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                 |  |  |

| 24                                                            | TES                                                                    | ı            | Tracking erro                                      | signal input. Schmidt input.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                 |  |  |

| 25                                                            | TOFF                                                                   | 0            | Tracking off o                                     | utput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | High-level output |  |  |

| 26                                                            | TGL                                                                    | 0            | Tracking gain                                      | switch output. Gain is increased with low level.                                                                                                                                                                                                                                                                                                                                                                                                                                     | Undefined         |  |  |

| 27                                                            | JP <sup>+</sup>                                                        | 0            |                                                    | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |  |  |

| 28                                                            | JP <sup>-</sup>                                                        | 0            | Track jump co                                      | ontrol output. Can be 3-state output depending on the command.                                                                                                                                                                                                                                                                                                                                                                                                                       | Low-level output  |  |  |

| 29                                                            | PCK                                                                    | 0            | EFM data pla                                       | yback clock monitor. 4.3218 MHz during phase lock.                                                                                                                                                                                                                                                                                                                                                                                                                                   | Low-level output  |  |  |

| 30                                                            | FSEQ                                                                   | 0            |                                                    | etect output. A high level when the sync signal detected from the EFM signal matches the erated sync signal.                                                                                                                                                                                                                                                                                                                                                                         | Undefined         |  |  |

| 31                                                            | V <sub>DD</sub>                                                        | Р            | Digital system                                     | power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                 |  |  |

| 32                                                            |                                                                        | I(I/O)       | this pin is low<br>connected to<br>only reset disa | input for initializing only the anti-shock control part (i.e. excluding the DSP part). Resets when level, and release the reset when this pin is high level. Tie this pin to the low level (i.e., 0 V) if when using software control on the anti-shock part alone through the anti-shock part able/release command (\$F4) or the anti-shock only reset enable/inrush command (\$F5). is assigned as the least significant bit of the general I/O port however, use as a general I/O | Input mode        |  |  |

| 33                                                            | ASRES                                                                  |              | pin is disabled                                    | d. When the port I/O set command (\$DB) is executed, the least significant bit is always "0," and ver is not turned ON.                                                                                                                                                                                                                                                                                                                                                              |                   |  |  |

Continued on next page.

# Continued from preceding page.

| Pin<br>No. | Pin<br>Name        | I/O |                         | Description                                                                                                                                                                                                                                                                  | Output pin states during reset |  |  |

|------------|--------------------|-----|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| 34         | CONT3/SBCK         | I/O | the subcode read clo    | General I/O pin 3. This controls the commands from the microcontroller. This pin is shared exclusively with he subcode read clock input (SBCK). When not used, either set this as an input port and connect to 0 V, or set this as an output port and leave it open.         |                                |  |  |

| 35         | CONT4/SFSY         | I/O | the subcode frame s     | eneral I/O pin 4. This controls the commands from the microcontroller. This pin is shared exclusively with e subcode frame sync signal output (SFSY). When not used, either set this as an input port and connect 0 V, or set this as an output port and leave it open.      |                                |  |  |

| 36         | CONT5/PW           | I/O | the subcode P, Q, R,    | eneral I/O pin 5. This controls the commands from the microcontroller. This pin is shared, exclusively, with a subcode P, Q, R, S, T, U, V, W output (PW). When not used, either set this as an input port and connect 0 V, or set this as an output port and leave it open. |                                |  |  |

| 37         | SBSY               | 0   | Subcode block sync      | signal output                                                                                                                                                                                                                                                                | Undefined                      |  |  |

| 38         | TEST3              | I   | Test input. Equipped    | with an internal pull-down resistor. Must be connected to 0 V.                                                                                                                                                                                                               | _                              |  |  |

| 39         | DOUT               | 0   | Digital output. EIAJ fo | ormat.                                                                                                                                                                                                                                                                       | Undefined                      |  |  |

| 40         | TEST4              | I   | Test input. Equipped    | with an internal pull-down resistor. Must be connected to 0 V.                                                                                                                                                                                                               | _                              |  |  |

| 41         | 16M/NGJ            | 0   |                         | at functions either as the 16.9344 MHz output (16M) or as the C2 flag data continuity check start is indicated by a low to high transition). Controlled by microcontroller commands.                                                                                         | Clock output                   |  |  |

| 42         | 4.2M               | 0   | 4.2336 MHz output       |                                                                                                                                                                                                                                                                              | Clock output                   |  |  |

| 43         | EFLG               | 0   | C1, C2, one error, tw   | o error error correction monitor output                                                                                                                                                                                                                                      | Undefined                      |  |  |

| 44         | FSX                | 0   | 7.35 kHz sync signal    | 35 kHz sync signal output (frequency divided from the crystal oscillator).                                                                                                                                                                                                   |                                |  |  |

| 45         | EMPH               | 0   | Deemphasis monitor      | eemphasis monitor output. When high level, a deemphasis disk is being played back.                                                                                                                                                                                           |                                |  |  |

| 46         | C2F                | 0   | C2 flag output          | 2 flag output                                                                                                                                                                                                                                                                |                                |  |  |

| 47         | TOUT               | 0   | Test output. Under no   | est output. Under normal operation, this should be left open.                                                                                                                                                                                                                |                                |  |  |

| 48         | MR1                | ı   | DRAM switch: high:      | RAM switch: high: 1M, low: 4M                                                                                                                                                                                                                                                |                                |  |  |

| 49         | MR2                | ı   |                         | M: high, low 4 M: low, low 16 M: low, high 4 M X 2: high, high (MR1, MR2)                                                                                                                                                                                                    |                                |  |  |

| 50         | TESD               | ı   | Test input. Must be c   | Test input. Must be connected to 0V.                                                                                                                                                                                                                                         |                                |  |  |

| 51         | MUTESL             | 0   |                         | L channel mute output                                                                                                                                                                                                                                                        | High-level output              |  |  |

| 52         | LV <sub>DD</sub>   | Р   |                         | L channel power supply                                                                                                                                                                                                                                                       | _                              |  |  |

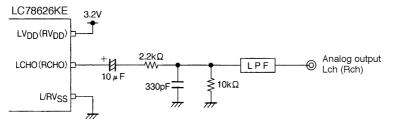

| 53         | LCHO               | AO  |                         | L channel output                                                                                                                                                                                                                                                             | _                              |  |  |

| 54         | L/RV <sub>SS</sub> | Р   | For the one-bit D/A     | L/R channel ground. Must be connected to 0 V.                                                                                                                                                                                                                                | _                              |  |  |

| 55         | RCHO               | AO  | converter               | R channel output                                                                                                                                                                                                                                                             | _                              |  |  |

| 56         | RV <sub>DD</sub>   | Р   |                         | R channel power supply                                                                                                                                                                                                                                                       | _                              |  |  |

| 57         | MUTER              | 0   |                         | R channel mute output                                                                                                                                                                                                                                                        | High-level output              |  |  |

| 58         | $XV_{DD}$          | Р   | Crystal oscillator pow  | ver supply                                                                                                                                                                                                                                                                   | _                              |  |  |

| 59         | XOUT               | 0   |                         |                                                                                                                                                                                                                                                                              |                                |  |  |

| 60         | XIN                | ı   | 16.9344 MHz crystal     | oscillator connection                                                                                                                                                                                                                                                        | _                              |  |  |

| 61         | XV <sub>SS</sub>   | Р   | Crystal oscillator grou | und. Must be connected to 0 V.                                                                                                                                                                                                                                               | _                              |  |  |

| 62         | RWC                | ı   | Read/write control in   |                                                                                                                                                                                                                                                                              | _                              |  |  |

| 63         | COIN               | ı   | Microcontroller comn    | nand input                                                                                                                                                                                                                                                                   | _                              |  |  |

| 64         | CQCK               | ı   |                         | mand input latch clock and the subcode readout clock. Schmitt input.                                                                                                                                                                                                         | _                              |  |  |

| 65         | SQOUT              | 0   | Subcode Q output        | ·                                                                                                                                                                                                                                                                            | Undefined                      |  |  |

| 66         | WRQ                | 0   | Subcode Q output sta    | andby output                                                                                                                                                                                                                                                                 | Undefined                      |  |  |

| 67         | FMT                | I   | Operating mode swit     | ch: high: shock proof, low: through.                                                                                                                                                                                                                                         | _                              |  |  |

| 68         | EMPP               | 0   |                         | P pulse is output when the DRAM is empty).                                                                                                                                                                                                                                   | Low-level output               |  |  |

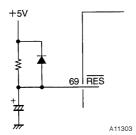

| 69         | RES                | 1   |                         | low reset (all internal blocks are reinitialized).                                                                                                                                                                                                                           | <u> </u>                       |  |  |

Continued on next page.

# Continued from preceding page.

| Pin<br>No. | Pin<br>Name     | I/O | Description                                                                                                                                                                                                                         | Output pin states during reset |

|------------|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 70         | MMC0            | 0   | Remaining DRAM output                                                                                                                                                                                                               | Low-level output               |

| 71         | MMC1            | 0   | Remaining DRAM output                                                                                                                                                                                                               | Low-level output               |

| 72         | MMC2            | 0   | Remaining DRAM output                                                                                                                                                                                                               | Low-level output               |

| 73         | MMC3            | 0   | Remaining DRAM output                                                                                                                                                                                                               | Low-level output               |

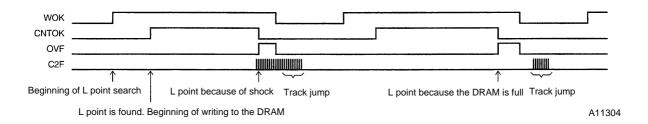

| 74         | OVF             | 0   | DRAM write terminated. (An RZP pulse is output when there is an overflow or a shock.)                                                                                                                                               | Low-level output               |

| 75         | CNTOK           | 0   | Data contact point detection complete signal: low→ high: detection complete. (DRAM write start).                                                                                                                                    | High-level output              |

| 76         | WOK             | ı   | DRAM write enable signal input: high: write enable.                                                                                                                                                                                 | _                              |

| 77         | PAUSE IN        | 1   | Pause signal input: high: pause.                                                                                                                                                                                                    | _                              |

| 78         | AD10/CAS2       | 0   | Shared function pin that functions either as a 16M DRAM address output (AD10) or as a DRAM control signal (CAS2) used when 8M of DRAM (two 4M DRAM chips) is used. The function is switched by the DRAM selection pins MR1 and MR2. | Undefined                      |

| 79         | EMPN            | 0   | Remaining DRAM alarm output: low: memory low.                                                                                                                                                                                       | Low-level output               |

| 80         | SHOCK           | 1   | C2F shock detect pause signal input: low: pause shock detection.                                                                                                                                                                    | _                              |

| 81         | DRAM3           | I/O | DRAM data bus                                                                                                                                                                                                                       | Input mode                     |

| 82         | DRAM2           | I/O | DRAM data bus                                                                                                                                                                                                                       | Input mode                     |

| 83         | DRAM1           | I/O | DRAM data bus                                                                                                                                                                                                                       | Input mode                     |

| 84         | DRAM0           | I/O | DRAM data bus                                                                                                                                                                                                                       | Input mode                     |

| 85         | ŌE              | 0   | DRAM control signal                                                                                                                                                                                                                 | Low-level output               |

| 86         | WE              | 0   | DRAM control signal                                                                                                                                                                                                                 | High-level output              |

| 87         | CAS             | 0   | DRAM control signal                                                                                                                                                                                                                 | Undefined                      |

| 88         | RAS             | 0   | DRAM control signal                                                                                                                                                                                                                 | Undefined                      |

| 89         | AD9             | 0   | DRAM address bus                                                                                                                                                                                                                    | Low-level output               |

| 90         | AD8             | 0   | DRAM address bus                                                                                                                                                                                                                    | Low-level output               |

| 91         | AD7             | 0   | DRAM address bus                                                                                                                                                                                                                    | Low-level output               |

| 92         | AD6             | 0   | DRAM address bus                                                                                                                                                                                                                    | Low-level output               |

| 93         | AD5             | 0   | DRAM address bus                                                                                                                                                                                                                    | Low-level output               |

| 94         | V <sub>SS</sub> | Р   | Digital system ground. Must be connected to 0 V.                                                                                                                                                                                    | _                              |

| 95         | AD4             | 0   | DRAM address bus                                                                                                                                                                                                                    | Low-level output               |

| 96         | AD3             | 0   | DRAM address bus                                                                                                                                                                                                                    | Low-level output               |

| 97         | AD2             | 0   | DRAM address bus                                                                                                                                                                                                                    | Low-level output               |

| 98         | AD1             | 0   | DRAM address bus                                                                                                                                                                                                                    | Undefined                      |

| 99         | AD0             | 0   | DRAM address bus                                                                                                                                                                                                                    | Undefined                      |

| 100        | $V_{DD}$        | Р   | Digital system power supply                                                                                                                                                                                                         | _                              |

# **Pin Applications**

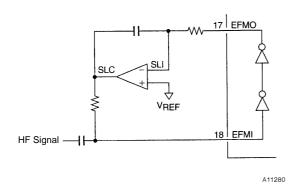

The HF Signal Input Circuit

Pin 18: EFMI, Pin 17: EFMO, Pin 1: DEFI, and Pin 20: CLV<sup>+</sup>

When an HF signal is input to the EFMI, an EFM signal (NRZ), sliced at the optimal levels, is obtained.

As a countermeasure against defects, when the DEFI pin (Pin 1) is high, the slice level control output EFMO pin (Pin 17) goes to a high impedance state, and the slice level is held. However, this is only enabled when the CLV is in phase-control mode, or in other words, when the V/P pin (Pin 22) is low. This can be structured from a combination with the DEF pin of LA9230/40/50 series ICs.

\* When the EFMI and CLV<sup>+</sup> signal lines are close to each other then the error rate due to unnecessary radiation may increase. It is recommended that these two lines be separated by a ground line or by a V<sub>DD</sub> line as a shield line.

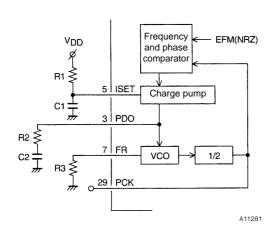

The PLL Clock Playback Circuit

Pin 3: PDO, Pin 5: ISET and Pin 7: FR

The VCO circuit is equipped internally, and the PLL circuit is structured using external resistors and external capacitors. The ISET is the reference current for the charge pump. The PDO is the loop filter for the VCO circuit, and the FR is the resistor that determines the frequency range of the VCO.

Reference Values

$$R1 = 68 \text{ k}\Omega \qquad \qquad C1 = 0.1 \text{ } \mu\text{F (standard speed)}$$

$$C1 = 0.047 \text{ } \mu\text{F (2} \times \text{speed)}$$

$$R2 = 680 \text{ } \Omega \qquad \qquad C2 = 0.1 \text{ } \mu\text{F}$$

$$R3 = 1.2 \text{ } k\Omega$$

\* It is recommended that a carbon coated resistor with a tolerance of ±5.0% be used for R3.

The VCO Monitor

Pin 29: PCK

This is the monitor pin with an average frequency of 4.3218 MHz, which is a 1/2 frequency division from VCO.

The Sync Detect Monitor Pin 30: FSEQ

The EFM signal goes high when the frame sync signal (the true sync signal) from the PCK matches the timing (the interpolated sync signal) generated by the counter. This serves as the sync detect monitor (holding the high level over a single frame).

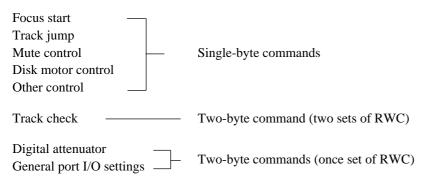

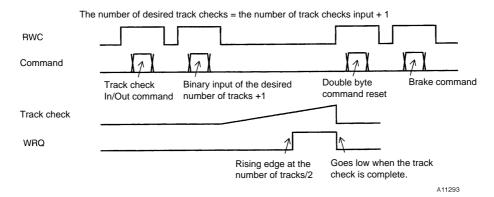

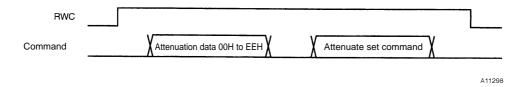

The Servo Command Functions Pin 62: RWC, Pin 63: COIN, Pin 64: CQCK

Various commands can be executed by setting RWC to high and by inputting the command from COIN synchronized with the CQCK clock. The commands are executed beginning with the falling edge of RWC.

· Single-byte commands

• Two-byte commands (RWC 2 set: for the track count)

• Two-byte commands (RWC 1 set: digital attenuation and setting the general I/O port)

A11284

• Eliminating command noise

| Code | COMMAND                                       | RES = low |

|------|-----------------------------------------------|-----------|

| \$EF | Command input noise reduction mode            |           |

| \$EE | Resets the command input noise reduction mode | 0         |

This command makes it possible to reduce the noise that is mixed into the  $\overline{CQCK}$  clock. This is effective for noise of less than 500 ns; however, the  $\overline{CQCK}$  timing must be set to have 1  $\mu s$  or more for  $t_{WL}$ ,  $t_{WH}$ , and  $t_{SU}$ .

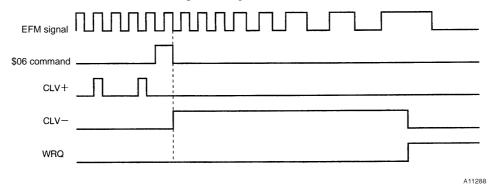

The CLV Servo Circuit Pin 20: CLV+, Pin 21: CLV-, Pin 22: V/P

| Code | COMMAND                       | RES = low |

|------|-------------------------------|-----------|

| \$04 | DISC MOTOR START (Accelerate) |           |

| \$05 | DISC MOTOR CLV (CLV)          |           |

| \$06 | DISC MOTOR BRAKE (Decelerate) |           |

| \$07 | DISC MOTOR STOP (Stop)        | 0         |

$CLV^+$  is the signal for accelerating the disk in the forward direction, while  $CLV^-$  is the signal for decelerating the disk. Depending on the commands from the microcontroller, one of the following four modes is selected: Accelerate, decelerate, CLV, or stop. The  $CLV^+$  and  $CLV^-$  outputs for each mode are as shown in the table below.

| MODE       | CLV <sup>+</sup> | CLV <sup>-</sup> |

|------------|------------------|------------------|

| Accelerate | High             | Low              |

| Decelerate | Low              | High             |

| CLV        | Pulse output     | Pulse output     |

| Stop       | Low              | Low              |

\* The CLV servo control command is such that the TOFF pin is low only when the CLV mode is in effect, and it is high otherwise. The TOFF pin control by the command is only active when the CLV mode is in effect.

# • CLV mode

In the CLV mode the rotation of the disk is detected from the HF signal, and a precise linear speed of rotation is derived by exerting the respective forms on control when the internal modes of the DSP change. The PWM frequency is 7.35 kHz. The  $V/\overline{P}$  has a high output when the internal mode is the rough servo, and a low output when the internal mode is phase control.

| Internal mode                                                    | CLV⁺ | CLV <sup>-</sup> | V/P  |

|------------------------------------------------------------------|------|------------------|------|

| Rough servo (when the rotational speed is determined to be low)  | High | Low              | High |

| Rough servo (when the rotational speed is determined to be high) | Low  | High             | High |

| Phase control (when the PCK clock is running)                    | PWM  | PWM              | Low  |

# • Switching the rough servo gain

| Code | COMMAND        | RES = low |

|------|----------------|-----------|

| \$A8 | DISC 8 cm Set  |           |

| \$A9 | DISC 12 cm Set | 0         |

When the internal mode is the rough servo, the CLV control gain for the 8 cm disk can be reduced by 8.5 dB from the level for the 12 cm disk.

# • Switching the phase control gain

| Code | COMMAND                                     | RES = low |

|------|---------------------------------------------|-----------|

| \$B1 | CLV phase comparator 1/2 frequency division |           |

| \$B2 | CLV phase comparator 1/4 frequency division |           |

| \$B3 | CLV phase comparator 1/8 frequency division |           |

| \$B0 | CLV phase comparator, no frequency division | 0         |

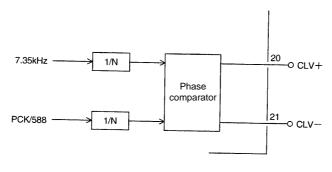

By changing the frequency division value of the first-stage frequency divider of the phase comparator it is possible to change the phase control gain.

A11286

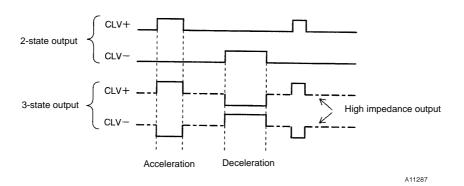

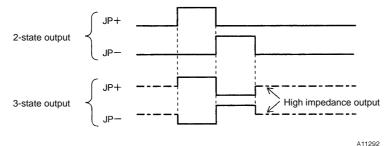

# • CLV 3-state output

| Code | COMMAND                                 | RES = low |

|------|-----------------------------------------|-----------|

| \$B4 | CLV 3-state output                      |           |

| \$B5 | CLV 2-state output (traditional method) | 0         |

The CLV 3-state output command makes it possible to control the CLV with a single pin. However, because this will cause the spindle gain to fall by 6 dB, it will be necessary to increase the gain on the servo side.

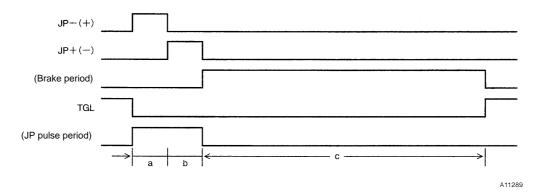

#### · Internal brake mode

| Code | COMMAND                              | RES = low |

|------|--------------------------------------|-----------|

| \$C5 | Internal Break ON                    |           |

| \$C4 | Internal Break OFF                   | 0         |

| \$A3 | Internal brake control               |           |

| \$CB | Internal brake continuous mode       |           |

| \$CA | Internal brake continuous mode reset | 0         |

| \$CD | Internal brake TON mode              |           |

| \$CC | Internal brake TON mode reset        | 0         |