# **Dot Matrix VFD Display Controller/Driver**

# **Preliminary**

#### Overview

The LC75710NE series products are dot matrix VFD controller/driver LSIs that display characters, numbers, and symbols. These LSIs generate dot matrix VFD drive signals based on serial data sent from a microprocessor, and allow display systems to be implemented easily using the built-in character generator ROM and RAM.

The LC75710NE series products are fabricated in a CMOS process and can contribute to achieving low-power operation in user applications.

#### **Features**

- 5 × 7 dot matrix VFD display controller/driver (Driver outputs can be connected directly to VFD devices: pull-down resistors are not required.)

- Display technique: Dynamic lighting technique

- Display digits: 1 to 16 digits (programmable)

- · Display control data

CGROM:  $5 \times 7$  dots, 160 characters CGRAM:  $5 \times 7$  dots, 8 characters

ADRAM: 16 × 8 bits DCRAM: 64 × 8 bits • Instruction functions Display on/off control Display shift

Display blink

Intensity adjustment (dimmer)

- Serial data input (DI, CL, and CE pins)

- Built-in reset circuit

- 64-pin flat package

# Differences between the LC75710NE, LC75711NE, and LC75712E

The data in the built-in character generator ROM (CGROM) differs between these products. All other functions are identical.

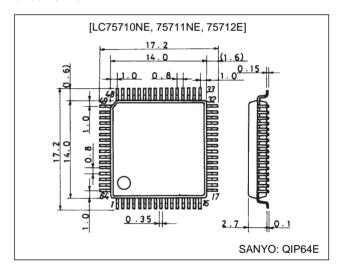

# **Package Dimensions**

unit: mm

#### 3159-QFP64E

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

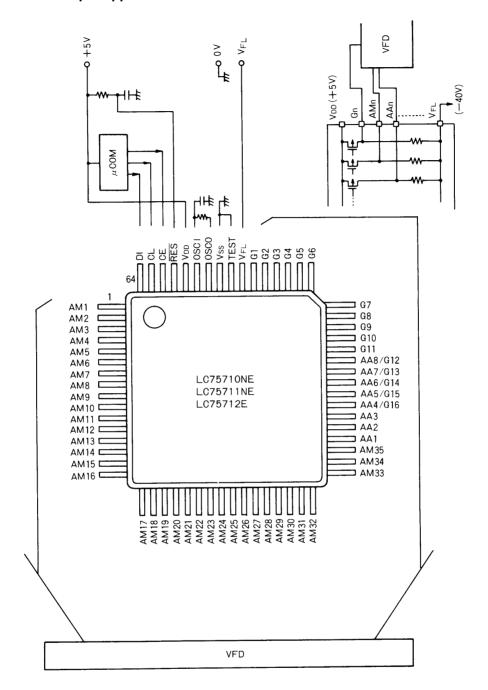

# Pin Assignment and Sample Application Circuit

# **Specifications**

# Absolute Maximum Ratings at $Ta=25^{\circ}C,\,V_{SS}=0~V$

| Parameter                   | Symbol              | Conditions                                                  | Ratings                                | Unit |

|-----------------------------|---------------------|-------------------------------------------------------------|----------------------------------------|------|

| Maximum aupply valtage      | V <sub>DD</sub> max | V <sub>DD</sub>                                             | -0.3 to +6.5                           | V    |

| Maximum supply voltage      | V <sub>FL</sub> max | V <sub>FL</sub>                                             | $V_{DD} - 55 \text{ to } V_{DD} + 0.3$ |      |

| lanut valtara               | V <sub>IN</sub> 1   | OSCI                                                        | -0.3 to V <sub>DD</sub> + 0.3          | V    |

| Input voltage               | V <sub>IN</sub> 2   | DI, CL, CE, RES                                             | -0.3 to +6.5                           | V    |

|                             | I <sub>OUT</sub> 1  | AM1 to AM35                                                 | 1                                      |      |

| Output current              | I <sub>OUT</sub> 2  | AA1 to AA3                                                  | 10                                     | mA   |

|                             | I <sub>OUT</sub> 3  | AA4 to AA8, G1 to G16                                       | 20                                     |      |

| Allowable power dissipation | Pd max              | Ta ≤ 85°C, with up to 70% of the AM1 to AM35 outputs driven | 400                                    | mW   |

| Operating temperature       | Topr                |                                                             | -40 to +85                             | °C   |

| Storage temperature         | Tstg                |                                                             | -50 to +125                            | °C   |

# Allowable Operating Ranges at $Ta=-40~to~+85^{\circ}C,\,V_{DD}=4.5~to~5.5~V,\,V_{SS}=0~V$

| Parameter                      | Symbol            | Conditions      | min                  | typ | max                 | Unit |

|--------------------------------|-------------------|-----------------|----------------------|-----|---------------------|------|

| Supply voltage                 | $V_{DD}$          | $V_{DD}$        | 4.5                  | 5.0 | 5.5                 | V    |

| Supply voltage                 | $V_{FL}$          | V <sub>FL</sub> | V <sub>DD</sub> – 50 |     | $V_{DD}$            | V    |

|                                | V <sub>IH</sub> 1 | DI, CL, CE      | 0.8 V <sub>DD</sub>  |     | 5.5                 |      |

| Input high level voltage       | V <sub>IH</sub> 2 | RES             | 0.7 V <sub>DD</sub>  |     | 5.5                 | V    |

|                                | V <sub>IH</sub> 3 | OSCI            | 0.7 V <sub>DD</sub>  |     | $V_{DD}$            |      |

| Input low level voltage        | V <sub>IL</sub> 1 | DI, CL, CE      | 0                    |     | 0.2 V <sub>DD</sub> | V    |

| input low level voltage        | V <sub>IL</sub> 2 | RES, OSCI       | 0                    |     | 0.3 V <sub>DD</sub> | V    |

| Guaranteed oscillator range    | fosc              | OSCI, OSCO      | 1.0                  | 2.7 | 3.5                 | MHz  |

| Recommended external resistor  | R <sub>OSC</sub>  | OSCI, OSCO      |                      | 10  |                     | kΩ   |

| Recommended external capacitor | Cosc              | OSCI, OSCO      |                      | 30  |                     | pF   |

| Minimum reset pulse width      | twres             | RES             | 1                    |     |                     | μs   |

| Low level clock pulse width    | t <sub>øL</sub>   | CL              | 0.5                  |     |                     | μs   |

| High level clock pulse width   | $t_{\phi H}$      | CL              | 0.5                  |     |                     | μs   |

| Data setup time                | t <sub>DS</sub>   | DI, CL          | 0.5                  |     |                     | μs   |

| Data hold time                 | t <sub>DH</sub>   | DI, CL          | 0.5                  |     |                     | μs   |

| CE wait time                   | t <sub>CP</sub>   | CE, CL          | 0.5                  |     |                     | μs   |

| CE setup time                  | t <sub>CS</sub>   | CE, CL          | 0.5                  |     |                     | μs   |

| CE hold time                   | t <sub>CH</sub>   | CE, CL          | 0.5                  |     |                     | μs   |

### **Electrical Characteristics within the Allowable Operating Ranges**

| Parameter                 | Symbol            | Conditions                                                                   | min                   | typ | max                  | Unit |

|---------------------------|-------------------|------------------------------------------------------------------------------|-----------------------|-----|----------------------|------|

| Input high level current  | I <sub>IH</sub>   | DI, CL, CE, RES, OSCI: Vi = 5.5 V                                            |                       |     | 5                    | μA   |

| Input low level current   | I <sub>IL</sub>   | DI, CL, CE, RES, OSCI: Vi = 0 V                                              | -5                    |     |                      | μΑ   |

|                           | V <sub>OH</sub> 1 | AM1 to AM35: $I_O = 1 \text{ mA}$                                            | V <sub>DD</sub> – 1.0 |     |                      |      |

| Output high level voltage | V <sub>OH</sub> 2 | AA1 to AA3: I <sub>O</sub> = 10 mA                                           | V <sub>DD</sub> – 1.0 |     |                      | V    |

| Output high level voltage | V <sub>OH</sub> 3 | AA4 to AA8, G1 to G16: I <sub>O</sub> = 20 mA                                | V <sub>DD</sub> – 2.0 |     |                      | V    |

|                           | V <sub>OH</sub> 4 | OSCO: I <sub>O</sub> = 0.5 mA                                                | V <sub>DD</sub> – 2.0 |     | $V_{DD}$             |      |

| Output low level voltage  | V <sub>OL</sub>   | OSCO: I <sub>O</sub> = -0.5 mA                                               | 0                     |     | 2.0                  | V    |

| Output off voltage        | V <sub>OFF</sub>  | AM1 to AM35, AA1 to AA8, G1 to G16: $V_{FL} = V_{DD} - 50 \text{ V}$         |                       |     | V <sub>DD</sub> – 49 | V    |

| Pull-down resistors       | R <sub>1</sub>    | AM1 to AM35: $V_{DD} - V_{FL} = 48 \text{ V}$                                | 140                   |     | 650                  | kΩ   |

| Full-down resistors       | R <sub>2</sub>    | AA1 to AA8, G1 to G16: $V_{DD} - V_{FL} = 48 \text{ V}$                      | 70                    |     | 325                  | K52  |

| Oscillator frequency      | fosc              | R = 10 kΩ, C = 30 pF                                                         | 2.16                  | 2.7 | 3.24                 | MHz  |

| Hysteresis voltage        | V <sub>H</sub>    | DI, CL, CE                                                                   | 0.5                   |     |                      | V    |

| Supply current            | I <sub>DD</sub>   | Outputs open, $f_{OSC} = 2.7 \text{ MHz}$ , $V_{FL} = V_{DD} - 50 \text{ V}$ |                       |     | 5                    | mA   |

Note: Since this IC incorporates high voltage ports it is easily damaged by static discharges. Therefore, extra care is required when handling this IC.

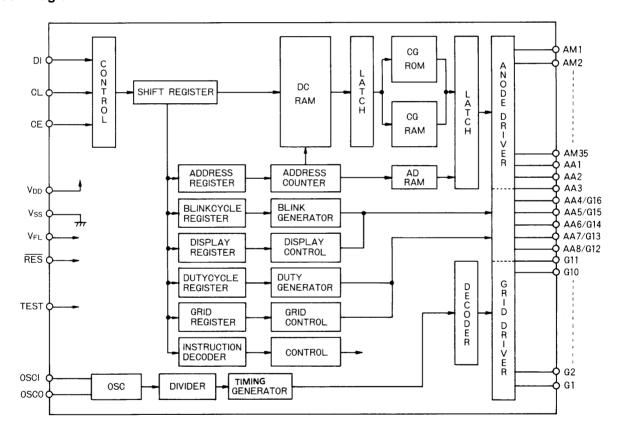

#### **Block Diagram**

### **Pin Functions**

| Pin                                                 | No.         | Pin circuit     | Function                                                                                                                                                                                                               |

|-----------------------------------------------------|-------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>                                     | 1           |                 | Logic block power supply: +5 V (typical)                                                                                                                                                                               |

| V <sub>SS</sub>                                     | 1           |                 | Logic block power supply: ground                                                                                                                                                                                       |

| V <sub>FL</sub>                                     | 1           |                 | Driver block power supply                                                                                                                                                                                              |

| DI<br>CL<br>CE                                      | 1<br>1<br>1 |                 | Serial data interface DI: Transfer data CL: Synchronization clock CE: Chip enable                                                                                                                                      |

| OSCI<br>OSCO                                        | 1 1         | 0SC1 0SC0       | External oscillator RC circuit connections                                                                                                                                                                             |

| RES                                                 | 1           |                 | System reset input                                                                                                                                                                                                     |

| AM1 to AM35<br>AA1 to AA3                           | 38          | Vpo             | Anode outputs Pull-down resistors are built in.                                                                                                                                                                        |

| AA4/G16<br>AA5/G15<br>AA6/G14<br>AA7/G13<br>AA8/G12 | 5           |                 | Anode/grid outputs These pins function as grid output pins when the number of displayed digits is selected to be between 12 and 16 digits with the "Grid register load" instruction. Pull-down resistors are built in. |

| G1 to G11                                           | 11          | V <sub>FL</sub> | Grid outputs Pull-down resistors are built in.                                                                                                                                                                         |

| TEST                                                | 1           |                 | LSI testing This pin must be connected to $V_{\mbox{\scriptsize SS}}$ during normal operation.                                                                                                                         |

#### **Block Functions**

#### 1. AC (address counter)

AC is a counter that provides addresses for DCRAM and ADRAM.

The address is modified automatically by internal operations to maintain the VFD display state.

#### 2. DCRAM (data control RAM)

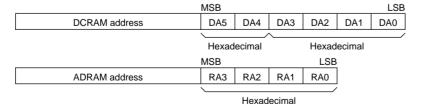

DCRAM is RAM that holds the display data, which is expressed as 8-bit character codes. (These character codes are converted to  $5 \times 7$  dot matrix patterns using the CGROM and CGRAM memories.) DCRAM has a capacity of  $64 \times 8$  bits, and can hold the data for 64 characters. The relationship between the 6-bit DCRAM address in AC and the display position on the VFD display is described below.

• When the DCRAM address in AC is 00<sub>H</sub>. (16 digits displayed)

| Display digit               | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  |

|-----------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| DCRAM address (hexadecimal) | 0F | 0E | 0D | 0C | 0B | 0A | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

However, the DCRAM address moves as follows when a display shift is performed by specifying MDATA.

| Display digit               | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | Right shift |

|-----------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------------|

| DCRAM address (hexadecimal) | 10 | 0F | 0E | 0D | 0C | 0B | 0A | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | Right Shift |

|                             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |             |

| Display digit               | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | Left shift |

|-----------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------------|

| DCRAM address (hexadecimal) | 0E | 0D | 0C | 0B | 0A | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 | 3F | Len Silli  |

Note: The 6-bit DCRAM addresses are expressed in hexadecimal.

#### 3. ADRAM (additional data RAM)

ADRAM is RAM used to store ADATA display data. ADRAM has a  $16 \times 8$ -bit capacity and the stored display data is output directly without using CGROM and CGRAM. The relationship between the 4-bit ADRAM address in AC and the display position on the VFD display is described below.

• When the ACRAM address in AC is 0<sub>H</sub>. (16 digits displayed)

| Display digit               | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|-----------------------------|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|

| ADRAM address (hexadecimal) | F  | Е  | D  | С  | В  | Α  | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

However, the ADRAM address moves as follows when a display shift is performed by specifying ADATA.

| Display digit               | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | Diaht ahift |

|-----------------------------|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-------------|

| ADRAM address (hexadecimal) | 0  | F  | Е  | D  | С  | В  | Α  | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | Right shift |

| Display digit               | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | Left shift |

|-----------------------------|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|------------|

| ADRAM address (hexadecimal) | Е  | D  | С  | В  | Α  | 9  | 8  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | F | Left shift |

Note: DCRAM and ADRAM addresses are expressed in hexadecimal.

Example: When the DCRAM address is 3E<sub>H</sub>.

| DA5 | DA4 | DA3 | DA2 | DA1 | DA0 |  |

|-----|-----|-----|-----|-----|-----|--|

| 1   | 1   | 1   | 1   | 1   | 0   |  |

4. CGROM (character generator ROM)

CGROM is ROM that is used to generate the 160 different  $5 \times 7$  dot matrix character patterns. It has a capacity of  $160 \times 35$  bits. When 8-bit character codes are written to DCRAM, the CGROM character pattern corresponding to this 8-bit character code is displayed at the VFD display position corresponding to the DCRAM address in AC. Tables 3 to 5 show the correspondence between the character codes and the character patterns.

5. CGRAM (character generator RAM)

CGRAM is RAM to which user programs can write arbitrary data. Up to eight  $5 \times 7$  dot matrix character patterns can be stored in the CGRAM. CGRAM has a capacity of  $8 \times 35$  bits.

To display a character pattern stored in CGRAM, write one of the character codes shown at the left of tables 3 to 5 to DCRAM. The CGRAM character pattern will be displayed at the VFD position corresponding to the DCRAM address in AC.

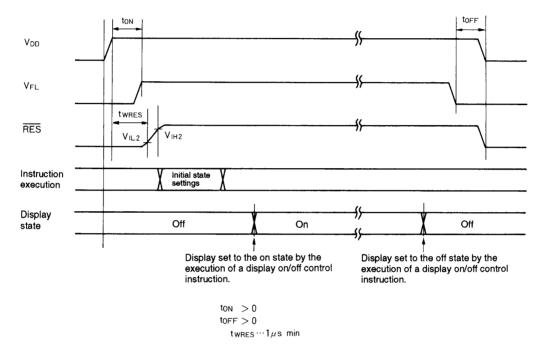

#### **Reset Function**

The LC75710NE series accepts a reset when a low level is applied to the  $\overline{RES}$  pin. On a reset the LC75710NE series creates a display with all VFD lamps turned off. However, note that the values in DCRAM, ADRAM, and CGRAM, as well as the values of the duty cycle register (intensity) and the grid register (number of digits) are undefined following a reset. Therefore, before turning on display with a display on/off control instruction, these values must be initialized. In particular, the following instructions must be executed when power is first applied.

- · Display blink

- · DCRAM data write

- ADRAM data write (if ADRAM is used)

- CGRAM data write (if CGRAM is used)

- · Set AC address

- · Grid register load

- Intensity adjustment (dimmer)

Initial state settings

After executing the above instructions the display must be turned on by executing a "Display on/off control" instruction.

Note that incorrect display may occur if the number of displayed digits and the intensity are not set up in advance. This can occur in cases where a display on/off control instruction is executed before the grid register load and intensity adjustment instructions are executed. To prevent this problem, always execute the following three instructions together as a single set.

- · Grid register load

- Intensity adjustment (dimmer)

- · Display on/off control

#### **Data Input**

1. Serial control data consists of an 8-bit address and a 24-bit instruction. The address is used as a chip select function when multiple ICs are connected to the same bus. The table shows the address for the LC75710NE series.

|    |    |    | Add | ress |    |    |    |

|----|----|----|-----|------|----|----|----|

| В0 | B1 | B2 | В3  | A0   | A1 | A2 | А3 |

| 1  | 1  | 1  | 0   | 0    | 1  | 1  | 0  |

Note: Only one instruction, the "CGRAM data write" instruction, consists of 56 bits. See Table 1 for instruction code details.

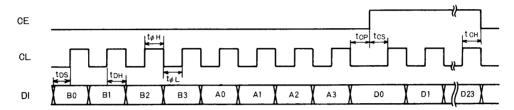

2. DI, CL, CE signal timing

Data is acquired on the rising edge of the CL signal and latched on the falling edge of the CE signal. When the microprocessor sends multiple instructions to the LC75710NE series, it must wait long enough for the LC75710NE series to complete the execution of each instruction before sending the next instruction.

Table 1 Instruction Table

|                                   |                 |                                             | Code                             |                                |                                                                              | Execution time |

|-----------------------------------|-----------------|---------------------------------------------|----------------------------------|--------------------------------|------------------------------------------------------------------------------|----------------|

| Instruction                       | D23 D22 D21 D20 | D23 D22 D21 D20 D19 D18 D17 D16 D15 D14 D13 | D15 D14 D13 D12 D11 D10 D9 D8 D7 | D7 D6 D5 D4 D3 D2 D1 D0        | Description                                                                  | (maximum)*3    |

| Display blink                     | 1 0 1           | A Blink cycle data                          | Grid                             | O                              | Blinks the display. Me 1: ADATA specification, A = 1: ADATA specification *1 | 18 µs          |

| Display on/off control            | 0 0 0 1         | 0                                           | Grid                             | O                              | Turns the display on or off.<br>O = 1: Display on, O = 0: Display off        | 18 µs          |

| Display shift                     | 0 1 0           | * M A R/L                                   | * * *                            | * * *                          | Shifts the display.<br>R/L = 1: Left shift, R/L = 0: Right shift             | 18 µs          |

| Grid register load                | 0 0 1 1         | Grid<br>number data                         | * * * * * * *                    | * * * * * * *                  | Sets the number of digits displayed according to the grid number data.       | srl 0          |

| Set AC address                    | 0 1 0 0         | ADRAM<br>address                            | * BOCRAM address                 | * * *                          | Loads a DCRAM and ADRAM address into AC (address counter).                   | 18 µs          |

| Intensity adjustment (dimmer) 0 1 | 0 1 0 1         | * * *                                       | Duty cycle<br>data               | * * * * * * *                  | Adjusts the VFD intensity according to the duty cycle data.                  | srl 0          |

| DCRAM data write                  | 0 1 1 0         | * * *                                       | * BOCRAM address                 | Write data<br>(character code) | Specifies the DCRAM (data control RAM) address and writes data.              | 18 µs          |

| ADRAM data write                  | 0 1 1 1         | ADRAM<br>address                            | ADATA                            | * * * * * * *                  | Specifies the ADRAM (additional data RAM) address and writes data.           | 18 µs          |

| CGRAM data write                  | 1 0 0 0         | * *                                         | CGRAM<br>address                 | Write data*2                   | Specifies the CGRAM (character generator RAM) address and writes data.       | 18 µs          |

|                                   |                 |                                             |                                  |                                |                                                                              |                |

\*: Don't care. Note: 1. MDATA MDATA

2. The table below shows the structure of the CGRAM data write instruction.

|      | → D0                    |                      |  |

|------|-------------------------|----------------------|--|

|      |                         | Write data           |  |

|      | $\downarrow$            |                      |  |

|      | D34                     |                      |  |

|      | D35                     | *                    |  |

|      | D36                     | *                    |  |

|      | D37 D36                 | *                    |  |

|      | D38                     | *                    |  |

|      | D39 D38                 | *                    |  |

|      | D40                     |                      |  |

| Code | D45 D44 D43 D42 D41 D40 | SS                   |  |

|      | D43                     | <b>CGRAM</b> address |  |

|      | D44                     | <b>SRAM</b>          |  |

|      | D45                     | $\mathcal{S}$        |  |

|      | D46 I                   |                      |  |

|      | D47                     |                      |  |

|      | D50 D49 D48 D47         | *                    |  |

|      | D49                     | *                    |  |

|      | D20                     | *                    |  |

|      | D51                     | *                    |  |

|      | D52                     | 0                    |  |

|      | D53                     | 0                    |  |

|      | D54                     | 0                    |  |

|      | D55                     | 1                    |  |

3.  $f_{OSC} = 2.7 \text{ MHz}$

#### **Detailed Instruction Descriptions**

1. Display blink ......<Blinks the display.>

|     |     |     |     |     |     |     |     |     |     |     | Co  | de  |     |     |    |    |    |    |    |    |    |    |    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1   | 0   | 1   | М   | Α   | BC2 | BC1 | BC0 | G16 | G15 | G14 | G13 | G12 | G11 | G10 | G9 | G8 | G7 | G6 | G5 | G4 | G3 | G2 | G1 |

#### M, A: Data that specifies the blinking operation

| М | Α | Display operating state         |

|---|---|---------------------------------|

| 0 | 0 | Neither MDATA nor ADATA blinks. |

| 0 | 1 | Only ADATA blinks.              |

| 1 | 0 | Only MDATA blinks.              |

| 1 | 1 | Both ADATA and MDATA blink.     |

#### BC0 to BC2: Blink period setting

| BC2 | BC1 | BC0 | HEX | Blink Period (s)*1<br>(when f <sub>OSC</sub> is 2.7 MHz) |

|-----|-----|-----|-----|----------------------------------------------------------|

| 0   | 0   | 0   | 0   | Blink operation is stopped.                              |

| 0   | 0   | 1   | 1   | 0.1                                                      |

| 0   | 1   | 0   | 2   | 0.2                                                      |

| 0   | 1   | 1   | 3   | 0.3                                                      |

| 1   | 0   | 0   | 4   | 0.4                                                      |

| 1   | 0   | 1   | 5   | 0.5                                                      |

| 1   | 1   | 0   | 6   | 0.8                                                      |

| 1   | 1   | 1   | 7   | 1.0                                                      |

#### G1 to G16: Blinking digit specification

Each bit Gn (where n is an integer between 1 and 16) specifies that blinking be applied to grid output pin Gn when the corresponding bit Gn is 1.

This instruction is used to specify the blinking operation. Not only can an arbitrary digit be specified, but MDATA and ADATA can also be specified. There are also seven blinking periods.

Note: 1. When the blinking period needs to be controlled precisely the display should be blinked by repeatedly turning the display on and off using the display on/off control instruction.

#### 2. Display on/off control......<br/>Turns the display on or off.>

|     |     |     |     |     |     |     |     |     |     |     | Co  | de  |     |     |    |    |    |    |    |    |    |    |    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0   | 0   | 0   | 1   | *   | М   | Α   | 0   | G16 | G15 | G14 | G13 | G12 | G11 | G10 | G9 | G8 | G7 | G6 | G5 | G4 | G3 | G2 | G1 |

<sup>\*:</sup> Don't care.

#### M, A: Specifies the data to be turned on or off.

| М | Α | Display operating state        |

|---|---|--------------------------------|

| 0 | 0 | Both MDATA and ADATA turn off. |

| 0 | 1 | Only ADATA turns on.           |

| 1 | 0 | Only MDATA turns on.           |

| 1 | 1 | Both ADATA and MDATA turn on.  |

#### O: On/off control

|   | 0 | Display state |

|---|---|---------------|

|   | 0 | Off           |

| Ī | 1 | On            |

When the display is turned off with an O value of 0, the data can be displayed immediately with an O value of 1 since the display data remains in DCRAM.

G1 to G16: Display digit specification

Each bit Gn (where n is an integer between 1 and 16) specifies that the corresponding grid output pin Gn be turned on when that bit (Gn) is 1.

This instruction is used to specify the display on/off control operation. Not only can an arbitrary digit be specified, but MDATA and ADATA can also be specified.

3. Display shift ......<Shifts the display.>

|     |     |     |     |     |     |     |     |     |     |     | Co  | ode |     |    |    |    |    |    |    |    |    |    |    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0   | 0   | 1   | 0   | *   | М   | Α   | R/L | *   | *   | *   | *   | *   | *   | *  | *  | *  | *  | *  | *  | *  | *  | *  | *  |

<sup>\*:</sup> Don't care.

#### M, A: Specifies the data to be shifted.

| М | Α | Shift operating state                |

|---|---|--------------------------------------|

| 0 | 0 | Neither MDATA nor ADATA are shifted. |

| 0 | 1 | Only ADATA is shifted.               |

| 1 | 0 | Only MDATA is shifted.               |

| 1 | 1 | Both MDATA and ADATA are shifted.    |

#### R/L: Shift direction specification

| R/L | Shift direction |

|-----|-----------------|

| 0   | Right shift     |

| 1   | Left shift      |

4. Grid register load ......< Specifies the number of digits displayed.>

|     |     |     |     |     |     |     |     |     |     |     | Co  | de  |     |    |    |    |    |    |    |    |    |    |    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0   | 0   | 1   | 1   | GN3 | GN2 | GN1 | GN0 | *   | *   | *   | *   | *   | *   | *  | *  | *  | *  | *  | *  | *  | *  | *  | *  |

<sup>\*:</sup> Don't care.

#### GN0 to GN3: Displayed digits specification

| GN3 | GN2 | GN1 | GN0 | HEX | Digits Controlled |

|-----|-----|-----|-----|-----|-------------------|

| 0   | 0   | 0   | 0   | 0   | G1 to G16         |

| 0   | 0   | 0   | 1   | 1   | G1                |

| 0   | 0   | 1   | 0   | 2   | G1 to G2          |

| 0   | 0   | 1   | 1   | 3   | G1 to G3          |

| 0   | 1   | 0   | 0   | 4   | G1 to G4          |

| 0   | 1   | 0   | 1   | 5   | G1 to G5          |

| 0   | 1   | 1   | 0   | 6   | G1 to G6          |

| 0   | 1   | 1   | 1   | 7   | G1 to G7          |

| 1   | 0   | 0   | 0   | 8   | G1 to G8          |

| 1   | 0   | 0   | 1   | 9   | G1 to G9          |

| 1   | 0   | 1   | 0   | Α   | G1 to G10         |

| 1   | 0   | 1   | 1   | В   | G1 to G11         |

| 1   | 1   | 0   | 0   | С   | G1 to G12         |

| 1   | 1   | 0   | 1   | D   | G1 to G13         |

| 1   | 1   | 1   | 0   | Е   | G1 to G14         |

| 1   | 1   | 1   | 1   | F   | G1 to G15         |

The AA4/G16, AA5/G15, AA6/G14, AA7/G13, and AA8/G12 anode/grid output pins function as grid output pins if between 12 and 16 digits are selected. Also, this instruction must be executed prior to turn the display on since the value of the grid register is undefined immediately after power is applied.

|     |     |     |     |     |     |     |     |     |     |     | Co  | de  |     |     |     |    |    |    |    |    |    |    |    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0   | 1   | 0   | 0   | RA3 | RA2 | RA1 | RA0 | *   | *   | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 | *  | *  | *  | *  | *  | *  | *  | *  |

<sup>\*:</sup> Don't care.

DA0 to DA5: DCRAM address

DA0.....LSB (least significant bit)

DA5.....MSB (most significant bit)

RA0 to RA3: ADRAM address

RA0.....LSB RA3.....MSB

This instruction loads the 6-bit DA0 to DA5 DCRAM address and the 4-bit RA0 to RA3 ADRAM address into AC.

6. Intensity adjustment ......<Adjusts the VFD intensity.>

|     |     |     |     |     |     |     |     |     |     |     | Co  | de  |     |     |     |    |    |    |    |    |    |    |    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0   | 1   | 0   | 1   | *   | *   | *   | *   | DC7 | DC6 | DC5 | DC4 | DC3 | DC2 | DC1 | DC0 | *  | *  | *  | *  | *  | *  | *  | *  |

<sup>\*:</sup> Don't care.

DC0 to DC7: Duty cycle data (intensity adjustment data)

DC0.....LSB

DC7.....MSB

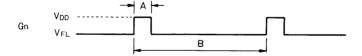

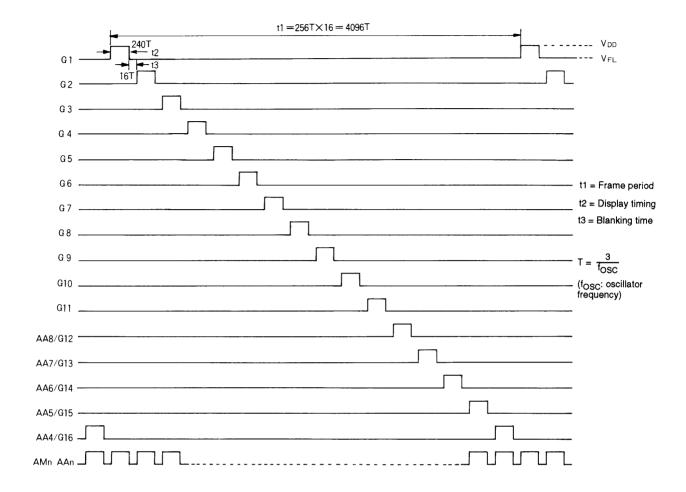

The data in the 8 bits DC0 to DC7 sets the VFD intensity to one of 240 levels. Since the value in the duty cycle register is undefined immediately after power is applied, the display intensity is not determined at that point. Therefore, applications must execute this instruction before turning on the display. Applications can adjust the intensity using the duty cycle register and grid register. The duty cycle register value sets the pulse width (A) and the grid register value sets the period (B). See Figure 3 for the grid timing chart details.

|     |     |     |     |     |     |     |     |     |     |     | Co  | de  |     |     |     |     |     |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 1   | 1   | 0   | *   | *   | *   | *   | *   | *   | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

<sup>\*:</sup> Don't care.

DA0 to DA5: DCRAM address

DA0.....LSB DA5.....MSB

AC0 to AC7: DCRAM write data (character code)

AC0.....LSB AC7.....MSB

This instruction writes the 8 bits of data AC0 to AC7 to DCRAM. This data is a character code (see Tables 3 to 5) and is converted to  $5 \times 7$  dot matrix display data using CGROM and CGRAM.

|     |     |     |     |     |     |     |     |     |     |     | Co  | de  |     |     |     |    |    |    |    |    |    |    |    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0   | 1   | 1   | 1   | RA3 | RA2 | RA1 | RA0 | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | *  | *  | *  | *  | *  | *  | *  | *  |

<sup>\*:</sup> Don't care.

RA0 to RA3: ADRAM address

RA0.....LSB RA3.....MSB

AD1 to AD8: ADATA display data

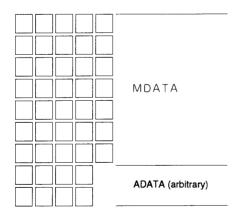

There are 8 bits of additional display data, referred to as ADATA, in addition to the  $5 \times 7$  dot matrix of display data (MDATA). This data is used to generate arbitrary dot patterns without using CGROM or CGRAM. The figures show the correspondence between these data types. In particular, when ADn = 1 (where n is an integer between 1 and 8), the dot AAn will be turned on.

| ADATA | Corresponding output pin |

|-------|--------------------------|

| AD1   | AA1                      |

| AD2   | AA2                      |

| AD3   | AA3                      |

| AD4   | AA4/G16                  |

| AD5   | AA5/G15                  |

| AD6   | AA6/G14                  |

| AD7   | AA7/G13                  |

| AD8   | AA8/G12                  |

9. CGRAM data write ......Specifies the CGRAM address and stores data at that address.>

|     |     |     |     |     |     |     | Co  | ode |     |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D55 | D54 | D53 | D52 | D51 | D50 | D49 | D48 | D47 | D46 | D45 | D44 | D43 | D42 | D41 | D40 |

| 1   | 0   | 0   | 0   | *   | *   | *   | *   | CA7 | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 |

|     |     |     |     |     |      |      | Co   | ode  |      |      |      |      |      |      |      |

|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|------|------|------|------|

| D39 | D38 | D37 | D36 | D35 | D34  | D33  | D32  | D31  | D30  | D29  | D28  | D27  | D26  | D25  | D24  |

| *   | *   | *   | *   | *   | CD35 | CD34 | CD33 | CD32 | CD31 | CD30 | CD29 | CD28 | CD27 | CD26 | CD25 |

|      |      |      |      |      |      |      | Co   | ode  |      |      |      |      |      |      |     |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|

| D23  | D22  | D21  | D20  | D19  | D18  | D17  | D16  | D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8  |

| CD24 | CD23 | CD22 | CD21 | CD20 | CD19 | CD18 | CD17 | CD16 | CD15 | CD14 | CD13 | CD12 | CD11 | CD10 | CD9 |

|     |     |     | Co  | de  |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| CD8 | CD7 | CD6 | CD5 | CD4 | CD3 | CD2 | CD1 |

\*: Don't care.

CA0 to CA7: CGRAM address

CA0.....LSB CA7.....MSB

CD1 to CD35: CGRAM write data (5 × 7 dot matrix display data)

The bit CDn (where n is an integer between 1 and 35), corresponds to the AMn dot display data. The figure below shows the positional relationship for this display data.

| <b>AM</b> 1 | AM2          | AM3  | AM 4         | AM5  |

|-------------|--------------|------|--------------|------|

| <b>AM</b> 6 | AM 7         | AM 8 | AM 9         | AM10 |

| AM11        | AM12         | AM13 | AM14         | AM15 |

| AM16        | AM17         | AM18 | <b>AM</b> 19 | AM20 |

| AM21        | <b>AM</b> 22 | AM23 | AM24         | AM25 |

| AM26        | AM27         | AM28 | <b>AM</b> 29 | AM30 |

| AM31        | AM32         | AM33 | AM34         | AM35 |

#### **Usage Notes**

#### 1. Power supply sequence

The sequences shown below must be followed when turning the power supply on and off. (See Figure 1.) Power on: Logic block power supply  $(V_{DD})$  on  $\rightarrow$  Driver block power supply  $(V_{FL})$  on  $\rightarrow$  Display on (by the execution of a display on/off control instruction)

Power off: Display off (by the execution of a display on/off control instruction)  $\rightarrow$  Driver block power supply  $(V_{FL})$  off  $\rightarrow$  Logic block power supply  $(V_{DD})$  off

Fig. 1 Power Supply Sequence

#### 2. Anode output pins

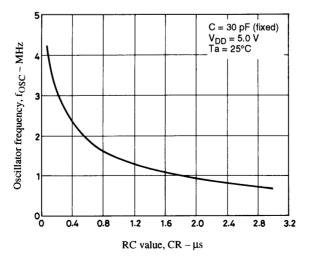

The anode output pins AM1 to AM35 are used as the anode outputs that form the  $5 \times 7$  dot matrix due to output current considerations. We recommend using the anode output pins AA1 to AA8 for other anode output functions. If the anode waveform is distorted and the VFD glows slightly (smearing) due to the VFD panel used or wiring considerations, try using a lower oscillator frequency. Refer to Figure 2 when determining the oscillator frequency.

Fig. 2 Oscillator Frequency

Fig. 3 Grid Timing Chart (16 display digits)

# Table 2 Instruction/Display Correspondence (LC75710NE)

| No.     | Instruction (hexadecimal)                           | Display  | Operation                                                 |

|---------|-----------------------------------------------------|----------|-----------------------------------------------------------|

| 1       | Power application (Initialization with the RES pin) |          | Initializes the IC. The display will be in the off state. |

| 2       | DCRAM data write 6 * 0 0 2 0                        |          | Writes display data "" to DCRAM address 00H.              |

| 3       | DCRAM data write 6 * 0 1 4 F                        |          | Writes display data "O" to DCRAM address 01H.             |

| 4       | DCRAM data write 6 * 0 2 5 9                        |          | Writes display data "Y" to DCRAM address 02H.             |

| 5       | DCRAM data write 6 * 0 3 4 E                        |          | Writes display data "N" to DCRAM address 03H.             |

| 6       | DCRAM data write 6 * 0 4 4 1                        |          | Writes display data "A" to DCRAM address 04H.             |

| 7       | DCRAM data write 6 * 0 5 5 3                        |          | Writes display data "S" to DCRAM address 05H.             |

| 8       | DCRAM data write 6 * 0 6 2 0                        |          | Writes display data "" to DCRAM address 06H.              |

| 9       | DCRAM data write<br>6 * 0 7 2 0                     |          | Writes display data "" to DCRAM address 07H.              |

| 10      | DCRAM data write 6 * 3 D 4 9                        |          | Writes display data "I' to DCRAM address 3DH.             |

| 11      | DCRAM data write 6 * 3 E 5 3                        |          | Writes display data "S" to DCRAM address 3EH.             |

| 12      | DCRAM data write 6 * 3 F 4 C                        |          | Writes display data "L" to DCRAM address 3FH.             |

| 13      | Grid register load                                  |          | Specifies that the display has 8 digits.                  |

| 14      | Intensity adjustment 5 * F F * *                    |          | Sets the VFD intensity to the maximum.                    |

| 15      | Display on/off control                              | SANYO    | Turns on the VFD for only the digits G1 to G8 in MDATA.   |

| 16      | Display shift 2 5 * * * *                           | SANYOL   | Shifts the display (MDATA only) to the left.              |

| 17      | Display shift 2 5 * * * *                           | SANYO LS | Shifts the display (MDATA only) to the left.              |

| 18      | Display shift 2 5 * * * *                           | ANYO LSI | Shifts the display (MDATA only) to the left.              |

| 19      | Set AC address                                      | SANYO    | Returns the display to the original state.                |

| * Don't |                                                     |          |                                                           |

<sup>\*</sup> Don't care

Note: The example above assumes the use of an 8 digit  $5 \times 7$  dot matrix VFD, and CGRAM and ADRAM are not used.

Table 3 LC75710NE CGROM (Version for use in USA and Japan)

| Lower  | Upper<br>4 bits | MSB<br>0 0 0 0 | 0.0 | 1 0 | 0 0 | 1 1 | <u>n</u> 1 | 0 0                             | η 1 | 0 1 | <u>η</u> 1 | 1 0 | <sub>በ 1</sub> | 1 1 | 1 ∩      | 1 0 | 1 N | 1 1 | 1 1 | 0 0 | 1 1 | 0 1 |

|--------|-----------------|----------------|-----|-----|-----|-----|------------|---------------------------------|-----|-----|------------|-----|----------------|-----|----------|-----|-----|-----|-----|-----|-----|-----|

| 4 bits |                 |                | 0 0 | -   |     |     | υI         |                                 | U I | -   | U 1        |     | U 1            |     | 1 0      | . 1 | 1 0 |     |     |     | - 1 |     |

| 0 0    | 0 0<br>LSB      | CG<br>RAM(1)   |     |     |     |     | @          |                                 | Р   |     | \          |     | р              |     |          |     | _   |     | タ   |     | 111 |     |

| 0 0    | 0 1             | (2)            | !   |     | 1   |     | А          | 000<br>000<br>000<br>000<br>000 | Q   |     | а          |     | q              |     | 0        |     | ア   |     | チ   |     | Д   |     |

| 0 0    | 1 0             | (3)            | ,,  |     |     |     | В          |                                 | R   |     | b          |     | r              |     | Γ        |     | 1   |     | ツ   |     | ×   |     |

| 0 0    | 1 1             | (4)            | #   |     | 3   |     | С          |                                 | S   |     | С          |     | S              |     | J        |     | ゥ   |     |     |     | Ŧ   |     |

| 0 1    | 0 0             | (5)            | \$  |     | 4   |     | D          |                                 | Т   |     | d          |     | t              |     | `        |     | エ   |     | 7   |     | ヤ   |     |

| 0 1    | 0 1             | (6)            | %   |     | ) 5 |     | E          |                                 | U   |     | е          |     | u              |     |          |     | オ   |     | t   |     | ュ   |     |

| 0 1    | 1 0             | (7)            | &   |     | 6   |     | F          |                                 | V   |     | f          |     | V              |     | ヲ        |     | カ   |     |     |     | ∋   |     |

| 0 1    | 1 1             | (8)            | ,   |     | 7   |     | G          |                                 | W   |     | g          |     | W              |     | ア        |     | ‡   |     | ヌ   |     | ラ   |     |

| 1 0    | 0 0             |                | (   |     | 8   |     | Н          |                                 | X   |     | h          |     | X              |     | 1        |     | ク   |     | ネ   |     | リ   |     |

| 1 0    | 0 1             |                | )   |     | 9   |     | 1          |                                 | Υ   |     | i          |     | У              |     | ウ        |     | ケ   |     | 1   |     | ル   |     |

| 1 0    | 1 0             |                | *   |     |     |     | J          |                                 | Z   |     | j          |     | Z              |     | I        |     |     |     | Л   |     | レ   |     |

| 1 0    | 1 1             |                | +   |     | ;   |     | Κ          |                                 | (   |     | k          |     | {              |     | <b>オ</b> |     | サ   |     | Ł   |     |     |     |

| 1 1    | 0 0             |                | ,   |     | <   |     | L          |                                 | ¥   |     | I          |     | 1              |     | ャ        |     | シ   |     |     |     | ワ   |     |

| 1 1    | 0 1             |                |     |     | =   |     | М          |                                 | )   |     | m          |     | }              |     | ユ        |     | ス   |     | <   |     | ン   |     |

| 1 1    | 1 0             | :              | •   |     | >   |     | 2          |                                 | ^   |     | n          |     | <b>→</b>       |     | 3        |     | セ   |     | ホ   |     | ž   |     |

| 1 1    | 1 1             |                | /   |     | ?   |     | 0          |                                 | _   |     | 0          |     | <b>←</b>       |     | ツ        |     | ソ   |     | マ   |     | ٥   |     |

Note: The character pattern (output data) is undefined if the character codes 00001000<sub>B</sub> to 00011111<sub>B</sub>, 100000000<sub>B</sub> to 10011111<sub>B</sub>, or 111000000<sub>B</sub> to 111111111<sub>B</sub> are written to DCRAM.

Table 4 LC75711NE CGROM (Version for use in Europe)

| Upper<br>4 bits | MSB          |     |                                                            |     |                                                       |     |                                           |     |                                                      |     |                                              |     |                                                             |     |                                                            |     |                                                    |               |                                                      |     |                                                               |

|-----------------|--------------|-----|------------------------------------------------------------|-----|-------------------------------------------------------|-----|-------------------------------------------|-----|------------------------------------------------------|-----|----------------------------------------------|-----|-------------------------------------------------------------|-----|------------------------------------------------------------|-----|----------------------------------------------------|---------------|------------------------------------------------------|-----|---------------------------------------------------------------|

| Lower<br>4 bits | 0000         | 0 0 |                                                            | 0 0 | 1 1                                                   | 0 1 | 0 0                                       | 0 1 | 0 1                                                  | 0 1 | 1 0                                          | 0 1 | 1 1                                                         | 1 0 |                                                            | 1 0 | 0 1                                                | 1 0           | 1 0                                                  | 1 0 |                                                               |

| 0 0 0 0<br>LSB  | CG<br>RAM(1) |     | 00000<br>00000<br>00000<br>00000<br>00000<br>00000<br>0000 | 0   |                                                       | @   |                                           | Р   | 0000<br>0000<br>0000<br>0000<br>0000<br>0000         |     |                                              | р   |                                                             | á   |                                                            | â   |                                                    | <u>a</u>      |                                                      | 0   | 01100<br>0300<br>9300<br>9300<br>9300<br>9300<br>9000<br>9000 |

| 0001            | (2)          | !   |                                                            | 1   |                                                       | А   |                                           | Q   |                                                      | а   |                                              | q   |                                                             | à   |                                                            | ä   |                                                    | α             | 00000<br>00000<br>00000<br>00000<br>00000<br>00000   | Φ   |                                                               |

| 0010            | (3)          | ,,  |                                                            | 2   |                                                       | В   |                                           | R   |                                                      | b   |                                              | r   | 00000<br>00000<br>00000<br>00000<br>00000<br>00000          | é   | 00000<br>00000<br>00000<br>00000<br>00000<br>00000<br>0000 | ê   | 00000<br>00000<br>00000<br>00000<br>00000          | Ö             | 0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000 | ã   |                                                               |

| 0011            | (4)          | #   |                                                            | 3   |                                                       | С   |                                           | S   |                                                      | С   | 00000<br>00000<br>00000<br>00000<br>00000    | S   |                                                             | è   |                                                            | ë   |                                                    | Å             |                                                      | å   |                                                               |

| 0100            | (5)          | }{  |                                                            | 4   |                                                       | D   |                                           | T   |                                                      | d   |                                              | t   |                                                             | ĺ   |                                                            | î   |                                                    | <b>&gt;</b> G |                                                      | +   |                                                               |

| 0 1 0 1         | (6)          | %   |                                                            | 5   |                                                       | E   | 0000<br>0000<br>0000<br>0000<br>0000      | U   | 0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000 | е   | 00000<br>00000<br>00000<br>00000<br>00000    | u   | 00000<br>00000<br>0000<br>0000<br>0000<br>0000              | ì   |                                                            | ï   |                                                    | <b>&gt;</b> e |                                                      | İ   |                                                               |

| 0110            | (7)          | &   |                                                            | 6   |                                                       | F   | 0000<br>0000<br>0000<br>0000<br>0000      | V   | 0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000 | f   |                                              | ٧   | 03000<br>03000<br>03000<br>03000<br>00000<br>00000<br>00000 | ó   |                                                            | ô   |                                                    | ) <u>C</u>    |                                                      | ń   |                                                               |

| 0 1 1 1         | (8)          | ,   | 0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000       | 7   |                                                       | G   |                                           | W   |                                                      | g   |                                              | w   |                                                             | ò   |                                                            | ö   |                                                    | Æ             |                                                      | æ   |                                                               |

| 1000            |              | (   |                                                            | 8   |                                                       | Н   |                                           | X   |                                                      | h   | 0000<br>0000<br>0000<br>0000<br>0000<br>0000 | ×   |                                                             | ú   |                                                            | û   | 00000<br>00000<br>00000<br>00000<br>00000          | π             | 00000<br>00000<br>00000<br>00000<br>00000            | μ   | 00000<br>00000<br>00000<br>0000<br>0000                       |

| 1001            |              | )   |                                                            | 9   |                                                       | I   |                                           | Υ   |                                                      | i   |                                              | У   | 00000                                                       | ù   |                                                            | ü   |                                                    | Œ             |                                                      | ¿   |                                                               |

| 1010            |              | *   |                                                            | :   | 00000<br>00000<br>00000<br>00000<br>00000             | J   |                                           | Z   |                                                      | j   |                                              | Z   |                                                             | Ñ   |                                                            | ñ   |                                                    | £             |                                                      | ÷   | 00000<br>00000<br>00000<br>00000<br>00000                     |

| 1011            |              | +   |                                                            | ;   | 00000<br>00000<br>00000<br>00000<br>00000             | K   |                                           | (   |                                                      | k   |                                              | {   |                                                             | Ç   | 00000<br>00000<br>00000<br>00000<br>00000<br>00000         | ç   | 00000<br>00000<br>00000<br>00000<br>00000<br>00000 | \$            |                                                      | сe  |                                                               |

| 1100            |              | ,   | 00000<br>00000<br>00000<br>00000<br>00000<br>00000         | <   |                                                       | L   | 00000<br>00000<br>00000<br>00000<br>00000 | \   | 00000<br>00000<br>0000<br>00000<br>00000<br>00000    | l   |                                              |     |                                                             | Ş   |                                                            | ş   | D0000<br>D0000<br>D0000<br>D0000<br>B0000<br>D0000 | •             | 00000<br>00000<br>00000<br>00000<br>00000<br>00000   | φ   |                                                               |

| 1 1 0 1         |              | _   | 00000<br>00000<br>00000<br>00000<br>00000                  | =   | 00000                                                 | M   |                                           | )   |                                                      | m   |                                              | }   |                                                             | ß   |                                                            | ğ   |                                                    | †             | 00000<br>00000<br>00000<br>00000<br>00000<br>00000   | Ω   |                                                               |

| 1110            |              |     | 00000<br>00000<br>00000<br>00000<br>00000                  | >   | 50000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000 | N   |                                           | ٨   | 5000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000 | n   | 00000<br>00000<br>00000<br>00000<br>00000    | _   | 00000<br>00000<br>00000<br>00000<br>00000                   | i   |                                                            | 1   |                                                    | <b>→</b>      | 00000                                                | Σ   |                                                               |

| 1 1 1 1         |              | /   | 00000<br>00001<br>00000<br>00000<br>00000<br>00000         | ?   |                                                       | 0   |                                           |     | 00000<br>00000<br>00000<br>00000<br>00000            | 0   |                                              |     | 20124<br>20024<br>20024<br>20024<br>20024                   | IJ  |                                                            | Ä   |                                                    | ţ             |                                                      | §   |                                                               |

Note: The character pattern (output data) is undefined if the character codes  $00001000_B$  to  $00011111_B$  or  $11000000_B$  to  $11111111_B$  are written to DCRAM.

Table 5 LC75712E CGROM (Version for use in Europe)

| Upper<br>4 bits | MSB          |   |                                                             |     |     |     |                                      |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----------------|--------------|---|-------------------------------------------------------------|-----|-----|-----|--------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Lower<br>4 bits | 0000         |   | 1 0                                                         | 0 0 | 1 1 | 0 1 | 0 0                                  | 0 1 | 0 1 | 0 1 | 1 0 | 0 1 | 1 1 | 1 0 | 0 0 | 1 0 | 0 1 | 1 0 | 1 0 | 1 0 | 1 1 |

| 0 0 0 0<br>LSB  | CG<br>RAM(1) |   | 00000<br>00000<br>00000<br>00000<br>00000<br>00000<br>0000  | 0   |     | @   |                                      | Р   |     | II  |     | р   |     | á   |     | Ä   |     | Á   |     | Ã   |     |

| 0001            | (2)          | ! |                                                             | 1   |     | Α   |                                      | Q   |     | а   |     | q   |     | à   |     | ä   |     | À   |     | ã   |     |

| 0010            | (3)          | " |                                                             | 2   |     | В   |                                      | R   |     | b   |     | r   |     | é   |     | Ë   |     | É   |     | Å   |     |

| 0011            | (4)          | # |                                                             |     |     | С   |                                      | S   |     | С   |     | S   |     | è   |     | ë   |     | È   |     | å   |     |

| 0100            | (5)          |   |                                                             | 4   |     | D   |                                      | Т   |     | d   |     | t   |     | í   |     | Ϊ   |     | Í   |     | Æ   |     |

| 0101            | (6)          | % |                                                             | 5   |     | E   | 0000<br>0000<br>0000<br>0000<br>0000 | U   |     | е   |     | u   |     | ì   |     | ï   |     | Ì   |     | æ   |     |

| 0110            | (7)          | & |                                                             | 6   |     | F   |                                      | V   |     | f   |     | V   |     | ó   |     | Ö   |     | Ó   |     | Œ   |     |

| 0 1 1 1         | (8)          | , | 00000<br>00000<br>00000<br>00000<br>00000<br>00000          | 7   |     | G   |                                      | W   |     | 8   |     | W   |     | ò   |     | Ö   |     | Ò   |     | ce  |     |

| 1000            |              | ( |                                                             | 8   |     | Н   |                                      | X   |     | h   |     | X   |     | ú   |     | Ü   |     | Ú   |     | õ   |     |

| 1 0 0 1         |              | ) |                                                             | 9   |     | I   |                                      | Υ   |     | i   |     | У   |     | ù   |     | ü   |     | Ù   |     | õ   |     |

| 1010            |              | * |                                                             | •   |     | J   |                                      | Z   |     | j   |     | Z   |     | Ñ   |     | ñ   |     | £   |     | ÷   |     |

| 1011            |              | + |                                                             | ;   |     | K   |                                      | (   |     | k   |     | {   |     | Ç   |     | Ç   |     | \$  |     | 0   |     |

| 1100            |              | , | 00000<br>00000<br>00000<br>00000<br>00000<br>00 <b>0</b> 00 | <   |     | L   |                                      | \   |     | 1   |     | 1   |     | π   |     | +   |     | •   |     | Φ   |     |

| 1 1 0 1         |              | _ |                                                             | =   |     |     |                                      | )   |     | m   |     | }   |     | ß   |     | μ   |     | †   |     | φ   |     |

| 1110            |              |   | 00000<br>00000<br>00000<br>00000<br>00000<br>00000          | >   |     | Ν   |                                      | ^   |     | n   |     | _   |     | i   |     | ن   |     | -+  |     | +   |     |

| 1 1 1 1         |              | / |                                                             | ?   |     | 0   |                                      | _   |     | 0   |     |     |     | IJ  |     | ij  |     | ţ   |     | §   |     |

Note: 1. The character pattern (output data) is undefined if the character codes 00001000<sub>B</sub> to 00011111<sub>B</sub> or 11000000<sub>B</sub> to 111111111<sub>B</sub> are written to DCRAM.

<sup>2.</sup> Both the LC75711NE and the LC75712E are for use in the European market. These products differ in that the LC75712E CGROM takes handling a 5 × 8 dot matrix into consideration. In particular, this product allows the AA1 to AA5 anode output pins to be used to form a 5 × 8 dot matrix artificially, with the combination of AM1 to AM35 and AA1 to AA5. Adopting this structure allows applications to provide improved display quality for European characters, especially those requiring an umlaut.

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any and all SANYO products described or contained herein fall under strategic products (including services) controlled under the Foreign Exchange and Foreign Trade Control Law of Japan, such products must not be exported without obtaining export license from the Ministry of International Trade and Industry in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of August, 1998. Specifications and information herein are subject to change without notice.