# LC74FCT16425T, 74FCT162245T

## Fast 16-Bit CMOS Bidirectional Transceiver

## Overview

The LC74FCT16245T and LC74FCT162245T 16-bit transceivers are fabricated in an advanced two-metal-layer CMOS technology. These fast, low-power transceivers are optimal for synchronous communication between two buses, referred to as the A and B busses. The directionality and output enable control in these products is designed to allow them to be used as either two independent 8-bit transceivers or as a single 16-bit transceiver. The direction control pin (× DIR) controls the data flow direction and the output enable pin (×  $\overline{\text{OE}}$ ) disables directionality control and disables both ports.

The LC74FCT16245T is optimal for driving large-capacitance loads and low-impedance loads.

The LC74FCT162245T provides a balanced output drive function that incorporates current limiting resistors. These minimize ground bounce and undershoot, and limit the output fall time. As a result, external series terminating resistors are no longer required.

The LC74FCT162245T is a plug-in replacement for the LC74FCT16245T in on-board interface applications.

#### **Features**

- 0.8 µm CMOS technology

- Fast, low-power CMOS replacement products for use in ABT function applications

- ESD tolerance > 2000 V; MIL-STD-883 (when tested with the 3015 method)

- ESD tolerance > 200 V; For a machine model with C = 200 pF and R = 0  $\Omega$

- Bidirectional data transfer

- 20 mil center SQFP

- Expanded temperature range: -40 to +85°C

- $V_{CC} = 5 V \pm 10\%$

#### LC74FCT16245T Features

• High drive output levels (I<sub>OH</sub>: -32 mA, I<sub>OL</sub>: 40 mA)

#### LC74FCT162245T Features

- Balanced output drive: ±24 mA

- Reduced system switching noise

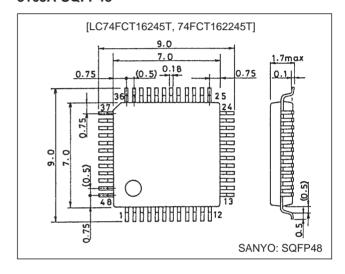

# **Package Dimensions**

unit: mm

#### 3163A-SQFP48

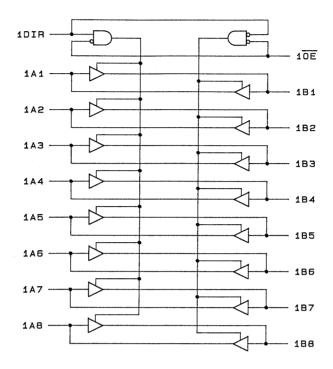

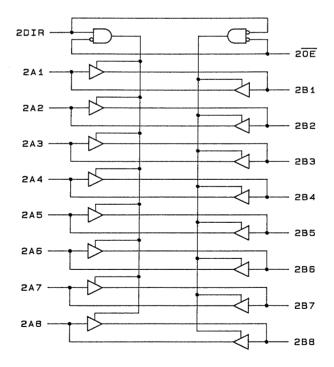

# **Function Block Diagram**

A02708

A02709

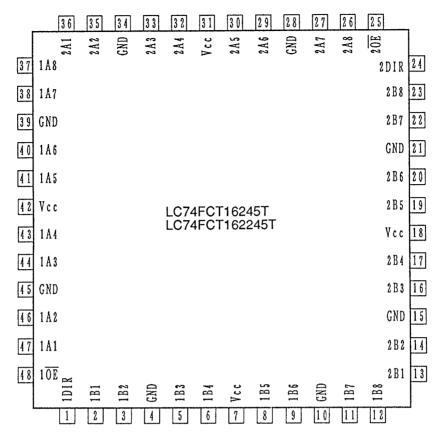

#### **Pin Functions**

| Pin             | Function                           |  |  |  |  |  |

|-----------------|------------------------------------|--|--|--|--|--|

| × <del>OE</del> | Output enable input (active low)   |  |  |  |  |  |

| × DIR           | Direction control input            |  |  |  |  |  |

| ×AX             | A side input or three-state output |  |  |  |  |  |

| ×BX             | B side input or three-state output |  |  |  |  |  |

# **Specifications**

# Absolute Maximum Ratings\*1

| Parameter                        | Symbol               | Conditions | Ratings                       | Unit |

|----------------------------------|----------------------|------------|-------------------------------|------|

| Pin voltage referenced to GND    | V <sub>TERM</sub> *2 |            | -0.5 to +7.0                  | V    |

| Pin voltage referenced to GND    | V <sub>TERM</sub> *3 |            | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| Operating temperature            | Topr                 |            | -40 to +85                    | °C   |

| Temperature when bias is applied | T <sub>BIAS</sub>    |            | -55 to +125                   | °C   |

| Storage temperature              | Tstg                 |            | -55 to +125                   | °C   |

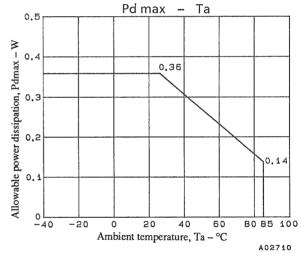

| Power dissipation                | P <sub>T</sub>       |            | *4                            | W    |

| DC output current                | I <sub>OUT</sub>     |            | -60 to +60                    | mA   |

- Note: 1. Applying stresses in excess of the absolute maximum ratings may permanently damage the device. The values specified here are stress ratings only, and do not refer to operation under conditions outside either these conditions or the operating conditions. Operating for extended periods at the absolute maximum ratings may adversely influence device reliability. Unless otherwise specified, pin voltages must not exceed V CC + 0.5 V.

- 2. All pins except the FCT162xxxT output and I/O pins

- 3. All FCT162xxxT output and I/O pins

- 4. See Figure 1.

#### **Function Truth Table\***

| Inp             | out  | Output                     |  |

|-----------------|------|----------------------------|--|

| × <del>OE</del> | ×DIR | Output                     |  |

| L               | L    | Bus B data output to bus A |  |

| L               | Н    | Bus A data output to bus B |  |

| Н               | ×    | High-impedance state.      |  |

Note: \* H = High level L = Low level X = Don't care

Figure 1

# Capacitances (Ta = 25°C)

| Parameter*        | Symbol           | Conditions | min | typ | max | Unit |

|-------------------|------------------|------------|-----|-----|-----|------|

| Input capacitance | C <sub>IN</sub>  |            |     | 5.5 | 8.0 | pF   |

| I/O capacitance   | C <sub>I/O</sub> |            |     | 4.5 | 6.0 | pF   |

Note: \* These capacitance values are logic values, and are not tested.

## LC74FCT16245T, 74FCT162245T

## **DC Electrical Characteristics in the Operating Ranges** The following conditions apply unless otherwise specified.

Ta = -40 to  $+85^{\circ}$ C,  $V_{CC}$  = +5.0 V  $\pm$  10%

| Parameter                             | Symbol                                                       | Conditions*                                 |                      | min            | typ  | max | Unit |  |

|---------------------------------------|--------------------------------------------------------------|---------------------------------------------|----------------------|----------------|------|-----|------|--|

| Input high level voltage              | V <sub>IH</sub>                                              | Logic high level guaranteed                 |                      | 2.0            |      |     | V    |  |

| Input low level voltage               | V <sub>IL</sub>                                              | Logic low level guaranteed                  |                      |                |      | 0.8 | V    |  |

| Input high level current (input pins) |                                                              |                                             |                      |                |      | ±5  |      |  |

| Input high level current (I/O pins)   | I <sub>IH</sub>                                              | V <sub>CC</sub> = max                       |                      | $V_I = V_{CC}$ |      |     | ±15  |  |

| Input low level current (input pins)  |                                                              |                                             | V CND                |                |      | ±5  | μA   |  |

| Input low level current (I/O pins)    |                                                              |                                             | V <sub>I</sub> = GND |                |      | ±15 |      |  |

| Quiescent current                     | I <sub>CCL</sub> ,<br>I <sub>CCH</sub> ,<br>I <sub>CCZ</sub> | $V_{CC} = max$ , $V_{IN} = GND$ or $V_{CC}$ |                      |                | 0.05 | 1.5 | mA   |  |

Note: \* Values stipulated in the electrical characteristics for the corresponding product must be used for the test conditions for the maximum and minimum values.

## LC74FCT16245T Output Drive Characteristics

| Parameter                 | Symbol          | Conditions*1                                                                |                                | min | typ*2 | max  | Unit |

|---------------------------|-----------------|-----------------------------------------------------------------------------|--------------------------------|-----|-------|------|------|

|                           |                 |                                                                             | $I_{OH} = -3 \text{ mA}$       | 2.5 | 3.5   |      | V    |

| Output high level voltage | V <sub>OH</sub> | $V_{CC} = min, V_{IN} = V_{IH} or V_{IL}$                                   | I <sub>OH</sub> = -15 mA       | 2.4 | 3.5   |      | V    |

|                           |                 |                                                                             | $I_{OH} = -32 \text{ mA}^{*3}$ | 2.0 | 3.0   |      | V    |

| Output low level voltage  | V <sub>OL</sub> | V <sub>CC</sub> = min, V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OL</sub> = 40 mA        |     | 0.2   | 0.55 | V    |

Note: 1. Values stipulated in the electrical characteristics for the corresponding product must be used for the test conditions for the maximum and minimum

- Typical values are values for V<sub>CC</sub> = 5.0 V, and an ambient temperature of +25°C.

The test time must not exceed 1 second.

# LC74FCT162245T Output Drive Characteristics

| Parameter                 | Symbol           | Conditions*1                                                                             |                                | min | typ*2 | max  | Unit |

|---------------------------|------------------|------------------------------------------------------------------------------------------|--------------------------------|-----|-------|------|------|

| Output low level current  | I <sub>ODL</sub> | $V_{CC} = 5 \text{ V}, V_{IN} = V_{IH} \text{ or } V_{IL}, V_{OUT} = 1.5 \text{ V}^{*3}$ |                                | 60  | 115   | 150  | mA   |

| Output high level current | I <sub>ODH</sub> | $V_{CC} = 5 \text{ V}, V_{IN} = V_{IH} \text{ or } V_{IL}, V_{OUT} = 1.5 \text{ V}^{*3}$ |                                | -60 | -115  | -150 | mA   |

| Output high level voltage | V <sub>OH</sub>  | V <sub>CC</sub> = min, V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>              | $I_{OH} = -24 \text{ mA}^{*4}$ | 2.4 | 3.3   |      | V    |

| Output low level voltage  | V <sub>OL</sub>  | $V_{CC} = min, V_{IN} = V_{IH} or V_{IL}$                                                | I <sub>OL</sub> = 24 mA        |     | 0.3   | 0.55 | V    |

Note: 1. Values stipulated in the electrical characteristics for the corresponding product must be used for the test conditions for the maximum and minimum

- Typical values are values for V<sub>CC</sub> = 5.0 V, and an ambient temperature of +25°C.

Do not test more than one output at a time. The test time must not exceed 1 second.

The test time must not exceed 1 second.

#### LC74FCT16245T, 74FCT162245T

#### **Power Supply Current Characteristics**

| Parameter                               | Symbol           | Conditions*1                                                                                              |                                                              | min | typ*2 | max                | Unit   |

|-----------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|-------|--------------------|--------|

| Quiescent current high-level TTL inputs | Δl <sub>CC</sub> | $V_{CC} = max, V_{IN} = 3.4 V^{*3}$                                                                       |                                                              |     | 0.5   | 1.5                | μА     |

| Operating supply current*4              | I <sub>CCD</sub> | V <sub>CC</sub> = max, outputs open,<br>× OE = × DIR = GND,<br>toggling a single input,<br>50% duty cycle | V <sub>IN</sub> = V <sub>CC</sub> ,<br>V <sub>IN</sub> = GND |     | 100   | 160                | μΑ/MHz |

|                                         |                  | $V_{CC}$ = max, outputs open,<br>fi = 10 MHz, $\times \overline{OE}$ = $\times$ DIR = GND,                | $V_{IN} = V_{CC},$<br>$V_{IN} = GND$                         |     | 0.7   | 2.5                |        |

| Total supply current*6                  |                  | toggling a single bit,<br>50% duty cycle                                                                  | $V_{IN} = 3.4 \text{ V},$<br>$V_{IN} = \text{GND}$           |     | 0.9   | 3.3                | mA.    |

| Total supply current                    | l <sub>C</sub>   | $V_{CC}$ = max, outputs open,<br>fi = 2.5 MHz, $\times \overline{OE}$ = $\times$ DIR = GND,               | $V_{IN} = V_{CC},$<br>$V_{IN} = GND$                         |     | 2.5   | 5.5 <sup>*5</sup>  | IIIA   |

|                                         |                  | toggling a 16 bits,<br>50% duty cycle                                                                     | V <sub>IN</sub> = 3.4 V,<br>V <sub>IN</sub> = GND            |     | 6.5   | 17.5 <sup>*5</sup> |        |

- Note: 1. Values stipulated in the electrical characteristics for the corresponding product must be used for the test conditions for the maximum and minimum

- 2. Typical values are values for  $V_{CC}$  = 5.0 V, and at an ambient temperature of +25°C. 3. For the TTL drive inputs ( $V_{IN}$  = 3.4 V), connect all the other inputs to  $V_{CC}$  or GND.

- 4. Although this parameter cannot be directly measured, it is provided for calculating the total power dissipation.

- 5. The values for these conditions are values with respect to the I<sub>CC</sub> rating. Although these values are guaranteed, they are not tested.

- 6. Ic + Iquiescent + Inputs + Ipynamic Ic + Iquiescent + Iquiescent + Iquiescent + Iquiescent + Iquiescent + Iquiescent Ct-ICC +  $\Delta$ IcC +

- D<sub>H</sub> = Duty cycle for the high-level TTL inputs

- $N_T$  = The number of TTL inputs in  $D_H$   $I_{CCD}$  = Operating current due to input transition pairs (HLH or LHL)

- f<sub>CP</sub> = Clock frequency for register devices (zero for non-register devices)

- $N_{CP}$  = The number of clocks input in  $f_{CP}$

- fi = Input frequency

- Ni = The number of inputs in fi.

#### LC74FCT16245T/162245T Switching Characteristics in the Operating Ranges

| Parameter                                                            | Symbol                                      | Conditions*1                            | min | typ | max  | Unit |

|----------------------------------------------------------------------|---------------------------------------------|-----------------------------------------|-----|-----|------|------|

| Transmission delay (From A to B or from B to A)                      | t <sub>PLH</sub> ,<br>t <sub>PHL</sub>      |                                         | 1.5 |     | 7.0  | ns   |

| Output enable time (From $\times$ $\overline{OE}$ to A or B)         | t <sub>PZH</sub> *1,<br>t <sub>PZL</sub> *1 |                                         | 1.5 |     | 12.0 | ns   |

| Output disable time (From $\times$ $\overline{\text{OE}}$ to A or B) | t <sub>PHZ</sub> *1,<br>t <sub>PLZ</sub> *1 | $C_1 = 50 \text{ pF}, R_1 = 500 \Omega$ | 1.5 |     | 7.5  | ns   |

| Output enable time (From × DIRS to A or B*3)                         | t <sub>PZH</sub> *2,<br>t <sub>PZL</sub> *2 |                                         | 1.5 |     | 9.5  | ns   |

| Output disable time (From × DIRS to A or B*3)                        | t <sub>PHZ</sub> *2,<br>t <sub>PLZ</sub> *2 |                                         | 1.5 |     | 7.5  | ns   |

| Output skew*4                                                        | t <sub>SK</sub> (O)                         |                                         |     |     | 0.5  | ns   |

- Note: 1. See the figures for the test circuit and waveforms.

- 2. Although the minimum values are guaranteed, the transmission delay is not tested.

- 3. Although these items are guaranteed, they are not tested.

- 4. The skew between two outputs in the same package switched in the same direction. This parameter is a design guarantee.

## **Pin Assignment**

Top view

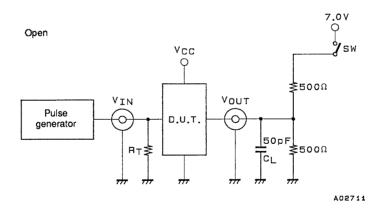

## **Test Circuit and Waveform Diagrams**

## **Test Circuit for All Outputs**

## **Switch Positions**

| Test                                                  | Switch |

|-------------------------------------------------------|--------|

| Open drain,<br>Disable low level,<br>Enable low level | Closed |

| All other tests                                       | Open   |

Definitions:  $C_L$  = Load capacitance: including the jig and probe capacitances

R<sub>T</sub> = Terminating resistance: equivalent to the pulse generator's Zout.

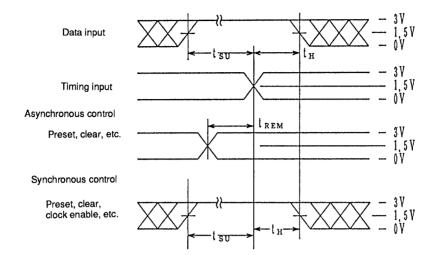

# Setup, Hold, and Release Timing

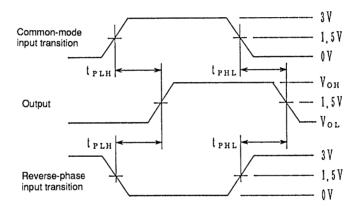

# **Transmission Delay**

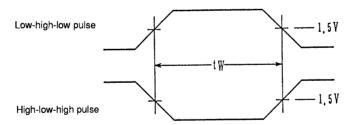

# **Pulse Width**

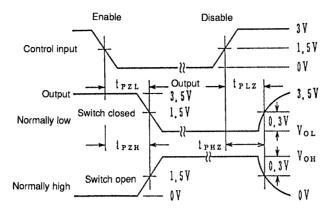

#### **Enable and Disable Timing**

Note: 1. These diagrams are for the input enable low level and the input control disable high level cases.

2. Pulse generator setup for all pulses: rate  $\leq$  1.0 MHz, Zo  $\leq$  50  $\Omega$ ,  $t_f \leq$  2.5 ns,  $t_r \leq$  2.5 ns

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- 2 Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of June, 1995. Specifications and information herein are subject to change without notice.