## Low-Voltage ETR-Controller

## **Preliminary**

### Overview

The LC72311W, LC72312W, and LC72313W are low-voltage single-chip FM/AM electronic tuning microcontrollers that include a built-in PLL circuit for frequencies up to 230 MHz, a 1/4 duty 1/2 bias LCD controller, and a small EEPROM. These microcontroller also provide a low-power standby mode that reduces power consumption by switching the system clock frequency. Furthermore, since these devices include a low-pass filter amplifier required for the electronic tuning system and a tuning voltage generator circuit, they can contribute to reduced end product costs through lower parts counts.

These ICs are optimal for use in low-voltage portable audio equipment that includes a radio receiver.

### **Functions**

- Program memory (ROM):

- $--8192 \times 16 \text{ bits } (16 \text{ KB}) \text{ LC72311W}$

- $-16,384 \times 16$  bits (32 KB) LC72312W

- $-24,576 \times 16$  bits (48 KB) LC72313W

- Data memory (RAM):

- $--512 \times 4$  bits (RAM)

- $--512 \times 4$  bits (EEPROM)

- Cycle time:

0.71 µs (at 4.2336 MHz) (All 1-word instructions) 40 µs (at 75 kHz) (All 1-word instructions)

- Stack: 8 levels

- LCD driver:

48 to 96 segments (1/4 duty 1/2 bias drive)

• Interrupts:

Two external interrupt systems Internal timer interrupts: two systems (1,5,10, and 50 ms) Serial I/O interrupt (SIO0 only)

- A/D converter: Four-input 8-bit converter

- Input ports:

9 or 10 ports (Ports PA, PF, and HCTR) The PF port is shared with the A/D converter, and HCTR is shared with the IF counter.

• Output ports:

8 ports (Ports PB and PE)

PE3 is shared with the BEEP pin, PE0 to PE2 are open-drain ports, and the PB port can be switched to function as an open-drain port.

Continued on next page.

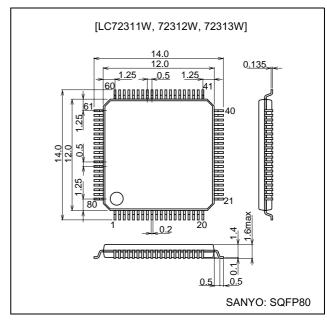

### **Package Dimensions**

unit: mm

#### 3220-SQFP80

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

Continued from preceding page.

• I/O ports:

22 ports (Ports PC, PD, PL, PI, PG, and PH)

Port PD is shared with the interrupt function, ports PC and PK are shared with the serial I/O function, and ports PI, PG, and PH are shared with the LCD segment driver function.

• PLL:

Provides dead band control (4 settings)

Reference frequencies: 1, 3, 3.125, 5, 6.25, 12.5, and 25 kHz

• Input frequencies:

FM band: 10 to 230 MHz AM band: 0.5 to 10 MHz

• Input sensitivity:

FM band: 35 mVrms (130 MHz to 50 mVrms)

AM band: 35 mVrms

• HCTR:

IF counter (0.4 to 15 MHz)

• External reset pin:

Starts the PC from address 0 during CPU and PLL operation.

• Built-in power-on reset circuit:

Starts the PC from address 0 at power on.

• Halt mode:

Temporarily slows the microcontroller operating clock and reduces power consumption.

· Backup mode:

Stops the crystal oscillator circuit.

• Static power on:

Backup mode can be cleared with the PF port.

• BEEP:

Seven alarm tones: 0.75, 1.25, 1.5, 2.08, 2.5, 3.125, and 6.25 kHz.

• Serial I/O:

Two channels (These functions use the PC and PK port pins.)

The internal serial transfer clock provides three frequencies: 12.5, 25, and 75 kHz.

• On-chip low-pass filter amplifier:

Reduces end product parts counts and costs.

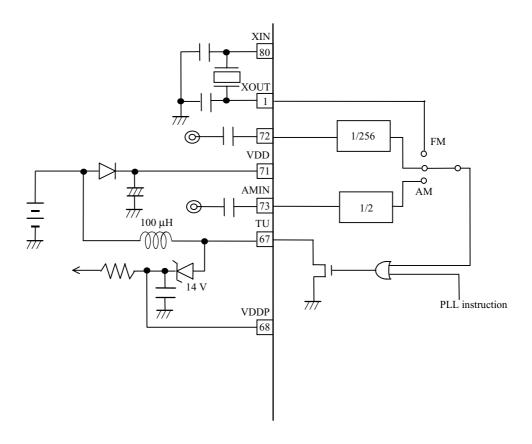

• Tuning voltage generator circuit:

Obviates the need for an external tuning power supply circuit for reduced end product parts counts and costs.

• Memory retention voltage:

Over 0.9 V.

• VDD voltage:

PLL circuit: 1.8 to 3.6 V CPU and A/D converter: 1.6 to 3.6 V (For a 40 µs instruction cycle) 2.4 to 3.6 V (For a 0.71 µs instruction cycle)

• Option selections:

PH0 to PH3/S13 to S16 PG0 to PG3/S17 to S20 PI0 to PI3/S21 to S24

Vsense circuit present/absent

· Package:

SQFP80 (0.5 mm lead pitch)

## **Tuning Voltage Generator Circuit**

# Specifications

# Absolute Maximum Ratings at Ta = 25°C, $V_{SS}$ = 0 V

| Parameter                   | Symbol              | Conditions                                    | Ratings                  | Unit |

|-----------------------------|---------------------|-----------------------------------------------|--------------------------|------|

| Maximum aumahuvaltaga       | V <sub>DD</sub> max |                                               | -0.3 to +4.0             | V    |

| Maximum supply voltage      | VDDPmax             |                                               | -0.3 to +16.0            | V    |

| Input voltage               | $V_{IN}$            | All input pins                                | $-0.3$ to $V_{DD} + 0.3$ | ٧    |

| Outside at                  | V <sub>OUT</sub> 1  | AOUT, PE0 to 2, TU                            | -0.3 to +15              | V    |

| Output voltage              | V <sub>OUT</sub> 2  | All output pins other than V <sub>OUT</sub> 1 | $-0.3$ to $V_{DD} + 0.3$ | V    |

| Output current              | I <sub>OUT</sub> 1  | PC, PD, PE3, PG, PH, PI, PK, PL, EO           | 0 to 3                   | mA   |

|                             | I <sub>OUT</sub> 2  | РВ                                            | 0 to 1                   | mA   |

|                             | I <sub>OUT</sub> 3  | AOUT, PE0 to 2, TU                            | 0 to 2                   | mA   |

|                             | I <sub>OUT</sub> 4  | S1 to S24                                     | 300                      | μΑ   |

|                             | I <sub>OUT</sub> 5  | COM1 to COM4                                  | 3                        | mA   |

| Allowable power dissipation | Pdmax               | $Ta = -20 \text{ to } +70^{\circ}C$           | 300                      | mW   |

| Operating temperature       | Topr                |                                               | -20 to +70               | °C   |

| Storage temperature         | Tstg                |                                               | -45 to +125              | °C   |

# Allowable Operating Ranges at Ta = -20 to +70 °C, $V_{DD}$ = 1.8 to 3.6 V

| Parameter                | Symbol            | Conditions                                                                                                     | Ratings             |     |                     | Unit    |

|--------------------------|-------------------|----------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------------|---------|

|                          | Syllibol          | Conditions                                                                                                     | min                 | typ | max                 | - Offic |

|                          | V <sub>DD</sub> 1 | PLL operating voltage                                                                                          | 1.8                 | 3.0 | 3.6                 |         |

|                          | V <sub>DD</sub> 2 | Memory retention voltage                                                                                       | 1.0                 |     |                     |         |

| Supply voltage           | V <sub>DD</sub> 3 | CPU operating voltage                                                                                          | 1.6                 | 3.0 | 3.6                 | V       |

|                          | V <sub>DD</sub> 4 | A/D converter operating voltage                                                                                | 1.6                 | 3.0 | 3.6                 |         |

|                          | VDDP1             | Voltage applied to the VDDP pin                                                                                | 13                  | 14  | 15                  |         |

|                          | V <sub>IH</sub> 1 | Input ports other than $\rm V_{IH}2,V_{IH}3,AMIN,FMIN,HCTR,XIN,$ and DIN (with amplifier circuit)              | 0.7 V <sub>DD</sub> |     | $V_{DD}$            | V       |

| High-level input voltage | V <sub>IH</sub> 2 | BRES                                                                                                           | $0.8 V_{DD}$        |     | $V_{DD}$            | V       |

|                          | V <sub>IH</sub> 3 | The PF port                                                                                                    | $0.6  V_{DD}$       |     | $V_{DD}$            | V       |

|                          | V <sub>IL</sub> 1 | Input ports other than V $_{\rm L}$ 2, V $_{\rm L}$ 3, AMIN, FMIN, HCTR, XIN, and DIN (with amplifier circuit) | 0                   |     | 0.3 V <sub>DD</sub> | V       |

| Low-level input voltage  | V <sub>IL</sub> 2 | BRES                                                                                                           | 0                   |     | 0.2 V <sub>DD</sub> | V       |

|                          | V <sub>IL</sub> 3 | The PF port                                                                                                    | 0                   |     | 0.2 V <sub>DD</sub> | V       |

|                          | V <sub>IN</sub> 1 | XIN                                                                                                            | 0.5                 |     | 0.6                 | Vrms    |

| Innut amplituda          | V <sub>IN</sub> 2 | FMIN,AMIN                                                                                                      | 0.035               |     | 0.35                | Vrms    |

| Input amplitude          | V <sub>IN</sub> 3 | FMIN                                                                                                           | 0.05                |     | 0.35                | Vrms    |

|                          | V <sub>IN</sub> 4 | HCTR and DIN (with amplifier circuit)                                                                          | 0.035               |     | 0.35                | Vrms    |

| Input voltage range      | V <sub>IN</sub> 6 | ADI0, ADI1, ADI2, ADI3                                                                                         | 0                   |     | $V_{DD}$            | V       |

|                          | F <sub>IN</sub> 1 | XIN CI $\leq$ 35 kΩ                                                                                            | 70                  | 75  | 80                  | kHz     |

|                          | F <sub>IN</sub> 2 | FMIN: V <sub>IN</sub> 2, V <sub>DD</sub> 1                                                                     | 10                  |     | 130                 | MHz     |

|                          | F <sub>IN</sub> 3 | FMIN: V <sub>IN</sub> 3, V <sub>DD</sub> 1                                                                     | 130                 |     | 230                 | MHz     |

| Input frequency          | F <sub>IN</sub> 4 | AMIN (H): V <sub>IN</sub> 2, V <sub>DD</sub> 1                                                                 | 2                   |     | 40                  | MHz     |

| input frequency          | F <sub>IN</sub> 5 | AMIN (L): V <sub>IN</sub> 2, V <sub>DD</sub> 1                                                                 | 0.5                 |     | 10                  | MHz     |

|                          | F <sub>IN</sub> 6 | HCTR: V <sub>IN</sub> 4, V <sub>DD</sub> 1                                                                     | 0.4                 |     | 12                  | MHz     |

|                          | F <sub>IN</sub> 7 | DIN (with amplifier circuit): V <sub>IN</sub> 4, V <sub>DD</sub> 1                                             | 2                   |     | 18                  | MHz     |

|                          | F <sub>IN</sub> 8 | DIN (without amplifier circuit): V <sub>IH</sub> 1, V <sub>DD</sub> 1                                          | 2                   |     | 18                  | MHz     |

# **Electrical Characteristics** in the Allowable Operating Ranges

| Parameter                         | Symbol               | Conditions                                                                                                                                          | Ratings                               |                     |                                       | Unit |  |

|-----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------|---------------------------------------|------|--|

| raiametei                         | Symbol               | Conditions                                                                                                                                          | min                                   | typ                 | max                                   | Unit |  |

| High-level input current          | I <sub>IH</sub> 1    | $XIN: VI = V_{DD} = 3.0 V$                                                                                                                          |                                       |                     | 3                                     | μΑ   |  |

|                                   | I <sub>IH</sub> 2    | FMIN, AMIN, HCTR, DIN (with amplifier circuit): $VI = V_{DD} = 3.0 \text{ V}$                                                                       | 3                                     | 8                   | 20                                    | μА   |  |

|                                   | I <sub>IH</sub> 3    | The PA/PF (without pull-down resistors), PC, PD, PG, PH, PI, PK, and PL ports, BRES, and DIN (without amplifier circuit): VI = $V_{DD}$ = 3.0 V     |                                       |                     | 3                                     | μА   |  |

|                                   | I <sub>IL</sub> 1    | $XIN: VI = V_{DD} = V_{SS}$                                                                                                                         |                                       |                     | -3                                    | μΑ   |  |

| Low-level input current           | I <sub>IL</sub> 12   | FMIN, AMIN, HCTR, DIN (with amplifier circuit): $VI = V_{DD} = V_{SS} \label{eq:VDD}$                                                               | -3                                    | -8                  | -20                                   | μА   |  |

| Low-level input current           | I <sub>IL</sub> 13   | The PA/PF (without pull-down resistors), PC, PD, PG, PH, PI, PK, and PL ports, BRES, and DIN (without amplifier circuit): VI = $V_{\rm DD}$ = 3.0 V |                                       |                     | -3                                    | μА   |  |

| Input floating voltage            | ViF                  | The PA and PF ports with pull-down resistors                                                                                                        |                                       |                     | $0.05  V_{DD}$                        | V    |  |

| Pull-down resistors               | R <sub>PD</sub> 1    | The PA and PF ports with pull-down resistors: $\mbox{V}_{\mbox{\scriptsize DD}} = 3.0 \mbox{ V}$                                                    | 75                                    | 100                 | 200                                   | kΩ   |  |

|                                   | R <sub>PD</sub> 2    | The TEST1 and TEST2 resistor                                                                                                                        |                                       | 10                  |                                       | kΩ   |  |

| Hysteresis                        | $V_{H}$              | BRES                                                                                                                                                | $0.1 V_{DD}$                          | 0.2 V <sub>DD</sub> |                                       | V    |  |

| Voltage doubler reference voltage | DBR4                 | V <sub>DD</sub> reference C (3) = 0.47 μF, Ta = 25°C (Note 1)                                                                                       | 1.3                                   | 1.5                 | 1.7                                   | V    |  |

| Voltage doubler step-up voltage   | DBR1, 2, 3           | C (1) = $0.47\mu F$<br>C (2) = $0.47\mu F$ No output load, Ta = $25^{\circ}C$ (Note 1)                                                              | 2.7                                   | 3.0                 | 3.3                                   | V    |  |

|                                   | V <sub>OH</sub> 1    | PB:IO = -1 mA                                                                                                                                       | V <sub>DD</sub> – 0.7 V <sub>DD</sub> |                     | V <sub>DD</sub> – 0.3 V <sub>DD</sub> | V    |  |

|                                   | V <sub>OH</sub> 2    | PC, PD, PG, PH,PI, PK, PL:IO = -1 mA                                                                                                                | V <sub>DD</sub> – 0.3 V <sub>DD</sub> |                     |                                       | V    |  |

| High-level output voltage         | V <sub>OH</sub> 3    | ΕΟ: ΙΟ = -500 μΑ                                                                                                                                    | V <sub>DD</sub> – 0.3 V <sub>DD</sub> |                     |                                       | V    |  |

|                                   | V <sub>OH</sub> 4    | XOUT: IO = -200 μA                                                                                                                                  | V <sub>DD</sub> – 0.3 V <sub>DD</sub> |                     |                                       | V    |  |

|                                   | V <sub>OH</sub> 5    | S1 to S24: IO = -20 μA *1                                                                                                                           | 2.0                                   |                     |                                       | V    |  |

|                                   | V <sub>OH</sub> 6    | COM1, COM2, COM3, COM4: IO = -100μA *1                                                                                                              | 2.0                                   |                     |                                       | V    |  |

|                                   | V <sub>OL</sub> 1    | PB: IO = -50 μA                                                                                                                                     | 0.3 V <sub>DD</sub>                   |                     | 0.7 V <sub>DD</sub>                   | V    |  |

|                                   | V <sub>OL</sub> 2    | PC, PD, PE3, PG, PH, PI, PK, PL:IO = -1 mA                                                                                                          |                                       |                     | 0.3 V <sub>DD</sub>                   | V    |  |

|                                   | V <sub>OL</sub> 3    | EO: IO = -500 μA                                                                                                                                    |                                       |                     | 0.3 V <sub>DD</sub>                   | V    |  |

| Low lovel output valtage          | V <sub>OL</sub> 4    | XOUT: IO = -200 μA                                                                                                                                  |                                       |                     | 0.3 V <sub>DD</sub>                   | V    |  |

| Low-level output voltage          | V <sub>OL</sub> 5    | S1 to S24: IO = –20 μA *1                                                                                                                           |                                       |                     | 1.0                                   | V    |  |

|                                   | V <sub>OL</sub> 6    | COM1, COM2, COM3, COM4: IO = -100μA *1                                                                                                              |                                       |                     | 1.0                                   | V    |  |

|                                   | V <sub>OL</sub> 7    | PE0 to 2: IO = 2 mA                                                                                                                                 |                                       |                     | 1.0                                   | V    |  |

|                                   | V <sub>OL</sub> 8    | AOUT, TU: IO = 1 mA AIN = 1.3 V V <sub>DD</sub> = 3 V                                                                                               |                                       |                     | 0.5                                   | V    |  |

| Output off leakage current        | I <sub>OFF</sub> 1   | Ports PB, PC, PD, PE3, PG, PH, PI, PK, PL, and EO                                                                                                   | -3                                    |                     | +3                                    | μΑ   |  |

|                                   | I <sub>OFF</sub> 2   | AOUT, TU, and PE0 to PE2                                                                                                                            | -100                                  |                     | +100                                  | nA   |  |

| A/D converter error               |                      | ADI0, ADI1, ADI2, ADI3                                                                                                                              | -3/2                                  |                     | +3/2                                  | LSB  |  |

| Voltage drop detection voltage    | V <sub>SENSE</sub> 1 | Ta = 25°C *2                                                                                                                                        | 1.6                                   | 1.75                | 1.9                                   | V    |  |

| Voltage rise detection voltage    | V <sub>SENSE</sub> 2 | Ta = 25°C *2                                                                                                                                        | (1) min<br>+0.1                       |                     | (1) max<br>+0.2                       | V    |  |

|                                   | I <sub>DD</sub> 1    | V <sub>DD</sub> 1: FIN (2) 130 MHz Ta = 25°C                                                                                                        |                                       | 10                  |                                       | mA   |  |

| Ourse at desir                    | I <sub>DD</sub> 2    | V <sub>DD</sub> 2: Halt mode, Ta = 25°C *3                                                                                                          |                                       | 0.1                 |                                       | mA   |  |

| Current drain                     | I <sub>DD</sub> 3    | $V_{DD} = 3.6 \text{ V}$ , with the oscillator stopped, $Ta = 25^{\circ}C$ *4                                                                       |                                       | 1                   |                                       | μΑ   |  |

|                                   | I <sub>DD</sub> 4    | V <sub>DD</sub> = 2.4 V, with the oscillator stopped,Ta = 25°C *4                                                                                   |                                       | 0.5                 |                                       | μА   |  |

With the halt mode current, this IC can execute 20 instruction steps every 125 ms.

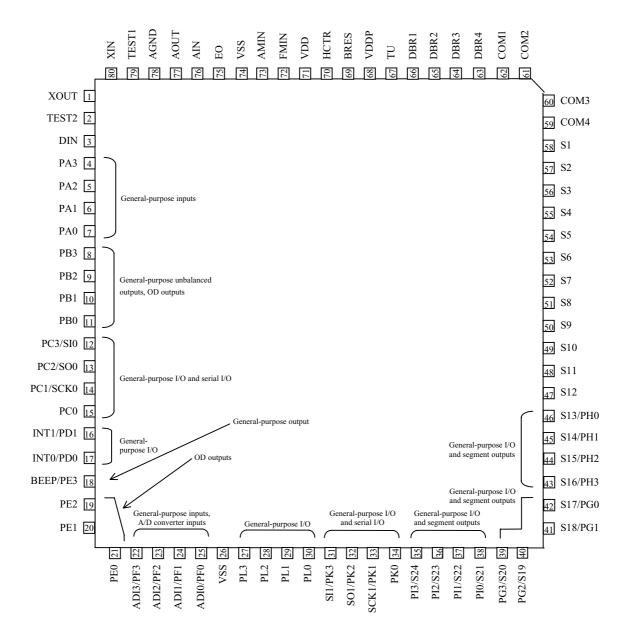

#### Pin Assignment

### **Pin Functions**

| Pin No.  | Pin                | I/O | Function                                                                                                                                                                                                            |

|----------|--------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80       | XIN                | I   | Occupations for a 75 library state or illustration                                                                                                                                                                  |

| 1        | XOUT               | 0   | Connections for a 75 kHz crystal oscillator                                                                                                                                                                         |

| 79       | TEST1              | 1   | IC testing.                                                                                                                                                                                                         |

| 2        | TEST2              | 1   | These pins must be tied to ground.                                                                                                                                                                                  |

| 4        | PA3                |     | General-purpose inputs with built-in pull-down resistors. The pull-down resistors are selected using the                                                                                                            |

| 5        | PA2                | I   | IOS instruction (IOS 2, b1). Note that the pull-down resistors cannot be selected individually for each pin.                                                                                                        |

| 6        | PA1                |     | When these inputs are used in conjunction with port PB (unbalanced outputs) to form a key matrix circuit,                                                                                                           |

| 7        | PA0                |     | multiple key presses of up to up to 3 keys can be detected.                                                                                                                                                         |

| 8        | PB3                |     | The IOS instruction (IOS 2, b0, b2, b3) is used to select between the unbalanced output and open drain                                                                                                              |

| 9        | PB2                | 0   | output circuit types. When the unbalanced type output circuit is selected, these outputs can be used in conjunction with port PA to form a key matrix circuit that can detect multiple key presses. If the          |

| 10       | PB1                |     | general-purpose output function is selected, care is required to prevent problems related to impedance. If                                                                                                          |

| 11       | PB0                |     | the open-drain output circuit is selected, the maximum output voltage will be VDD, and pull-up resistors will be required.                                                                                          |

| 12       | PC3/SI0            |     | General-purpose I/O ports and serial I/O ports.                                                                                                                                                                     |

| 13       | PC2/SO0            |     | The I/O direction of these general-purpose ports can be selected in 1-bit units with the IOS instruction (IOS                                                                                                       |

| 14       | PC1/SCK0           | I/O | 4, b0 to b3).                                                                                                                                                                                                       |

| 15       | PC0                |     | The IOS instruction (IOS 3, b2) is used to switch between the general-purpose input and the serial I/O functions.                                                                                                   |

| 16       | INT1/PD1           | I/O | The I/O directions of the PD port pins can be selected in 1-bit units with the IOS instruction (IOS 5, b1, b2).                                                                                                     |

| 17       | INT0/PD0           | I/O | The PD port pins can be used as interrupt input pins. For this use, the pin I/O direction must be set to input.                                                                                                     |

| 18       | BEEP/PE3           | 0   | BEEP output and general-purpose output. The BEEP instruction is used to switch the pin function. The output circuit is a CMOS push-pull circuit.                                                                    |

| 19       | PE2                |     |                                                                                                                                                                                                                     |

| 20       | PE1                | 0   | N-channel open-drain port. These port pins require pull-up resistors.                                                                                                                                               |

| 21       | PE0                |     |                                                                                                                                                                                                                     |

| 22       | ADI3/PF3           |     | General-purpose input/A/D converter input shared function port. The IOS instruction (IOS F, b0 to b3) is                                                                                                            |

| 23       | ADI2/PF2           | 1   | used to switch between the general-purpose input and A/D converter input functions. All of these ports can be used to recover from backup mode. The IOS instruction (IOS 0, b0 to b3) is used to select which ports |

| 24       | ADI1/PF1           | '   | are used for recovery from backup mode. The A/D converter is an 8-bit successive approximation A/D                                                                                                                  |

| 25       | ADI0/PF0           |     | converter and VDD is the full-scale voltage.                                                                                                                                                                        |

| 27       | PL3                |     | DIG is a second summary I/O and                                                                                                                                                                                     |

| 28       | PL2                | I/O | PL0 is a general-purpose I/O port.  The I/O direction of these general-purpose port pins can be selected in 1-bit units with the IOS instruction                                                                    |

| 29       | PL1                |     | (IOS B, b0 to b3).                                                                                                                                                                                                  |

| 30       | PL0                |     |                                                                                                                                                                                                                     |

| 31       | SI1/PK3            |     | General-purpose I/O ports.                                                                                                                                                                                          |

| 32       | SO1/PK2            | 110 | The I/O direction of these general-purpose port pins can be selected in 1-bit units with the IOS instruction                                                                                                        |

| 33       | SCK1/PK1           | I/O | (IOS C, b0 to b3).                                                                                                                                                                                                  |

| 34       | PK0                |     | PK1 to PK3 are general-purpose input or serial I/O ports. The IOS instruction (IOS 3, b3) is used to switch between the general-purpose input and serial I/O port functions.                                        |

| 35       | PI3/S24            |     |                                                                                                                                                                                                                     |

| 36       | PI2/S23            |     |                                                                                                                                                                                                                     |

| 37       | PI1/S22            |     | LCD driver segment output and general-purpose I/O shared function ports. The IOS instruction is used to                                                                                                             |

| 38       | PI0/S21            |     | set the I/O direction for these pins used as general-purpose I/O pins.                                                                                                                                              |

| 20       | DC2/022            |     | Port PI: IOS 8, b0 to b3                                                                                                                                                                                            |

| 39       | PG3/S20            |     | Port PH: IOS 7, b0 to b3                                                                                                                                                                                            |

| 40<br>41 | PG2/S19<br>PG1/S18 | I/O | Port PG: IOS 6, b0 to b3                                                                                                                                                                                            |

| 41       | PG1/S18<br>PG0/S17 | 1,0 | A combination of mask options and the IOS instruction are used to select the segment output and general-purpose port functions. The function can be selected in 1-bit units.                                        |

|          |                    |     | Port PI: IOS D, b0 to b3                                                                                                                                                                                            |

| 43       | PH3/S16            |     | Port PH: IOS D, b0 to b3                                                                                                                                                                                            |

| 44       | PH2/S15            |     | Port PG: IOS B, b0 to b3                                                                                                                                                                                            |

| 45       | PH1/S14            |     |                                                                                                                                                                                                                     |

| 46       | PH0/S13            |     |                                                                                                                                                                                                                     |

|          |                    |     |                                                                                                                                                                                                                     |

Continued on next page.

### Continued from preceding page.

| Pin No.              | Pin                                                   | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|-------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47 to 58             | S12 to S1                                             | 0   | LCD driver segment outputs.  This circuit implements a 1/4 duty 1/2 bias LCD drive technique.  The frame frequency is 75 Hz.  An output voltage of 3 V is maintained for VDD in the range 1.8 to 3.6 V.                                                                                                                                                                                                       |

| 59<br>60<br>61<br>62 | COM4<br>COM3<br>COM2<br>COM1                          | 0   | LCD driver segment outputs.  This circuit implements a 1/4 duty 1/2 bias LCD drive technique.  The frame frequency is 75 Hz.  An output voltage of 3 V is maintained for VDD in the range 1.8 to 3.6 V.                                                                                                                                                                                                       |

| 63<br>64<br>65<br>66 | DBR4<br>DBR3<br>DBR2<br>DBR1                          |     | LCD power supply step-up voltage outputs                                                                                                                                                                                                                                                                                                                                                                      |

| 69                   | BRES                                                  | I   | System reset.  A system reset is applied if a low level is applied to this pin for at least 1 machine cycle in either CPU operating mode or halt mode. The PC is set to 0 and program execution is started.  In backup mode, applying a low level to this pin clears backup mode.                                                                                                                             |

| 67                   | TU                                                    | _   | Tuning voltage generation circuit. This IC provides an internal transistor, and a circuit that generates the tuning voltage (12 to 14 V) can be formed on this pin with external coil, Zener diode, and capacitor components.                                                                                                                                                                                 |

| 72                   | FMIN                                                  | I   | FM VCO (local oscillator) input. This pin is selected with CW1 in the PLL instruction. The input must be capacitor coupled. The input frequency is 10 to 230 MHz.                                                                                                                                                                                                                                             |

| 73                   | AMIN                                                  | ı   | AM VCO (local oscillator) input. This pin is selected with CW1 in the PLL instruction. The input must be capacitor coupled. The input frequency is 0.5 to 10 MHz.                                                                                                                                                                                                                                             |

| 70                   | HCTR                                                  | I   | IF counter input and general-purpose input shared function pin. The IOS instruction (IOS 1, b3) is used to switch between these functions. If the IF counter is used, use a capacitor-coupled input, and use the UCC instruction to start and stop the counter. The input frequency range is 0.4 to 12 MHz. If the general-purpose input function is used, use the INR instruction to acquire the input data. |

| 75                   | EO                                                    | 0   | Main charge pump output. If the frequency created by dividing the local oscillator frequency by N is higher than the reference frequency, a high level is output. If that frequency is lower than the reference, a low level is output. If the frequencies match, this pin goes to the high-impedance state.                                                                                                  |

| 3                    | DIN                                                   | I   | Clock input from a CD DSP or other IC. The input frequency can be switched between 1/1, 1/2, and 1/4. A frequency range of from 4 to 4.5 MHz is used for the internal clock frequency. This pin can be used to form a self-oscillating circuit by connecting a capacitor. These functions are all switched with the DIN instruction.                                                                          |

| 68                   | VDDP                                                  |     | The internal EEPROM power supply. If the EEPROM is used, apply a 14 V level to this pin. The TU pin output can be used for this 14 V level.                                                                                                                                                                                                                                                                   |

| 76<br>77<br>78       | AIN<br>AOUT<br>AGND                                   | -   | Connections for the low-pass filter amplifier transistor. Connect AGND to ground.                                                                                                                                                                                                                                                                                                                             |

| 71<br>26<br>74       | V <sub>DD</sub><br>V <sub>SS</sub><br>V <sub>SS</sub> | -   | Power supply.                                                                                                                                                                                                                                                                                                                                                                                                 |

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, of otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of November, 2001. Specifications and information herein are subject to change without notice.