# PLL Frequency Synthesizer for Electronic Tuning

## Overview

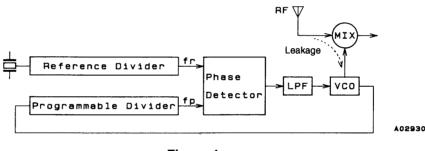

The LC72136N and LC72136NM are PLL frequency synthesizers for use in radio/cassette players. They allow high-performance AM/FM tuners to be implemented easily.

#### **Features**

- · High-speed programmable frequency divider

- FMIN: 10 to 160 MHz.....Pulse swallower (divide-by-two prescaler built in)

- AMIN: 2 to 40 MHz......Pulse swallower 0.5 to 10 MHz.....Direct division

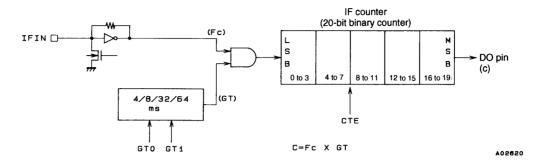

- IF counter

IFIN: 0.4 to 12 MHz.....For use as an AM/FM IF counter

- · Reference frequency

- Selectable from one of eight frequencies (crystal oscillator: 75 kHz)

1, 3, 5, 3.125, 6.25, 12.5, 15, and 25 kHz

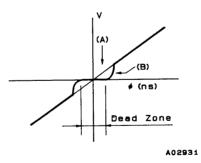

- Phase comparator

- Supports dead zone control

- Built-in unlock detection circuit

- Built-in deadlock clear circuit

- Built-in MOS transistor for forming an active low-pass filter

- I/O ports

- Dedicated output ports: 6

- I/O ports: 2

- Supports clock time base output

- Serial Data I/O

- Supports CCB format communication with the system controller.

- Operating ranges

- Supply voltage: 4.5 to 5.5 V

- Operating temperature: –20 to +70°C

- Packages

- -DIP22S/MFP24S

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

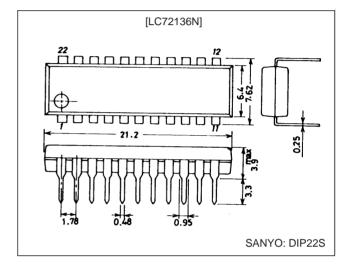

## **Package Dimensions**

unit: mm

#### 3059-DIP22S

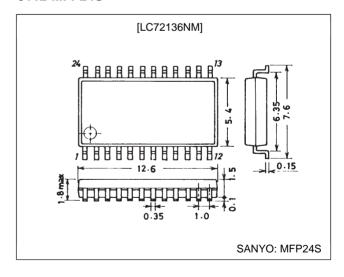

unit: mm

#### 3112-MFP24S

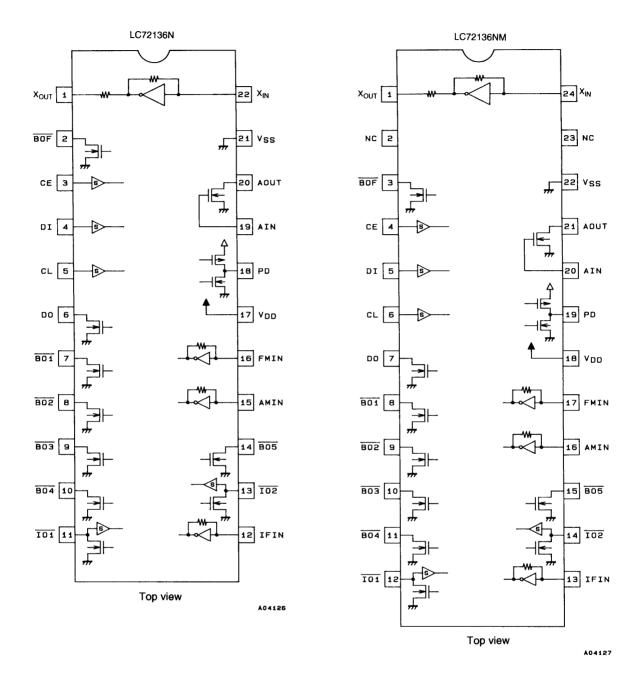

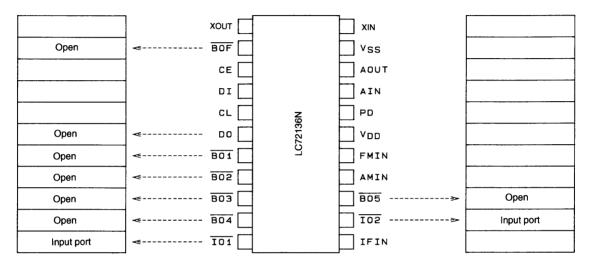

## **Pin Assignments**

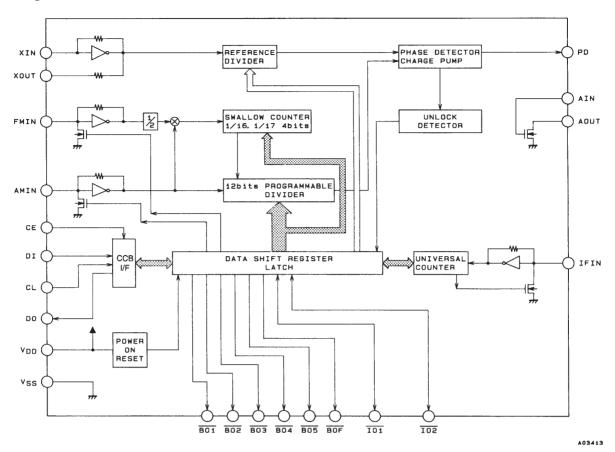

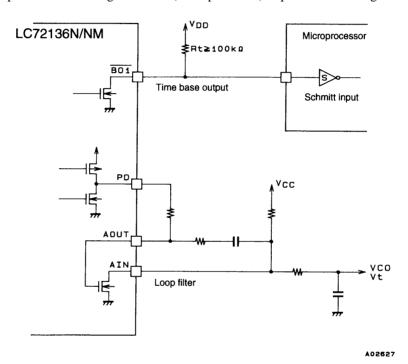

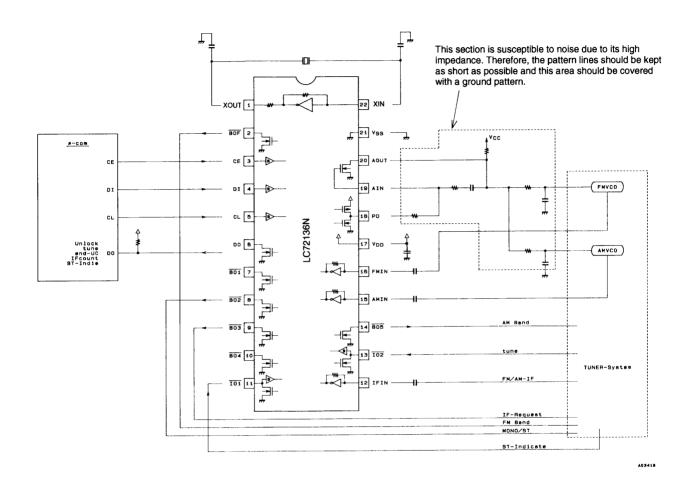

## **Block Diagram**

## **Specifications**

## Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , $V_{SS} = 0$ V

| Parameter                   | Symbol                | Conditions                      | Ratings                       | Unit |

|-----------------------------|-----------------------|---------------------------------|-------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max   | V <sub>DD</sub>                 | -0.3 to +7.0                  | V    |

|                             | V <sub>IN</sub> 1 max | CE, CL, DI, AIN                 | -0.3 to +7.0                  | V    |

| Maximum input voltage       | V <sub>IN</sub> 2 max | XIN, FMIN, AMIN, IFIN           | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                             | V <sub>IN</sub> 3 max | <u>101</u> , <u>102</u>         | -0.3 to +15                   | V    |

|                             | V <sub>O</sub> 1 max  | DO                              | -0.3 to +7.0                  | V    |

| Maximum output voltage      | V <sub>O</sub> 2 max  | XOUT, PD                        | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                             | V <sub>O</sub> 3 max  | BO1 to BO5, BOF, IO1, IO2, AOUT | -0.3 to +15                   | V    |

|                             | I <sub>O</sub> 1 max  | I <sub>O</sub> 1 max BO1        |                               | mA   |

| Maximum output current      | I <sub>O</sub> 2 max  | AOUT, DO                        | 0 to 6.0                      | mA   |

|                             | I <sub>O</sub> 3 max  | BO2 to BO5, BOF, IO1, IO2       | 0 to 10.0                     | mA   |

| Allowable news dissination  | Dd may                | Ta ≤ 70°C: LC72136N (DIP22S)    | 350                           | mW   |

| Allowable power dissipation | Pd max                | Ta ≤ 70°C: LC72136NM (MFP24S)   | 200                           | mW   |

| Operating temperature       | Topr                  |                                 | -20 to +70                    | °C   |

| Storage temperature         | Tstg                  |                                 | -40 to +125                   | °C   |

## Allowable Operating Ranges at $Ta = -20 \ to \ +70 ^{\circ}C, \ V_{SS} = 0 \ V$

| Parameter                               | Symbol              | Conditions                       | min                 | typ | max                 | Unit  |

|-----------------------------------------|---------------------|----------------------------------|---------------------|-----|---------------------|-------|

| Supply voltage                          | V <sub>DD</sub>     | $V_{DD}$                         | 4.5                 |     | 5.5                 | V     |

| Input high lovel voltege                | V <sub>IH</sub> 1   | CE, CL, DI                       | 0.7 V <sub>DD</sub> |     | 6.5                 | V     |

| Input high-level voltage                | V <sub>IH</sub> 2   | 101, 102                         | 0.7 V <sub>DD</sub> |     | 13                  | V     |

| Input low-level voltage                 | V <sub>IL</sub>     | CE, CL, DI, IO1, IO2             | 0                   |     | 0.3 V <sub>DD</sub> | V     |

| Output voltage                          | V <sub>O</sub> 1    | DO                               | 0                   |     | 6.5                 | V     |

| Output voltage                          | V <sub>O</sub> 2    | BO1 to BO5, BOF, IO1, IO2, AOUT  | 0                   |     | 13                  | V     |

|                                         | f <sub>IN</sub> 1   | XIN: V <sub>IN</sub> 1           |                     | 75  |                     | kHz   |

| Input frequency                         | f <sub>IN</sub> 2   | FMIN: V <sub>IN</sub> 2          | 10                  |     | 160                 | MHz   |

|                                         | f <sub>IN</sub> 3   | AMIN: V <sub>IN</sub> 3, SNS = 1 | 2                   |     | 40                  | MHz   |

|                                         | f <sub>IN</sub> 4   | AMIN: $V_{IN}4$ , SNS = 0        | 0.5                 |     | 10                  | MHz   |

|                                         | f <sub>IN</sub> 5   | IFIN: V <sub>IN</sub> 5          | 0.4                 |     | 12                  | MHz   |

|                                         | V <sub>IN</sub> 1   | XIN: f <sub>IN</sub> 1           | 400                 |     | 1500                | mVrms |

|                                         | V <sub>IN</sub> 2-1 | FMIN: f = 10 to 130 MHz          | 40                  |     | 1500                | mVrms |

|                                         | V <sub>IN</sub> 2-2 | FMIN: f = 130 to 160 MHz         | 70                  |     | 1500                | mVrms |

| Input amplitude                         | V <sub>IN</sub> 3   | AMIN: f <sub>IN</sub> 3, SNS = 1 | 40                  |     | 1500                | mVrms |

|                                         | V <sub>IN</sub> 4   | AMIN: $f_{IN}4$ , SNS = 0        | 40                  |     | 1500                | mVrms |

|                                         | V <sub>IN</sub> 5-1 | IFIN: f <sub>IN</sub> 5, IFS = 1 | 40                  |     | 1500                | mVrms |

|                                         | V <sub>IN</sub> 5-2 | IFIN: f <sub>IN</sub> 6, IFS = 0 | 70                  |     | 1500                | mVrms |

| Guaranteed crystal oscillator frequency | Xtal                | XIN, XOUT*                       |                     | 75  |                     | kHz   |

Note: \* Crystal oscillator recommended CI value

Cl ≤ 35 kΩ (for a 75 kHz crystal)

The circuit constants for the crystal oscillator circuit depend on the crystal used, the printed circuit board pattern, and other items. Therefore we recommend consulting with the manufacturer of the crystal for evaluation and reliability.

The extremely high input impedance of the XIN pins means that applications must take the possibility of leakage into account.

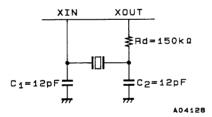

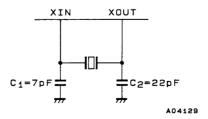

## **Sample Oscillator Circuits**

1. Seiko-Epson C-2-75kHz ( $C_L = 11 \text{ pF}$ )

2. Kyocera Corporation KF-38R5-09P0300 ( $C_L = 9 pF$ )

## Electrical Characteristics at $Ta=-20~to~+70^{\circ}C,\,V_{SS}=0~V$

| Parameter                                 | Symbol             | Conditions                                                                                                                 | min                   | typ                 | max | Unit |

|-------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|-----|------|

|                                           | Rf1                | XIN                                                                                                                        |                       | 8.0                 |     | ΜΩ   |

|                                           | Rf2                | FMIN                                                                                                                       |                       | 500                 |     | kΩ   |

| Internal feedback resistors               | Rf3                | AMIN                                                                                                                       |                       | 500                 |     | kΩ   |

|                                           | Rf1 XIN Rf2 FMIN   | 250                                                                                                                        |                       | kΩ                  |     |      |

|                                           | Rpd1               | FMIN                                                                                                                       |                       | 200                 |     | kΩ   |

| Internal pull-down resistors              | Rpd2               | AMIN                                                                                                                       |                       | 200                 |     | kΩ   |

| Internal output resistor                  | Rd                 | XOUT                                                                                                                       |                       | 250                 |     | kΩ   |

| Hysteresis                                | V <sub>HIS</sub>   | CE, CL, DI, $\overline{\text{IO1}}$ , $\overline{\text{IO2}}$                                                              |                       | 0.1 V <sub>DD</sub> |     | V    |

| Output high-level voltage                 |                    | PD: I <sub>O</sub> = -1 mA                                                                                                 | V <sub>DD</sub> – 1.0 |                     |     | V    |

|                                           | V <sub>OL</sub> 1  | PD: I <sub>O</sub> = 1 mA                                                                                                  |                       |                     | 1.0 | V    |

|                                           | \/ a               | BO1: I <sub>O</sub> = 0.5 mA                                                                                               |                       |                     | 0.5 | V    |

|                                           | VOL <sup>2</sup>   | BO1: I <sub>O</sub> = 1 mA                                                                                                 |                       |                     | 1.0 | V    |

|                                           | \/ 2               | DO: I <sub>O</sub> = 1 mA                                                                                                  |                       |                     | 0.2 | V    |

| Output low-level voltage                  | V <sub>OL</sub> 3  | DO: I <sub>O</sub> = 5 mA                                                                                                  |                       |                     | 1.0 | V    |

|                                           |                    | $\overline{BO2}$ to $\overline{BO5}$ , $\overline{BOF}$ , $\overline{IO1}$ , $\overline{IO2}$ : $I_O = 1 \text{ mA}$       |                       |                     | 0.2 | V    |

|                                           | V <sub>OL</sub> 4  | $\overline{BO2}$ to $\overline{BO5}$ , $\overline{BOF}$ , $\overline{IO1}$ , $\overline{IO2}$ : $I_O = 5 \text{ mA}$       |                       |                     | 1.0 | V    |

|                                           |                    | $\overline{BO2}$ to $\overline{BO5}$ , $\overline{BOF}$ , $\overline{IO1}$ , $\overline{IO2}$ : $I_O = 8 \text{ mA}$       |                       |                     | 1.6 | V    |

|                                           | V <sub>OL</sub> 5  | AOUT: I <sub>O</sub> = 1 mA, AIN = 1.3 V                                                                                   |                       |                     | 0.5 | V    |

|                                           | I <sub>IH</sub> 1  | CE, CL, DI: V <sub>I</sub> = 6.5 V                                                                                         |                       |                     | 5.0 | μA   |

| land birth land only                      | I <sub>IH</sub> 2  | <del>101</del> , <del>102</del> : V <sub>1</sub> = 13 V                                                                    |                       |                     | 5.0 | μA   |

|                                           | I <sub>IH</sub> 3  | $XIN: V_I = V_{DD}$                                                                                                        | 0.3                   | 0.6                 | 1.4 | μA   |

| Input high-level voltage                  | I <sub>IH</sub> 4  | FMIN, AMIN: V <sub>I</sub> = V <sub>DD</sub>                                                                               | 4.0                   |                     | 22  | μA   |

|                                           | I <sub>IH</sub> 5  | IFIN: V <sub>I</sub> = V <sub>DD</sub>                                                                                     | 8.0                   |                     | 44  | μA   |

|                                           | I <sub>IH</sub> 6  | AIN: V <sub>I</sub> = 6.5 V                                                                                                |                       |                     | 200 | nA   |

|                                           | I <sub>IL</sub> 1  | CE, CL, DI: V <sub>I</sub> = 0 V                                                                                           |                       |                     | 5.0 | μA   |

|                                           | I <sub>IL</sub> 2  | $\overline{101}$ , $\overline{102}$ : $V_1 = 0 V$                                                                          |                       |                     | 5.0 | μA   |

| Innut law lavel ourrent                   | I <sub>IL</sub> 3  | XIN: V <sub>I</sub> = 0 V                                                                                                  | 0.3                   | 0.6                 | 1.4 | μA   |

| Input low-level current                   | I <sub>IL</sub> 4  | FMIN, AMIN: V <sub>I</sub> = 0 V                                                                                           | 4.0                   |                     | 22  | μA   |

|                                           | I <sub>IL</sub> 5  | IFIN: V <sub>I</sub> = 0 V                                                                                                 | 8.0                   |                     | 44  | μA   |

|                                           | I <sub>IL</sub> 6  | AIN: V <sub>I</sub> = 0 V                                                                                                  |                       |                     | 200 | nA   |

| Output off leakage current                | I <sub>OFF</sub> 1 | $\overline{BO1}$ to $\overline{BO5}$ , $\overline{BOF}$ , AOUT, $\overline{IO1}$ , $\overline{IO2}$ : $V_O = 13 \text{ V}$ |                       |                     | 5.0 | μA   |

| Output on leakage current                 | I <sub>OFF</sub> 2 | DO: V <sub>O</sub> = 6.5 V                                                                                                 |                       |                     | 5.0 | μA   |

| High-level tree-state off leakage current | I <sub>OFFH</sub>  | PD: V <sub>O</sub> = V <sub>DD</sub>                                                                                       |                       | 0.01                | 200 | nA   |

| Low-level tree-state off leakage current  | I <sub>OFFL</sub>  | PD: V <sub>O</sub> = 0 V                                                                                                   |                       | 0.01                | 200 | nA   |

| Input capacitance                         | C <sub>IN</sub>    | FMIN                                                                                                                       |                       | 6                   |     | pF   |

|                                           | I <sub>DD</sub> 1  | $V_{DD}$ : Xtal = 75 kHz, $f_{IN}$ 2 = 130 MHz, $V_{IN}$ 2 = 40 mVrms                                                      |                       | 5                   | 10  | mA   |

| Current drain                             | I <sub>DD</sub> 2  |                                                                                                                            |                       | 0.1                 |     | mA   |

|                                           | I <sub>DD</sub> 3  | V <sub>DD</sub> : PLL block stopped, Xtal oscillator stopped                                                               |                       |                     | 10  | μA   |

## **Pin Functions**

| Memory   Symbol   Memory   Symbol   S   |                 |         | I            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| The extremely high input importance of the XIN pins means that applications must stake the possibility of leakage into account.  16 (17)  Local oscillator signal input  - FMIN is selected when the serial data input DVS bit is set to 1.  - The input frequency range is from 10 to 160 MHz.  - The input frequency range is from 10 to 160 MHz.  - The input frequency range is from 10 to 160 MHz.  - The input frequency range is from 10 to 160 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The input frequency range is 50 set to 40 MHz.  - The signal input of the range 27 set advance counter.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50 mHz.  - The input frequency range is 50 set to 50  | Symbol          | , ,     | Туре         | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Circuit configuration |

| Set to 1.  The input frequency range is from 10 to 160 MHz. The input signal passes through the internal divide-by-two prescaler and is input to the swallow counter. The divisor can be in the range 272 to 6535.9. However, since the signal has passed through the divide-by-two prescaler, the actual divisor is twice the set value.  ADZE999  ADZE991  ADZE999  ADZE999  ADZE999  ADZE999  ADZE999  ADZE999  ADZE991  ADZE999  ADZE9 |                 | 1       | Xtal         | The extremely high input impedance of the XIN pins<br>means that applications must take the possibility of                                                                                                                                                                                                                                                                                                                                                               | W                     |

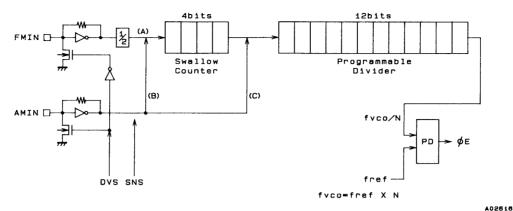

| AMIN 15 (16) Local oscillator signal input  Local oscillator signal input sole signal | FMIN            | 16 (17) |              | set to 1.  The input frequency range is from 10 to 160 MHz.  The input signal passes through the internal divide-bytwo prescaler and is input to the swallow counter.  The divisor can be in the range 272 to 65535. However, since the signal has passed through the divide-by-two                                                                                                                                                                                      | A02599                |

| Serial data.  **Serial data**  **Used as the synchronization clock when inputting (DI) or outputting (DO) serial data.  **Description**  **Des | AMIN            | 15 (16) |              | set to 0.  When the serial data input SNS bit is set to 1:  The input frequency range is 2 to 40 MHz.  The signal is directly input to the swallow counter.  The divisor can be in the range 272 to 65535, and the divisor used will be the value set.  When the serial data input SNS bit is set to 0:  The input frequency range is 0.5 to 10 MHz.  The signal is directly input to a 12-bit programmable divider.  The divisor can be in the range 4 to 4095, and the | A02599                |

| DI 4 (5) Input data • Inputs serial data transferred from the controller to the LC72136N.  • Output serial data transferred from the LC72136N to the controller. The data output is determined by the DOC0 to DOC2 bits in the serial data.  • The LC72136N power supply pin. (VDD = 4.5 to 5.5 V) • The power on reset circuit operates when power is first applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CE              | 3 (4)   | Chip enable  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |

| DO 6 (7) Output data  Output data  Outputs serial data transferred from the LC72136N to the controller. The data output is determined by the DOC0 to DOC2 bits in the serial data.  VDD 17 (18) Power supply  The LC72136N power supply pin. (VDD = 4.5 to 5.5 V) The power on reset circuit operates when power is first applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CL              | 5 (6)   | Clock        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | D S                   |

| Output data  Output serial data transferred from the LC72136N to the controller. The data output is determined by the DOC0 to DOC2 bits in the serial data.  A02601  The LC72136N power supply pin. (V <sub>DD</sub> = 4.5 to 5.5 V) The power on reset circuit operates when power is first applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DI              | 4 (5)   | Input data   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | □ S A02500            |

| V <sub>DD</sub> 17 (18) Power supply • The power on reset circuit operates when power is first applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DO              | 6 (7)   | Output data  | the controller. The data output is determined by the                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |

| V <sub>SS</sub> 21 (22) Ground • The LC72136N ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>DD</sub> | 17 (18) | Power supply | The power on reset circuit operates when power is first                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>SS</sub> | 21 (22) | Ground       | The LC72136N ground                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |

Continued on next page.

## Continued from preceding page.

| Symbol                          | Pin No.<br>(MFP pin numbers<br>are in parentheses.)     | Туре                                 | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Circuit configuration |

|---------------------------------|---------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| BO1<br>BO2<br>BO3<br>BO4<br>BO5 | 7 (8)<br>8 (9)<br>9 (10)<br>10 (11)<br>14 (15)<br>2 (3) | Output ports                         | Dedicated outputs The output states are determined by the BO1 to BO5 bits in the serial data. Data: 0 = open, 1 = low A time base signal (8 Hz) can be output from the BO1 pin. (When the serial data TBC bit is set to 1.) Care is required when using the BO1 pin, since it has a higher on impedance that the other output ports (pins BO2 to BO5). The output state of the BOF pin is determined by the serial data DVS bit. Thus this pin can be used as an FM band selection switch. (Note that it should not be used as an AM band selection switch since it is susceptible to noise from the crystal oscillator.) DVS data: 0 = open, 1 = low All output ports are set to the open state following a power on reset. | A02501                |

| ĪO1<br>ĪO2                      | 11 (12)<br>13 (14)                                      | Input or output ports                | I/O dual-use pins Interview of the serial data.  Interview of the input port, 1 = output port  When specified for use as input ports: The state of the input pin is transmitted to the controller over the DO pin. Input state: low = 0 data value high = 1 data value When specified for use as output ports: The output states are determined by the IO1 and IO2 bits in the serial data. Data: 0 = open, 1 = low These pins function as input pins following a power on reset.                                                                                                                                                                                                                                            | A02502                |

| PD                              | 18 (19)                                                 | Charge pump<br>output                | PLL charge pump output     When the frequency generated by dividing the local oscillator signal frequency by N is higher than the reference frequency, a high level is output from the PD pin. Similarly, when that frequency is lower, a low level is output. The PD pin goes to the high-impedance state when the frequencies match.                                                                                                                                                                                                                                                                                                                                                                                       | A02603                |

| AIN<br>AOUT                     | 19 (20)<br>20 (21)                                      | LPF amplifier transistor connections | The n-channel MOS transistor used for the PLL active low-pass filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A02504                |

| IFIN                            | 12 (13)                                                 | IF counter                           | Accepts an input in the frequency range 0.4 to 12 MHz.     The input signal is directly transmitted to the IF counter.     The result is output starting the MSB of the IF counter using the DO pin.     Four measurement periods are supported: 4, 8, 32, and 64 ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A02599                |

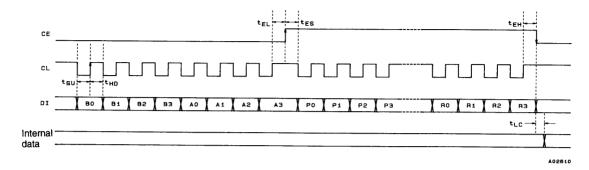

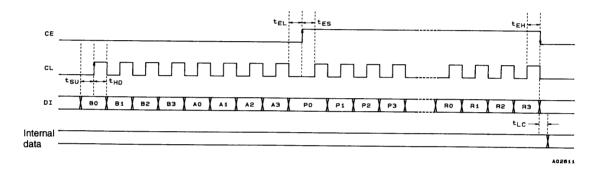

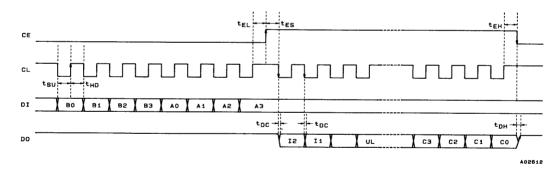

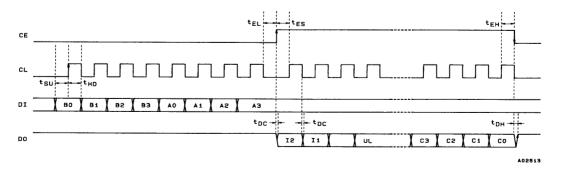

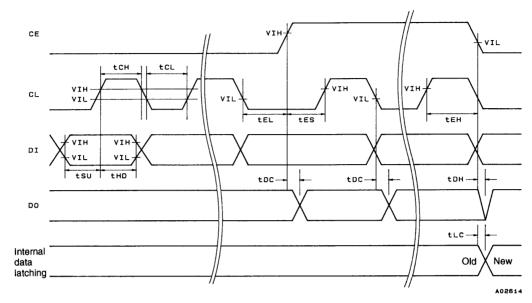

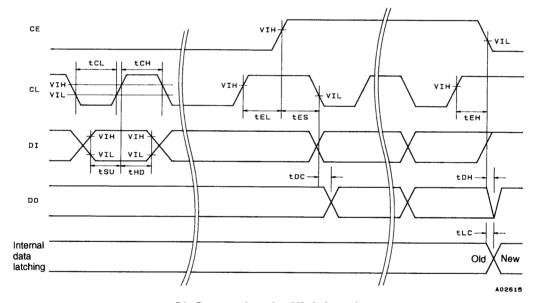

## Serial Data I/O Procedures

The LC72136N inputs and outputs data using the Sanyo CCB (computer control bus) audio LSI serial bus format. This LSI adopts an 8-bit address format CCB.

|   | I/O mode                                                                                        | В0           | B1       | B2 | В3   | A0 | A1 | A2 | А3                                    | Function                                                                                                                                                                                                            |  |  |  |

|---|-------------------------------------------------------------------------------------------------|--------------|----------|----|------|----|----|----|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1 | IN1 (82)                                                                                        | 0            | 0        | 0  | 1    | 0  | 1  | 0  | 0                                     | Control data input mode (serial data input) 24 data bits are input. See the "DI Control Data (serial data input) Structure" item for details on the meaning of the input data.                                      |  |  |  |

| 2 | IN2 (92)                                                                                        | 1            | 0        | 0  | 1    | 0  | 1  | 0  | 0                                     | Control data input mode (serial data input)     24 data bits are input.     See the "DI Control Data (serial data input) Structure" item for details on the meaning of the input data.                              |  |  |  |

| 3 | OUT (A2)                                                                                        | 0            | 1        | 0  | 1    | 0  | 1  | 0  | 0                                     | Data output mode (serial data output) The number of bits output is equal to the number of clock cycles. See the "DO Output Data (Serial Data Output) Structure" item for details on the meaning of the output data. |  |  |  |

|   | CL (3) DI BO  DO (4) (2) (3) (4) (5) (6) (6) (7) (7) (8) (9) (9) (9) (9) (9) (9) (9) (9) (9) (9 | B1  CL: norr | mal high |    | B3 \ |    | A1 | A2 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | J/O mode determined    J/O mode determined                                                                                                                                                                          |  |  |  |

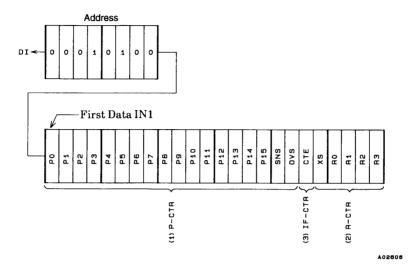

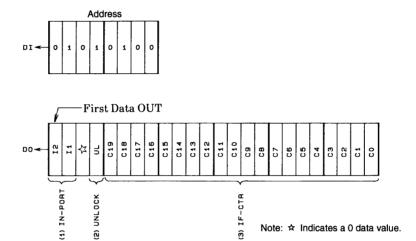

## DI Control Data (serial data input) Structure

## 1. IN1 Mode

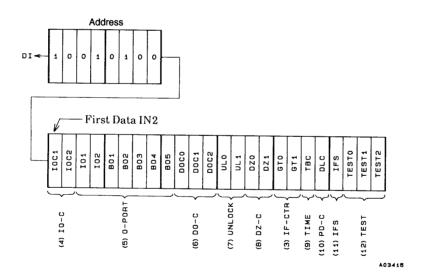

## 2. IN2 Mode

## **DI Control Data Functions**

| No.   | Control block/data                       |              | Description                                                                       |                          |                              |             |                                                              |                 |                                     |        | Related data |  |

|-------|------------------------------------------|--------------|-----------------------------------------------------------------------------------|--------------------------|------------------------------|-------------|--------------------------------------------------------------|-----------------|-------------------------------------|--------|--------------|--|

|       | Programmable divider data                | •            | Data that sets the programmable divider                                           |                          |                              |             |                                                              |                 |                                     |        |              |  |

|       | P0 to P15                                |              | A binary value in which P15 is the MSB. The LSB changes depending on DVS and SNS. |                          |                              |             |                                                              |                 |                                     |        |              |  |

|       |                                          |              | DVS                                                                               | SNS                      | LSB                          | Divisor     | r setting (N)                                                | Act             | tual divisor                        |        |              |  |

|       |                                          |              | 1                                                                                 | *                        | P0                           | 272 t       | to 65535                                                     | Twice the val   | lue of the setting                  |        |              |  |

|       |                                          |              | 0                                                                                 | 1                        | P0                           | 272 t       | to 65535                                                     | The value of    | the setting                         |        |              |  |

|       |                                          |              | 0                                                                                 | 0                        | P4                           | 4           | to 4095                                                      | The value of    | the setting                         |        |              |  |

| (1)   |                                          |              | Note: P0 to P3 are ignored when P4 is the LSB.                                    |                          |                              |             |                                                              |                 |                                     |        |              |  |

|       | DVS, SNS                                 |              |                                                                                   |                          |                              |             | IIN) for the proposition of the property of the pin output s |                 | rider, switches the care.)          |        |              |  |

|       |                                          |              | DVS                                                                               | SNS                      | Input pi                     | n           | Input frequen                                                | cy range        | BOF pin                             |        |              |  |

|       |                                          |              | 1                                                                                 | *                        | FMIN                         |             | 10 to 160                                                    | MHz             | Low                                 |        |              |  |

|       |                                          |              | 0                                                                                 | 1                        | AMIN                         |             | 2 to 40 N                                                    | ЛHz             | Open                                |        |              |  |

|       |                                          |              | 0                                                                                 | 0                        | AMIN                         |             | 0.5 to 10                                                    |                 | Open                                |        |              |  |

|       | B (                                      |              |                                                                                   |                          |                              |             | item for details                                             | •               |                                     | -      |              |  |

|       | Reference divider data<br>R0 to R3       | •            | Reference                                                                         | trequenc                 | y (fref) sel                 | ection dat  | a<br>                                                        |                 |                                     |        |              |  |

|       | No to No                                 |              | R3                                                                                | R2                       | R1                           | R0          | Re                                                           | ference freque  | ncy (kHz)                           |        |              |  |

|       |                                          |              | 0<br>0                                                                            | 0                        | 0                            | 0           |                                                              | 25<br>25        |                                     |        |              |  |

|       |                                          |              | 0                                                                                 | 0                        | 0<br>1                       | 1<br>0      |                                                              | 25<br>25        |                                     |        |              |  |

|       |                                          |              | 0                                                                                 | 0                        | 1                            | 1           |                                                              | 25              |                                     |        |              |  |

|       |                                          |              | 0<br>0                                                                            | 1                        | 0                            | 0<br>1      |                                                              | 12.5<br>6.25    |                                     |        |              |  |

|       |                                          | 0 1 0 1 6.25 |                                                                                   |                          |                              |             |                                                              |                 |                                     |        |              |  |

|       |                                          |              |                                                                                   | 0 1 1 1 3.125            | :5                           |             |                                                              |                 |                                     |        |              |  |

|       |                                          |              |                                                                                   |                          | 1<br>1                       | 0           | 0                                                            | 0<br>1          |                                     | 5<br>5 |              |  |

|       |                                          |              | 1                                                                                 | 0                        | 1                            | 0           |                                                              | 5               |                                     |        |              |  |

| (2)   |                                          |              | 1                                                                                 | 0                        | 1                            | 1           |                                                              | 1               |                                     |        |              |  |

|       |                                          |              |                                                                                   |                          |                              |             |                                                              |                 |                                     |        |              |  |

|       |                                          |              | 1                                                                                 | 1                        | 1                            | 0           | PLL I                                                        | NHIBIT + Xtal   | OSC STOP                            |        |              |  |

|       |                                          |              | 1                                                                                 | 1                        | 1                            |             | PLL INHIB                                                    |                 |                                     |        |              |  |

|       |                                          | '            | Note: PLI                                                                         | INHIBIT                  |                              |             |                                                              |                 |                                     |        |              |  |

|       |                                          |              |                                                                                   |                          |                              |             |                                                              |                 | e FMIN, AMIN,<br>output pin goes to |        |              |  |

|       |                                          |              |                                                                                   |                          | dance stat                   |             | m state, and the                                             | e charge pump   | output pin goes to                  |        |              |  |

|       | XS                                       | •            | Oscillator                                                                        | margin se                | lection dat                  | а           |                                                              |                 |                                     |        |              |  |

|       |                                          |              |                                                                                   | Reduction in reduced.    | mode" The                    | oscillator  | r margin is redu                                             | iced and the cr | rystal radiation                    |        |              |  |

|       |                                          |              |                                                                                   | ormal mod                | le.                          |             |                                                              |                 |                                     |        |              |  |

|       |                                          |              | Normal m                                                                          | ode is sele              | ected follov                 | wing a pov  | wer-on reset.                                                |                 |                                     |        |              |  |

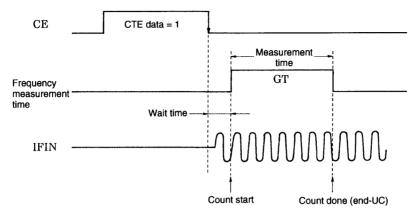

|       | IF counter control data                  |              |                                                                                   |                          | ment start                   | specificat  | ion                                                          |                 |                                     |        |              |  |

|       | CTE                                      |              |                                                                                   | Counter st<br>Counter re |                              |             |                                                              |                 |                                     |        |              |  |

|       | GT0, GT1                                 | •            | IF counter                                                                        | measure                  | ment time                    | determina   | ation                                                        |                 |                                     |        |              |  |

|       |                                          |              | GT1                                                                               | GT0                      | Meas                         | surement    | time (ms)                                                    | Wa              | uit time (ms)                       |        |              |  |

| (3)   |                                          |              | 0                                                                                 | 0                        | Wicas                        | 4           | unic (ms)                                                    | vva             | 3 to 4                              |        | FS           |  |

|       |                                          |              | 0                                                                                 | 1                        |                              | 8           |                                                              |                 | 3 to 4                              |        |              |  |

|       |                                          |              | 1                                                                                 | 0                        |                              | 32          |                                                              |                 | 7 to 8                              |        |              |  |

|       |                                          |              | 1                                                                                 | 1                        |                              | 64          |                                                              |                 | 7 to 8                              |        |              |  |

|       |                                          |              | Note: See                                                                         | the "IF C                | ounter Str                   | ucture" ite | m for details.                                               |                 |                                     |        |              |  |

| (4)   | I/O port specification data              |              | Data that specifies input or output for the I/O dual-use pins                     |                          |                              |             |                                                              |                 |                                     |        |              |  |

| L . / | IOC1, IOC2                               |              |                                                                                   |                          | e, 1 = outp                  |             | -1-4-                                                        |                 |                                     | -      |              |  |

| (5)   | Output port data<br>BO1 to BO5, IO1, IO2 |              |                                                                                   | )5, IO1, aı<br>open, 1 = | nd <del>IO2</del> out<br>low | put state ( | uata                                                         |                 |                                     | - 1    | OC1          |  |

| (3)   | ,,                                       |              |                                                                                   |                          |                              | ollowing a  | power-on rese                                                | t.              |                                     |        | OC2          |  |

|       | <b>1</b>                                 | _            |                                                                                   | •                        |                              | 3 -         |                                                              |                 |                                     | _      |              |  |

## Continued from preceding page.

| No.  | Control block/data       |              |              |                 | Related data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                          |                   |

|------|--------------------------|--------------|--------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------|

|      | DO pin control data      | Data that    | determine    | s DO pin        | output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                          |                   |

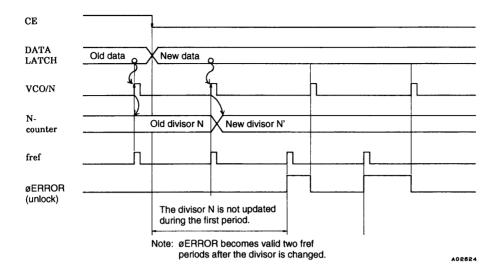

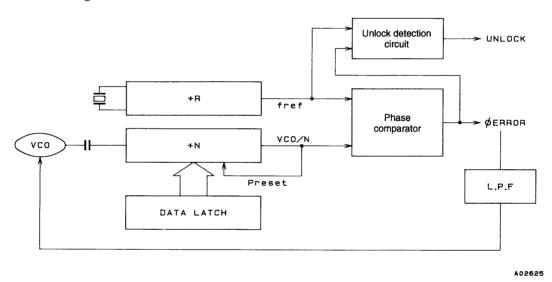

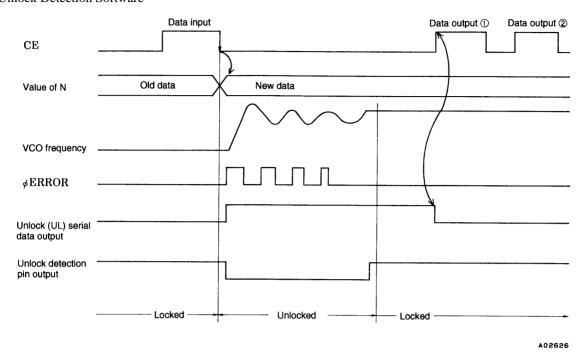

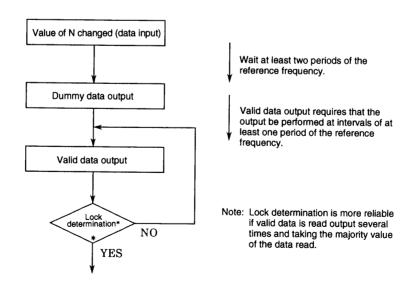

|      | DOC0, DOC1, DOC2         | DOC2         | DOC1         | DOC0            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DO pin state                                                             |                   |