# 3-Phase Brushless Motor Driver for VCR Capstan Motors

#### Overview

The LB1980 is a 3-phase brushless motor driver IC that is particularly well suited for driving VCR capstan motors.

#### **Functions**

- · Three-phase full wave current linear drive

- Torque ripple correction circuit with variable correction ratio

- · Current limiter circuit

- Output stage up/down oversaturation protection circuit (no external capacitor required)

- · FG amplifier

- · Thermal shutdown circuit

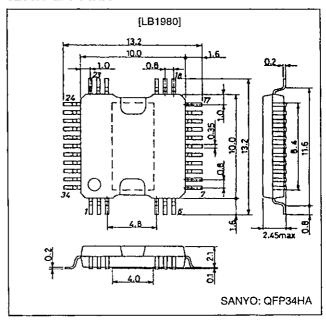

# **Package Dimensions**

unit: mm

#### 3206A-QFP34HA

## **Specifications**

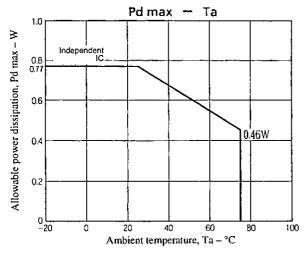

Absolute Maximum Ratings at Ta = 25°C

| Parameter                   | Symbol              | Conditions                          | Ratings    | Unit |

|-----------------------------|---------------------|-------------------------------------|------------|------|

|                             | V <sub>CC</sub> max |                                     | 7          | ٧    |

| Maximum supply voltage      | V <sub>S</sub> max  |                                     | 24         | ٧    |

| Maximum output current      | I <sub>O</sub> max  |                                     | 1.3        | Α    |

|                             |                     | With an arbitrarily large heat sink | 12.5       | W    |

| Allowable power dissipation | Pd max              | Independent IC                      | 0.77       | W    |

| Operating temperature       | Topr                |                                     | -20 to +75 | °C   |

| Storage temperature         | Tstg                |                                     | 55 to +150 | °C   |

Allowable Operating Ranges at Ta = 25°C

| Parameter            | Symbol              | Conditions                                | Ratings        | Unit_ |

|----------------------|---------------------|-------------------------------------------|----------------|-------|

|                      | Vs                  |                                           | 5 to 22        | ٧     |

| Supply voltage       | V <sub>CC</sub>     |                                           | 4.5 to 5.5     | V     |

| Hall input amplitude | V <sub>HALL</sub>   | Between Hall inputs                       | ±30 to ±80     | mVo-p |

| GSENSE input range   | V <sub>GSENSE</sub> | With respect to the control system ground | -0.20 to +0.20 | ٧     |

# Electrical Characteristics at Ta = 25°C, $V_{CC}$ = 5 V, $V_S$ = 15 V

| Parameter                                                | Symbol            | Conditions                                                                                                                         | Ratings |             |               | Unit |

|----------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|---------------|------|

| raianietei                                               | Symbol            | Conditions                                                                                                                         | min     | typ         | max           |      |

| V <sub>CC</sub> current drain                            | lcc               | R <sub>L</sub> = ∞, V <sub>CTL</sub> = 0 V,<br>V <sub>LIM</sub> = 0 V(When stopped)                                                |         | 12          | 18            | mA   |

| [Output]                                                 | <u> </u>          |                                                                                                                                    |         | <del></del> |               |      |

| Output coturation voltage                                | Vo(sat)1          | $I_O = 500$ mA, Rf = 0.5 $\Omega$ , Sink + Source $V_{CTL} = V_{LIM} = 5$ V(With saturation protection)                            | _       | 2.1         | 2.6           | ٧    |

| Output saturation voltage                                | Vo(sat)2          | $I_O = 1.0$ A, Rf = 0.5 $\Omega$ , Sink + Source $V_{CTL} = V_{LIM} = 5$ V(With saturation protection)                             | -       | 2.6         | 3.5           | ٧    |

| Output leakage current                                   | lo leak           |                                                                                                                                    |         | -           | 1.0           | mA   |

| [FR]                                                     |                   |                                                                                                                                    |         |             |               |      |

| FR pin input threshold voltage                           | V <sub>FSR</sub>  |                                                                                                                                    | 2.25    | 2.50        | 2.75          | V    |

| FR pin input bias current                                | lb(FSR)           |                                                                                                                                    | -5.0    | -           | _             | μA   |

| [Control]                                                |                   |                                                                                                                                    |         | •           |               |      |

| CTLREF pin voltage                                       | VC <sub>REF</sub> |                                                                                                                                    | 2.05    | 2.15        | 2.25          |      |

| CTLREF pin input range                                   | VCREFIN           |                                                                                                                                    | 1.50    | -           | 3.50          | ٧    |

| CTL pin input bias current                               | Ib(CTL)           | V <sub>CTL</sub> = 5 V, with CTLREF open                                                                                           | -       | _           | 4.0           | μA   |

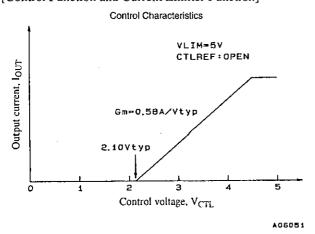

| CTL control start voltage                                | VCTL(ST)          | With Rf = 0.5 $\Omega$ , $V_{LIM}$ = 5 V, $I_Q \ge 10$ mA<br>With the Hall input logic fixed(u, v, w = H, H, L)                    | 2.00    | 2.15        | 2.30          | ٧    |

| CTL pin control Gm                                       | Gm(CTL)           | With Rf = $0.5 \Omega$ , $\Delta l_0 = 200 \text{ mA}$<br>With the Hall input logic fixed(u, v, w = H, H, L)                       | 0.46    | 0.58        | 0.70          | ΑV   |

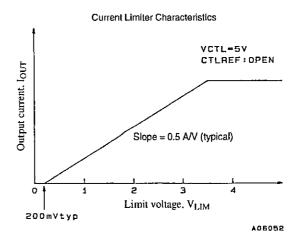

| [Current Limiter]                                        | <del></del>       | <u> </u>                                                                                                                           |         |             |               |      |

| LIM current limiter offset voltage                       | Voff(LIM)         | With Rf = 0.5 $\Omega$ , V <sub>CTL</sub> = 5 V, I <sub>O</sub> $\geq$ 10 mA<br>With the Hall input logic fixed(u, v, w = H, H, L) | 140     | 200         | 260           | mV   |

| LIM pin input bias current                               | ib(LIM)           | V <sub>CTL</sub> = 5 V, CTLREF: OPEN, V <sub>LIM</sub> = 0 V                                                                       | -2.5    |             | -             | μA   |

| LIM pin current limit level                              | llim              | With Rf = $0.5 \Omega$ , $V_{CTL} = 5 V$ , $V_{LIM} = 20.6 V$<br>With the Hall input logic fixed(u, v, w = H, H, L)                | 830     | 900         | 970           | mA   |

| [Hail Amplifier]                                         |                   | · · · · · · · · · · · · · · · · · · ·                                                                                              |         |             | -             |      |

| Hall amplifier input offset voltage                      | Voff(HALL)        |                                                                                                                                    | -6      |             | +6            | mV   |

| Hall amplifier input bias current                        | lb(HALL)          |                                                                                                                                    | -1      | 1.0         | 3.0           | μА   |

| Hall amplifier common-mode input voltage                 | Vcm(HALL)         |                                                                                                                                    | 1.3     | -           | 3.3           | V    |

| [TRC]                                                    | •                 | · · · · · · · · · · · · · · · · · · ·                                                                                              |         |             | <del></del> ' |      |

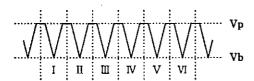

| Torque ripple correction ratio                           | TRC               | For the troughs and peaks in the Rf waveform at $I_0$ = 200 mA(Rf = 0.5 $\Omega$ , ADJ: open)(note 1)                              | -       | 9           | _             | %    |

| ADJ pin voltage                                          | Vadj              |                                                                                                                                    | 2.37    | 2.50        | 2.63          | Ý    |

| [FG Amplifier]                                           |                   | ·                                                                                                                                  | , L     | I           |               |      |

| FG amplifier input offset voltage                        | Voff(FG)          |                                                                                                                                    | -8      | - 1         | +8            | mV   |

| FG amplifier input bias current                          | lb(FG)            |                                                                                                                                    | -100    |             | . –           | пA   |

| FG amplifier output saturation voltage                   | Vo(sat)(FG)       | For the sink side and the internal pull-up resistor load                                                                           | -       | -           | 0.5           | V    |

| FG amplifier voltage gain                                | VG(FG)            | For open loop at f = 10 kHz                                                                                                        | 41.5    | 44.5        | 47.5          | dB   |

| FG amplifier common-mode input voltage                   | VCM(FG)           |                                                                                                                                    | 0.5     |             | 4.0           | v    |

| [Saturation]                                             |                   |                                                                                                                                    |         | J.          |               |      |

| Saturation prevention circuit lower side voltage setting | Vo(sat)(DET)      | $I_O$ = 10 mA, Rf = 0.5 $\Omega$ The voltage between each OUT and Rf when $V_{CTL}$ = $V_{LIM}$ = 5 V.                             | 0.175   | 0.25        | 0.325         | ٧    |

| [TSD]                                                    |                   |                                                                                                                                    |         |             |               |      |

| TSD operating temperature                                | T-TSD             | (Design target value)*                                                                                                             | - [     | 180         | -             | °C   |

| TSD temperature hysteresis                               | ΔTSD              | (Design target value)*                                                                                                             |         | 20          |               | °C   |

| Notes: *Items marked with an asterisk are de             |                   |                                                                                                                                    |         |             |               |      |

Notes: \*Items marked with an asterisk are design target values and are not measured.

1. The torque ripple correction ratio is determined from the Rf voltage waveform as follows.

$$= \frac{2 \cdot (Vp - Vb)}{Vp + Vb} \cdot 100 \, (\%)$$

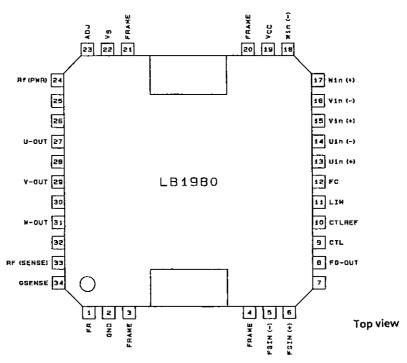

#### Pin Assignment

Note: For ground potential stabilization, the FRAME pins must be connected to ground.

#### **Truth Table and Control Functions**

|     | Source → Sink     | Hall input |   | FR |                 |  |

|-----|-------------------|------------|---|----|-----------------|--|

|     | Source → Sink     | U          | ٧ | W  | ] <sup>FN</sup> |  |

| 1 - | $V \rightarrow W$ | - н        | н | L  | Н               |  |

|     | $W \rightarrow V$ | _ n        | " |    | L               |  |

| 2   | $U \rightarrow W$ | н          | L | L  | Н               |  |

|     | $W \rightarrow U$ | [1         |   |    | L               |  |

| 3   | U -→ V            | Н          |   | н  | Н               |  |

| ٥   | V → U             | 7          |   |    | L               |  |

| 4   | $W \rightarrow V$ |            | 1 | Н  | Н               |  |

|     | $V \rightarrow W$ | Ī          | L |    | L               |  |

| 5   | $W \rightarrow U$ |            | Н | н  | н               |  |

|     | U→W               | <u> </u>   | п |    | L               |  |

| 6   | $V \rightarrow U$ |            | Н | L  | Н               |  |

|     | U→V               | }          | " |    | L               |  |

Note: An H in the FR column indicates a voltage of 2.75 V or higher, and an L indicates a voltage of 2.25 V or lower. (When V<sub>CC</sub> = 5 V.)

Note: For the Hall inputs, H indicates that the + input is 0.01 V or more higher than the - input, and L indicates that the + input is 0.01 V or more lower than the - input, for all phases.

Note: Since this drive technique is a 180° conducting technique, the phases other than the sink and source phases are never off.

#### [Control Function and Current Limiter Function]

## **Pin Functions**

| Pin No.  | Pin name | Pin functions                                                                            | Equivalent circuit                          |

|----------|----------|------------------------------------------------------------------------------------------|---------------------------------------------|

| 1        | FR       | Forward/reverse selection pin.                                                           |                                             |

|          |          | Forward or reverse is selected by the voltage applied to this pin.                       |                                             |

|          |          | (Vth = 2.5 V (typical) at V <sub>CC</sub> = 5 V)                                         | VCCA VCCA VCCA                              |

| 23       | ADJ      | This pin allows the torque ripple correction ratio to be adjusted                        | [ S20#A ]                                   |

|          |          | externally. Applications that adjust the correction ratio should                         |                                             |

| .        |          | apply a voltage to the ADJ pln with a low-impedance circuit.                             | EB                                          |

|          |          | The correction ratio falls as the applied voltage increases, and                         | 200a   5kg 500a 6kg                         |

| i I      |          | increases as the applied voltage decreases. The correction ratio                         | T   VCC   \$10k0 10k0\$                     |

|          |          | can be varied over a range from about 0 to twice the ratio when                          | l 1" Il l                                   |

|          |          | this pin is left open. (This voltage is set internally to about $V_{CO}/2$ ,             | A08058                                      |

|          |          | and the input impedance is about 5 kΩ.)                                                  |                                             |

| 2        | GND      | Ground for circuits other than the output transistors                                    |                                             |

| <u> </u> |          | The output transistor minimum potential is that of the resistor Rf.                      |                                             |

| 5        | FGin-    | When the FG amplifier is used as an inverting input amplifier,                           | VCC A                                       |

|          |          | a feedback resistor must be inserted between FG-OUT                                      |                                             |

| 1        |          | and this pin.                                                                            |                                             |

|          |          |                                                                                          | 5#A                                         |

|          |          |                                                                                          | [                                           |

| 6        | EC:      | This is the positive transfer to the FO                                                  | FGin (-) FGin (+)                           |

|          | FGin+    | This is the noninverting input when the FG amplifier is used as                          | T 7 300 7 1                                 |

|          |          | a differential input amplifier. There is no internally applied bias.                     | *     *                                     |

| ]        | ,        |                                                                                          | <del> </del>                                |

|          |          |                                                                                          | A05057                                      |

| 8        | FG-OUT   | This is the FG amplifier output. It has an internal load resistance.                     |                                             |

|          |          | ·                                                                                        |                                             |

|          |          |                                                                                          | Acc Vacc                                    |

|          |          |                                                                                          |                                             |

|          |          |                                                                                          | FGOUT                                       |

| 12       | FC       | Frequency characteristics correction for the speed control loop                          | 3000                                        |

|          |          |                                                                                          | │                                           |

|          |          |                                                                                          |                                             |

|          |          |                                                                                          | 40805                                       |

|          |          |                                                                                          |                                             |

| 9        | CTL      | Speed control connection. Speed control is implemented as a                              |                                             |

|          |          | fixed current drive in which current feedback is applied from Rf.                        |                                             |

| <u></u>  |          | Gm = 0.58 A/V (typical) at Rf = $0.5 \Omega$                                             | **CC                                        |

| 10       | CTLREF   | Control reference. Although this pin is set to about 0.43 * V <sub>CC</sub>              | CTL BOOMAN                                  |

|          |          | internally, it can be changed by applying a voltage with                                 | O DOOR TOOK TOOK TOOK TOOK TOOK TOOK TOOK T |

|          |          | a low-impedance circuit. (It has an input impedance of about                             | ★                                           |

|          |          | 4.3 kΩ (typical).)                                                                       | #                                           |

|          | 1104     | Courses Business Superior control The college and the Marie and                          | 100#4 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| 11       | LIM      | Current limiter function control. The voltage applied to this pin                        | AOSOSS                                      |

|          |          | changes the output current linearly. Slope = 0.5 A/V (typical)                           |                                             |

| 12       | Uin+     | at Rf = 0.5 Ω.  U phase Hall element input. IN+ must be higher than IN-                  |                                             |

| 13<br>14 | Uin-     | 1                                                                                        | Each (+) input Each (-) input               |

| 15       | Vin+     | for a logical high input level.  V phase Hall element input. IN+ must be higher than IN- | 2000                                        |

| 16       | Vin-     | for a logical high input level.                                                          | * ****                                      |

| 17       | Win+     | W phase Hall element input. IN+ must be higher than IN-                                  | # SIODHA #                                  |

| 1        | i        | 1 '                                                                                      | <u></u>                                     |

| 18       | Win-     | for a logical high input level.                                                          | AD6053                                      |

Continued on next page.

#### Continued from preceding page.

| Pin No. | Pin name | Pin functions                                                      | Equivalent circuit              |

|---------|----------|--------------------------------------------------------------------|---------------------------------|

| 19      | Vcc      | Power supply for all IC internal circuits except for the output    |                                 |

| •       |          | block. This voltage must be stabilized so that ripple and noise    | 1                               |

|         |          | do not enter the IC circuits.                                      |                                 |

| 22      | ٧s       | Output block power supply                                          |                                 |

| 24      | Rf       | These are the output current detection pins, and the control       | ]                               |

|         | (PWR)    | block current feedback is applied by connecting the resistor       |                                 |

| 33      | Rí       | Rf between these pins and ground. Additionally, the lower side     | V <sub>S</sub> V <sub>C</sub> C |

|         | (SENSE)  | oversaturation protection circult and the torque ripple correction | Lower side saturation           |

|         |          | circuit operate according to the voltages on these pins.           | prevention circuit input        |

|         | 1        | In particular, since the oversaturation protection level is set by | Each out                        |

|         |          | the voltages on these pins, if the value of Rf is lowered          | 2000                            |

|         |          | excessively, the effectiveness of the lower side oversaturation    | —— \$30×4 #                     |

|         |          | protection in the high-current region will be degraded.            | 2000                            |

|         |          | Note that the POWER and SENSE pins must be connected               | RI (SENSE)                      |

|         |          | together.                                                          | Rf (PONER)                      |

| 27      | U-OUT    | U phase output. (A spark killer diode is built in.)                | A08054                          |

| 29      | V-OUT    | V phase output. (A spark killer diode is built in.)                |                                 |

| 31      | W-OUT    | W phase output. (A spark killer diode is built in.)                | ·                               |

| 34      | GSENSE   | Ground sense. By connecting this pin near the ground for the       |                                 |

|         |          | Rf resistor side of the motor ground wiring that includes Rf,      |                                 |

|         |          | the influence that the common ground Impedance has on              |                                 |

|         |          | Rf can be removed. (This pin must not be left open.)               |                                 |

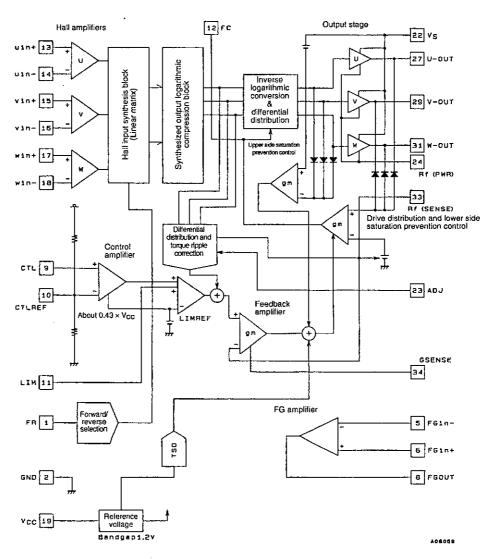

## **Block Diagram**

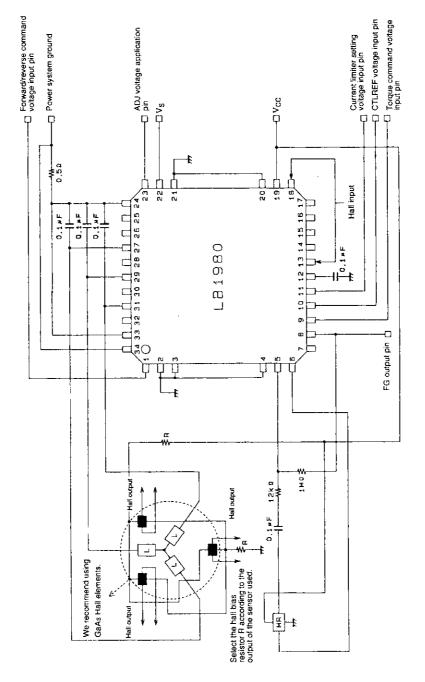

#### **Sample Application Circuit**

Note: The constants presented in this sample application circuit are examples, and the circuit characteristics for these values are not guaranteed.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.