# **PWM Current Control Stepping Motor Driver**

### Overview

The LB1845 is a PWM current control type stepping motor driver that uses a bipolar drive scheme. It is particularly suitable for driving carriage and paper feed stepping motors in printers and similar products.

## **Features**

- PWM current control (fixed off time scheme)

- Digital load current selection function

- Sustained output voltage: 45 V

- Built-in thermal shutdown circuit

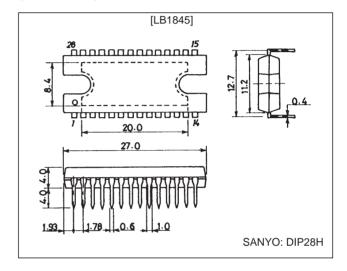

## **Package Dimensions**

unit: mm

#### 3147A-DIP28H

## **Specifications**

### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol             | Conditions                          | Ratings                 | Unit |

|-----------------------------|--------------------|-------------------------------------|-------------------------|------|

| Motor supply voltage        | V <sub>BB</sub>    |                                     | 45                      | V    |

| Peak output current         | I <sub>OPEAK</sub> | t <sub>W</sub> = 20 μS              | 1.75                    | А    |

| Continuous output current   | I <sub>OMAX</sub>  |                                     | 1.5                     | Α    |

| Logic block supply voltage  | V <sub>CC</sub>    |                                     | 7.0                     | V    |

| Logic input voltage range   | V <sub>IN</sub>    |                                     | -0.3 to V <sub>CC</sub> | V    |

| Emitter output voltage      | V <sub>E</sub>     |                                     | 1.0                     | V    |

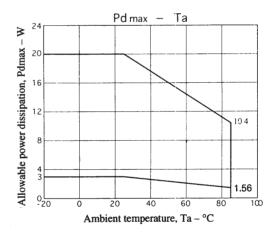

| All II Bring                | Pd max1            | Independent IC                      | 3.0                     | W    |

| Allowable power dissipation | Pd max2            | With an arbitrarily large heat sink | 20.0                    | W    |

| Operating temperature       | Topr               |                                     | -20 to +85              | °C   |

| Storage temperature         | Tstg               |                                     | -55 to +150             | °C   |

## Recommended Operating Ranges at $Ta = 25^{\circ}C$

| Parameter                  | Symbol           | Conditions | Ratings      | Unit |

|----------------------------|------------------|------------|--------------|------|

| Motor supply voltage       | V <sub>BB</sub>  |            | 10 to 44.5   | V    |

| Logic block supply voltage | V <sub>CC</sub>  |            | 4.75 to 5.25 | V    |

| Reference voltage          | V <sub>REF</sub> |            | 1.5 to 7.5   | V    |

# Electrical Characteristics at Ta = 25°C, $V_{BB}$ = 38 V, $V_{CC}$ = 5 V, $V_{REF}$ = 5 V

| Parameter                         | Cumbal                               | Conditions                     | Ratings |      |      | Unit  |

|-----------------------------------|--------------------------------------|--------------------------------|---------|------|------|-------|

| Parameter                         | Symbol                               | Symbol                         |         | typ  | max  | Offic |

| [Output Block]                    |                                      |                                |         |      |      |       |

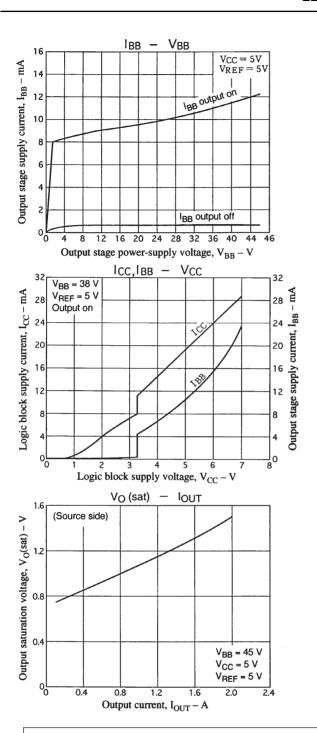

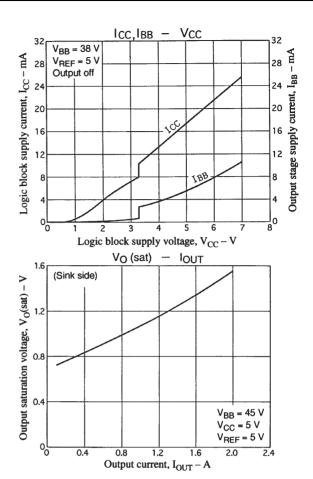

|                                   | I <sub>BB ON</sub>                   |                                |         | 12   | 16   | mA    |

| Output stage supply voltage       | I <sub>BB OFF</sub>                  |                                |         | 0.7  | 0.9  | mA    |

|                                   | V <sub>O</sub> (sat)1                | I <sub>O</sub> = +1.0 A sink   |         | 1.2  | 1.4  | V     |

|                                   | V <sub>O</sub> (sat)2                | I <sub>O</sub> = +1.5 A sink   |         | 1.4  | 1.7  | V     |

| Output saturation voltage 1       | V <sub>O</sub> (sat)3                | I <sub>O</sub> = -1.0 A source |         | 1.1  | 1.3  | V     |

|                                   | V <sub>O</sub> (sat)4                | I <sub>O</sub> = -1.5 A source |         | 1.3  | 1.6  | V     |

|                                   | I <sub>O</sub> (leak)1               | $V_O = V_{BB}$ sink            |         |      | 50   | μA    |

| Output leakage current            | I <sub>O</sub> (leak)2               | V <sub>O</sub> = 0 V source    | -50     |      |      | μA    |

| Sustained output voltage          | V(sus)                               | *                              | 45      |      |      | V     |

| [Logic Block]                     |                                      |                                |         |      |      |       |

|                                   | I <sub>CC ON</sub>                   | I0 = 0.8 V, I1 = 0.8 V         |         | 19.5 | 25.3 | mA    |

| Logic supply current              | I <sub>CC OFF</sub>                  | I0 = 2.4 V, I1 = 2.4 V         |         | 15.5 | 20.1 | mA    |

|                                   | V <sub>IH</sub>                      |                                | 2.4     |      |      | V     |

| Input voltage                     | V <sub>IL</sub>                      |                                |         |      | 0.8  | V     |

|                                   | I <sub>IH</sub>                      | V <sub>IH</sub> = 2.4 V        |         |      | 10   | μA    |

| Input current                     | I <sub>IL</sub>                      | V <sub>IL</sub> = 0.8 V        | -10     |      |      | μΑ    |

|                                   |                                      | I0 = 0.8 V, I1 = 0.8 V         | 9.5     | 10   | 10.5 |       |

| Current control threshold voltage | V <sub>REF</sub> /V <sub>SENSE</sub> | I0 = 2.4 V, I1 = 0.8 V         | 13.5    | 15   | 16.5 |       |

|                                   |                                      | I0 = 0.8 V, I1 = 2.4 V         | 25.5    | 30   | 34.5 |       |

| Thermal shutdown temperature      | T <sub>S</sub>                       |                                |         | 170  |      | °C    |

Note: \*Design guaranteed value

### **Truth Table**

| ENABLE | PHASE | OUT A | OUT B |

|--------|-------|-------|-------|

| L      | Н     | Н     | L     |

| L L    |       | L     | Η     |

| Н      | _     | OFF   | OFF   |

| 10 | l1 | Output current                                   |

|----|----|--------------------------------------------------|

| L  | L  | $V_{REF} / (10 \times R_E) = I_{OUT}$            |

| Н  | L  | $V_{REF} / (15 \times R_E) = I_{OUT} \times 2/3$ |

| L  | Н  | $V_{REF} / (30 \times R_E) = I_{OUT} \times 1/3$ |

| Н  | Н  | 0                                                |

Note: Outputs go off when ENABLE is high or in the 10 = 11 = high state.

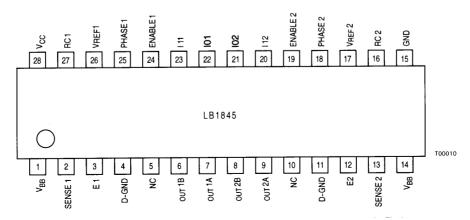

# **Pin Assignment**

Top view

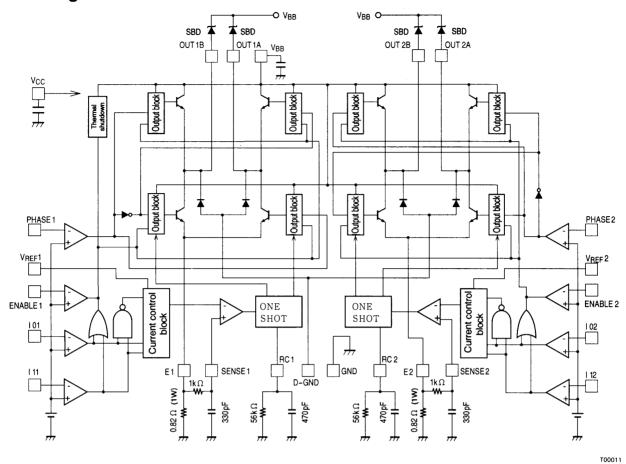

# **Block Diagram**

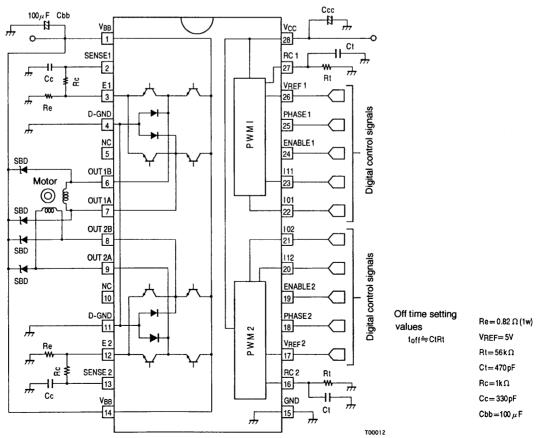

# **Application Circuit Diagram**

## **Pin Functions**

| Pin no. | Pin                | Function                                                                                                                      |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 1, 14   | V <sub>BB</sub>    | Output stage power-supply voltage                                                                                             |

| 2       | SENSE1             | Set current detection pins.                                                                                                   |

| 13      | SENSE2             | Connect these pins, fed back through noise filters, to E1 and E2.                                                             |

| 3       | E1                 | The set current is controlled by the resistors Re inserted between these pins and ground.                                     |

| 12      | E2                 |                                                                                                                               |

| 4, 11   | D-GND              | Internal diode anode connection                                                                                               |

| 6       | OUT 1B             | Outputs                                                                                                                       |

| 7       | OUT 1A             |                                                                                                                               |

| 8       | OUT 2B             |                                                                                                                               |

| 9       | OUT 2A             |                                                                                                                               |

| 15      | GND                | Ground                                                                                                                        |

| 27      | RC1                | Used to set the output off time for the switched output signal.                                                               |

| 16      | RC2                | The fixed off times are set by the capacitors and resistors connected to these pins. toff = CR.                               |

| 26      | V <sub>REF</sub> 1 | Output current settings                                                                                                       |

| 17      | V <sub>REF</sub> 2 | The output current is determined by the voltage (in the range 1.5 to 7.5 V) input to these pins.                              |

| 25      | PHASE1             | Output phase switching inputs.                                                                                                |

| 18      | PHASE2             | High-level input: OUT A = high, OUT B = low                                                                                   |

|         |                    | Low-level input: OUT A = low, OUT B = high                                                                                    |

| 24      | ENABLE1            | Output on/off settings                                                                                                        |

| 19      | ENABLE2            | High-level input: output off                                                                                                  |

|         |                    | Low-level input: output on                                                                                                    |

| 22, 23  | I01, I11           | Digital inputs that set the output current                                                                                    |

| 21, 20  | 102, 112           | The output currents can be set to 1/3, 2/3, or full by setting these pins to appropriate combinations of high and low levels. |

| 28      | V <sub>CC</sub>    | Logic block power supply                                                                                                      |

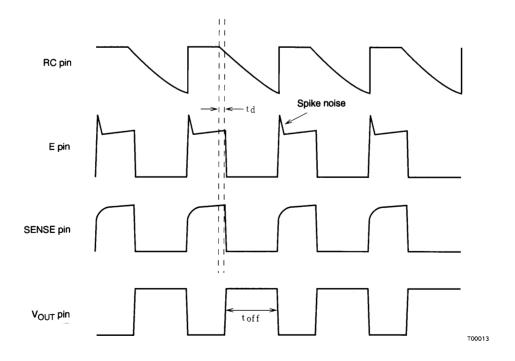

## Timing chart for pin switching operations during PWM drive

Figure 1 Switching Waveforms

toff: Output off time. Determined by external capacitor and resistor Ct and Rt. (toff =  $Ct \times Rt$ ) td: Delay time between the point the set current is sensed at the SENSE pin and the point the output turns off.

#### **Usage Notes**

#### 1. External diode

Since this IC adopts a system based on lower side transistor switching drive, an external diode for the regenerative current that occurs during switching is required between  $V_{BB}$  and  $V_{OUT}$ . Use a Schottky barrier diode with a low feedthrough current.

#### 2. Noise filters

Since spike noise (see Figure 1) occurs when switching to the on state due to the external diode's feedthrough current, applications must remove noise from the SENSE pin with a noise filter (Cc, Rc) between the E pin and the SENSE pin. However, note that if the values of Cc and Rc are too large, the SENSE voltage rise will be slowed, and the current setting will be shifted towards a higher current level.

## $3.V_{REF}$ pin

It is possible to change the output current continuously by continuously changing the  $V_{REF}$  pin voltage. However, this voltage cannot be set to 0 V. The  $V_{REF}$  pin input impedance is 26 k $\Omega$  ( $\pm 30\%$ ) when  $V_{REF}$  is 5 V. Since this pin is used to set the output current, applications must be designed so that noise does not appear on this pin's input.

#### 4. GND pin

Since this IC switches large currents, care must be taken to avoid ground loops when the IC is mounted in the application. The section of the PCB that handles large currents should be designed with a low-impedance pattern, and must be separated from the small signal sections of the circuit. In particular, the ground for the sense resistor Re must be as close as possible to the IC ground.

#### 5. Operation in hold mode

There are cases where a current somewhat larger than the current setting may flow in hold mode (light load mode). Since this IC adopts a lower side switching, lower side sense system, the emitter voltage falls and the sense voltage goes to 0 when the switching state goes to off. The circuit then always turns the output on after the toff period has elapsed. At this time, due to the light load, the existence of the time td, and the fact that the output goes on even if the output current is higher than the set current, the output current will be somewhat higher than the set current. Applications should set the current setting somewhat lower than required if this occurs.

### 6. Function for preventing the upper and lower outputs being on at the same time

This IC incorporates a built-in circuit that prevents the through currents that occur when the phase is switched. The table lists the output on and off delay times when PHASE and EANBLE are switched.

|                        |                | Sink side | Source side |

|------------------------|----------------|-----------|-------------|

| M/ BUAGE: ': !         | On delay time  | 10 µs     | 9 µs        |

| When PHASE is switched | Off delay time | 1.5 µs    | 3 µs        |

| MI ENIABLE:            | On delay time  | 9 µs      | 9 µs        |

| When ENABLE is on      | Off delay time | 1.5 µs    | 6.5 µs      |

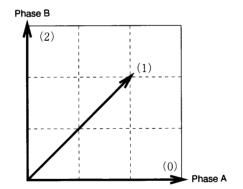

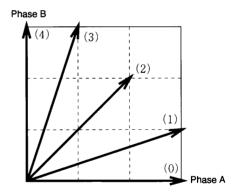

#### 7.1-2 phase excitation and the double 1-2 phase excitation control sequence

To reduce the vibration that occurs when the motor turns, this IC supports 1-2 phase excitation and double 1-2 phase excitation by using the output current setting digital input pins I0 and I1 without changing the  $V_{REF}$  pin voltage. Tables 1 and 2 list that control sequence, and Figure 2 and Figure 3 present the composite vector diagram for this sequence.2. Noise filters

Table 1 [1-2 phase excitation] 1/2 step

ENABLE1 = ENABLE2 = 0

|     | Phase A |     |     | Phase B       |     |     |     |               |

|-----|---------|-----|-----|---------------|-----|-----|-----|---------------|

| No. | PH1     | l11 | I01 | Current value | PH2 | l12 | 102 | Current value |

| 0   | 0       | 0   | 0   | 1             | *   | 1   | 1   | 0             |

| 1   | 0       | 0   | 1   | 2/3           | 0   | 0   | 1   | 2/3           |

| 2   | *       | 1   | 1   | 0             | 0   | 0   | 0   | 1             |

| 3   | 1       | 0   | 1   | 2/3           | 0   | 0   | 1   | 2/3           |

| 4   | 1       | 0   | 0   | 1             | *   | 1   | 1   | 0             |

| 5   | 1       | 0   | 1   | 2/3           | 1   | 0   | 1   | 2/3           |

| 6   | *       | 1   | 1   | 0             | 1   | 0   | 0   | 1             |

| 7   | 0       | 0   | 1   | 2/3           | 1   | 0   | 1   | 2/3           |

Table 2 [Double 1-2 phase excitation] about 1/4 step

FNARI F1 = FNARI F2 = 0

|     |     | Ph  | nase A |               | Phase B |     |     |               |

|-----|-----|-----|--------|---------------|---------|-----|-----|---------------|

| No. | PH1 | l11 | I01    | Current value | PH2     | l12 | 102 | Current value |

| 0   | 0   | 0   | 0      | 1             | *       | 1   | 1   | 0             |

| 1   | 0   | 0   | 0      | 1             | 0       | 1   | 0   | 1/3           |

| 2   | 0   | 0   | 1      | 2/3           | 0       | 0   | 1   | 2/3           |

| 3   | 0   | 1   | 0      | 1/3           | 0       | 0   | 0   | 1             |

| 4   | *   | 1   | 1      | 0             | 0       | 0   | 0   | 1             |

| 5   | 1   | 1   | 0      | 1/3           | 0       | 0   | 0   | 1             |

| 6   | 1   | 0   | 1      | 2/3           | 0       | 0   | 1   | 2/3           |

| 7   | 1   | 0   | 0      | 1             | 0       | 1   | 0   | 1/3           |

| 8   | 1   | 0   | 0      | 1             | *       | 1   | 1   | 0             |

| 9   | 1   | 0   | 0      | 1             | 1       | 1   | 0   | 1/3           |

| 10  | 1   | 0   | 1      | 2/3           | 1       | 0   | 1   | 2/3           |

| 11  | 1   | 1   | 0      | 1/3           | 1       | 0   | 0   | 1             |

| 12  | *   | 1   | 1      | 0             | 1       | 0   | 0   | 1             |

| 13  | 0   | 1   | 0      | 1/3           | 1       | 0   | 0   | 1             |

| 14  | 0   | 0   | 1      | 2/3           | 1       | 0   | 1   | 2/3           |

| 15  | 0   | 0   | 0      | 1             | 1       | 1   | 0   | 1/3           |

### **Composite Vector Diagram**

[1-2 phase excitation]

Figure 2 Composite Vector Diagram for the Sequence in Table 1 (1/4 cycle)

[Double 1-2 phase excitation]

Figure 3 Composite Vector Diagram for the Sequence in Table 2 (1/4 cycle)

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1996. Specifications and information herein are subject to change without notice.